Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                      |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 67                                                                       |

| Program Memory Size        | 384KB (384K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 36K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p44l3ceaby |

## 1 Introduction

#### 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the SPC560P44/50 series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 1.3 Device comparison

Table 2 provides a summary of different members of the SPC560P44Lx, SPC560P50Lx family and their features—relative to full-featured version—to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

Table 2. SPC560P44Lx, SPC560P50Lx device comparison

| Feature                                              | SPC560P44                       | SPC560P50       |  |

|------------------------------------------------------|---------------------------------|-----------------|--|

| Code flash memory (with ECC)                         | 384 KB                          | 512 KB          |  |

| Data flash memory / EE option (with ECC)             | 64                              | KB              |  |

| SRAM (with ECC)                                      | 36 KB                           | 40 KB           |  |

| Processor core                                       | 32-bit e                        | 200z0h          |  |

| Instruction set                                      | VLE (variable le                | ength encoding) |  |

| CPU performance                                      | 0–64                            | MHz             |  |

| FMPLL (frequency-modulated phase-locked loop) module | 2                               |                 |  |

| INTC (interrupt controller) channels                 | 14                              | 17              |  |

| PIT (periodic interrupt timer)                       | 1 (includes four 32-bit timers) |                 |  |

The SIU provides the following features:

- Centralized general purpose input output (GPIO) control of as many as 80 input/output pins and 26 analog input-only pads (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins (except ADC channels) can be alternatively configured as both general purpose input or output pins

- ADC channels support alternative configuration as general purpose inputs

- Direct readback of the pin value is supported on all pins through the SIUL

- Configurable digital input filter that can be applied to some general purpose input pins for noise elimination: as many as 4 internal functions can be multiplexed onto 1 pin

## 1.5.17 Boot and censorship

Different booting modes are available in the SPC560P44Lx, SPC560P50Lx: booting from internal flash memory and booting via a serial link.

The default booting scheme uses the internal flash memory (an internal pull-down is used to select this mode). Optionally, the user can boot via FlexCAN or LINFlex (using the boot assist module software).

A censorship scheme is provided to protect the content of the flash memory and offer increased security for the entire device.

A password mechanism is designed to grant the legitimate user access to the non-volatile memory.

#### **Boot assist module (BAM)**

The BAM is a block of read-only one-time programmed memory and is identical for all SPC560Pxx devices that are based on the e200z0h core. The BAM program is executed every time the device is powered on if the alternate boot mode has been selected by the user.

The BAM provides the following features:

- Serial bootloading via FlexCAN or LINFlex

- Ability to accept a password via the used serial communication channel to grant the legitimate user access to the non-volatile memory

### 1.5.18 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC560P44Lx, SPC560P50Lx.

The sources of the ECC errors are:

- Flash memory

- SRAM

### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

## 1.5.20 Controller area network (FlexCAN)

The SPC560P44Lx, SPC560P50Lx MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

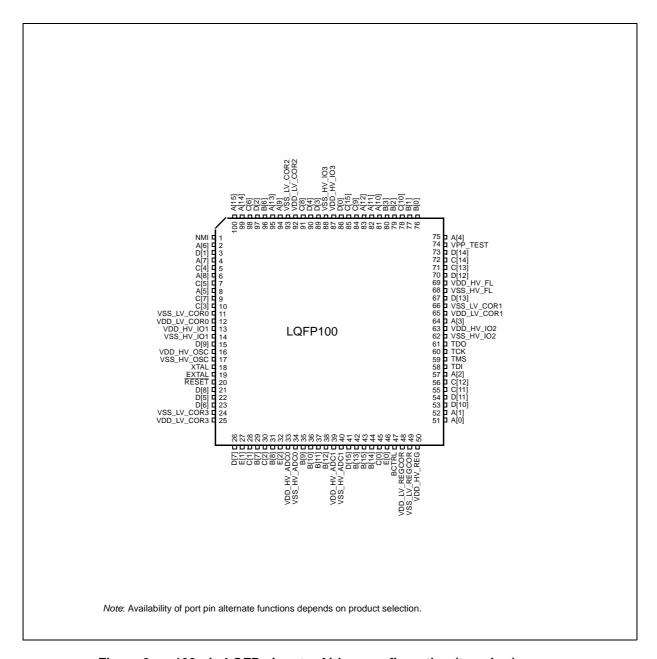

Figure 3. 100-pin LQFP pinout – Airbag configuration (top view)

Table 7. Pin muxing (continued)

| Port           | Pad                          | Alternate                    | ,         |                           | I/O              | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|----------------|------------------------------|------------------------------|-----------|---------------------------|------------------|---------|---------------------|---------|---------|

| pin            | configuration register (PCR) | function <sup>(1),</sup> (2) | Functions | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

|                |                              | ALT0                         | GPIO[14]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | TXD       | Safety Port_0             | 0                |         |                     |         |         |

| A[14]          | PCR[14]                      | ALT2                         | ETC[4]    | eTimer_1                  | I/O              | Slow    | Medium              | 99      | 143     |

|                |                              | ALT3                         | _         | _                         | _                |         |                     |         |         |

|                |                              | _                            | EIRQ[13]  | SIUL                      | I                |         |                     |         |         |

|                |                              | ALT0                         | GPIO[15]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | _         | _                         | _                |         |                     |         |         |

| Λ[1 <i>E</i> ] | A[15] PCR[15]                | ALT2                         | ETC[5]    | eTimer_1                  | I/O              | Slow    | Medium              | 100     | 144     |

| A[15]          | FUN[15]                      | ALT3                         | _         | _                         | _                | Slow    | ivieuluiti          | 100     | 144     |

|                |                              | _                            | RXD       | Safety Port_0             | I                |         |                     |         |         |

|                |                              | _                            | EIRQ[14]  | SIUL                      | I                |         |                     |         |         |

|                |                              |                              |           | Port B (16-bit)           |                  |         |                     |         |         |

|                |                              | ALT0                         | GPIO[16]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | TXD       | FlexCAN_0                 | 0                |         |                     |         |         |

| B[0]           | PCR[16]                      | ALT2                         | ETC[2]    | eTimer_1                  | I/O              | Slow    | Medium              | 76      | 109     |

|                |                              | ALT3                         | DEBUG[0]  | SSCM                      | _                |         |                     |         |         |

|                |                              | _                            | EIRQ[15]  | SIUL                      | I                |         |                     |         |         |

|                |                              | ALT0                         | GPIO[17]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | _         | _                         | _                |         |                     |         |         |

| B[1]           | PCR[17]                      | ALT2                         | ETC[3]    | eTimer_1                  | I/O              | Slow    | Medium              | 77      | 110     |

| [ ال           | FCK[17]                      | ALT3                         | DEBUG[1]  | SSCM                      | _                | Slow    | ivieululli          | ' '     | 110     |

|                |                              | _                            | RXD       | FlexCAN_0                 | I                |         |                     |         |         |

|                |                              | _                            | EIRQ[16]  | SIUL                      | I                |         |                     |         |         |

|                |                              | ALT0                         | GPIO[18]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | TXD       | LIN_0                     | 0                |         |                     |         |         |

| B[2]           | PCR[18]                      | ALT2                         | _         | _                         | _                | Slow    | Medium              | 79      | 114     |

|                |                              | ALT3                         | DEBUG[2]  | SSCM                      | _                |         |                     |         |         |

|                |                              | _                            | EIRQ[17]  | SIUL                      | I                |         |                     |         |         |

|                |                              | ALT0                         | GPIO[19]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | _         | _                         | _                |         |                     |         |         |

| B[3]           | PCR[19]                      | ALT2                         | _         | _                         | _                | Slow    | Medium              | 80      | 116     |

|                |                              | ALT3                         | DEBUG[3]  | SSCM                      | _                |         |                     |         |         |

|                |                              | _                            | RXD       | LIN_0                     | I                |         |                     |         |         |

|                |                              | ALT0                         | GPIO[22]  | SIUL                      | I/O              |         |                     |         |         |

|                |                              | ALT1                         | CLKOUT    | MC_CGL                    | 0                |         |                     |         |         |

| B[6]           | PCR[22]                      | ALT2                         | CS2       | DSPI_2                    | 0                | Slow    | Medium              | 96      | 138     |

|                |                              | ALT3                         | _         | _                         | _                |         |                     |         |         |

|                |                              | _                            | EIRQ[18]  | SIUL                      | I                |         |                     |         |         |

Table 7. Pin muxing (continued)

| Dowt        | Pad                          | Alternate                              | ,                                               |                                             | I/O                    | Pad sp  | peed <sup>(5)</sup> | Pin     | No.     |

|-------------|------------------------------|----------------------------------------|-------------------------------------------------|---------------------------------------------|------------------------|---------|---------------------|---------|---------|

| Port<br>pin | configuration register (PCR) | function <sup>(1),</sup> (2)           | Functions                                       | Peripheral <sup>(3)</sup>                   | direction<br>(4)       | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| B[14]       | PCR[30]                      | ALT0 ALT1 ALT2 ALT3 — — —              | GPIO[30]  AN[1] ETC[4] EIRQ[19]                 | SIUL ADC_1 eTimer_0 SIUL                    | Input only             | _       | I                   | 44      | 64      |

| B[15]       | PCR[31]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[31]  AN[2] EIRQ[20]                        | SIUL  ADC_1 SIUL                            | Input only             | _       | -                   | 43      | 62      |

|             |                              |                                        |                                                 | Port C (16-bit)                             |                        |         |                     |         |         |

| C[0]        | PCR[32]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[32]<br>—<br>—<br>—<br>AN[3]                | SIUL<br>—<br>—<br>—<br>ADC_1                | Input only             | _       | -                   | 45      | 66      |

| C[1]        | PCR[33]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[33]<br>—<br>—<br>—<br>—<br>AN[2]           | SIUL<br>—<br>—<br>—<br>ADC_0                | Input only             | _       | _                   | 28      | 41      |

| C[2]        | PCR[34]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[34]<br>—<br>—<br>—<br>AN[3]                | SIUL<br><br><br>ADC_0                       | Input only             | _       | ĺ                   | 30      | 45      |

| C[3]        | PCR[35]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[35]<br>CS1<br>ETC[4]<br>TXD<br>EIRQ[21]    | SIUL<br>DSPI_0<br>eTimer_1<br>LIN_1<br>SIUL | I/O<br>O<br>I/O<br>O   | Slow    | Medium              | 10      | 16      |

| C[4]        | PCR[36]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[36]<br>CS0<br>X[1]<br>DEBUG[4]<br>EIRQ[22] | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL | I/O<br>I/O<br>I/O<br>— | Slow    | Medium              | 5       | 11      |

Table 7. Pin muxing (continued)

| Table       | Pad                             | Alternate                         | ,                                             |                                                   | I/O                       | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------------|---------------------------------|-----------------------------------|-----------------------------------------------|---------------------------------------------------|---------------------------|---------|---------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) |                                   | Functions                                     | Peripheral <sup>(3)</sup>                         | direction<br>(4)          | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| C[13]       | PCR[45]                         | ALT0 ALT1 ALT2 ALT3 — —           | GPIO[45] ETC[1] — EXT_IN EXT_SYNC             | SIUL eTimer_1  CTU_0 FlexPWM_0                    | I/O<br>I/O<br>—<br>—<br>— | Slow    | Medium              | 71      | 101     |

| C[14]       | PCR[46]                         | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[46]<br>ETC[2]<br>EXT_TGR<br>—            | SIUL<br>eTimer_1<br>CTU_0<br>—                    | I/O<br>I/O<br>O           | Slow    | Medium              | 72      | 103     |

| C[15]       | PCR[47]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[47] CA_TR_EN ETC[0] A[1] EXT_IN EXT_SYNC | SIUL FlexRay_0 eTimer_1 FlexPWM_0 CTU_0 FlexPWM_0 | I/O<br>O<br>I/O<br>O<br>I | Slow    | Symmetric           | 85      | 124     |

|             |                                 |                                   |                                               | Port D (16-bit)                                   |                           |         |                     |         |         |

| D[0]        | PCR[48]                         | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[48]<br>CA_TX<br>ETC[1]<br>B[1]           | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0        | I/O<br>O<br>I/O<br>O      | Slow    | Symmetric           | 86      | 125     |

| D[1]        | PCR[49]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[49]  ETC[2]  EXT_TRG  CA_RX              | SIUL — eTimer_1 CTU_0 FlexRay_0                   | I/O<br>—<br>I/O<br>O      | Slow    | Medium              | 3       | 3       |

| D[2]        | PCR[50]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[50]  — ETC[3]  X[3]  CB_RX               | SIUL — eTimer_1 FlexPWM_0 FlexRay_0               | I/O<br><br>I/O<br>I/O     | Slow    | Medium              | 97      | 140     |

| D[3]        | PCR[51]                         | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[51]<br>CB_TX<br>ETC[4]<br>A[3]           | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0        | I/O<br>O<br>I/O<br>O      | Slow    | Symmetric           | 89      | 128     |

| D[4]        | PCR[52]                         | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[52]<br>CB_TR_EN<br>ETC[5]<br>B[3]        | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0        | I/O<br>O<br>I/O<br>O      | Slow    | Symmetric           | 90      | 129     |

**577**

Table 7. Pin muxing (continued)

| Port  | Pad                          | Alternate                         |                                        |                                   | I/O              | Pad sp  | peed <sup>(5)</sup> |         | No.     |

|-------|------------------------------|-----------------------------------|----------------------------------------|-----------------------------------|------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup> (2)      | Functions                              | Peripheral <sup>(3)</sup>         | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| E[5]  | PCR[69]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[69]<br>—<br>—<br>—<br>AN[8]       | SIUL<br>—<br>—<br>—<br>ADC_0      | Input only       | _       | _                   | _       | 44      |

| E[6]  | PCR[70]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[70]<br>—<br>—<br>—<br>—<br>AN[9]  | SIUL<br>—<br>—<br>—<br>ADC_0      | Input only       | _       | _                   | _       | 46      |

| E[7]  | PCR[71]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[71]  AN[10]                       | SIUL<br>—<br>—<br>—<br>—<br>ADC_0 | Input only       | _       | _                   | _       | 48      |

| E[8]  | PCR[72]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[72]<br>—<br>—<br>—<br>—<br>AN[6]  | SIUL  ADC_1                       | Input only       |         | _                   | _       | 59      |

| E[9]  | PCR[73]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[73]  AN[7]                        | SIUL  ADC_1                       | Input only       | _       | _                   | _       | 61      |

| E[10] | PCR[74]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[74]<br>—<br>—<br>—<br>—<br>AN[8]  | SIUL<br>—<br>—<br>—<br>ADC_1      | Input only       | _       | _                   | _       | 63      |

| E[11] | PCR[75]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[75]<br>—<br>—<br>—<br>—<br>AN[9]  | SIUL<br>—<br>—<br>—<br>ADC_1      | Input only       | _       | _                   | _       | 65      |

| E[12] | PCR[76]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[76]<br>—<br>—<br>—<br>—<br>AN[10] | SIUL<br>—<br>—<br>—<br>ADC_1      | Input only       | _       | _                   | _       | 67      |

| Symbol                                 |     | Dozomotov                  | Conditions                | Val | ue                 | llmit |  |

|----------------------------------------|-----|----------------------------|---------------------------|-----|--------------------|-------|--|

| Symbol                                 |     | Parameter                  | Conditions                | Min | Max <sup>(1)</sup> | Unit  |  |

| V <sub>SS_LV_CORx</sub> <sup>(4)</sup> | SR  | Internal reference voltage | _                         | 0   | 0                  | V     |  |

| т.                                     | SR  | Ambient temperature under  | f <sub>CPU</sub> = 64 MHz | -40 | 105                | - °C  |  |

| 'A                                     | J.K | bias                       | f <sub>CPU</sub> = 60 MHz | -40 | 125                | ] ~   |  |

Table 11. Recommended operating conditions (3.3 V) (continued)

- Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

- 2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD\_HV\_IOy} V_{DD\_HV\_IOx}| < 100$  mV.

- The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_ADC1</sub> V<sub>DD\_HV\_ADC0</sub>| < 100 mV. As long as that condition is met, ADC\_0 and ADC\_1 can be operated at 5 V with the rest of the device operating at 3.3 V.</li>

- 4. To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast

- 5. The low voltage supplies ( $V_{DD\_LV\_xxx}$ ) are not all independent.

- $V_{DD\_LV\_COR1}$  and  $V_{DD\_LV\_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly,  $V_{SS\_LV\_COR1}$  and  $V_{SS\_LV\_COR2}$  are internally shorted.

$V_{DD\_LV\_REGCOR} \text{ and } V_{DD\_LV\_REGCORx} \text{ are physically shorted internally, as are } V_{SS\_LV\_REGCOR} \text{ and } V_{SS\_LV\_CORx}.$

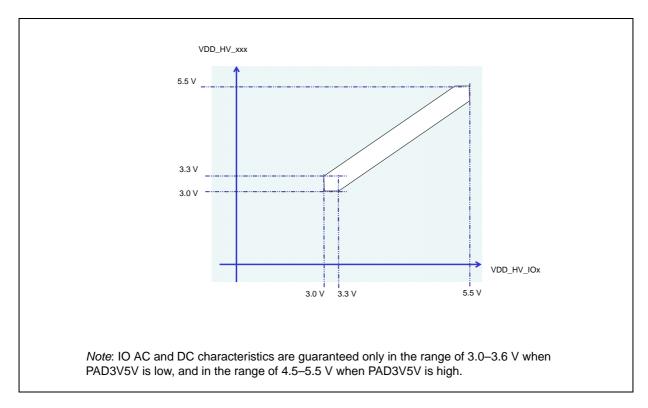

*Figure 7* shows the constraints of the different power supplies.

Figure 7. Power supplies constraints (3.0 V  $\leq$  V<sub>DD HV IOx</sub>  $\leq$  5.5 V)

- 1. C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 3.6 Electromagnetic interference (EMI) characteristics

Table 14. EMI testing specifications

| Symbol           | Parameter | Conditions                                                                                                               | Clocks                                                    | Frequency       | Level<br>(Max) | Unit |

|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|----------------|------|

|                  |           |                                                                                                                          | f <sub>OSC</sub> 8 MHz                                    | 150 kHz-150 MHz | 16             | dBuV |

|                  |           | conditions and EM testing per standard IEC61967-2 diated emissions  Supply voltage = 5 V DC  Ambient temperature = 25 °C | f <sub>CPU</sub> 64 MHz<br>No PLL frequency<br>modulation | 150–1000 MHz    | 15             | αυμν |

| V                |           |                                                                                                                          |                                                           | IEC Level       | М              | _    |

| V <sub>EME</sub> |           |                                                                                                                          | f <sub>OSC</sub> 8 MHz                                    | 150 kHz-150 MHz | 15             | dBuV |

|                  |           |                                                                                                                          | f <sub>CPU</sub> 64 MHz                                   | 150–1000 MHz    | 14             | чъμν |

|                  |           | Worst-case orientation                                                                                                   | 1% PLL frequency modulation                               | IEC Level       | М              | _    |

# 3.7 Electrostatic discharge (ESD) characteristics

Table 15. ESD ratings<sup>(1),(2)</sup>

| Symbol                |        | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|--------|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | S<br>R | Electrostatic discharge (Human Body Model)     | _          | 2000          | ٧    |

| V                     | S      | Electrostatic discharge (Charged Device Model) |            | 750 (corners) | V    |

| V <sub>ESD(CDM)</sub> | R      | Electrostatic discharge (Charged Device Model) | _          | 500 (other)   | V    |

- 1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

- 2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# 3.8 Power management electrical characteristics

### 3.8.1 Voltage regulator electrical characteristics

The internal voltage regulator requires an external NPN ballast to be connected as shown in Figure 9. Table 16 contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the  $V_{DD\ HV\ REG}$ , BCTRL and  $V_{DD\ LV\ CORx}$  pins to less than

| Symbol                  | С      |                | Parameter                                                                              | Conditions                                         |                                                    | Va     | lue   | Unit |  |

|-------------------------|--------|----------------|----------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--------|-------|------|--|

| Symbol                  |        |                | raiailletei                                                                            | Conditions                                         |                                                    | Тур    | Max   | Onic |  |

|                         |        |                | RUN—Maximum mode <sup>(1)</sup>                                                        |                                                    | 40 MHz                                             | 62     | 77    |      |  |

|                         | Т      |                | NON—Waximum mode                                                                       | V <sub>DD_LV_CORx</sub> 64 MHz                     | 71                                                 | 88     |       |      |  |

|                         |        |                | RUN—Typical mode <sup>(2)</sup>                                                        | externally forced at 1.3 V                         | 40 MHz                                             | 45     | 56    |      |  |

|                         |        |                | KON—Typicai mode                                                                       |                                                    | 64 MHz                                             | 52     | 65    |      |  |

| I <sub>DD_LV_CORx</sub> | x<br>P | Р              |                                                                                        | RUN—Maximum mode <sup>(3)</sup>                    | V <sub>DD_LV_CORx</sub> externally forced at 1.3 V | 64 MHz | 60    | 75   |  |

|                         |        |                | ent                                                                                    | HALT mode <sup>(4)</sup>                           | V <sub>DD_LV_CORx</sub> externally forced at 1.3 V | _      | 1.5   | 10   |  |

|                         |        | Supply current | STOP mode <sup>(5)</sup>                                                               | V <sub>DD_LV_CORx</sub> externally forced at 1.3 V | _                                                  | 1      | 10    | mA   |  |

|                         |        | Sup            | Flash during read                                                                      | V <sub>DD_HV_FL</sub> at 5.0 V                     | _                                                  | 10     | 12    |      |  |

| I <sub>DD_FLASH</sub>   | Т      |                | Flash during erase operation on 1 flash module                                         | V <sub>DD_HV_FL</sub> at 5.0 V                     | _                                                  | 15     | 19    |      |  |

|                         |        |                | ADC—Maximum mode <sup>(1)</sup>                                                        |                                                    | ADC_1                                              | 3.5    | 5     |      |  |

| l                       | Т      |                | MDC—Maximum mode.                                                                      | V <sub>DD_HV_ADC0</sub> at 5.0 V                   | ADC_0                                              | 3      | 4     |      |  |

| I <sub>DD_ADC</sub>     | ļ '    |                | ADC—Typical mode <sup>(2)</sup> $V_{DD\_HV\_ADC1}$ at 5.0 V $f_{ADC} = 16 \text{ MHz}$ | ADC_1                                              | 0.8                                                | 1      |       |      |  |

|                         |        |                | Typical mode.                                                                          |                                                    | ADC_0                                              | 0.005  | 0.006 |      |  |

| I <sub>DD_OSC</sub>     | Т      |                | Oscillator                                                                             | V <sub>DD_OSC</sub> at 5.0 V                       | 8 MHz                                              | 2.6    | 3.2   |      |  |

Table 22. Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)

## 3.10.3 DC electrical characteristics (3.3 V)

*Table 23* gives the DC electrical characteristics at 3.3 V (3.0 V < V<sub>DD\_HV\_IOX</sub> < 3.6 V, NVUSRO[PAD3V5V] = 1); see *Figure 14*.

Table 23. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)<sup>(1)</sup>

| Symbol          | _ | Parameter               | Conditions | Va                  | alue                        | Unit  |

|-----------------|---|-------------------------|------------|---------------------|-----------------------------|-------|

| Symbol          |   | raiametei               | Conditions | Min                 | Max                         | Offic |

| V               | D | Low level input voltage | _          | -0.1 <sup>(2)</sup> | _                           | V     |

| V <sub>IL</sub> | Р | Low level input voltage | _          | _                   | 0.35 V <sub>DD_HV_IOx</sub> | V     |

Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

<sup>2.</sup> Typical mode configurations: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

<sup>3.</sup> Code fetched from RAM, PLL\_0: 64 MHz system clock (x4 multiplier with 16 MHz XTAL), PLL\_1 is ON at PHI\_div2 = 120 MHz and PHI\_div3 = 80 MHz, auxiliary clock sources set that all peripherals receive maximum frequency, all peripherals enabled.

<sup>4.</sup> Halt mode configurations: code fetched from RAM, code and data flash memories in low power mode, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

<sup>5.</sup> STOP "P" mode Device Under Test (DUT) configuration: code fetched from RAM, code and data flash memories OFF, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

Table 26. I/O weight (continued)

| Ded      | LQ        | FP144       | LQI       | FP100       |

|----------|-----------|-------------|-----------|-------------|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |

| PAD[60]  | 11%       | 10%         | 11%       | 10%         |

| PAD[100] | 12%       | 10%         | _         | _           |

| PAD[45]  | 12%       | 10%         | 12%       | 10%         |

| PAD[98]  | 12%       | 11%         | _         | _           |

| PAD[46]  | 12%       | 11%         | 12%       | 11%         |

| PAD[99]  | 13%       | 11%         | _         | _           |

| PAD[62]  | 13%       | 11%         | 13%       | 11%         |

| PAD[92]  | 13%       | 12%         | _         | _           |

| VPP_TEST | 1%        | 1%          | 1%        | 1%          |

| PAD[4]   | 14%       | 12%         | 14%       | 12%         |

| PAD[16]  | 13%       | 12%         | 13%       | 12%         |

| PAD[17]  | 13%       | 11%         | 13%       | 11%         |

| PAD[42]  | 13%       | 11%         | 13%       | 11%         |

| PAD[93]  | 12%       | 11%         | _         | _           |

| PAD[95]  | 12%       | 11%         | _         | _           |

| PAD[18]  | 12%       | 10%         | 12%       | 10%         |

| PAD[94]  | 11%       | 10%         | _         | _           |

| PAD[19]  | 11%       | 10%         | 11%       | 10%         |

| PAD[77]  | 10%       | 9%          | _         | _           |

| PAD[10]  | 10%       | 9%          | 10%       | 9%          |

| PAD[78]  | 9%        | 8%          | _         | _           |

| PAD[11]  | 9%        | 8%          | 9%        | 8%          |

| PAD[79]  | 8%        | 7%          | _         | _           |

| PAD[12]  | 7%        | 7%          | 7%        | 7%          |

| PAD[41]  | 7%        | 6%          | 7%        | 6%          |

| PAD[47]  | 5%        | 4%          | 5%        | 4%          |

| PAD[48]  | 4%        | 4%          | 4%        | 4%          |

| PAD[51]  | 4%        | 4%          | 4%        | 4%          |

| PAD[52]  | 5%        | 4%          | 5%        | 4%          |

| PAD[40]  | 5%        | 5%          | 6%        | 5%          |

| PAD[80]  | 9%        | 8%          | _         | _           |

| PAD[9]   | 10%       | 9%          | 11%       | 10%         |

| PAD[81]  | 10%       | 9%          | _         | _           |

Table 26. I/O weight (continued)

| Pad     | LQ        | FP144       | LQFP100   |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[13] | 10%       | 9%          | 12%       | 11%         |  |

| PAD[82] | 10%       | 9%          | _         | _           |  |

| PAD[22] | 10%       | 9%          | 13%       | 12%         |  |

| PAD[83] | 10%       | 9%          | _         | _           |  |

| PAD[50] | 10%       | 9%          | 14%       | 12%         |  |

| PAD[97] | 10%       | 9%          | _         | _           |  |

| PAD[38] | 10%       | 9%          | 14%       | 13%         |  |

| PAD[14] | 9%        | 8%          | 14%       | 13%         |  |

| PAD[15] | 9%        | 8%          | 15%       | 13%         |  |

Table 27. I/O consumption

| Symbol                                  |                                | С             | Dorometer                                         | Conditions <sup>(1)</sup>                     |                                                   | Parameter Conditions <sup>(1)</sup> |                               | Value                                             |    | Unit                         |                        |                                                   |                                                   |   |     |    |    |

|-----------------------------------------|--------------------------------|---------------|---------------------------------------------------|-----------------------------------------------|---------------------------------------------------|-------------------------------------|-------------------------------|---------------------------------------------------|----|------------------------------|------------------------|---------------------------------------------------|---------------------------------------------------|---|-----|----|----|

| Symbol                                  |                                | د             | Parameter                                         | Min                                           |                                                   |                                     |                               | Unit                                              |    |                              |                        |                                                   |                                                   |   |     |    |    |

| (2)                                     | 00 1                           | 00            |                                                   |                                               |                                                   |                                     |                               |                                                   |    |                              | Dynamic I/O current    | C - 25 pE                                         | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _ | _   | 20 | mΛ |

| I <sub>SWTSLW</sub> <sup>(2)</sup>      |                                |               | for SLOW configuration                            | C <sub>L</sub> = 25 pF                        | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _                                   | _                             | 16                                                | mA |                              |                        |                                                   |                                                   |   |     |    |    |

| (2)                                     | CC                             |               | Dynamic I/O current for MEDIUM                    | C <sub>1</sub> = 25 pF                        | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                   | _                             | 29                                                | mA |                              |                        |                                                   |                                                   |   |     |    |    |

| OVVIIVLED                               | configuration                  |               | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _                                             | _                                                 | 17                                  | IIIA                          |                                                   |    |                              |                        |                                                   |                                                   |   |     |    |    |

| (2)                                     | (2)                            |               | CC                                                | CC                                            | CC                                                |                                     |                               |                                                   |    | Dynamic I/O current for FAST | C <sub>I</sub> = 25 pF | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                                 | _ | 110 | mA |    |

| I <sub>SWTFST</sub> <sup>(2)</sup> CC D |                                | configuration |                                                   | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                                                 | _                                   | 50                            | IIIA                                              |    |                              |                        |                                                   |                                                   |   |     |    |    |

|                                         |                                |               |                                                   | C <sub>L</sub> = 25 pF, 2 MHz                 |                                                   | _                                   | _                             | 2.3                                               |    |                              |                        |                                                   |                                                   |   |     |    |    |

| I <sub>RMSSLW</sub> CC                  | 00 [                           |               |                                                   | C <sub>L</sub> = 25 pF, 4 MHz                 | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                   | _                             | 3.2                                               |    |                              |                        |                                                   |                                                   |   |     |    |    |

|                                         |                                |               | Root medium square I/O current for SLOW           | C <sub>L</sub> = 100 pF, 2 MHz                |                                                   | _                                   | _                             | 6.6                                               | mA |                              |                        |                                                   |                                                   |   |     |    |    |

|                                         |                                |               | configuration                                     | C <sub>L</sub> = 25 pF, 2 MHz                 |                                                   |                                     | _                             | 1.6                                               |    |                              |                        |                                                   |                                                   |   |     |    |    |

|                                         |                                |               |                                                   |                                               |                                                   |                                     | C <sub>L</sub> = 25 pF, 4 MHz | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _  | _                            | 2.3                    |                                                   |                                                   |   |     |    |    |

|                                         | C <sub>L</sub> = 100 pF, 2 MHz |               |                                                   | _                                             | _                                                 | 4.7                                 |                               |                                                   |    |                              |                        |                                                   |                                                   |   |     |    |    |

Table 27. I/O consumption (continued)

| Symbol              |                                                              | С | Parameter                                     | Condit                                            | Value                                             |                                |                                                   | Unit |      |     |  |

|---------------------|--------------------------------------------------------------|---|-----------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------------|---------------------------------------------------|------|------|-----|--|

|                     |                                                              | C | Farameter                                     | Condit                                            | Min                                               | Тур                            | Max                                               | Onit |      |     |  |

|                     |                                                              |   |                                               |                                                   |                                                   | C <sub>L</sub> = 25 pF, 13 MHz |                                                   | _    | _    | 6.6 |  |

|                     |                                                              |   | Root medium square I/O current for MEDIUM     | C <sub>L</sub> = 25 pF, 40 MHz                    | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                              | _                                                 | 13.4 | - mA |     |  |

|                     | СС                                                           |   |                                               | C <sub>L</sub> = 100 pF, 13 MHz                   |                                                   | _                              | _                                                 | 18.3 |      |     |  |

| IRMSMED             | CC                                                           |   |                                               | C <sub>L</sub> = 25 pF, 13 MHz                    |                                                   | _                              |                                                   | 5    |      |     |  |

|                     |                                                              |   |                                               |                                                   | configuration                                     | C <sub>L</sub> = 25 pF, 40 MHz | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _    | _    | 8.5 |  |

|                     |                                                              |   |                                               | C <sub>L</sub> = 100 pF, 13 MHz                   |                                                   | _                              | _                                                 | 11   | 1    |     |  |

|                     | I <sub>RMSFST</sub> CC I                                     |   |                                               | C <sub>L</sub> = 25 pF, 40 MHz                    | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0     | _                              | _                                                 | 22   |      |     |  |

|                     |                                                              |   |                                               | C <sub>L</sub> = 25 pF, 64 MHz                    |                                                   | _                              | _                                                 | 33   |      |     |  |

|                     |                                                              |   | D II/O current for FAST                       | C <sub>L</sub> = 100 pF, 40 MHz                   |                                                   | _                              | _                                                 | 56   | ^    |     |  |

| IRMSFST             |                                                              |   |                                               | C <sub>L</sub> = 25 pF, 40 MHz                    |                                                   | _                              | _                                                 | 14   | mA   |     |  |

|                     |                                                              |   | C <sub>L</sub> = 25 pF, 64 MHz                | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _                                                 | _                              | 20                                                | ]    |      |     |  |

|                     |                                                              |   |                                               | C <sub>L</sub> = 100 pF, 40 MHz                   | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,           | _                              | _                                                 | 35   |      |     |  |

|                     |                                                              |   | Sum of all the static                         | / <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0        |                                                   | _                              | _                                                 | 70   |      |     |  |

| I <sub>AVGSEG</sub> | I <sub>AVGSEG</sub> SR D I/O current within a supply segment |   | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ P/}$ | AD3V5V = 1                                        | _                                                 | _                              | 65                                                | mA   |      |     |  |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified

## 3.11 Main oscillator electrical characteristics

The SPC560P44Lx, SPC560P50Lx provides an oscillator/resonator driver.

Table 28. Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol           |        | С | Parameter                               | Va  | l lmit |      |

|------------------|--------|---|-----------------------------------------|-----|--------|------|

| Syli             | Symbol |   | Parameter                               | Min | Max    | Unit |

| fosc             | SR     | _ | Oscillator frequency                    | 4   | 40     | MHz  |

| 9 <sub>m</sub>   | _      | Р | Transconduc tance                       | 6.5 | 25     | mA/V |

| V <sub>OSC</sub> | _      | Т | Oscillation<br>amplitude on<br>XTAL pin | 1   | _      | V    |

| toscsu           | _      | Т | Start-up time <sup>(1),(2)</sup>        | 8   | _      | ms   |

The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

<sup>2.</sup> Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

<sup>2.</sup> Value captured when amplitude reaches 90% of XTAL

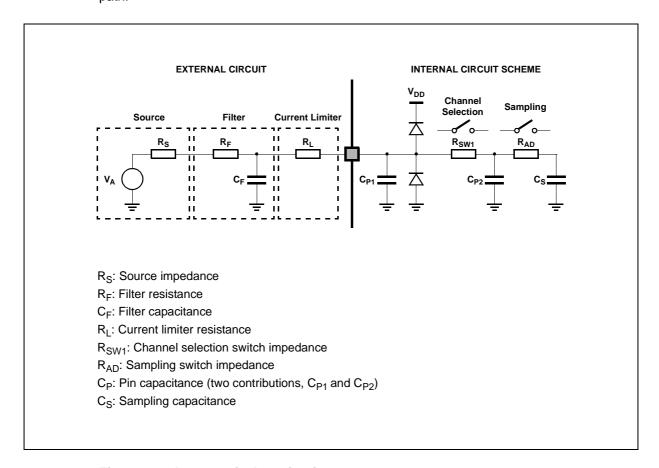

The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{P2}$  being substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S + C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1$  / (fc × ( $C_S + C_{P2}$ )), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S + C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the *Equation 4*:

#### **Equation 4**

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

*Equation 4* generates a constraint for external network design, in particular on resistive path.

Figure 16. Input equivalent circuit

#### **Equation 7**

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

A second charge transfer involves also C<sub>F</sub> (that is typically bigger than the on-chip capacitance) through the resistance R<sub>L</sub>: again considering the worst case in which C<sub>P2</sub> and C<sub>S</sub> were in parallel to C<sub>P1</sub> (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2 < R_L \cdot (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_I$  sizing is obtained:

#### **Equation 9**

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

#### **Equation 10**

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

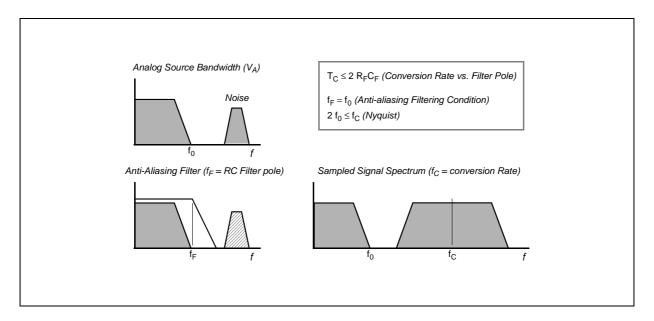

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time  $(T_S)$ . The filter is typically designed to act as anti-aliasing.

Figure 18. Spectral representation of input signal

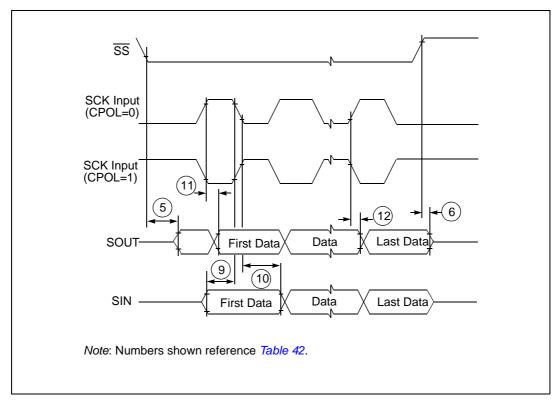

Figure 32. DSPI classic SPI timing – Slave, CPHA = 1

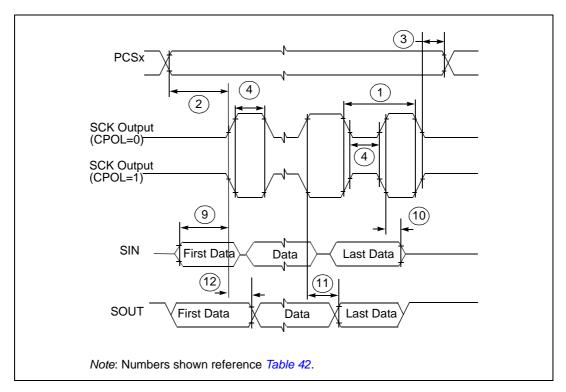

Figure 33. DSPI modified transfer format timing – Master, CPHA = 0

Table 44. LQFP100 package mechanical data

|                    | Dimensions |        |        |                       |        |        |  |  |  |

|--------------------|------------|--------|--------|-----------------------|--------|--------|--|--|--|

| Symbol             |            | mm     |        | inches <sup>(1)</sup> |        |        |  |  |  |

|                    | Min        | Тур    | Max    | Min                   | Тур    | Max    |  |  |  |

| А                  | _          | _      | 1.600  | _                     | _      | 0.0630 |  |  |  |

| A1                 | 0.050      | _      | 0.150  | 0.0020                | _      | 0.0059 |  |  |  |

| A2                 | 1.350      | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |  |

| b                  | 0.170      | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |  |

| С                  | 0.090      | _      | 0.200  | 0.0035                | _      | 0.0079 |  |  |  |

| D                  | 15.800     | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |

| D1                 | 13.800     | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |  |

| D3                 | _          | 12.000 | _      | _                     | 0.4724 | _      |  |  |  |

| Е                  | 15.800     | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |

| E1                 | 13.800     | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |  |

| E3                 | _          | 12.000 | _      | _                     | 0.4724 | _      |  |  |  |

| е                  | _          | 0.500  | _      | _                     | 0.0197 | _      |  |  |  |

| L                  | 0.450      | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |  |

| L1                 | _          | 1.000  | _      | _                     | 0.0394 | _      |  |  |  |

| k                  | 0.0°       | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |  |  |

| ccc <sup>(2)</sup> |            | 0.08   |        |                       | 0.0031 |        |  |  |  |

<sup>1.</sup> Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

<sup>2.</sup> Tolerance

107/112

# 6 Revision history

Table 46 summarizes revisions to this document.

Table 46. Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 28-Aug-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 25-Nov-2008 | 2        | Table 7: TDO and TDI pins (Port pins B[4:5] are single function pins.  Table 12, Table 13: Thermal characteristics added.  Table 11, Table 12: EMI testing specifications split into separate tables for Normal mode and Airbag mode; data to be added in a later revision.  Table 16, Table 17, Table 19, Table 20: Supply current specifications split into separate tables for Normal mode and Airbag mode; data to be added in a later revision.  Table 23:  Values for I <sub>OL</sub> and I <sub>OH</sub> (in Conditions column) changed.  Max values for V <sub>OH_S</sub> , V <sub>OH_M</sub> , V <sub>OH_F</sub> and V <sub>OH_SYM</sub> deleted.  V <sub>ILR</sub> max value changed.  I <sub>PUR</sub> min and max values changed.  Table 27: Sensitivity value changed.  Table 30: Most values in table changed. |  |  |  |

| 05-Mar-2009 | 3        | <ul> <li>Description of system requirements, controller characteristics and how controller characteristics are guaranteed updated.</li> <li>Electrical parameters updated.</li> <li>EMI characteristics are now in one table; values have been updated.</li> <li>ESD characteristics are now in one table.</li> <li>Electrical parameters are identified as either system requirements or controller characteristics. Method used to guarantee each controller characteristic is noted in table.</li> <li>AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing, and DSPI Timing sections deleted</li> </ul>                                                                                                                                                                                             |  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com