#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 67                                                                       |

| Program Memory Size        | 384KB (384K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64К х 8                                                                  |

| RAM Size                   | 36K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p44l3cefar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

## 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

## 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P44Lx, SPC560P50Lx:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module can run on an independent clock source

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

The SIU provides the following features:

- Centralized general purpose input output (GPIO) control of as many as 80 input/output pins and 26 analog input-only pads (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins (except ADC channels) can be alternatively configured as both general purpose input or output pins

- ADC channels support alternative configuration as general purpose inputs

- Direct readback of the pin value is supported on all pins through the SIUL

- Configurable digital input filter that can be applied to some general purpose input pins for noise elimination: as many as 4 internal functions can be multiplexed onto 1 pin

### 1.5.17 Boot and censorship

Different booting modes are available in the SPC560P44Lx, SPC560P50Lx: booting from internal flash memory and booting via a serial link.

The default booting scheme uses the internal flash memory (an internal pull-down is used to select this mode). Optionally, the user can boot via FlexCAN or LINFlex (using the boot assist module software).

A censorship scheme is provided to protect the content of the flash memory and offer increased security for the entire device.

A password mechanism is designed to grant the legitimate user access to the non-volatile memory.

#### Boot assist module (BAM)

The BAM is a block of read-only one-time programmed memory and is identical for all SPC560Pxx devices that are based on the e200z0h core. The BAM program is executed every time the device is powered on if the alternate boot mode has been selected by the user.

The BAM provides the following features:

- Serial bootloading via FlexCAN or LINFlex

- Ability to accept a password via the used serial communication channel to grant the legitimate user access to the non-volatile memory

### 1.5.18 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC560P44Lx, SPC560P50Lx.

## 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

# 1.5.23 Serial communication interface module (LINFlex)

The LINFlex (local interconnect network flexible) on the SPC560P44Lx, SPC560P50Lx features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and as much as 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors (sync field, delimiter, ID parity, bit framing, checksum, and time-out)

- Classic or extended checksum calculation

- Configurable Break duration as long as 36-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit or 9-bit words)

- Error detection and flagging

- Parity, Noise and Framing errors

- Interrupt-driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal busses to provide development support as per the IEEE-ISTO 5001-2003 Class 2+ standard. The development support provided includes access to the MCU's internal memory map and access to the processor's internal registers during run time.

The Nexus Interface provides the following features:

- Configured via the IEEE 1149.1

- All Nexus port pins operate at V<sub>DDIO</sub> (no dedicated power supply)

- Nexus 2+ features supported

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or keep executing and allow overwrite of information

- Watchpoint triggering, watchpoint triggers program tracing

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin

## 1.5.30 Cyclic redundancy check (CRC)

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC module features:

- Support for CRC-16-CCITT (*x*25 protocol):

- $x^{16} + x^{12} + x^5 + 1$

- Support for CRC-32 (Ethernet protocol):

- $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

## 1.5.31 IEEE 1149.1 JTAG controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

| Symbol   | Description                                                                  | Direction        | Pad sp      | beed <sup>(1)</sup> | Pin     |         |

|----------|------------------------------------------------------------------------------|------------------|-------------|---------------------|---------|---------|

| Symbol   | Description                                                                  | Direction        | SRC = 0     | SRC = 1             | 100-pin | 144-pin |

| TMS      | JTAG state machine control                                                   | Bidirectional    | Slow        | Fast                | 59      | 87      |

| тск      | JTAG clock                                                                   | Input only       | Slow        | —                   | 60      | 88      |

| TDI      | Test Data In                                                                 | Input only       | Slow        | Medium              | 58      | 86      |

| TDO      | Test Data Out                                                                | Output only      | Slow        | Fast                | 61      | 89      |

|          | Reset pin, available on                                                      | 100-pin and 144- | pin packag  | e.                  |         |         |

| RESET    | Bidirectional reset with Schmitt trigger<br>characteristics and noise filter | Bidirectional    | Medium      | —                   | 20      | 31      |

|          | Test pin, available on 1                                                     | 00-pin and 144-p | oin package | ).                  |         |         |

| VPP_TEST | Pin for testing purpose only. To be tied to ground in normal operating mode. | _                | _           | _                   | 74      | 107     |

#### Table 6. System pins (continued)

1. SCR values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

## 2.2.3 Pin muxing

Table 7 defines the pin list and muxing for the SPC560P44Lx, SPC560P50Lx devices.

Each row of *Table 7* shows all the possible ways of configuring each pin, via alternate functions. The default function assigned to each pin after reset is the ALTO function.

SPC560P44Lx, SPC560P50Lx devices provide four main I/O pad types, depending on the associated functions:

- *Slow pads* are the most common, providing a compromise between transition time and low electromagnetic emission.

- *Medium pads* provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- *Fast pads* provide maximum speed. They are used for improved NEXUS debugging capability.

- Symmetric pads are designed to meet FlexRay requirements.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance. For more information, see the datasheet's "Pad AC Specifications" section.

| Port  | Pad                          | Alternate                         |                                         |                                             | I/O                       | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|-----------------------------------|-----------------------------------------|---------------------------------------------|---------------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions                               | Peripheral <sup>(3)</sup>                   | direction<br>(4)          | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| D[5]  | PCR[53]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[53]<br>CS3<br>F[0]<br>SOUT         | SIUL<br>DSPI_0<br>FCU_0<br>DSPI_3           | I/O<br>O<br>O             | Slow    | Medium              | 22      | 33      |

| D[6]  | PCR[54]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[54]<br>CS2<br>SCK<br>—<br>FAULT[1] | SIUL<br>DSPI_0<br>DSPI_3<br>—<br>FlexPWM_0  | I/O<br>O<br>I/O<br>—<br>I | Slow    | Medium              | 23      | 34      |

| D[7]  | PCR[55]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[55]<br>CS3<br>F[1]<br>CS4<br>SIN   | SIUL<br>DSPI_1<br>FCU_0<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>O<br>I        | Slow    | Medium              | 26      | 37      |

| D[8]  | PCR[56]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[56]<br>CS2<br>—<br>CS5<br>FAULT[3] | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>FlexPWM_0  | I/O<br>O<br>—<br>O<br>I   | Slow    | Medium              | 21      | 32      |

| D[9]  | PCR[57]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>X[0]<br>TXD<br>—            | SIUL<br>FlexPWM_0<br>LIN_1<br>—             | I/O<br>I/O<br>O<br>—      | Slow    | Medium              | 15      | 26      |

| D[10] | PCR[58]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>A[0]<br>CS0<br>—            | SIUL<br>FlexPWM_0<br>DSPI_3<br>—            | I/O<br>O<br>I/O<br>—      | Slow    | Medium              | 53      | 76      |

| D[11] | PCR[59]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>CS1<br>SCK          | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>I/O      | Slow    | Medium              | 54      | 78      |

| D[12] | PCR[60]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD            | SIUL<br>FlexPWM_0<br>—<br>LIN_1             | I/O<br>I/O<br>—<br>I      | Slow    | Medium              | 70      | 99      |

| D[13] | PCR[61]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>CS2<br>SOUT         | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>O        | Slow    | Medium              | 67      | 95      |

# Table 7. Pin muxing (continued)

| Port  | Pad                          | Alternate                         |                                        |                             | I/O                | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|-----------------------------------|----------------------------------------|-----------------------------|--------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions                              | Peripheral <sup>(3)</sup>   | direction<br>(4)   | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| F[14] | PCR[94]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[94]<br>TXD<br>—<br>—              | SIUL<br>LIN_1<br>—          | V0 0               | Slow    | Medium              | _       | 115     |

| F[15] | PCR[95]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[95]<br>—<br>—<br>RXD              | SIUL<br>—<br>—<br>LIN_1     | I/O<br>     <br>   | Slow    | Medium              |         | 113     |

|       |                              |                                   |                                        | Port G (12-bit)             |                    |         |                     |         |         |

| G[0]  | PCR[96]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[96]<br>F[0]<br>—<br>EIRQ[30]      | SIUL<br>FCU_0<br>—<br>SIUL  | I/O<br>O<br>—<br>I | Slow    | Medium              |         | 38      |

| G[1]  | PCR[97]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[97]<br>F[1]<br>—<br>—<br>EIRQ[31] | SIUL<br>FCU_0<br>—<br>SIUL  | I/O<br>O<br>—<br>I | Slow    | Medium              |         | 141     |

| G[2]  | PCR[98]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[98]<br>X[2]<br>—                  | SIUL<br>FlexPWM_0<br>—<br>— | I/O<br>I/O<br>—    | Slow    | Medium              |         | 102     |

| G[3]  | PCR[99]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[99]<br>A[2]<br>—<br>—             | SIUL<br>FlexPWM_0<br>—      | I/O<br>O<br>—      | Slow    | Medium              | _       | 104     |

| G[4]  | PCR[100]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[100]<br>B[2]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—      | I/O<br>O<br>—      | Slow    | Medium              | _       | 100     |

| G[5]  | PCR[101]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[101]<br>X[3]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—      | I/O<br>I/O<br>—    | Slow    | Medium              | _       | 85      |

| G[6]  | PCR[102]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[102]<br>A[3]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—<br>— | I/O<br>O<br>—      | Slow    | Medium              | _       | 98      |

# Table 7. Pin muxing (continued)

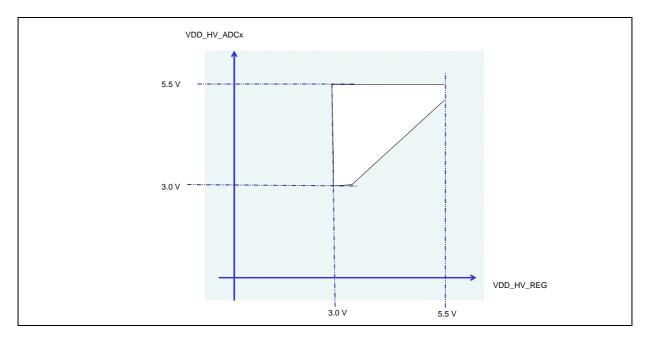

The SPC560P44Lx, SPC560P50Lx supply architecture allows the ADC supply to be managed independently from the standard  $V_{DD_HV}$  supply. *Figure 8* shows the constraints of the ADC power supply.

# 3.5 Thermal characteristics

## 3.5.1 Package thermal characteristics

|                     | ·····                                                    |                           |                  |          |

|---------------------|----------------------------------------------------------|---------------------------|------------------|----------|

| Symbol              | Parameter                                                | Conditions                | Typical<br>value | Unit     |

| D                   | Thermal resistance junction-to-ambient,                  | Single layer board—1s     | 54.2             | °C/<br>W |

| $R_{	hetaJA}$       | natural convection <sup>(1)</sup>                        | Four layer board—<br>2s2p | 44.4             | °C/<br>W |

| $R_{	hetaJB}$       | Thermal resistance junction-to-board <sup>(2)</sup>      | Four layer board—<br>2s2p | 29.9             | °C/<br>W |

| R <sub>θJCtop</sub> | Thermal resistance junction-to-case (top) <sup>(3)</sup> | Single layer board—1s     | 9.3              | °C/<br>W |

| $\Psi_{JB}$         | Junction-to-board, natural convection <sup>(4)</sup>     | Operating conditions      | 30.2             | °C/<br>W |

| $\Psi_{JC}$         | Junction-to-case, natural convection <sup>(5)</sup>      | Operating conditions      | 0.8              | °C/<br>W |

### Table 12. Thermal characteristics for 144-pin LQFP

Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

- C.E. Triplett and B. Joiner, An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 3.6 Electromagnetic interference (EMI) characteristics

| Symbol           | Parameter                   | Conditions                                        | Clocks                                      | Frequency       | Level<br>(Max) | Unit |

|------------------|-----------------------------|---------------------------------------------------|---------------------------------------------|-----------------|----------------|------|

|                  |                             | 1) ovice contiguration test                       | f <sub>OSC</sub> 8 MHz                      | 150 kHz–150 MHz | 16             | dBµV |

|                  |                             | and EM testing par                                | f <sub>CPU</sub> 64 MHz<br>No PLL frequency | 150–1000 MHz    | 15             | uυμν |

| V                | Radiated emissions          | standard IEC61067.2                               | modulation                                  | IEC Level       | М              | —    |

| V <sub>EME</sub> | Supply voltage = 5 V DC     | f <sub>OSC</sub> 8 MHz<br>f <sub>CPU</sub> 64 MHz | 150 kHz–150 MHz                             | 15              | dBµV           |      |

|                  | Ambient temperature = 25 °C |                                                   | 150–1000 MHz                                | 14              | ubµv           |      |

|                  |                             | Worst-case orientation                            | 1% PLL frequency modulation                 | IEC Level       | М              | —    |

#### Table 14. EMI testing specifications

# 3.7 Electrostatic discharge (ESD) characteristics

### Table 15.ESD ratings(1),(2)

| Symbol                                                                        |   | Parameter                                      | Conditions | Value         | Unit |

|-------------------------------------------------------------------------------|---|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub><br>S<br>R<br>Electrostatic discharge (Human Body Model) |   | _                                              | 2000       | V             |      |

|                                                                               | s | Electrostatic discharge (Charged Device Model) |            | 750 (corners) | v    |

| VESD(CDM)                                                                     | R | Electrostatic discharge (Charged Device Model) | _          | 500 (other)   | v    |

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# **3.8 Power management electrical characteristics**

## 3.8.1 Voltage regulator electrical characteristics

The internal voltage regulator requires an external NPN ballast to be connected as shown in *Figure 9. Table 16* contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the V<sub>DD HV REG</sub>, BCTRL and V<sub>DD LV CORx</sub> pins to less than

| Table 26. | I/O weight (continued) |

|-----------|------------------------|

|-----------|------------------------|

| D- 1     | LQ        | FP144       | LQI       | FP100       |

|----------|-----------|-------------|-----------|-------------|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |

| PAD[72]  | 1%        | 1%          | —         | _           |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |

| PAD[73]  | 1%        | 1%          | —         | _           |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |

| PAD[74]  | 1%        | 1%          | —         |             |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |

| PAD[75]  | 1%        | 1%          | —         | _           |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |

| PAD[76]  | 1%        | 1%          | —         | _           |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |

| PAD[107] | 20%       | 17%         | _         |             |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |

| PAD[106] | 18%       | 16%         | —         |             |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |

| PAD[105] | 16%       | 14%         | —         |             |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |

| PAD[104] | 14%       | 13%         | _         |             |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |

| PAD[103] | 12%       | 11%         | —         | _           |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |

| PAD[101] | 11%       | 9%          | —         | _           |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |

| TMS      | 1%        | 1%          | 1%        | 1%          |

| TCK      | 1%        | 1%          | 1%        | 1%          |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |

| PAD[102] | 11%       | 10%         | —         | —           |

## 3.14.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

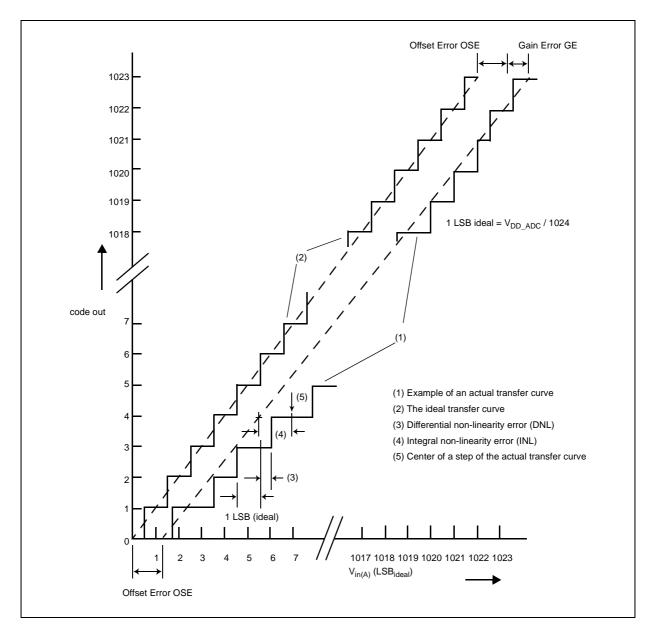

Figure 27. Nexus TDI, TMS, TDO timing

# 3.17.4 External interrupt timing (IRQ pin)

Table 41.External interrupt timing<sup>(1)</sup>

| No  | No. Symbol C      |    | C | Parameter                            | Conditions | Val                  | lue | Unit             |

|-----|-------------------|----|---|--------------------------------------|------------|----------------------|-----|------------------|

| NO. |                   |    |   |                                      | Conditions | Min                  | Мах | Onic             |

| 1   | t <sub>IPWL</sub> | CC | D | IRQ pulse width low                  | _          | 4                    | _   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | CC | D | IRQ pulse width high                 | _          | 4                    | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | CC | D | IRQ edge to edge time <sup>(2)</sup> | _          | 4 + N <sup>(3)</sup> |     | t <sub>CYC</sub> |

1. IRQ timing specified at  $f_{SYS}$  = 64 MHz and  $V_{DD_HV_IOx}$  = 3.0 V to 5.5 V,  $T_A = T_L$  to  $T_H$ , and  $C_L$  = 200 pF with SRC = 0b00.

2. Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

3. N = ISR time to clear the flag

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

IIn order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 4.2 Package mechanical data

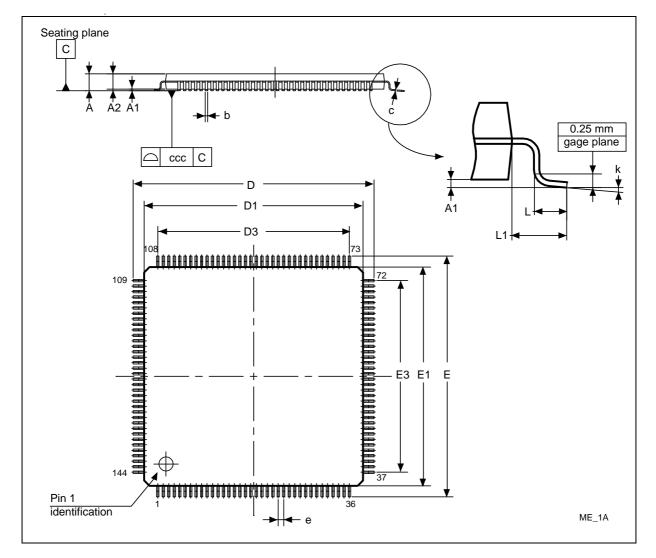

# 4.2.1 LQFP144 mechanical outline drawing

Figure 38. LQFP144 package mechanical drawing

Doc ID 14723 Rev 9

|                    |        | Dimensions |        |                       |        |        |  |  |  |  |

|--------------------|--------|------------|--------|-----------------------|--------|--------|--|--|--|--|

| Symbol             |        | mm         |        | inches <sup>(1)</sup> |        |        |  |  |  |  |

|                    | Min    | Тур        | Max    | Min                   | Тур    | Мах    |  |  |  |  |

| А                  | _      | —          | 1.600  | —                     | —      | 0.0630 |  |  |  |  |

| A1                 | 0.050  | —          | 0.150  | 0.0020                | _      | 0.0059 |  |  |  |  |

| A2                 | 1.350  | 1.400      | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |  |  |

| b                  | 0.170  | 0.220      | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |  |  |

| С                  | 0.090  | _          | 0.200  | 0.0035                | _      | 0.0079 |  |  |  |  |

| D                  | 21.800 | 22.000     | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |  |  |  |

| D1                 | 19.800 | 20.000     | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |  |  |  |

| D3                 | _      | 17.500     | _      | _                     | 0.6890 | _      |  |  |  |  |

| Е                  | 21.800 | 22.000     | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |  |  |  |

| E1                 | 19.800 | 20.000     | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |  |  |  |

| E3                 | _      | 17.500     | _      | _                     | 0.6890 | _      |  |  |  |  |

| е                  | —      | 0.500      | —      | —                     | 0.0197 | —      |  |  |  |  |

| L                  | 0.450  | 0.600      | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |  |  |

| L1                 | —      | 1.000      | —      | —                     | 0.0394 | —      |  |  |  |  |

| k                  | 0.0°   | 3.5°       | 7.0°   | 3.5°                  | 0.0°   | 7.0°   |  |  |  |  |

| ccc <sup>(2)</sup> |        | 0.080      | 1      |                       | 0.0031 |        |  |  |  |  |

### Table 43. LQFP144 mechanical data

1. Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

2. Tolerance

| able 44. L         |        | ige mechanica |        |                       |        |        |  |  |

|--------------------|--------|---------------|--------|-----------------------|--------|--------|--|--|

|                    |        |               | Dimer  | nsions                |        |        |  |  |

| Symbol             |        | mm            |        | inches <sup>(1)</sup> |        |        |  |  |

|                    | Min    | Тур           | Max    | Min                   | Тур    | Мах    |  |  |

| А                  | —      | —             | 1.600  | —                     | —      | 0.0630 |  |  |

| A1                 | 0.050  | —             | 0.150  | 0.0020                | _      | 0.0059 |  |  |

| A2                 | 1.350  | 1.400         | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b                  | 0.170  | 0.220         | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С                  | 0.090  | —             | 0.200  | 0.0035                | _      | 0.0079 |  |  |

| D                  | 15.800 | 16.000        | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1                 | 13.800 | 14.000        | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| D3                 | —      | 12.000        | —      | —                     | 0.4724 | —      |  |  |

| Е                  | 15.800 | 16.000        | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| E1                 | 13.800 | 14.000        | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3                 | —      | 12.000        | —      | —                     | 0.4724 | —      |  |  |

| е                  | _      | 0.500         | —      | —                     | 0.0197 | —      |  |  |

| L                  | 0.450  | 0.600         | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1                 | —      | 1.000         | —      | —                     | 0.0394 | —      |  |  |

| k                  | 0.0°   | 3.5°          | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |  |

| ccc <sup>(2)</sup> |        | 0.08          | •      | 0.0031                |        |        |  |  |

### Table 44. LQFP100 package mechanical data

1. Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

2. Tolerance

# Appendix A Abbreviations

Table 45 lists abbreviations used in this document.

| Abbreviation | Meaning                                 |  |  |

|--------------|-----------------------------------------|--|--|

| CMOS         | Complementary metal-oxide-semiconductor |  |  |

| СРНА         | Clock phase                             |  |  |

| CPOL         | Clock polarity                          |  |  |

| CS           | Peripheral chip select                  |  |  |

| DUT          | Device under test                       |  |  |

| ECC          | Error code correction                   |  |  |

| EVTO         | Event out                               |  |  |

| GPIO         | General purpose input/output            |  |  |

| MC           | Modulus counter                         |  |  |

| МСКО         | Message clock out                       |  |  |

| MCU          | Microcontroller unit                    |  |  |

| MDO          | Message data out                        |  |  |

| MSEO         | Message start/end out                   |  |  |

| MTFE         | Modified timing format enable           |  |  |

| NPN          | Negative-positive-negative              |  |  |

| NVUSRO       | Non-volatile user options register      |  |  |

| PTF          | Post trimming frequency                 |  |  |

| PWM          | Pulse width modulation                  |  |  |

| RBW          | Resolution bandwidth                    |  |  |

| SCK          | Serial communications clock             |  |  |

| SOUT         | Serial data out                         |  |  |

| ТСК          | Test clock input                        |  |  |

| TDI          | Test data input                         |  |  |

| TDO          | Test data output                        |  |  |

| TMS          | Test mode select                        |  |  |

Table 45.Abbreviations

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 07-Jul-2009 | 4        | Through all document:<br>Replaced all "RESET_B" occurrences with "RESET" through all document.<br>AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing, and DSPI<br>Timing sections inserted again.<br>Electrical parameters updated.<br>Section , Features:<br>Section , Features:<br>Section , Features:<br>Added row for Data Flash.<br>Table 2<br>Added a footnote regarding the decoupling capacitors.<br>Table 6<br>Removed the "other function" column.<br>Rearranged the contents.<br>Table 14<br>Updated definition of Condition column.<br>Table 19<br>merged in an unique Table the power consumption data related to "Maximum mode"<br>and "Airbag mode".<br>Table 29<br>Updated the parameter definition of $\Delta$ RCMVAR.<br>Removed the condition definition of $\Delta$ RCMVAR.<br>Removed Rave.<br>Table 29<br>Added t <sub>ADC_C</sub> and TUE rows.<br>Table 30<br>Added t <sub>ADC_C</sub> and TUE rows.<br>Removed Rave.<br>Table 33<br>Added.<br>Table 33<br>Added.<br>Table 29<br>Updated and added footnotes.<br>Section 3.16.1 RESET Pin Characteristics<br>Replaces whole section.<br>Table 38<br>Renamed the "Flash (KB)" heading column in "Code Flash / Data Flash (EE) (KB)"<br>Replaced the value of RAM from 32 to 36KB in the last four rows. |  |  |

# Table 46. Revision history (continued)

# Table 46. Revision history (continued)

| Date        | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 07-Apr-2011 | 7<br>(cont'd) | SPC560P44Lx, SPC560P50Lx device configuration differences: Removed "temperature"<br>rww (temperature information is provided in Order codes)<br>Updated SPC560P44Lx, SPC560P50Lx block diagram<br>Added SPC560P44Lx, SPC560P50Lx series block summary<br>Added Section 1.5 Feature details<br>Section 2.1, Package pinotts: removed alternate functions from pinout diagrams<br>Supply pins: updated descriptions of power supply pins (1.2 V)<br>System pins: updated table<br>Pin muxing: added rows "B[4]" and "B[5]<br>Section 3.3, Absolute maximum ratings: added voltage specifications to titles of <i>Figure 5</i><br>and <i>Figure 6</i> ; in <i>Table 9</i> , changed row "V <sub>SS_HV</sub> / Digital Ground" to "V <sub>SS</sub> / Device<br>Ground"; updated symbols<br>Section 3.4, Recommended operating conditions: added voltage specifications to titles of<br><i>Figure 7</i> and <i>Figure 8</i><br>Recommended operating conditions (5.0 V), and Recommended operating conditions<br>(3.3 V): changed row "V <sub>SS_HV</sub> / Digital Ground" to "V <sub>SS</sub> / Device Ground"; updated<br>symbols<br>Updated Section 3.6, Electromagnetic interference (EMI) characteristics<br>Section 3.4, 1, Voltage regulator electrical characteristics<br>updated Section 3.6, Electromagnetic interference (EMI) characteristics<br>Section 3.1, 1, Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics: reorganized contents<br>Updated Section 3.10, <i>NUVSRO</i> (PAD3VSV] = 0): updated symbols<br>Corrected parameter descriptions in DC electrical characteristics (3.3 V,<br>NVUSRO[PAD3VSV] = 1):<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage", is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage |  |  |  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18-Jul-2012 | 8        | Updated Table 1 (Device summary)<br>Section 1.5.4, Flash memory: Changed "Data flash memory: 32-bit ECC" to "Data flash<br>memory: 64-bit ECC"<br>Figure 40 (Commercial product code structure), replaced "C = 60 MHz, 5 V" and "D = 60<br>MHz, 3.3 V" with respectively "C = 40 MHz, 5 V" and "D = 40 MHz, 3.3 V"<br>Table 9 (Absolute maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum value to 0.5 V/µs<br>Table 7 (Pin muxing), changed the description in the column "I/O direction" from "I/O" to<br>"O" for the following port pins:<br>A[10] with function B[0]<br>A[11] with function A[2]<br>A[12] with function A[2]<br>A[12] with function B[2]<br>C[7] with function A[3]<br>C[15] with function A[1]<br>D[0] with function A[1]<br>D[10] with function A[1]<br>D[11] with function A[1]<br>D[12] with function A[1]<br>D[13] with function A[1]<br>D[14] with function A[1]<br>D[15] with function A[1]<br>D[15] with function A[1]<br>D[16] bectrical characteristics:<br>deleted references to "oscillator margin"<br>deleted subsection "NVUSRO[OSCILLATOR_MARGIN] field description"<br>Table 21 (DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 0)), added IPU row<br>for RESET pin<br>Table 23 (DC electrical characteristics), added V <sub>INAN</sub> entry<br>Removed "Order codes" table<br>Figure 40 (Commercial product code structure):<br>added a footnote<br>updated "E = Data flash memory" |  |  |

| 18-Sep-2013 | 9        | Updated Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Table 46. Revision history (continued | Table 46. | Revision his | story (cont | (inued) |

|---------------------------------------|-----------|--------------|-------------|---------|

|---------------------------------------|-----------|--------------|-------------|---------|

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 14723 Rev 9