#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 67                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p50l3b1abr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

### 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P44Lx, SPC560P50Lx:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module can run on an independent clock source

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

### 1.5.13 System timer module (STM)

The STM module implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

### 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- 32-bit time-out register to set the time-out period

- Programmable selection of system or oscillator clock for timer operation

- Programmable selection of window mode or regular servicing

- Programmable selection of reset or interrupt on an initial time-out

- Master access protection

- Hard and soft configuration lock bits

- Reset configuration inputs allow timer to be enabled out of reset

### 1.5.15 Fault collection unit (FCU)

The FCU provides an independent fault reporting mechanism even if the CPU is malfunctioning.

The FCU module has the following features:

- FCU status register reporting the device status

- Continuous monitoring of critical fault signals

- User selection of critical signals from different fault sources inside the device

- Critical fault events trigger 2 external pins (user selected signal protocol) that can be used externally to reset the device and/or other circuitry (for example, safety relay or FlexRay transceiver)

- Faults are latched into a register

### 1.5.16 System integration unit – Lite (SIUL)

The SPC560P44Lx, SPC560P50Lx SIUL controls MCU pad configuration, external interrupt, general purpose I/O (GPIO), and internal peripheral multiplexing.

The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

The sources of the ECC errors are:

- Flash memory

- SRAM

### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

### 1.5.20 Controller area network (FlexCAN)

The SPC560P44Lx, SPC560P50Lx MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

| Port  | Pad                          | Alternate |           |                           | I/O              | Pad s   | peed <sup>(5)</sup> | Pin     | Pin No. |  |

|-------|------------------------------|-----------|-----------|---------------------------|------------------|---------|---------------------|---------|---------|--|

| pin   | configuration register (PCR) | (0)       | Functions | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |  |

|       |                              | ALT0      | GPIO[14]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | TXD       | Safety Port_0             | 0                |         |                     |         |         |  |

| A[14] | PCR[14]                      | ALT2      | ETC[4]    | eTimer_1                  | I/O              | Slow    | Medium              | 99      | 143     |  |

|       |                              | ALT3      | —         | —                         | —                |         |                     |         |         |  |

|       |                              | —         | EIRQ[13]  | SIUL                      | I                |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[15]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | —         | —                         | —                |         |                     |         |         |  |

| A[15] | PCR[15]                      | ALT2      | ETC[5]    | eTimer_1                  | I/O              | Slow    | Medium              | 100     | 144     |  |

| A[15] | FCR[15]                      | ALT3      | —         | —                         | —                | 310W    | Medium              | 100     | 144     |  |

|       |                              | —         | RXD       | Safety Port_0             | I                |         |                     |         |         |  |

|       |                              | —         | EIRQ[14]  | SIUL                      | I                |         |                     |         |         |  |

|       |                              |           |           | Port B (16-bit)           |                  |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[16]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | TXD       | FlexCAN_0                 | 0                |         |                     |         |         |  |

| B[0]  | PCR[16]                      | ALT2      | ETC[2]    | eTimer_1                  | I/O              | Slow    | Medium              | 76      | 109     |  |

|       |                              | ALT3      | DEBUG[0]  | SSCM                      | —                |         |                     |         |         |  |

|       |                              | —         | EIRQ[15]  | SIUL                      | I                |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[17]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | —         | —                         | —                |         |                     |         |         |  |

| B[1]  | PCR[17]                      | ALT2      | ETC[3]    | eTimer_1                  | I/O              | Slow    | Medium              | 77      | 110     |  |

| D[1]  | FCR[17]                      | ALT3      | DEBUG[1]  | SSCM                      | —                | 310W    | Medium              | 11      | 110     |  |

|       |                              | —         | RXD       | FlexCAN_0                 | I                |         |                     |         |         |  |

|       |                              | —         | EIRQ[16]  | SIUL                      | I                |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[18]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | TXD       | LIN_0                     | 0                |         |                     |         |         |  |

| B[2]  | PCR[18]                      | ALT2      | —         | —                         | —                | Slow    | Medium              | 79      | 114     |  |

|       |                              | ALT3      | DEBUG[2]  | SSCM                      | —                |         |                     |         |         |  |

|       |                              | —         | EIRQ[17]  | SIUL                      | I                |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[19]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | —         | —                         | —                |         |                     |         |         |  |

| B[3]  | PCR[19]                      | ALT2      | —         | —                         | —                | Slow    | Medium              | 80      | 116     |  |

|       |                              | ALT3      | DEBUG[3]  | SSCM                      | —                |         |                     |         |         |  |

|       |                              | —         | RXD       | LIN_0                     | I                |         |                     |         |         |  |

|       |                              | ALT0      | GPIO[22]  | SIUL                      | I/O              |         |                     |         |         |  |

|       |                              | ALT1      | CLKOUT    | MC_CGL                    | 0                |         |                     |         |         |  |

| B[6]  | PCR[22]                      | ALT2      | CS2       | DSPI_2                    | 0                | Slow    | Medium              | 96      | 138     |  |

|       |                              | ALT3      | —         | —                         | —                |         |                     |         |         |  |

|       |                              | —         | EIRQ[18]  | SIUL                      | I                |         |                     |         |         |  |

| Port    | Pad                             | Alternate                       |              |                           | I/O              | Pad sp  | Pin No. |         |         |

|---------|---------------------------------|---------------------------------|--------------|---------------------------|------------------|---------|---------|---------|---------|

| nin     | configuration<br>register (PCR) | function <sup>(1),</sup><br>(2) | Functions    | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1 | 100-pin | 144-pin |

|         |                                 | ALT0                            | GPIO[23]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT1                            |              | —                         |                  |         |         |         |         |

| B[7]    | PCR[23]                         | ALT2                            |              | —                         | Input only       | _       | _       | 29      | 43      |

|         |                                 | ALT3                            |              | ADC_0                     |                  |         |         |         |         |

|         |                                 | _                               | AN[0]<br>RXD | LIN_0                     |                  |         |         |         |         |

|         |                                 | ALT0                            |              |                           |                  |         |         |         |         |

|         |                                 | ALT0<br>ALT1                    | GPIO[24]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT2                            | _            | _                         |                  |         |         | 31      |         |

| B[8]    | PCR[24]                         | ALT3                            |              | _                         | Input only       | —       | —       |         | 47      |

|         |                                 | _                               | AN[1]        | ADC_0                     |                  |         |         |         |         |

|         |                                 | —                               | ETC[5]       | eTimer_0                  |                  |         |         |         |         |

|         |                                 | ALT0                            | GPIO[25]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                  |         |         |         |         |

| B[9]    | PCR[25]                         | ALT2                            |              | —                         | Input only       | —       | —       | 35      | 52      |

|         |                                 | ALT3                            | —            | —                         |                  |         |         |         |         |

|         |                                 | —                               | AN[11]       | ADC_0 / ADC_1             |                  |         |         |         |         |

|         |                                 | ALT0                            | GPIO[26]     | SIUL                      |                  |         |         |         |         |

| DI ( O) | DODION                          | ALT1                            |              | —                         |                  |         |         |         |         |

| B[10]   | PCR[26]                         | ALT2<br>ALT3                    |              | —                         | Input only       | _       | _       | 36      | 53      |

|         |                                 | ALI3<br>—                       | <br>AN[12]   | <br>ADC_0 / ADC_1         |                  |         |         |         |         |

|         |                                 | ALT0                            | GPIO[27]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT1                            | —            |                           |                  |         |         |         |         |

| B[11]   | PCR[27]                         | ALT2                            | _            | _                         | Input only       | _       | _       | 37      | 54      |

|         |                                 | ALT3                            |              | _                         |                  |         |         |         |         |

|         |                                 | —                               | AN[13]       | ADC_0 / ADC_1             |                  |         |         |         |         |

|         |                                 | ALT0                            | GPIO[28]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                  |         |         |         |         |

| B[12]   | PCR[28]                         | ALT2                            |              | —                         | Input only       | —       | —       | 38      | 55      |

|         |                                 | ALT3                            | —            | —                         |                  |         |         |         |         |

|         |                                 | _                               | AN[14]       | ADC_0 / ADC_1             |                  |         |         |         |         |

|         |                                 | ALT0                            | GPIO[29]     | SIUL                      |                  |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                  |         |         |         |         |

| B[13]   | PCR[29]                         | ALT2<br>ALT3                    | _            |                           | Input only       | —       | —       | 42      | 60      |

|         |                                 | ALIS                            | <br>AN[0]    | ADC_1                     |                  |         |         |         |         |

|         |                                 | _                               | RXD          | LIN_1                     |                  |         |         |         |         |

| Port  | Pad                          | Alternate                         |                                         |                                             | I/O                       | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|-----------------------------------|-----------------------------------------|---------------------------------------------|---------------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions                               | Peripheral <sup>(3)</sup>                   | direction<br>(4)          | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| D[5]  | PCR[53]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[53]<br>CS3<br>F[0]<br>SOUT         | SIUL<br>DSPI_0<br>FCU_0<br>DSPI_3           | I/O<br>O<br>O             | Slow    | Medium              | 22      | 33      |

| D[6]  | PCR[54]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[54]<br>CS2<br>SCK<br>—<br>FAULT[1] | SIUL<br>DSPI_0<br>DSPI_3<br>—<br>FlexPWM_0  | I/O<br>O<br>I/O<br>—<br>I | Slow    | Medium              | 23      | 34      |

| D[7]  | PCR[55]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[55]<br>CS3<br>F[1]<br>CS4<br>SIN   | SIUL<br>DSPI_1<br>FCU_0<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>O<br>I        | Slow    | Medium              | 26      | 37      |

| D[8]  | PCR[56]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[56]<br>CS2<br>—<br>CS5<br>FAULT[3] | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>FlexPWM_0  | I/O<br>O<br>—<br>O<br>I   | Slow    | Medium              | 21      | 32      |

| D[9]  | PCR[57]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>X[0]<br>TXD<br>—            | SIUL<br>FlexPWM_0<br>LIN_1<br>—             | I/O<br>I/O<br>O<br>—      | Slow    | Medium              | 15      | 26      |

| D[10] | PCR[58]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>A[0]<br>CS0<br>—            | SIUL<br>FlexPWM_0<br>DSPI_3<br>—            | I/O<br>O<br>I/O<br>—      | Slow    | Medium              | 53      | 76      |

| D[11] | PCR[59]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>CS1<br>SCK          | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>I/O      | Slow    | Slow Medium         |         | 78      |

| D[12] | PCR[60]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD            | SIUL<br>FlexPWM_0<br>—<br>LIN_1             | I/O<br>I/O<br>—<br>I      | Slow    | Medium              | 70      | 99      |

| D[13] | PCR[61]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>CS2<br>SOUT         | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>O        | Slow    | Medium              | 67      | 95      |

| Port  | Pad                          | Alternate                       | -                  |                           | I/O              | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|---------------------------------|--------------------|---------------------------|------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup><br>(2) | Functions          | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

|       |                              | ALT0                            | GPIO[62]           | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | B[1]               | FlexPWM_0                 | 0                |         |                     |         |         |

| D[14] | PCR[62]                      | ALT2                            | CS3                | DSPI_3                    | 0                | Slow    | Medium              | 73      | 105     |

|       |                              | ALT3                            | —                  | —                         | —                |         |                     |         |         |

|       |                              | —                               | SIN                | DSPI_3                    | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[63]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| D[15] | PCR[63]                      | ALT2                            | _                  | —                         | Input only       | —       | —                   | 41      | 58      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[4]              | ADC_1                     |                  |         |                     |         |         |

|       |                              |                                 |                    | Port E(16-bit)            |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[64]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[0]  | PCR[64]                      | ALT2                            | _                  | —                         | Input only       | —       | —                   | 46      | 68      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[5]              | ADC_1                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[65]           | SIUL                      |                  |         |                     | 27      |         |

|       |                              | ALT1                            | —                  | —                         | Input only       | _       |                     |         |         |

| E[1]  | PCR[65]                      | ALT2                            | —                  | —                         |                  |         | _                   |         | 39      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[4]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[66]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[2]  | PCR[66]                      | ALT2                            | —                  | —                         | Input only       | —       | —                   | 32      | 49      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[5]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[67]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[3]  | PCR[67]                      | ALT2                            | —                  | —                         | Input only       | —       | —                   |         | 40      |

|       |                              | ALT3                            | —<br>• • • • • • • | —                         |                  |         |                     |         |         |

|       |                              | _                               | AN[6]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[68]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[4]  | PCR[68]                      | ALT2                            | —                  | —                         | Input only       | —       | _                   |         | 42      |

|       |                              | ALT3                            |                    | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[7]              | ADC_0                     |                  |         |                     |         |         |

| Port  | Pad                          | Alternate                         |                                        |                             | I/O                | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|-----------------------------------|----------------------------------------|-----------------------------|--------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions                              | Peripheral <sup>(3)</sup>   | direction<br>(4)   | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| F[14] | PCR[94]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[94]<br>TXD<br>—<br>—              | SIUL<br>LIN_1<br>—          | V0 0               | Slow    | Medium              | _       | 115     |

| F[15] | PCR[95]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[95]<br>—<br>—<br>RXD              | SIUL<br>—<br>—<br>LIN_1     | I/O<br>     <br>   | Slow    | Slow Medium         |         | 113     |

|       |                              |                                   |                                        | Port G (12-bit)             |                    |         |                     |         |         |

| G[0]  | PCR[96]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[96]<br>F[0]<br>—<br>EIRQ[30]      | SIUL<br>FCU_0<br>—<br>SIUL  | I/O<br>O<br>—<br>I | Slow    | Medium              | _       | 38      |

| G[1]  | PCR[97]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[97]<br>F[1]<br>—<br>—<br>EIRQ[31] | SIUL<br>FCU_0<br>—<br>SIUL  | I/O<br>O<br>—<br>I | Slow    | Medium              |         | 141     |

| G[2]  | PCR[98]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[98]<br>X[2]<br>—                  | SIUL<br>FlexPWM_0<br>—      | I/O<br>I/O<br>—    | Slow    | Medium              |         | 102     |

| G[3]  | PCR[99]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[99]<br>A[2]<br>—<br>—             | SIUL<br>FlexPWM_0<br>—      | I/O<br>O<br>—      | Slow    | Medium              | _       | 104     |

| G[4]  | PCR[100]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[100]<br>B[2]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—      | I/O<br>O<br>—      | Slow    | Medium              | _       | 100     |

| G[5]  | PCR[101]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[101]<br>X[3]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—      | I/O<br>I/O<br>—    | Slow    | Medium              | _       | 85      |

| G[6]  | PCR[102]                     | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[102]<br>A[3]<br>—<br>—            | SIUL<br>FlexPWM_0<br>—<br>— | I/O<br>O<br>—      | Slow    | Medium              | _       | 98      |

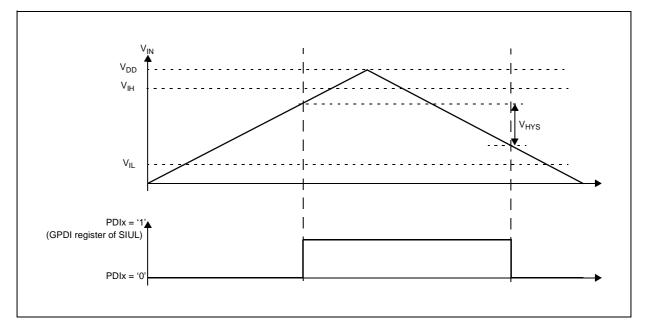

Figure 14. Input DC electrical characteristics definition

### 3.10.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in *Table 25*.

| Table 25. | I/O supply segment |

|-----------|--------------------|

|-----------|--------------------|

| Package |               |               | ę             | Supply segme  | nt            |                |               |

|---------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|

|         | 1             | 2             | 3             | 4             | 5             | 6              | 7             |

| LQFP144 | pin8 – pin20  | pin23 – pin38 | pin39 – pin55 | pin58 – pin68 | pin73 – pin89 | pin92 – pin125 | pin128 – pin5 |

| LQFP100 | pin15 – pin26 | pin27 – pin38 | pin41 – pin46 | pin51 – pin61 | pin64 – pin86 | pin89 – pin10  | —             |

Table 26 provides the weight of concurrent switching I/Os.

In order to ensure device functionality, the sum of the weight of concurrent switching I/Os on a single segment should remain below 100%.

Table 26. I/O weight

| Pad     | LQ        | FP144       | LQFP100   |             |  |  |  |  |

|---------|-----------|-------------|-----------|-------------|--|--|--|--|

| Pau     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |  |  |  |

| NMI     | 1%        | 1%          | 1%        | 1%          |  |  |  |  |

| PAD[6]  | 6%        | 5%          | 14%       | 13%         |  |  |  |  |

| PAD[49] | 5%        | 4%          | 14%       | 12%         |  |  |  |  |

| PAD[84] | 14%       | 10%         | —         | _           |  |  |  |  |

| PAD[85] | 9%        | 7%          | —         | _           |  |  |  |  |

| Table 26. | I/O weight ( | (continued) |

|-----------|--------------|-------------|

|-----------|--------------|-------------|

| Ded     | LQ        | FP144       | LQI       | FP100       |

|---------|-----------|-------------|-----------|-------------|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |

| PAD[86] | 9%        | 6%          | —         | _           |

| MODO[0] | 12%       | 8%          | _         |             |

| PAD[7]  | 4%        | 4%          | 11%       | 10%         |

| PAD[36] | 5%        | 4%          | 11%       | 9%          |

| PAD[8]  | 5%        | 4%          | 10%       | 9%          |

| PAD[37] | 5%        | 4%          | 10%       | 9%          |

| PAD[5]  | 5%        | 4%          | 9%        | 8%          |

| PAD[39] | 5%        | 4%          | 9%        | 8%          |

| PAD[35] | 5%        | 4%          | 8%        | 7%          |

| PAD[87] | 12%       | 9%          | —         | _           |

| PAD[88] | 9%        | 6%          | —         |             |

| PAD[89] | 10%       | 7%          | —         | _           |

| PAD[90] | 15%       | 11%         | —         | _           |

| PAD[91] | 6%        | 5%          | —         | _           |

| PAD[57] | 8%        | 7%          | 8%        | 7%          |

| PAD[56] | 13%       | 11%         | 13%       | 11%         |

| PAD[53] | 14%       | 12%         | 14%       | 12%         |

| PAD[54] | 15%       | 13%         | 15%       | 13%         |

| PAD[55] | 25%       | 22%         | 25%       | 22%         |

| PAD[96] | 27%       | 24%         | —         | _           |

| PAD[65] | 1%        | 1%          | 1%        | 1%          |

| PAD[67] | 1%        | 1%          | —         | _           |

| PAD[33] | 1%        | 1%          | 1%        | 1%          |

| PAD[68] | 1%        | 1%          | —         | _           |

| PAD[23] | 1%        | 1%          | 1%        | 1%          |

| PAD[69] | 1%        | 1%          | —         | _           |

| PAD[34] | 1%        | 1%          | 1%        | 1%          |

| PAD[70] | 1%        | 1%          | —         | _           |

| PAD[24] | 1%        | 1%          | 1%        | 1%          |

| PAD[71] | 1%        | 1%          | —         | _           |

| PAD[66] | 1%        | 1%          | 1%        | 1%          |

| PAD[25] | 1%        | 1%          | 1%        | 1%          |

| PAD[26] | 1%        | 1%          | 1%        | 1%          |

| Symbol                 |     | С                       | Parameter                              | Condit                                        | ions <sup>(1)</sup>                           |     | Value |      | Unit |                                |  |   |   |    |  |

|------------------------|-----|-------------------------|----------------------------------------|-----------------------------------------------|-----------------------------------------------|-----|-------|------|------|--------------------------------|--|---|---|----|--|

| Symbol                 |     | C                       |                                        |                                               |                                               | Min | Тур   | Max  | Unit |                                |  |   |   |    |  |

|                        |     |                         |                                        | C <sub>L</sub> = 25 pF, 13 MHz                |                                               | —   | _     | 6.6  |      |                                |  |   |   |    |  |

|                        |     |                         |                                        | C <sub>L</sub> = 25 pF, 40 MHz                | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | —     | 13.4 |      |                                |  |   |   |    |  |

|                        | сс  | Р                       |                                        | C <sub>L</sub> = 100 pF, 13 MHz               |                                               |     | —     | 18.3 | mA   |                                |  |   |   |    |  |

| I <sub>RMSMED</sub> CC |     | MEDIUM<br>configuration | C <sub>L</sub> = 25 pF, 13 MHz         |                                               |                                               | _   | 5     |      |      |                                |  |   |   |    |  |

|                        |     | configuration           | C <sub>L</sub> = 25 pF, 40 MHz         | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                                             | —   | 8.5   |      |      |                                |  |   |   |    |  |

|                        |     |                         |                                        | C <sub>L</sub> = 100 pF, 13 MHz               |                                               | _   | _     | 11   |      |                                |  |   |   |    |  |

|                        |     |                         |                                        |                                               |                                               |     |       |      |      | C <sub>L</sub> = 25 pF, 40 MHz |  | _ | _ | 22 |  |

|                        |     |                         | Root medium square                     | C <sub>L</sub> = 25 pF, 64 MHz                | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | —     | 33   |      |                                |  |   |   |    |  |

|                        | сс  |                         |                                        | C <sub>L</sub> = 100 pF, 40 MHz               |                                               | _   | _     | 56   | mA   |                                |  |   |   |    |  |

| IRMSFST                | CC  |                         | I/O current for FAST configuration     | C <sub>L</sub> = 25 pF, 40 MHz                |                                               | _   | _     | 14   | mA   |                                |  |   |   |    |  |

|                        |     |                         |                                        | C <sub>L</sub> = 25 pF, 64 MHz                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _     | 20   |      |                                |  |   |   |    |  |

|                        |     |                         |                                        | C <sub>L</sub> = 100 pF, 40 MHz               |                                               | _   | _     | 35   |      |                                |  |   |   |    |  |

|                        | 0.5 |                         | Sum of all the static                  | V <sub>DD</sub> = 5.0 V ± 10%, P/             | AD3V5V = 0                                    | _   | _     | 70   |      |                                |  |   |   |    |  |

| IAVGSEG                | SR  |                         | I/O current within a<br>supply segment | V <sub>DD</sub> = 3.3 V ± 10%, P/             | AD3V5V = 1                                    | _   | _     | 65   | mA   |                                |  |   |   |    |  |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

2. Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

# 3.11 Main oscillator electrical characteristics

The SPC560P44Lx, SPC560P50Lx provides an oscillator/resonator driver.

Table 28.Main oscillator output electrical characteristics (5.0 V,<br/>NVUSRO[PAD3V5V] = 0)

| Symbol             |    | С | Parameter                               | Value |     | Unit |  |

|--------------------|----|---|-----------------------------------------|-------|-----|------|--|

|                    |    | C | Farameter                               | Min   | Max | onit |  |

| fosc               | SR | — | Oscillator<br>frequency                 | 4     | 40  | MHz  |  |

| 9 <sub>m</sub>     | _  | Р | Transconduc<br>tance                    | 6.5   | 25  | mA/V |  |

| V <sub>OSC</sub>   | _  | Т | Oscillation<br>amplitude on<br>XTAL pin | 1     | _   | V    |  |

| t <sub>oscsu</sub> | —  | Т | Start-up<br>time <sup>(1),(2)</sup>     | 8     | _   | ms   |  |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of XTAL

| Symbol              | С                     | Devenueter                           |                                               | Conditions <sup>(1)</sup> | Value |                      | Unit                  |  |

|---------------------|-----------------------|--------------------------------------|-----------------------------------------------|---------------------------|-------|----------------------|-----------------------|--|

| Symbol C            |                       | Parameter                            |                                               | Conditions                | Min   | Max                  | onit                  |  |

|                     |                       |                                      | Short-term jitter <sup>(10)</sup>             | f <sub>SYS</sub> maximum  | -4    | 4                    | % f <sub>CLKOUT</sub> |  |

| C <sub>JITTER</sub> |                       |                                      | Long-term jitter (avg.<br>over 2 ms interval) |                           |       | 10                   | ns                    |  |

| t <sub>lpll</sub>   | D                     | PLL lock time <sup>(11), (12)</sup>  |                                               | _                         | _     | 200                  | μs                    |  |

| t <sub>dc</sub>     | D                     | Duty cycle of reference              |                                               | _                         | 40    | 60                   | %                     |  |

| f <sub>LCK</sub>    | D                     | Frequency LOCK range                 |                                               | —                         | -6    | 6                    | % f <sub>SYS</sub>    |  |

| f <sub>UL</sub>     | D                     | Frequency un-LOCK range              |                                               | _                         | -18   | 18                   | % f <sub>SYS</sub>    |  |

| f <sub>CS</sub>     | CS D Modulation depth |                                      |                                               | Center spread             | ±0.25 | ±4.0 <sup>(13)</sup> |                       |  |

| f <sub>DS</sub>     |                       | Modulation depth                     |                                               | Down spread               | -0.5  | -8.0                 | % f <sub>SYS</sub>    |  |

| f <sub>MOD</sub>    | D                     | Modulation frequency <sup>(14)</sup> |                                               | —                         |       | 70                   | kHz                   |  |

Table 31.

FMPLL electrical characteristics (continued)

1.  $V_{DD_{L}V_{C}ORx}$  = 1.2 V ±10%;  $V_{SS}$  = 0 V;  $T_A$  = -40 to 125 °C, unless otherwise specified

2. Considering operation with PLL not bypassed

3. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self-clocked mode.

4. Self-clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

6. This value is determined by the crystal manufacturer and board design.

7. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

8. Proper PC board layout procedures must be followed to achieve specifications.

- Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- 10. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

- 11. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 12. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 13. This value is true when operating at frequencies above 60 MHz, otherwise  $f_{CS}$  is 2% (above 64 MHz).

- 14. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

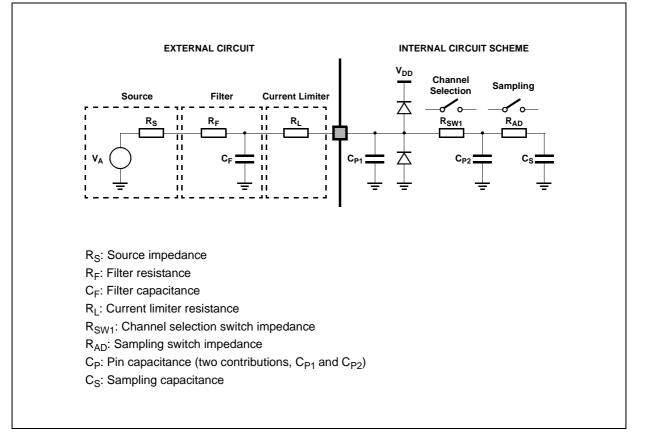

The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{P2}$  being substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc \times (C_S+C_{P2}))$ ), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the *Equation 4*:

#### **Equation 4**

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

*Equation 4* generates a constraint for external network design, in particular on resistive path.

Figure 16. Input equivalent circuit

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 16*): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch closed).

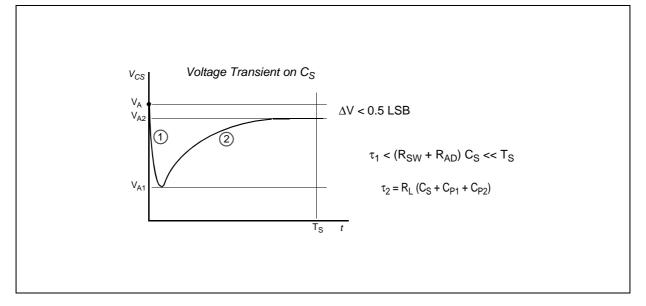

#### Figure 17. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

• A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

#### **Equation 5**

$$\tau_1 = (R_{SW} + R_{AD}) \bullet \frac{C_P \bullet C_S}{C_P + C_S}$$

*Equation 5* can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

#### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \bullet C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

**Equation 12**

$$C_F > 2048 \bullet C_S$$

#### 3.14.2 ADC conversion characteristics

| Table 33. ADC conversion characteristics | Table 33. | ADC conversion characteristics |

|------------------------------------------|-----------|--------------------------------|

|------------------------------------------|-----------|--------------------------------|

| Symbol C               |    | C | Parameter                                                                                                                  | Conditions <sup>(1)</sup>                                | Value                            |     |                                  | Unit |

|------------------------|----|---|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|-----|----------------------------------|------|

| Symb                   |    |   | Farameter                                                                                                                  | Conditions                                               | Min                              | Тур | Тур Мах                          |      |

| V <sub>INAN0</sub>     | SR |   | ADC0 and shared ADC0/1<br>analog input voltage <sup>(2), (3)</sup>                                                         | —                                                        | V <sub>SS_HV_ADV0</sub><br>- 0.3 | _   | V <sub>DD_HV_ADV0</sub><br>+ 0.3 | V    |

| V <sub>INAN1</sub>     | SR |   | ADC1 analog input voltage <sup>(2),</sup> <sup>(4)</sup>                                                                   | _                                                        | V <sub>SS_HV_ADV1</sub><br>- 0.3 | _   | V <sub>DD_HV_ADV1</sub><br>+ 0.3 | V    |

| f <sub>CK</sub>        | SR |   | ADC clock frequency<br>(depends on ADC<br>configuration)<br>(The duty cycle depends on<br>AD_clk <sup>(5)</sup> frequency) | _                                                        | 3(6)                             | _   | 60                               | MHz  |

| f <sub>s</sub>         | SR | _ | Sampling frequency                                                                                                         | —                                                        | _                                |     | 1.53                             | MHz  |

| tuno -                 |    | D | Sample time <sup>(7)</sup>                                                                                                 | f <sub>ADC</sub> = 20 MHz,<br>INPSAMP = 3                | 125                              | _   | —                                | ns   |

| t <sub>ADC_S</sub> — D |    | U |                                                                                                                            | f <sub>ADC</sub> = 9 MHz,<br>INPSAMP = 255               |                                  | _   | 28.2                             | μs   |

| t <sub>ADC_C</sub>     | _  | Ρ | Conversion time <sup>(8)</sup>                                                                                             | f <sub>ADC</sub> = 20 MHz <sup>(9)</sup> ,<br>INPCMP = 1 | 0.650                            |     | _                                | μs   |

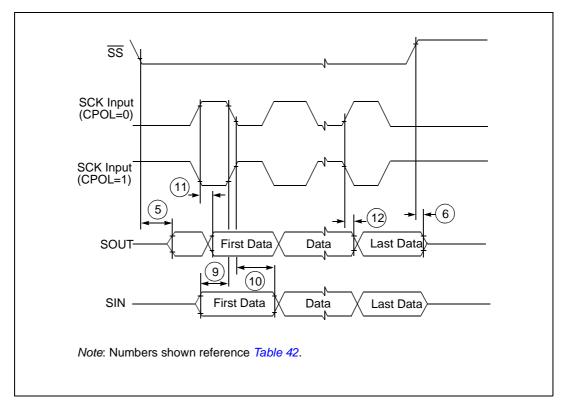

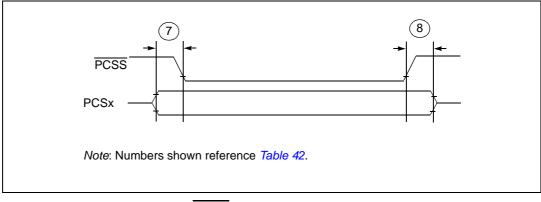

### Figure 36. DSPI modified transfer format timing – Slave, CPHA = 1

Figure 37. DSPI PCS strobe (PCSS) timing

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

IIn order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 4.2 Package mechanical data

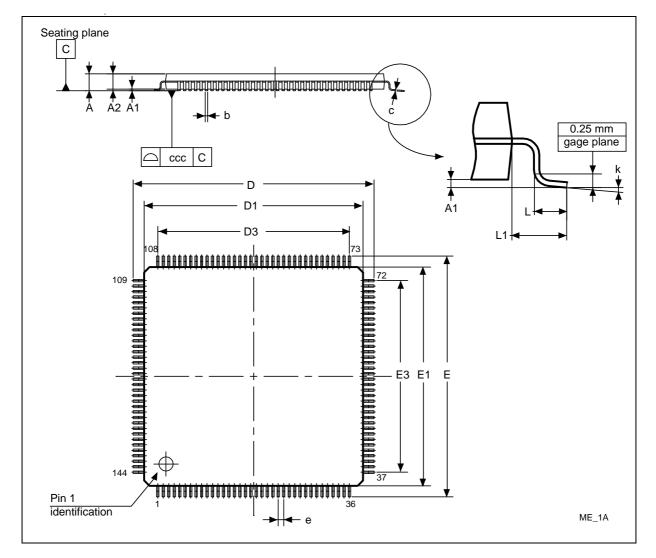

### 4.2.1 LQFP144 mechanical outline drawing

Figure 38. LQFP144 package mechanical drawing

Doc ID 14723 Rev 9

|                    | Dimensions |        |        |                       |        |        |  |

|--------------------|------------|--------|--------|-----------------------|--------|--------|--|

| Symbol             |            | mm     |        | inches <sup>(1)</sup> |        |        |  |

|                    | Min        | Тур    | Max    | Min                   | Тур    | Мах    |  |

| А                  | _          | —      | 1.600  | —                     | —      | 0.0630 |  |

| A1                 | 0.050      | —      | 0.150  | 0.0020                | —      | 0.0059 |  |

| A2                 | 1.350      | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b                  | 0.170      | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С                  | 0.090      | —      | 0.200  | 0.0035                | —      | 0.0079 |  |

| D                  | 21.800     | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| D1                 | 19.800     | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| D3                 | _          | 17.500 | _      | _                     | 0.6890 |        |  |

| Е                  | 21.800     | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| E1                 | 19.800     | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| E3                 | _          | 17.500 | _      | _                     | 0.6890 |        |  |

| е                  | _          | 0.500  | —      | —                     | 0.0197 | —      |  |

| L                  | 0.450      | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1                 | _          | 1.000  | —      | —                     | 0.0394 | —      |  |

| k                  | 0.0°       | 3.5°   | 7.0°   | 3.5°                  | 0.0°   | 7.0°   |  |

| ccc <sup>(2)</sup> |            | 0.080  | 1      | 0.0031                |        |        |  |

#### Table 43. LQFP144 mechanical data

1. Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

2. Tolerance

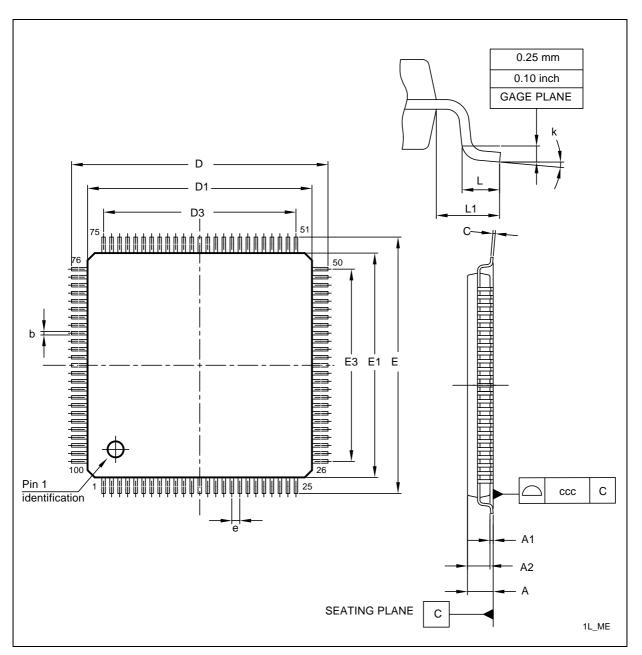

# 4.2.2 LQFP100 mechanical outline drawing

| Date                                                                                                                                     | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 27-Oct-2009                                                                                                                              | 5        | <ul> <li>Added "Full Feature" and "Airbag" customization.</li> <li>Removed B[4] and B[5] rows from "Pin muxing" table and inserted them on "System pins" table.</li> <li>Updated package pinout.</li> <li>Rewrote entirely section "Power Up/dpwn Sequencing" section.</li> <li>Renamend "V<sub>DD_LV</sub>_PLL" and "V<sub>SS_LV</sub>_PLL" supply pins with respectively "V<sub>DD_LV</sub>_COR3" and "V<sub>SS_LV</sub>_COR3".</li> <li>Added explicative figures on "Electrical characteristics" section.</li> <li>Updated "Thermal characteristics" for 100-pin.</li> <li>Proposed two different configuration of "voltage regulator Inserted Power Up/Down sequence.</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added "I/O pad current specification" section.</li> <li>Renamed the "Airbag mode" with "Typical mode"and updated the values on "supply current" tables.</li> <li>Added more order code.</li> </ul>                                         |  |  |  |

| 06-Apr-2010                                                                                                                              | 6        | Inserted label of Y-axis in the "Independent ADC supply" figure.<br>"Recommended Operating Conditions" tables:<br>Moved the T <sub>J</sub> row to "Absolute Maximum Ratings" table.<br>Rewrite note 1 and 3<br>Inverted Min a Typ value of C <sub>DEC2</sub> on "Voltage Regulator Electrical Characteristics" table<br>Removed an useless duplicate of "Voltage Regulator Electrical Characteristics" table.<br>Inserted the name of C <sub>S</sub> into "Input Equivalent Circuit" figure.<br>Removed leakage lvpp from datasheet.<br>Updated "Supply Current" tables.<br>Added note on "Output pin transition times" table.<br>Updated "Temperature Sensor Electrical Characteristics" table.<br>Updated "16 MHz RC Oscillator Electrical Characteristics" table.<br>Removed the note about the condition from "Flash read access timing" table.<br>Removed the notes that assert the values need to be confirmed before validation.                                                                                                                                      |  |  |  |

| 07-Apr-2011<br>7<br>07-Apr-2011<br>07-Apr-2011<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |          | <ul> <li>Formatting and editorial changes throughout<br/>Removed all content referencing Junction Temperature Sensor<br/>Cover page Features:</li> <li>CPU core—specified 64 MHz frequency</li> <li>updated memory features</li> <li>eTimer units: changed "up/down capabilities" to "up/down count capabilities"</li> <li>ADC—changed "2 × 13 input channels" to "2 × 11 input channels, + 4 shared channels"</li> <li>replaced "On-chip CAN/UART/FlexRay bootstrap loader" with "On-chip CAN/UART<br/>bootstrap loader"</li> <li>Section 1: Introduction: changed title (was: Overview); reorganized contents<br/>SPC560P44Lx, SPC560P50Lx device comparison:</li> <li>ADC feature: changed "16 channels" to "15-channel"; added footnote to to indicate that<br/>four channels are shared between the two ADCs</li> <li>removed SPC560P40 column</li> <li>changed "dual channel" to "selectable single or dual channel support" in FlexRay<br/>footnote</li> <li>updated "eTimer" feature</li> <li>updated footnote relative to "Digital power supply" feature</li> </ul> |  |  |  |

Table 46.

Revision history (continued)