#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 67                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p50l3befay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The sources of the ECC errors are:

- Flash memory

- SRAM

### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

### 1.5.20 Controller area network (FlexCAN)

The SPC560P44Lx, SPC560P50Lx MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal busses to provide development support as per the IEEE-ISTO 5001-2003 Class 2+ standard. The development support provided includes access to the MCU's internal memory map and access to the processor's internal registers during run time.

The Nexus Interface provides the following features:

- Configured via the IEEE 1149.1

- All Nexus port pins operate at V<sub>DDIO</sub> (no dedicated power supply)

- Nexus 2+ features supported

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or keep executing and allow overwrite of information

- Watchpoint triggering, watchpoint triggers program tracing

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin

### 1.5.30 Cyclic redundancy check (CRC)

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC module features:

- Support for CRC-16-CCITT (*x*25 protocol):

- $x^{16} + x^{12} + x^5 + 1$

- Support for CRC-32 (Ethernet protocol):

- $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

### 1.5.31 IEEE 1149.1 JTAG controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

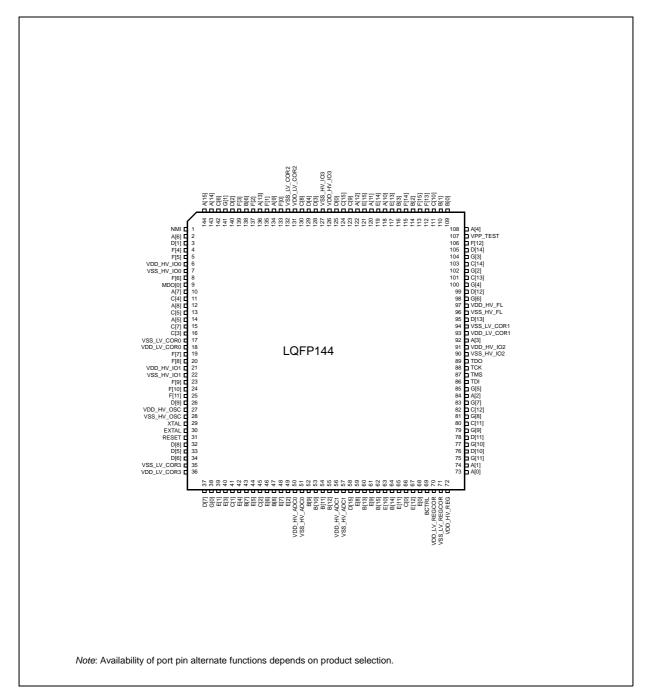

# 2 Package pinouts and signal descriptions

# 2.1 Package pinouts

The LQFP pinouts are shown in the following figures.

Figure 2. 144-pin LQFP pinout – Full featured configuration (top view)

Doc ID 14723 Rev 9

# Table 5.Supply pins

|                                            | Supply                                                                                                                                           |                | Pin     |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|

| Symbol                                     | Description                                                                                                                                      | 100-pin        | 144-pin |

| VREG                                       | control and power supply pins. Pins available on 100-pin and                                                                                     | 144-pin packa  | ge.     |

| BCTRL                                      | Voltage regulator external NPN ballast base control pin                                                                                          | 47             | 69      |

| V <sub>DD_HV_REG</sub> (3.3 V<br>or 5.0 V) | Voltage regulator supply voltage                                                                                                                 | 50             | 72      |

| V <sub>DD_LV_REGCOR</sub>                  | 1.2 V decoupling pins for core logic and regulator feedback. Decoupling capacitor must be connected between this pins and $V_{SS\_LV\_REGCOR}$ . | 48             | 70      |

| V <sub>SS_LV_REGCOR</sub>                  | 1.2 V decoupling pins for core logic and regulator feedback. Decoupling capacitor must be connected between this pins and $V_{DD_LV\_REGCOR}$ .  | 49             | 71      |

| ADC_0/AD                                   | C_1 reference and supply voltage. Pins available on 100-pin a                                                                                    | and 144-pin pa | ickage. |

| V <sub>DD_HV_ADC0</sub> <sup>(1)</sup>     | ADC_0 supply and high reference voltage                                                                                                          | 33             | 50      |

| V <sub>SS_HV_ADC0</sub>                    | ADC_0 ground and low reference voltage                                                                                                           | 34             | 51      |

| V <sub>DD_HV_ADC1</sub>                    | ADC_1 supply and high reference voltage                                                                                                          | 39             | 56      |

| V <sub>SS_HV_ADC1</sub>                    | ADC_1 ground and low reference voltage                                                                                                           | 40             | 57      |

| F                                          | ower supply pins (3.3 V or 5.0 V). All pins available on 144-pi<br>Five pairs (V <sub>DD</sub> ; V <sub>SS</sub> ) available on 100-pin package. |                |         |

| V <sub>DD_HV_IO0</sub> <sup>(2)</sup>      | Input/Output supply voltage                                                                                                                      | _              | 6       |

| $V_{SS_HV_IOO}^{(2)}$                      | Input/Output ground                                                                                                                              |                | 7       |

| V <sub>DD_HV_IO1</sub>                     | Input/Output supply voltage                                                                                                                      | 13             | 21      |

| $V_{SS_HV_{IO1}}$                          | Input/Output ground                                                                                                                              | 14             | 22      |

| $V_{DD_HV_1O2}$                            | Input/Output supply voltage                                                                                                                      | 63             | 91      |

| $V_{SS_HV_HO2}$                            | Input/Output ground                                                                                                                              | 62             | 90      |

| V <sub>DD_HV_IO3</sub>                     | Input/Output supply voltage                                                                                                                      | 87             | 126     |

| $V_{SS_HV_HO3}$                            | Input/Output ground                                                                                                                              | 88             | 127     |

| V <sub>DD_HV_FL</sub>                      | Code and data flash supply voltage                                                                                                               | 69             | 97      |

| V <sub>SS_HV_FL</sub>                      | Code and data flash supply ground                                                                                                                | 68             | 96      |

| V <sub>DD_HV_OSC</sub>                     | Crystal oscillator amplifier supply voltage                                                                                                      | 16             | 27      |

| V <sub>SS_HV_OSC</sub>                     | Crystal oscillator amplifier ground                                                                                                              | 17             | 28      |

| Po                                         | wer supply pins (1.2 V). All pins available on 100-pin and 144-                                                                                  | pin package.   |         |

| V <sub>DD_LV_COR0</sub>                    | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR}$ pin.           | 12             | 18      |

| V <sub>SS_LV_COR0</sub>                    | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD\ LV\ COR}$ pin.           | 11             | 17      |

| Table 7. | Pin r | nuxing |

|----------|-------|--------|

|----------|-------|--------|

| Port                | Pad                          | Alternate                                   |                                                            |                                                                | I/O                                 | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|---------------------|------------------------------|---------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|---------|---------------------|---------|---------|

| pin                 | configuration register (PCR) | function <sup>(1),</sup><br>(2)             | Functions                                                  | Peripheral <sup>(3)</sup>                                      | direction<br>(4)                    | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

|                     |                              |                                             |                                                            | Port A (16-bit)                                                |                                     |         |                     |         |         |

| A[0]                | PCR[0]                       | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[0]<br>ETC[0]<br>SCK<br>F[0]<br>EIRQ[0]                | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | I/O<br>I/O<br>O<br>I                | Slow    | Medium              | 51      | 73      |

| A[1]                | PCR[1]                       | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[1]<br>ETC[1]<br>SOUT<br>F[1]<br>EIRQ[1]               | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | I/O<br>I/O<br>O<br>I                | Slow    | Medium              | 52      | 74      |

| A[2] <sup>(6)</sup> | PCR[2]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[2]<br>ETC[2]<br>—<br>A[3]<br>SIN<br>ABS[0]<br>EIRQ[2] | SIUL<br>eTimer_0<br>—<br>FlexPWM_0<br>DSPI_2<br>MC_RGM<br>SIUL | I/O<br>I/O<br>-<br>O<br>I<br>I<br>I | Slow    | Medium              | 57      | 84      |

| A[3] <sup>(6)</sup> | PCR[3]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[3]<br>ETC[3]<br>CS0<br>B[3]<br>ABS[2]<br>EIRQ[3]      | SIUL<br>eTimer_0<br>DSPI_2<br>FlexPWM_0<br>MC_RGM<br>SIUL      | I/O<br>I/O<br>I/O<br>O<br>I<br>I    | Slow    | Medium              | 64      | 92      |

| A[4] <sup>(6)</sup> | PCR[4]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[4]<br>ETC[0]<br>CS1<br>ETC[4]<br>FAB<br>EIRQ[4]       | SIUL<br>eTimer_1<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL       | I/O<br>I/O<br>O<br>I/O<br>I<br>I    | Slow    | Medium              | 75      | 108     |

| A[5]                | PCR[5]                       | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[5]<br>CS0<br>ETC[5]<br>CS7<br>EIRQ[5]                 | SIUL<br>DSPI_1<br>eTimer_1<br>DSPI_0<br>SIUL                   | I/O<br>I/O<br>I/O<br>I              | Slow    | Medium              | 8       | 14      |

| A[6]                | PCR[6]                       | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[6]<br>SCK<br>—<br>—<br>EIRQ[6]                        | SIUL<br>DSPI_1<br>—<br>SIUL                                    | I/O<br>I/O<br>—<br>I                | Slow    | Medium              | 2       | 2       |

| Port  | Pad                          | Alternate                              |                                                              |                                                                  | I/O                            | Pad s           | peed <sup>(5)</sup> |         | No.     |

|-------|------------------------------|----------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|--------------------------------|-----------------|---------------------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup><br>(2)        | Functions Peripheral <sup>(3)</sup>                          |                                                                  | direction<br>(4)               | SRC = 0 SRC = 1 |                     | 100-pin | 144-pin |

| C[13] | PCR[45]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[45]<br>ETC[1]<br>—<br>EXT_IN<br>EXT_IN                  | SIUL<br>eTimer_1<br>—<br>—<br>CTU_0<br>FlexPWM_0                 | I/O<br>I/O<br>—<br>I<br>I      | Slow            | Medium              | 71      | 101     |

| C[14] | PCR[46]                      | ALTO<br>ALT1<br>ALT2<br>ALT3           | GPIO[46]<br>ETC[2]<br>EXT_TGR<br>—                           | SIUL<br>eTimer_1<br>CTU_0<br>—                                   | I/O<br>I/O<br>O                | Slow            | Medium              | 72      | 103     |

| C[15] | PCR[47]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[47]<br>CA_TR_EN<br>ETC[0]<br>A[1]<br>EXT_IN<br>EXT_SYNC | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0<br>CTU_0<br>FlexPWM_0 | I/O<br>O<br>I/O<br>O<br>I<br>I | Slow            | Symmetric           | 85      | 124     |

|       |                              |                                        |                                                              | Port D (16-bit)                                                  |                                |                 |                     |         |         |

| D[0]  | PCR[48]                      | ALTO<br>ALT1<br>ALT2<br>ALT3           | GPIO[48]<br>CA_TX<br>ETC[1]<br>B[1]                          | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0                       | I/O<br>O<br>I/O<br>O           | Slow            | Symmetric           | 86      | 125     |

| D[1]  | PCR[49]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[49]<br>—<br>ETC[2]<br>EXT_TRG<br>CA_RX                  | SIUL<br>—<br>eTimer_1<br>CTU_0<br>FlexRay_0                      | I/O<br>—<br>I/O<br>O<br>I      | Slow            | Medium              | 3       | 3       |

| D[2]  | PCR[50]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[50]<br>—<br>ETC[3]<br>X[3]<br>CB_RX                     | SIUL<br><br>eTimer_1<br>FlexPWM_0<br>FlexRay_0                   | I/O<br>—<br>I/O<br>I/O<br>I    | Slow            | Medium              | 97      | 140     |

| D[3]  | PCR[51]                      | ALTO<br>ALT1<br>ALT2<br>ALT3           | GPIO[51]<br>CB_TX<br>ETC[4]<br>A[3]                          | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0                       | I/O<br>O<br>I/O<br>O           | Slow            | Symmetric           | 89      | 128     |

| D[4]  | PCR[52]                      | ALTO<br>ALT1<br>ALT2<br>ALT3           | GPIO[52]<br>CB_TR_EN<br>ETC[5]<br>B[3]                       | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0                       | I/O<br>O<br>I/O<br>O           | Slow            | Symmetric           | 90      | 129     |

### Table 7. Pin muxing (continued)

| Port  | Pad                          | Alternate                         |                                         |                                             | I/O                       | Pad s   | peed <sup>(5)</sup> | Pin     | No.     |

|-------|------------------------------|-----------------------------------|-----------------------------------------|---------------------------------------------|---------------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions Peripheral <sup>(3)</sup>     |                                             | direction<br>(4)          | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

| D[5]  | PCR[53]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[53]<br>CS3<br>F[0]<br>SOUT         | SIUL<br>DSPI_0<br>FCU_0<br>DSPI_3           | I/O<br>O<br>O             | Slow    | Medium              | 22      | 33      |

| D[6]  | PCR[54]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[54]<br>CS2<br>SCK<br>—<br>FAULT[1] | SIUL<br>DSPI_0<br>DSPI_3<br>—<br>FlexPWM_0  | I/O<br>O<br>I/O<br>—<br>I | Slow    | Medium              | 23      | 34      |

| D[7]  | PCR[55]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[55]<br>CS3<br>F[1]<br>CS4<br>SIN   | SIUL<br>DSPI_1<br>FCU_0<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>O<br>I        | Slow    | Medium              | 26      | 37      |

| D[8]  | PCR[56]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[56]<br>CS2<br>—<br>CS5<br>FAULT[3] | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>FlexPWM_0  | I/O<br>O<br>—<br>O<br>I   | Slow    | Medium              | 21      | 32      |

| D[9]  | PCR[57]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>X[0]<br>TXD<br>—            | SIUL<br>FlexPWM_0<br>LIN_1<br>—             | I/O<br>I/O<br>O<br>—      | Slow    | Medium              | 15      | 26      |

| D[10] | PCR[58]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>A[0]<br>CS0<br>—            | SIUL<br>FlexPWM_0<br>DSPI_3<br>—            | I/O<br>O<br>I/O<br>—      | Slow    | Medium              | 53      | 76      |

| D[11] | PCR[59]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>CS1<br>SCK          | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>I/O      | Slow    | Medium              | 54      | 78      |

| D[12] | PCR[60]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD            | SIUL<br>FlexPWM_0<br>—<br>LIN_1             | I/O<br>I/O<br>—<br>I      | Slow    | Medium              | 70      | 99      |

| D[13] | PCR[61]                      | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>CS2<br>SOUT         | SIUL<br>FlexPWM_0<br>DSPI_3<br>DSPI_3       | I/O<br>O<br>O<br>O        | Slow    | Medium              | 67      | 95      |

### Table 7. Pin muxing (continued)

| Port  | Pad                          | Alternate                         |                                   |                              | I/O              | Pad s   | Pin No. |         |         |

|-------|------------------------------|-----------------------------------|-----------------------------------|------------------------------|------------------|---------|---------|---------|---------|

| pin   | configuration register (PCR) | (0)                               | Functions                         | Peripheral <sup>(3)</sup>    | direction<br>(4) | SRC = 0 | SRC = 1 | 100-pin | 144-pin |

| E[5]  | PCR[69]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[69]<br>—<br>—<br>AN[8]       | SIUL<br>—<br>—<br>ADC_0      | Input only       | _       | _       | _       | 44      |

| E[6]  | PCR[70]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[70]<br>—<br>—<br>—<br>AN[9]  | SIUL<br>—<br>—<br>—<br>ADC_0 | Input only       |         | _       | _       | 46      |

| E[7]  | PCR[71]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[71]<br>—<br>—<br>—<br>AN[10] | SIUL<br>—<br>—<br>—<br>ADC_0 | Input only       | _       | _       | _       | 48      |

| E[8]  | PCR[72]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[72]<br>—<br>—<br>—<br>AN[6]  | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only       | _       | _       | _       | 59      |

| E[9]  | PCR[73]                      | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[73]<br>—<br>—<br>—<br>AN[7]  | SIUL<br>—<br>—<br>ADC_1      | Input only       | _       | _       | _       | 61      |

| E[10] | PCR[74]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[74]<br>—<br>—<br>—<br>AN[8]  | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only       | -       | _       | _       | 63      |

| E[11] | PCR[75]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[75]<br>—<br>—<br>—<br>AN[9]  | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only       | _       | _       | _       | 65      |

| E[12] | PCR[76]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[76]<br>—<br>—<br>—<br>AN[10] | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only       | _       | _       | _       | 67      |

### Table 7. Pin muxing (continued)

# **3 Electrical characteristics**

### 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

**Caution:** All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

### 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

Table 8.Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

| Symbol                                 |    | Parameter                  | Conditions                    | Val | ue                        | Unit |     |  |

|----------------------------------------|----|----------------------------|-------------------------------|-----|---------------------------|------|-----|--|

| Symbol                                 |    | Parameter                  | Conditions                    | Min | Max <sup>(1)</sup>        | Unit |     |  |

| V <sub>SS_LV_CORx</sub> <sup>(4)</sup> | SR | Internal reference voltage | —                             | 0   | 0                         | V    |     |  |

| т                                      |    | Ambient temperature under  | f <sub>CPU</sub> = 64 MHz     | -40 | 105                       | °C   |     |  |

| I <sub>A</sub>                         |    |                            | bias f <sub>CPU</sub> = 60 MH |     | f <sub>CPU</sub> = 60 MHz | -40  | 125 |  |

#### Table 11. Recommended operating conditions (3.3 V) (continued)

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

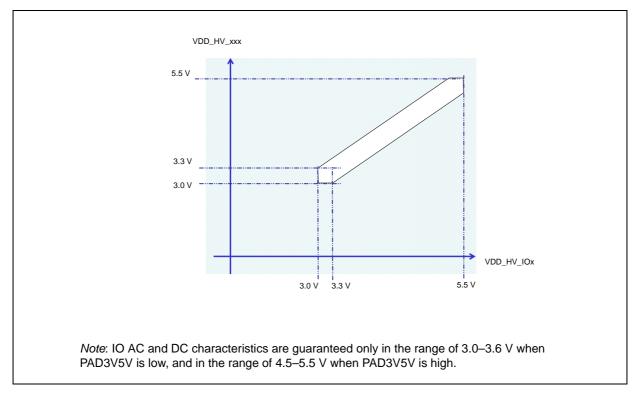

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_{-}HV_{-}IOy} - V_{DD_{-}HV_{-}IOx}| < 100 \text{ mV}.$

The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_ADC1</sub> - V<sub>DD\_HV\_ADC0</sub>| < 100 mV. As long as that condition is met, ADC\_0 and ADC\_1 can be operated at 5 V with the rest of the device operating at 3.3 V.</li>

4. To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an onchip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

5. The low voltage supplies ( $V_{DD_LV_xxx}$ ) are not all independent.

V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted.

$V_{DD_LV_REGCOR}$  and  $V_{DD_LV_REGCORx}$  are physically shorted internally, as are  $V_{SS_LV_REGCOR}$  and  $V_{SS_LV_CORx}$ .

*Figure 7* shows the constraints of the different power supplies.

#### Figure 7. Power supplies constraints (3.0 V $\leq$ V\_{DD\_HV\_IOx} $\leq$ 5.5 V)

Doc ID 14723 Rev 9

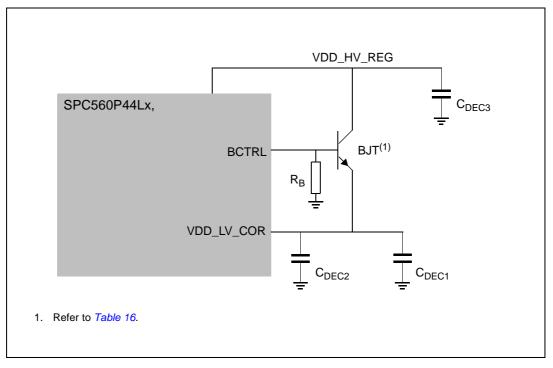

L<sub>Rea</sub>, see Table 17.

Note:

The voltage regulator output cannot be used to drive external circuits. Output pins are used only for decoupling capacitances.

$V_{DD\_LV\_COR}$  must be generated using internal regulator and external NPN transistor. It is not possible to provide  $V_{DD\_LV\_COR}$  through external regulator.

For the SPC560P44Lx, SPC560P50Lx microcontroller, capacitors, with total values not below  $C_{DEC1}$ , should be placed between  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  close to external ballast transistor emitter. 4 capacitors, with total values not below  $C_{DEC2}$ , should be placed close to microcontroller pins between each  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  supply pairs and the  $V_{DD\_LV\_REGCOR}/V_{SS\_LV\_REGCOR}$  pair . Additionally, capacitors with total values not below  $C_{DEC3}$ , should be placed between the  $V_{DD\_HV\_REG}/V_{SS\_HV\_REG}$  pins close to ballast collector. Capacitors values have to take into account capacitor accuracy, aging and variation versus temperature.

All reported information are valid for voltage and temperature ranges described in recommended operating condition, *Table 10* and *Table 11*.

#### Table 16. Approved NPN ballast components (configuration with resistor on base)

| Part  | Manufacturer | Approved derivatives <sup>(1)</sup> |  |  |

|-------|--------------|-------------------------------------|--|--|

|       | ON Semi      | BCP68                               |  |  |

| BCP68 | NXP          | BCP68-25                            |  |  |

|       | Infineon     | BCP68-25                            |  |  |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25          |  |  |

| BC868 | NXP          | BC868                               |  |  |

### **3.8.2** Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the  $V_{DD}$  and the  $V_{DD_{LV}}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ± 10 % range

- LVDLVCOR monitors low voltage digital power domain

| Symbol                   | с | Baramatar                                     | Conditions             | Va   | Unit  |      |

|--------------------------|---|-----------------------------------------------|------------------------|------|-------|------|

| Symbol                   | C | Parameter                                     | (1)                    | Min  | Max   | Unit |

| V <sub>PORH</sub>        | Т | Power-on reset threshold                      | —                      | 1.5  | 2.7   | V    |

| V <sub>PORUP</sub>       | Р | Supply for functional POR module              | T <sub>A</sub> = 25 °C | 1.0  | —     | V    |

| V <sub>REGLVDMOK_H</sub> | Р | Regulator low voltage detector high threshold | —                      | _    | 2.95  | V    |

| V <sub>REGLVDMOK_L</sub> | Р | Regulator low voltage detector low threshold  | —                      | 2.6  | —     | V    |

| V <sub>FLLVDMOK_H</sub>  | Р | Flash low voltage detector high threshold     | —                      | —    | 2.95  | V    |

| V <sub>FLLVDMOK_L</sub>  | Р | Flash low voltage detector low threshold      | —                      | 2.6  | —     | V    |

| V <sub>IOLVDMOK_H</sub>  | Р | I/O low voltage detector high threshold       | —                      | —    | 2.95  | V    |

| V <sub>IOLVDMOK_L</sub>  | Р | I/O low voltage detector low threshold        | —                      | 2.6  | —     | V    |

| V <sub>IOLVDM5OK_H</sub> | Р | I/O 5V low voltage detector high threshold    | —                      | _    | 4.4   | V    |

| V <sub>IOLVDM5OK_L</sub> | Р | I/O 5V low voltage detector low threshold     | —                      | 3.8  | —     | V    |

| V <sub>MLVDDOK_H</sub>   | Р | Digital supply low voltage detector high      | —                      | —    | 1.145 | V    |

| V <sub>MLVDDOK_L</sub>   | Р | Digital supply low voltage detector low       | —                      | 1.08 | —     | V    |

Table 19.

Low voltage monitor electrical characteristics

1. V\_{DD} = 3.3V  $\pm$  10% / 5.0V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

# 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the SPC560P44Lx, SPC560P50Lx implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct startup of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain). LVDs are gated low when POWER\_ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash

| Symbol  |    | с | Parameter                              | Condit                            | ions(1)                                       |                                | Value                                         |      | Unit |     |    |  |

|---------|----|---|----------------------------------------|-----------------------------------|-----------------------------------------------|--------------------------------|-----------------------------------------------|------|------|-----|----|--|

| Symbol  |    | C | Parameter Conditions <sup>(1)</sup>    |                                   |                                               | Min                            | Тур                                           | Max  | Unit |     |    |  |

|         |    |   |                                        | C <sub>L</sub> = 25 pF, 13 MHz    |                                               | —                              | —                                             | 6.6  |      |     |    |  |

|         |    |   |                                        | C <sub>L</sub> = 25 pF, 40 MHz    | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |                                |                                               | 13.4 |      |     |    |  |

|         | сс |   | Root medium square<br>I/O current for  | C <sub>L</sub> = 100 pF, 13 MHz   |                                               | _                              | _                                             | 18.3 | mA   |     |    |  |

| IRMSMED | CC | _ | MEDIUM                                 | C <sub>L</sub> = 25 pF, 13 MHz    |                                               | _                              | _                                             | 5    | mA   |     |    |  |

|         |    |   |                                        |                                   | configuration                                 | C <sub>L</sub> = 25 pF, 40 MHz | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _    | _    | 8.5 |    |  |

|         |    |   |                                        |                                   |                                               |                                | C <sub>L</sub> = 100 pF, 13 MHz               |      | _    | _   | 11 |  |

|         |    |   |                                        | C <sub>L</sub> = 25 pF, 40 MHz    |                                               | _                              | _                                             | 22   |      |     |    |  |

|         |    |   |                                        |                                   |                                               | C <sub>L</sub> = 25 pF, 64 MHz | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _    | _    | 33  |    |  |

|         | сс |   | Root medium square                     | C <sub>L</sub> = 100 pF, 40 MHz   |                                               | _                              | _                                             | 56   |      |     |    |  |

| IRMSFST | CC |   | I/O current for FAST configuration     | C <sub>L</sub> = 25 pF, 40 MHz    |                                               | _                              | _                                             | 14   | mA   |     |    |  |

|         |    |   |                                        | C <sub>L</sub> = 25 pF, 64 MHz    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |                                |                                               | 20   |      |     |    |  |

|         |    |   |                                        | C <sub>L</sub> = 100 pF, 40 MHz   |                                               |                                |                                               | 35   |      |     |    |  |

|         |    |   | Sum of all the static                  | V <sub>DD</sub> = 5.0 V ± 10%, P/ | AD3V5V = 0                                    | _                              | _                                             | 70   |      |     |    |  |

| AVGSEG  | SR |   | I/O current within a<br>supply segment | V <sub>DD</sub> = 3.3 V ± 10%, P/ | AD3V5V = 1                                    |                                |                                               | 65   | mA   |     |    |  |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

2. Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

### 3.11 Main oscillator electrical characteristics

The SPC560P44Lx, SPC560P50Lx provides an oscillator/resonator driver.

Table 28.Main oscillator output electrical characteristics (5.0 V,<br/>NVUSRO[PAD3V5V] = 0)

| Sum                | abol | C          | Parameter                               | Va      | Unit |      |  |

|--------------------|------|------------|-----------------------------------------|---------|------|------|--|

| Syn                | nbol | C Paramete |                                         | Min Max |      | Unit |  |

| fosc               | SR   | —          | Oscillator<br>frequency                 | 4       | 40   | MHz  |  |

| 9 <sub>m</sub>     | _    | Р          | Transconduc<br>tance                    | 6.5     | 25   | mA/V |  |

| V <sub>OSC</sub>   | _    | Т          | Oscillation<br>amplitude on<br>XTAL pin | 1       | _    | V    |  |

| t <sub>oscsu</sub> | —    | Т          | Start-up<br>time <sup>(1),(2)</sup>     | 8       | _    | ms   |  |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of XTAL

# 3.13 16 MHz RC oscillator electrical characteristics

| Symbol                      | с | Baramatar                                                                                                                                             | Conditions             |     | Unit |     |      |

|-----------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| Symbol                      | C | Parameter                                                                                                                                             | Conditions             | Min | Тур  | Max | Unit |

| f <sub>RC</sub>             | Ρ | RC oscillator frequency                                                                                                                               | T <sub>A</sub> = 25 °C |     | 16   |     | MHz  |

| $\Delta_{ m RCMVAR}$        | Ρ | Fast internal RC oscillator variation over temperature<br>and<br>supply with respect to $f_{RC}$ at $T_A = 25$ °C in high-<br>frequency configuration | _                      | -5  | _    | 5   | %    |

| $\Delta_{\rm RCMTRIM}$      | Т | Post Trim Accuracy: The variation of the PTF <sup>(1)</sup> from the 16 MHz                                                                           | T <sub>A</sub> = 25 °C | -1  |      | 1   | %    |

| $\Delta_{\mathrm{RCMSTEP}}$ | Т | Fast internal RC oscillator trimming step                                                                                                             | T <sub>A</sub> = 25 °C | —   | 1.6  | _   | %    |

#### Table 32. 16 MHz RC oscillator electrical characteristics

1. PTF = Post Trimming Frequency: The frequency of the output clock after trimming at typical supply voltage and temperature

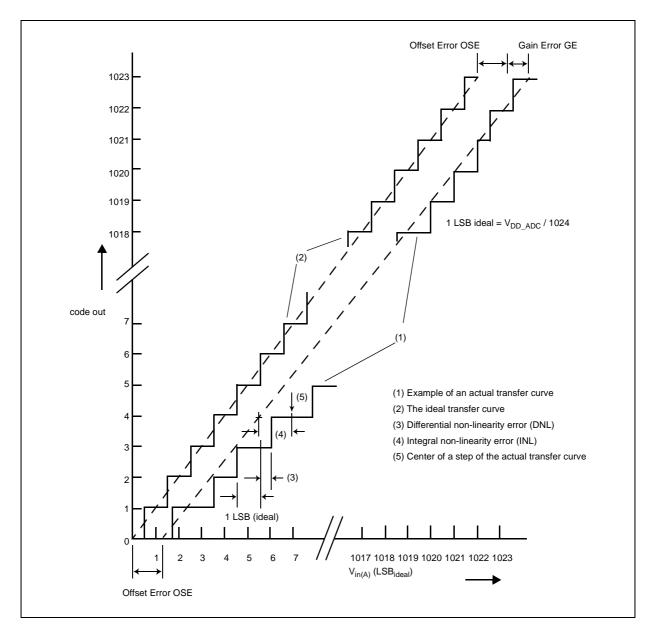

# 3.14 Analog-to-digital converter (ADC) electrical characteristics

The device provides a 10-bit successive approximation register (SAR) analog-to-digital converter.

### 3.14.1 Input impedance and ADC accuracy

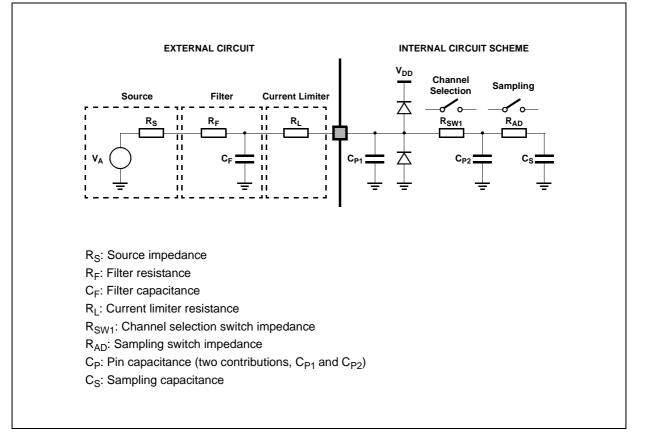

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{P2}$  being substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc \times (C_S+C_{P2}))$ ), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the *Equation 4*:

#### **Equation 4**

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

*Equation 4* generates a constraint for external network design, in particular on resistive path.

Figure 16. Input equivalent circuit

| Sumb               | Symbol |   | Parameter Conditions <sup>(1)</sup>                                                                           |                                                                       |                                                                      | Value |     |        |  |

|--------------------|--------|---|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|-------|-----|--------|--|

|                    |        | С | Parameter                                                                                                     | Conditions                                                            | Min                                                                  | Тур   | Max | - Unit |  |

|                    |        |   |                                                                                                               | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | —                                                                    | —     | 10  |        |  |

|                    |        |   |                                                                                                               | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _                                                                    | _     | 20  |        |  |

| +                  | сс     | П | Output transition time<br>output pin <sup>(3)</sup>                                                           | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _                                                                    | _     | 40  | ns     |  |

| t <sub>tr</sub>    |        |   | MEDIUM configuration                                                                                          | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _                                                                    | —     | 12  | 115    |  |

|                    |        |   |                                                                                                               |                                                                       | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _     | —   | 25     |  |

|                    |        |   |                                                                                                               | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _                                                                    | _     | 40  |        |  |

| W <sub>FRST</sub>  | SR     | Ρ | RESET input filtered pulse                                                                                    | _                                                                     | _                                                                    | _     | 40  | ns     |  |

| W <sub>NFRST</sub> | SR     | Ρ | RESET input not<br>filtered pulse                                                                             | _                                                                     | 500                                                                  | —     | _   | ns     |  |

| t <sub>POR</sub>   | сс     | D | Maximum delay before<br>internal reset is<br>released after all<br>V <sub>DD_HV</sub> reach nominal<br>supply | Monotonic V <sub>DD_HV</sub> supply ramp                              | _                                                                    | _     | 1   | ms     |  |

|                    |        |   |                                                                                                               | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                            | 10                                                                   | —     | 150 |        |  |

| I <sub>WPU</sub>   | сс     | Ρ | Weak pull-up current<br>absolute value                                                                        | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                            | 10                                                                   | _     | 150 | μA     |  |

|                    |        |   |                                                                                                               | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(4)</sup>             | 10                                                                   | —     | 250 |        |  |

| Table 38. | <b>RESET</b> electrical characteristics | (continued) | ) |

|-----------|-----------------------------------------|-------------|---|

|           |                                         |             |   |

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

2. This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of device reference manual).

3.  $C_L$  includes device and package capacitance ( $C_{PKG}$  < 5 pF).

4. The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

# 3.17.2 IEEE 1149.1 interface timing

| Table 39. | JTAG pin AC electrical characteristics |

|-----------|----------------------------------------|

|-----------|----------------------------------------|

| No. | Symbo                                                    | Symbol |   | Symbol C                                               |            | Parameter | Conditions | Value |  | Unit |

|-----|----------------------------------------------------------|--------|---|--------------------------------------------------------|------------|-----------|------------|-------|--|------|

| NO. | Symbo                                                    | •      |   | Falameter                                              | Conditions | Min       | Max        | Unit  |  |      |

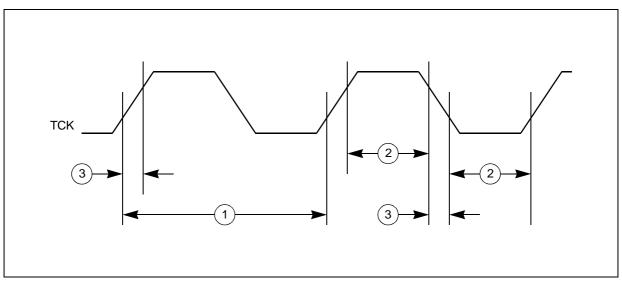

| 1   | t <sub>JCYC</sub>                                        | CC     | D | TCK cycle time                                         | —          | 100       | —          | ns    |  |      |

| 2   | t <sub>JDC</sub>                                         | СС     | D | TCK clock pulse width (measured at $V_{DD_HV_IOX}/2$ ) | —          | 40        | 60         | ns    |  |      |

| 3   | t <sub>TCKRISE</sub>                                     | CC     | D | TCK rise and fall times (40% – 70%)                    | —          | —         | 3          | ns    |  |      |

| 4   | t <sub>TMSS</sub> , t <sub>TDIS</sub> CC D TMS, TDI data |        | D | TMS, TDI data setup time                               | —          | 5         | —          | ns    |  |      |

| No. | Symbo                                 | Sumbal 0 Decemptor |                    | Conditions                                                | Value      |     | Unit |      |

|-----|---------------------------------------|--------------------|--------------------|-----------------------------------------------------------|------------|-----|------|------|

| NO. | 5. Symbol                             |                    | Symbol C Parameter |                                                           | Conditions | Min | Max  | Unit |

| 5   | t <sub>TMSH</sub> , t <sub>TDIH</sub> | CC                 | D                  | TMS, TDI data hold time                                   | —          | 25  | —    | ns   |

| 6   | t <sub>TDOV</sub>                     | СС                 | D                  | TCK low to TDO data valid                                 | —          |     | 40   | ns   |

| 7   | t <sub>TDOI</sub>                     | CC                 | D                  | TCK low to TDO data invalid                               | —          | 0   | —    | ns   |

| 8   | t <sub>TDOHZ</sub>                    | CC                 | D                  | TCK low to TDO high impedance                             | _          | 40  | —    | ns   |

| 11  | t <sub>BSDV</sub>                     | CC                 | D                  | TCK falling edge to output valid                          | —          |     | 50   | ns   |

| 12  | t <sub>BSDVZ</sub>                    | СС                 | D                  | TCK falling edge to output valid out of high<br>impedance | _          | _   | 50   | ns   |

| 13  | t <sub>BSDHZ</sub>                    | CC                 | D                  | TCK falling edge to output high impedance                 | —          |     | 50   | ns   |

| 14  | t <sub>BSDST</sub>                    | CC                 | D                  | Boundary scan input valid to TCK rising edge              |            | 50  | _    | ns   |

| 15  | t <sub>BSDHT</sub>                    | CC                 | D                  | TCK rising edge to boundary scan input invalid            | _          | 50  | —    | ns   |

Table 39.

JTAG pin AC electrical characteristics (continued)

Figure 22. JTAG test clock input timing

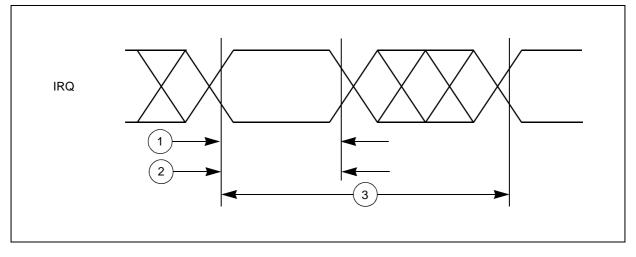

### Figure 28. External interrupt timing

# 3.17.5 DSPI timing

# Table 42.DSPI timing<sup>(1)</sup>

| Na  | o. Symbol           |     | Symbol |                               | Cumbel.                                       |                        | Cumbel                 |            | Symbol |  | с | Devementer | Conditions | Va | lue | Unit |

|-----|---------------------|-----|--------|-------------------------------|-----------------------------------------------|------------------------|------------------------|------------|--------|--|---|------------|------------|----|-----|------|

| No. | Sym                 | 100 | C      | Parameter                     |                                               |                        | Max                    | Unit       |        |  |   |            |            |    |     |      |

| 1   | +                   | сс  | D      | DSPI cycle time               | Master (MTFE = 0)                             | 60                     | _                      | 20         |        |  |   |            |            |    |     |      |

|     | t <sub>SCK</sub>    | CC  | D      |                               | Slave (MTFE = 0)                              | 60                     |                        | ns         |        |  |   |            |            |    |     |      |

| 2   | t <sub>CSC</sub>    | CC  | D      | CS to SCK delay               | —                                             | 16                     |                        | ns         |        |  |   |            |            |    |     |      |

| 3   | t <sub>ASC</sub>    | СС  | D      | After SCK delay               | —                                             | 26                     |                        | ns         |        |  |   |            |            |    |     |      |

| 4   | t <sub>SDC</sub>    | CC  | D      | SCK duty cycle                | —                                             | 0.4 * t <sub>SCK</sub> | 0.6 * t <sub>SCK</sub> | ns         |        |  |   |            |            |    |     |      |

| 5   | t <sub>A</sub>      | СС  | D      | Slave access time             | SS active to SOUT valid                       | —                      | 30                     | ns         |        |  |   |            |            |    |     |      |

| 6   | t <sub>DIS</sub>    | сс  | D      | Slave SOUT disable time       | SS inactive to SOUT high impedance or invalid | _                      | 16                     | ns         |        |  |   |            |            |    |     |      |

| 7   | t <sub>PCSC</sub>   | CC  | D      | PCSx to PCSS time             | —                                             | 13                     |                        | ns         |        |  |   |            |            |    |     |      |

| 8   | t <sub>PASC</sub>   | СС  | D      | PCSS to PCSx time             | —                                             | 13                     | -                      | ns         |        |  |   |            |            |    |     |      |

|     |                     |     |        |                               | Master (MTFE = 0)                             | 35                     |                        |            |        |  |   |            |            |    |     |      |

| 9   | +                   | сс  | D      | Data active times for insuit- | Slave                                         | 4                      |                        | ns         |        |  |   |            |            |    |     |      |

| 9   | t <sub>SUI</sub>    |     |        | Data setup time for inputs    | Master (MTFE = 1, CPHA = 0)                   | 35                     | -                      |            |        |  |   |            |            |    |     |      |

|     |                     |     |        |                               | Master (MTFE = 1, CPHA = 1)                   | 35                     | _                      |            |        |  |   |            |            |    |     |      |

|     |                     |     |        |                               | Master (MTFE = 0)                             | -5                     | _                      |            |        |  |   |            |            |    |     |      |

| 10  | ÷                   | сс  | D      | Data hold time for inputs     | Slave                                         | 4                      | _                      | <b>n</b> 0 |        |  |   |            |            |    |     |      |

| 10  | 0 t <sub>HI</sub> C |     | U      | Data hold time for inputs     | Master (MTFE = 1, CPHA = 0)                   | 11                     | _                      | ns         |        |  |   |            |            |    |     |      |

|     |                     |     |        |                               | Master (MTFE = 1, CPHA = 1)                   | -5                     |                        |            |        |  |   |            |            |    |     |      |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 27-Oct-2009 | 5        | <ul> <li>Added "Full Feature" and "Airbag" customization.</li> <li>Removed B[4] and B[5] rows from "Pin muxing" table and inserted them on "System pins" table.</li> <li>Updated package pinout.</li> <li>Rewrote entirely section "Power Up/dpwn Sequencing" section.</li> <li>Renamend "V<sub>DD_LV</sub>_PLL" and "V<sub>SS_LV</sub>_PLL" supply pins with respectively "V<sub>DD_LV</sub>_COR3" and "V<sub>SS_LV</sub>_COR3".</li> <li>Added explicative figures on "Electrical characteristics" section.</li> <li>Updated "Thermal characteristics" for 100-pin.</li> <li>Proposed two different configuration of "voltage regulator Inserted Power Up/Down sequence.</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added "I/O pad current specification" section.</li> <li>Renamed the "Airbag mode" with "Typical mode"and updated the values on "supply current" tables.</li> <li>Added more order code.</li> </ul>                                         |  |  |  |

| 06-Apr-2010 | 6        | Inserted label of Y-axis in the "Independent ADC supply" figure.<br>"Recommended Operating Conditions" tables:<br>Moved the T <sub>J</sub> row to "Absolute Maximum Ratings" table.<br>Rewrite note 1 and 3<br>Inverted Min a Typ value of C <sub>DEC2</sub> on "Voltage Regulator Electrical Characteristics" table.<br>Removed an useless duplicate of "Voltage Regulator Electrical Characteristics" table.<br>Inserted the name of C <sub>S</sub> into "Input Equivalent Circuit" figure.<br>Removed leakage Ivpp from datasheet.<br>Updated "Supply Current" tables.<br>Added note on "Output pin transition times" table.<br>Updated "Temperature Sensor Electrical Characteristics" table.<br>Updated "16 MHz RC Oscillator Electrical Characteristics" table.<br>Removed the note about the condition from "Flash read access timing" table.<br>Removed the notes that assert the values need to be confirmed before validation.                                                                                                                                     |  |  |  |

| 07-Apr-2011 | 7        | <ul> <li>Formatting and editorial changes throughout<br/>Removed all content referencing Junction Temperature Sensor<br/>Cover page Features:</li> <li>CPU core—specified 64 MHz frequency</li> <li>updated memory features</li> <li>eTimer units: changed "up/down capabilities" to "up/down count capabilities"</li> <li>ADC—changed "2 × 13 input channels" to "2 × 11 input channels, + 4 shared channels"</li> <li>replaced "On-chip CAN/UART/FlexRay bootstrap loader" with "On-chip CAN/UART<br/>bootstrap loader"</li> <li>Section 1: Introduction: changed title (was: Overview); reorganized contents<br/>SPC560P44Lx, SPC560P50Lx device comparison:</li> <li>ADC feature: changed "16 channels" to "15-channel"; added footnote to to indicate that<br/>four channels are shared between the two ADCs</li> <li>removed SPC560P40 column</li> <li>changed "dual channel" to "selectable single or dual channel support" in FlexRay<br/>footnote</li> <li>updated "eTimer" feature</li> <li>updated footnote relative to "Digital power supply" feature</li> </ul> |  |  |  |

Table 46.

Revision history (continued)