#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 107                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p50l5beaar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 1.5.29   | Nexus development interface (NDI)                                   |

|---|--------|----------|---------------------------------------------------------------------|

|   |        | 1.5.30   | Cyclic redundancy check (CRC)27                                     |

|   |        | 1.5.31   | IEEE 1149.1 JTAG controller                                         |

|   |        | 1.5.32   | On-chip voltage regulator (VREG) 28                                 |

| 2 | Packa  | age pinc | outs and signal descriptions                                        |

|   | 2.1    | Package  | e pinouts                                                           |

|   | 2.2    | Pin dese | cription                                                            |

|   |        | 2.2.1    | Power supply and reference voltage pins                             |

|   |        | 2.2.2    | System pins                                                         |

|   |        | 2.2.3    | Pin muxing                                                          |

| 3 | Electr | ical cha | aracteristics                                                       |

|   | 3.1    | Introduc | tion                                                                |

|   | 3.2    | Parame   | ter classification                                                  |

|   | 3.3    | Absolute | e maximum ratings                                                   |

|   | 3.4    | Recomr   | nended operating conditions 53                                      |

|   | 3.5    | Therma   | l characteristics                                                   |

|   |        | 3.5.1    | Package thermal characteristics                                     |

|   |        | 3.5.2    | General notes for specifications at maximum junction temperature 57 |

|   | 3.6    | Electron | nagnetic interference (EMI) characteristics                         |

|   | 3.7    | Electros | tatic discharge (ESD) characteristics                               |

|   | 3.8    | Power n  | nanagement electrical characteristics                               |

|   |        | 3.8.1    | Voltage regulator electrical characteristics                        |

|   |        | 3.8.2    | Voltage monitor electrical characteristics                          |

|   | 3.9    | Power u  | ıp/down sequencing 63                                               |

|   | 3.10   | DC elec  | trical characteristics                                              |

|   |        | 3.10.1   | NVUSRO register                                                     |

|   |        | 3.10.2   | DC electrical characteristics (5 V)                                 |

|   |        | 3.10.3   | DC electrical characteristics (3.3 V)                               |

|   |        | 3.10.4   | Input DC electrical characteristics definition                      |

|   |        | 3.10.5   | I/O pad current specification70                                     |

|   | 3.11   | Main os  | cillator electrical characteristics                                 |

|   | 3.12   | FMPLL    | electrical characteristics                                          |

|   | 3.13   | 16 MHz   | RC oscillator electrical characteristics                            |

### 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The PLL has the following major features:

- Input clock frequency: 4–40 MHz

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the PLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

#### 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

#### 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- ±5% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

### 1.5.12 Periodic interrupt timer (PIT)

The PIT module implements these features:

- 4 general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

The sources of the ECC errors are:

- Flash memory

- SRAM

### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

### 1.5.20 Controller area network (FlexCAN)

The SPC560P44Lx, SPC560P50Lx MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

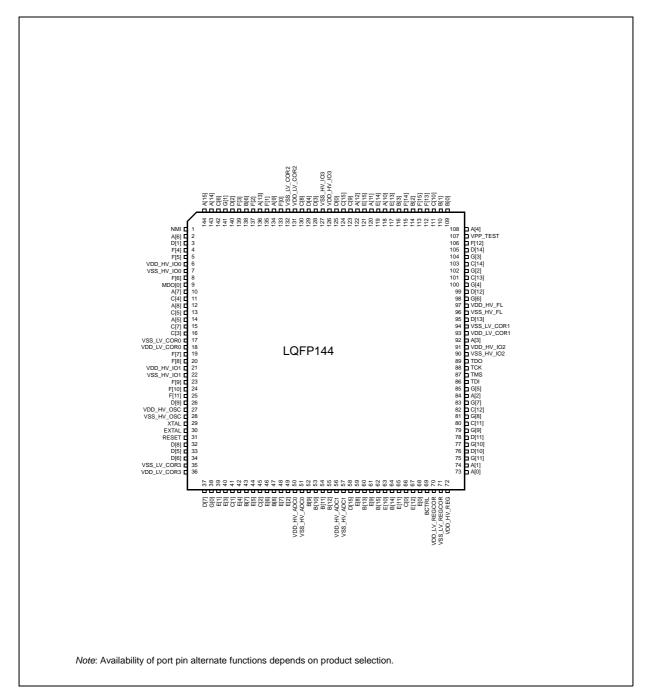

# 2 Package pinouts and signal descriptions

# 2.1 Package pinouts

The LQFP pinouts are shown in the following figures.

Figure 2. 144-pin LQFP pinout – Full featured configuration (top view)

|                         | Supply                                                                                                                                     | Pin     |         |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--|

| Symbol                  | Description                                                                                                                                | 100-pin | 144-pin |  |

| V <sub>DD_LV_COR1</sub> | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{\rm SS\_LV\_COR}$ pin. | 65      | 93      |  |

| V <sub>SS_LV_COR1</sub> | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD\_LV\_COR}$ pin.     | 66      | 94      |  |

| V <sub>DD_LV_COR2</sub> | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{\rm SS\_LV\_COR}$ pin. | 92      | 131     |  |

| V <sub>SS_LV_COR2</sub> | 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD\_LV\_COR}$ pin.     | 93      | 132     |  |

| V <sub>DD_LV_COR3</sub> | 1.2 V Decoupling pins for on-chip PLL modules. Decoupling capacitor must be connected between this pin and $V_{SS\_LV\_COR3}$ .            | 25      | 36      |  |

| V <sub>SS_LV_COR3</sub> | 1.2 V Decoupling pins for on-chip PLL modules. Decoupling capacitor must be connected between this pin and $V_{DD_LV_COR3}$ .              | 24      | 35      |  |

#### Table 5. Supply pins (continued)

Analog supply/ground and high/low reference lines are internally physically separate, but are shorted via a double-bonding connection on V<sub>DD\_HV\_ADCx</sub>/V<sub>SS\_HV\_ADCx</sub> pins.

2. Not available on 100-pin package.

### 2.2.2 System pins

*Table 5* and *Table 6* contain information on pin functions for the SPC560P44Lx, SPC560P50Lx devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective Pad Configuration Register (PCR) values.

#### Table 6. System pins

| Symbol | Description                                                                                                                                                                               | Direction        | Pad sp      | beed <sup>(1)</sup> | Pin     |         |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|---------------------|---------|---------|--|

| Symbol | Description                                                                                                                                                                               | Direction        | SRC = 0     | SRC = 1             | 100-pin | 144-pin |  |

|        | Dedicated pins. Available                                                                                                                                                                 | on 100-pin and 1 | 44-pin pack | kage.               |         |         |  |

| MDO[0] | Nexus Message Data Output—line 0                                                                                                                                                          | Output only      | Fa          | ist                 | —       | 9       |  |

| NMI    | Non-Maskable Interrupt                                                                                                                                                                    | Input only       | Slow        | —                   | 1       | 1       |  |

| XTAL   | Analog output of the oscillator amplifier<br>circuit; needs to be grounded if oscillator<br>is used in bypass mode                                                                        | _                | _           | _                   | 18      | 29      |  |

| EXTAL  | <ul> <li>Analog input of oscillator amplifier<br/>circuit, when oscillator not in bypass<br/>mode</li> <li>Analog input for clock generator when<br/>oscillator in bypass mode</li> </ul> | _                | _           | _                   | 19      | 30      |  |

| Port  | Pad                          | Alternate                       |           |                           | I/O              | Pad s   | beed <sup>(5)</sup> |         | No.     |

|-------|------------------------------|---------------------------------|-----------|---------------------------|------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup><br>(2) | Functions | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

|       |                              | ALT0                            | GPIO[7]   | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | SOUT      | DSPI_1                    | 0                |         |                     |         |         |

| A[7]  | PCR[7]                       | ALT2                            | —         | —                         | —                | Slow    | Medium              | 4       | 10      |

|       |                              | ALT3                            | —         | _                         | —                |         |                     |         |         |

|       |                              | —                               | EIRQ[7]   | SIUL                      | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[8]   | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            |           | _                         | _                |         |                     |         |         |

| 101   |                              | ALT2                            | —         | —                         | _                | Slow    | Medium              | 6       | 12      |

| A[8]  | PCR[8]                       | ALT3                            | —         | —                         | —                | 510W    | weatum              | 6       | 12      |

|       |                              | —                               | SIN       | DSPI_1                    | I                |         |                     |         |         |

|       |                              | —                               | EIRQ[8]   | SIUL                      | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[9]   | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | CS1       | DSPI_2                    | 0                |         |                     |         |         |

| A[9]  | PCR[9]                       | ALT2                            | —         | _                         | _                | Slow    | Medium              | 94      | 134     |

|       |                              | ALT3                            | B[3]      | FlexPWM_0                 | 0                |         |                     |         |         |

|       |                              | —                               | FAULT[0]  | FlexPWM_0                 | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[10]  | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | CS0       | DSPI_2                    | I/O              |         |                     |         |         |

| A[10] | PCR[10]                      | ALT2                            | B[0]      | FlexPWM_0                 | 0                | Slow    | Medium              | 81      | 118     |

|       |                              | ALT3                            | X[2]      | FlexPWM_0                 | I/O              |         |                     |         |         |

|       |                              | —                               | EIRQ[9]   | SIUL                      | I                |         |                     |         |         |

| -     |                              | ALT0                            | GPIO[11]  | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | SCK       | DSPI_2                    | I/O              |         |                     |         |         |

| A[11] | PCR[11]                      | ALT2                            | A[0]      | FlexPWM_0                 | 0                | Slow    | Medium              | 82      | 120     |

|       |                              | ALT3                            | A[2]      | FlexPWM_0                 | 0                |         |                     |         |         |

|       |                              | —                               | EIRQ[10]  | SIUL                      | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[12]  | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | SOUT      | DSPI_2                    | 0                |         |                     |         |         |

| A[12] | PCR[12]                      | ALT2                            | A[2]      | FlexPWM_0                 | 0                | Slow    | Medium              | 83      | 122     |

|       |                              | ALT3                            | B[2]      | FlexPWM_0                 | 0                |         |                     |         |         |

|       |                              | —                               | EIRQ[11]  | SIUL                      | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[13]  | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | —         | _                         | —                |         |                     |         |         |

|       |                              | ALT2                            | B[2]      | FlexPWM_0                 | 0                |         |                     |         |         |

| A[13] | PCR[13]                      | ALT3                            | —         | —                         | —                | Slow    | Medium              | 95      | 136     |

|       |                              | —                               | SIN       | DSPI_2                    | I                |         |                     |         |         |

|       |                              | —                               | FAULT[0]  | FlexPWM_0                 | I                |         |                     |         |         |

|       |                              | —                               | EIRQ[12]  | SIUL                      | I                |         |                     |         |         |

### Table 7. Pin muxing (continued)

| Symbol                                 |    | Parameter                  | Conditions                | Value |                    |      |  |

|----------------------------------------|----|----------------------------|---------------------------|-------|--------------------|------|--|

| Symbol                                 |    | Parameter                  | Conditions                | Min   | Max <sup>(1)</sup> | Unit |  |

| V <sub>SS_LV_CORx</sub> <sup>(4)</sup> | SR | Internal reference voltage | —                         | 0     | 0                  | V    |  |

| т с                                    | сD | Ambient temperature under  | f <sub>CPU</sub> = 64 MHz | -40   | 105                | °C   |  |

| 'A                                     |    | f <sub>CPU</sub> = 60 MHz  | -40                       | 125   |                    |      |  |

#### Table 11. Recommended operating conditions (3.3 V) (continued)

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_{-}HV_{-}IOy} - V_{DD_{-}HV_{-}IOx}| < 100 \text{ mV}.$

The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_ADC1</sub> - V<sub>DD\_HV\_ADC0</sub>| < 100 mV. As long as that condition is met, ADC\_0 and ADC\_1 can be operated at 5 V with the rest of the device operating at 3.3 V.</li>

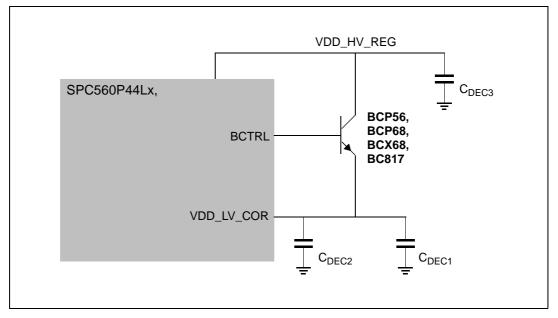

4. To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an onchip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

5. The low voltage supplies ( $V_{DD_LV_xxx}$ ) are not all independent.

V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted.

$V_{DD_LV_REGCOR}$  and  $V_{DD_LV_REGCORx}$  are physically shorted internally, as are  $V_{SS_LV_REGCOR}$  and  $V_{SS_LV_CORx}$ .

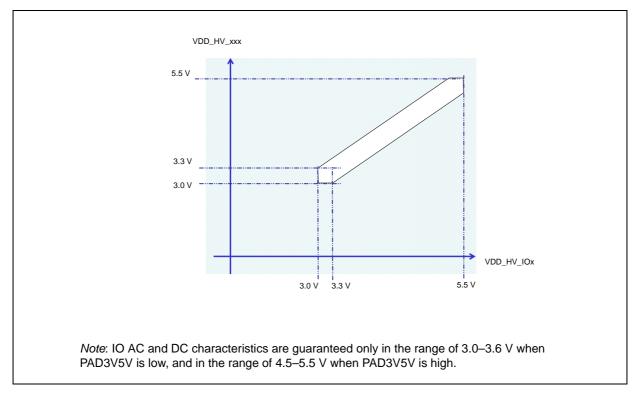

*Figure 7* shows the constraints of the different power supplies.

#### Figure 7. Power supplies constraints (3.0 V $\leq$ V\_{DD\_HV\_IOx} $\leq$ 5.5 V)

| Part  | Manufacturer | Approved derivatives <sup>(1)</sup> |

|-------|--------------|-------------------------------------|

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;          |

| BCOTT | NXP          | BC817-16;BC817-25                   |

|       | ST           | BCP56-16                            |

| BCP56 | Infineon     | BCP56-10;BCP56-16                   |

| BCF50 | ON Semi      | BCP56-10                            |

|       | NXP          | BCP56-10;BCP56-16                   |

#### Table 16. Approved NPN ballast components (configuration with resistor on base)

1. For automotive applications please check with the appropriate transistor vendor for automotive grade certification

| Symbol                    |    | с | Parameter                                                                       | Conditions                                                                                                                                        |      | Value |      | Unit                                |      |    |  |

|---------------------------|----|---|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------------------------------------|------|----|--|

| Symbol                    |    | C | Faiameter                                                                       | Conditions                                                                                                                                        | Min  | Тур   | Max  | Onit                                |      |    |  |

| V <sub>DD_LV_REGCOR</sub> | сс | Ρ | Output voltage under<br>maximum load run supply<br>current configuration        | Post-trimming                                                                                                                                     | 1.15 | _     | 1.32 | V                                   |      |    |  |

| R <sub>B</sub>            | SR | — | External resistance on bipolar junction transistor (BJT) base                   | _                                                                                                                                                 | 18   | _     | 22   | kΩ                                  |      |    |  |

| C <sub>DEC1</sub> SF      | SR | _ | External decoupling/stability ceramic capacitor                                 | BJT from <i>Table 16</i> . 3<br>capacitances (i.e. X7R or<br>X8R capacitors) with nominal<br>value of 10 µF                                       | 19.5 | 30    | _    | μF                                  |      |    |  |

|                           |    |   |                                                                                 |                                                                                                                                                   |      |       |      | BJT BC817, one capacitance of 22 μF | 14.3 | 22 |  |

|                           | SR |   | Resulting ESR of all three capacitors of C <sub>DEC1</sub>                      | BJT from <i>Table 16</i> . 3x10 μF.<br>Absolute maximum value<br>between 100 kHz and<br>10 MHz                                                    | _    | _     | 50   | mΩ                                  |      |    |  |

| R <sub>REG</sub>          | эк | _ | Resulting ESR of the unique capacitor C <sub>DEC1</sub>                         | BJT BC817, 1x 22 µF.<br>Absolute maximum value<br>between 100 kHz and<br>10 MHz                                                                   | 10   | _     | 40   | mΩ                                  |      |    |  |

| C <sub>DEC2</sub>         | SR | _ | External decoupling/stability ceramic capacitor                                 | 4 capacitances (i.e. X7R or<br>X8R capacitors) with nominal<br>value of 440 nF                                                                    | 1200 | 1760  | _    | nF                                  |      |    |  |

| C <sub>DEC3</sub>         | SR |   | External decoupling/stability<br>ceramic capacitor on<br>V <sub>DD_HV_REG</sub> | 3 capacitances (i.e. X7R or X8R capacitors) with nominal value of 10 $\mu$ F; C <sub>DEC3</sub> has to be equal or greater than C <sub>DEC1</sub> | 19.5 | 30    | _    | μF                                  |      |    |  |

| L <sub>Reg</sub>          | SR | — | Resulting ESL of V_DD_HV_REG BCTRL and V_DD_LV_CORx pins                        |                                                                                                                                                   | _    |       | 15   | nH                                  |      |    |  |

#### Table 17. Voltage regulator electrical characteristics (configuration with resistor on base)

Figure 10. Configuration without resistor on base

| Table 18. | Voltage | e reg | gulator electrical characteri | stics (configuration withou | ut resistor on bas | se) |

|-----------|---------|-------|-------------------------------|-----------------------------|--------------------|-----|

|           |         |       |                               |                             |                    |     |

| Symbol                    |    | с | Parameter                                                                | Conditions                                              |      | Unit |      |      |

|---------------------------|----|---|--------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| Symbol                    |    | C | Falameter                                                                | Conditions                                              | Min  | Тур  | Max  | Unit |

| V <sub>DD_LV_REGCOR</sub> | сс | Ρ | Output voltage under<br>maximum load run supply<br>current configuration | Post-trimming                                           | 1.15 | _    | 1.32 | V    |

| C <sub>DEC1</sub>         | SR | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances                                          | 40   | 56   | _    | μF   |

| R <sub>REG</sub>          | SR |   | Resulting ESR of all four<br>C <sub>DEC1</sub>                           | Absolute maximum value<br>between 100 kHz and<br>10 MHz | Ι    |      | 45   | mΩ   |

| C <sub>DEC2</sub>         | SR | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances of 100 nF<br>each                        | 400  | _    | _    | nF   |

| C <sub>DEC3</sub>         | SR |   | External decoupling/stability<br>ceramic capacitor on<br>VDD_HV_REG      | _                                                       | 40   |      | _    | μF   |

| L <sub>Reg</sub>          | SR |   | Resulting ESL of V_DD_HV_REG BCTRL and V_DD_LV_CORx pins                 | —                                                       |      |      | 15   | nH   |

#### **3.8.2** Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the  $V_{DD}$  and the  $V_{DD_{LV}}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ± 10 % range

- LVDLVCOR monitors low voltage digital power domain

| Symbol                   | с | Baramatar                                     | Conditions             | Va   | Unit  |      |

|--------------------------|---|-----------------------------------------------|------------------------|------|-------|------|

| Symbol                   | C | Parameter                                     | (1)                    | Min  | Max   | Unit |

| V <sub>PORH</sub>        | Т | Power-on reset threshold                      | —                      | 1.5  | 2.7   | V    |

| V <sub>PORUP</sub>       | Р | Supply for functional POR module              | T <sub>A</sub> = 25 °C | 1.0  | —     | V    |

| V <sub>REGLVDMOK_H</sub> | Р | Regulator low voltage detector high threshold | —                      | —    | 2.95  | V    |

| V <sub>REGLVDMOK_L</sub> | Р | Regulator low voltage detector low threshold  | —                      | 2.6  | —     | V    |

| V <sub>FLLVDMOK_H</sub>  | Р | Flash low voltage detector high threshold     | —                      | —    | 2.95  | V    |

| V <sub>FLLVDMOK_L</sub>  | Р | Flash low voltage detector low threshold      | —                      | 2.6  | —     | V    |

| V <sub>IOLVDMOK_H</sub>  | Р | I/O low voltage detector high threshold       | —                      | —    | 2.95  | V    |

| V <sub>IOLVDMOK_L</sub>  | Р | I/O low voltage detector low threshold        | —                      | 2.6  | —     | V    |

| V <sub>IOLVDM5OK_H</sub> | Р | I/O 5V low voltage detector high threshold    | —                      | —    | 4.4   | V    |

| V <sub>IOLVDM5OK_L</sub> | Р | I/O 5V low voltage detector low threshold     | —                      | 3.8  | —     | V    |

| V <sub>MLVDDOK_H</sub>   | Р | Digital supply low voltage detector high      | —                      | —    | 1.145 | V    |

| V <sub>MLVDDOK_L</sub>   | Р | Digital supply low voltage detector low       | —                      | 1.08 | —     | V    |

Table 19.

Low voltage monitor electrical characteristics

1. V\_{DD} = 3.3V  $\pm$  10% / 5.0V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

# 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the SPC560P44Lx, SPC560P50Lx implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct startup of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain). LVDs are gated low when POWER\_ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash

| Symbol                | с |                | Parameter                                   | Conditions                                                    |        | Va    | Unit  |     |

|-----------------------|---|----------------|---------------------------------------------|---------------------------------------------------------------|--------|-------|-------|-----|

| Symbol                | C |                | Farameter                                   | Conditions                                                    |        | Тур   | Max   | onn |

|                       |   |                | RUN—Maximum mode <sup>(1)</sup>             |                                                               | 40 MHz | 62    | 77    |     |

|                       | т |                |                                             | V <sub>DD_LV_CORx</sub>                                       | 64 MHz | 71    | 89    |     |

|                       | 1 |                | RUN—Typical mode <sup>(2)</sup>             | externally forced at 1.3 V                                    | 40 MHz | 45    | 56    |     |

|                       |   |                | KON—Typical mode                            |                                                               | 64 MHz | 53    | 66    |     |

| IDD_LV_CORX           |   |                | RUN—Maximum mode <sup>(3)</sup>             | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | 64 MHz | 60    | 75    |     |

|                       | Ρ | ent            | HALT mode <sup>(4)</sup>                    | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1.5   | 10    |     |

|                       |   | Supply current | STOP mode <sup>(5)</sup>                    | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1     | 10    | mA  |

|                       | т | Sup            | Flash during read on single mode            | V <sub>DD_HV_FL</sub> at 3.3 V                                |        | 8     | 10    |     |

| I <sub>DD_FLASH</sub> |   |                | Flash during erase operation on single mode | V <sub>DD_HV_FL</sub> at 3.3 V                                | _      | 10    | 12    |     |

|                       |   |                | ADC—Maximum mode <sup>(1)</sup>             |                                                               | ADC_1  | 2.5   | 4     |     |

|                       | т |                |                                             | V <sub>DD_HV_ADC0</sub> at 3.3 V                              | ADC_0  | 2     | 4     |     |

| I <sub>DD_ADC</sub>   |   |                | ADC—Typical mode <sup>(2)</sup>             | V <sub>DD_HV_ADC1</sub> at 3.3 V<br>f <sub>ADC</sub> = 16 MHz | ADC_1  | 0.8   | 1     |     |

|                       |   |                |                                             |                                                               | ADC_0  | 0.005 | 0.006 |     |

| I <sub>DD_OSC</sub>   | Т |                | Oscillator                                  | V <sub>DD_OSC</sub> at 3.3 V                                  | 8 MHz  | 2.4   | 3     |     |

| Table 24. | Supply current ( | 3.3 V, NVUSRO[PAD3V5V] = 1) |

|-----------|------------------|-----------------------------|

|-----------|------------------|-----------------------------|

1. Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

2. Typical mode: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

Code fetched from RAM, PLL\_0: 64 MHz system clock (x4 multiplier with 16 MHz XTAL), PLL\_1 is ON at PHI\_div2 = 120 MHz and PHI\_div3 = 80 MHz, auxiliary clock sources set that all peripherals receive maximum frequency, all peripherals enabled.

4. Halt mode configurations: code fetched from RAM, code and data flash memories in low power mode, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

5. STOP "P" mode Device Under Test (DUT) configuration: code fetched from RAM, code and data flash memories OFF, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

#### 3.10.4 Input DC electrical characteristics definition

Figure 14 shows the DC electrical characteristics behavior as function of time.

| Table 26. | I/O weight (continued) |

|-----------|------------------------|

|-----------|------------------------|

| D- 1     | LQ        | FP144       | LQFP100   |             |  |  |

|----------|-----------|-------------|-----------|-------------|--|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[72]  | 1%        | 1%          | —         | _           |  |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[73]  | 1%        | 1%          | —         | _           |  |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[74]  | 1%        | 1%          | —         |             |  |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[75]  | 1%        | 1%          | —         | _           |  |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[76]  | 1%        | 1%          | —         | _           |  |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |  |

| PAD[107] | 20%       | 17%         | —         |             |  |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |  |

| PAD[106] | 18%       | 16%         | —         | _           |  |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |  |

| PAD[105] | 16%       | 14%         | —         | _           |  |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |  |

| PAD[104] | 14%       | 13%         | —         |             |  |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |  |

| PAD[103] | 12%       | 11%         | —         | _           |  |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |  |

| PAD[101] | 11%       | 9%          | —         | —           |  |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |  |

| ТСК      | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |  |

| PAD[102] | 11%       | 10%         | —         | —           |  |  |

| Symbol  |    | с | Parameter                                           | Condit                                     | Conditions <sup>(1)</sup>                 |                                               | Value |      |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|---------|----|---|-----------------------------------------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------|-------|------|------|---------------|--------------------------------|-----------------------------------------------|---|---|-----|--------------------------------|--|---|---|----|--|

|         |    | C | Farameter                                           | Conditions                                 |                                           | Min                                           | Тур   | Max  | Unit |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     | C <sub>L</sub> = 25 pF, 13 MHz             |                                           | —                                             | —     | 6.6  |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     | C <sub>L</sub> = 25 pF, 40 MHz             | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0 |                                               |       | 13.4 |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         | сс |   | Root medium square<br>I/O current for               | C <sub>L</sub> = 100 pF, 13 MHz            |                                           | _                                             | _     | 18.3 | mA   |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

| IRMSMED | CC | _ | MEDIUM                                              | C <sub>L</sub> = 25 pF, 13 MHz             |                                           | _                                             | _     | 5    | mA   |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     |                                            |                                           |                                               |       |      |      | configuration | C <sub>L</sub> = 25 pF, 40 MHz | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _ | _ | 8.5 |                                |  |   |   |    |  |

|         |    |   |                                                     | C <sub>L</sub> = 100 pF, 13 MHz            |                                           | _                                             | _     | 11   |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     |                                            |                                           |                                               |       |      |      |               |                                |                                               |   |   |     | C <sub>L</sub> = 25 pF, 40 MHz |  | _ | _ | 22 |  |

|         | сс |   |                                                     |                                            |                                           |                                               |       |      |      |               | C <sub>L</sub> = 25 pF, 64 MHz | $V_{DD} = 5.0 V \pm 10\%$ ,<br>PAD3V5V = 0    | _ | _ | 33  |                                |  |   |   |    |  |

|         |    |   | Root medium square                                  | C <sub>L</sub> = 100 pF, 40 MHz            |                                           | _                                             | _     | 56   |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

| IRMSFST |    |   | configuration $C_L = 25 \text{ pF}, 40 \text{ MHz}$ |                                            |                                           |                                               |       | _    | _    | 14            | mA                             |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     |                                            | C <sub>L</sub> = 25 pF, 64 MHz            | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |       |      | 20   |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   |                                                     | C <sub>L</sub> = 100 pF, 40 MHz            |                                           |                                               |       | 35   |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

|         |    |   | Sum of all the static                               | V <sub>DD</sub> = 5.0 V ± 10%, P/          | AD3V5V = 0                                | _                                             | _     | 70   |      |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

| AVGSEG  | SR |   | I/O current within a<br>supply segment              | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |                                           |                                               |       | 65   | mA   |               |                                |                                               |   |   |     |                                |  |   |   |    |  |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

2. Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

### 3.11 Main oscillator electrical characteristics

The SPC560P44Lx, SPC560P50Lx provides an oscillator/resonator driver.

Table 28.Main oscillator output electrical characteristics (5.0 V,<br/>NVUSRO[PAD3V5V] = 0)

| Symbol             |      | C Parameter |                                         | Va      | Unit |      |

|--------------------|------|-------------|-----------------------------------------|---------|------|------|

| Syn                | IDOI | C Farameter |                                         | Min Max |      | Onit |

| fosc               | SR   | —           | Oscillator<br>frequency                 | 4       | 40   | MHz  |

| 9 <sub>m</sub>     | _    | Р           | Transconduc<br>tance                    | 6.5     | 25   | mA/V |

| V <sub>OSC</sub>   | _    | Т           | Oscillation<br>amplitude on<br>XTAL pin | 1       | _    | V    |

| t <sub>oscsu</sub> | —    | Т           | Start-up<br>time <sup>(1),(2)</sup>     | 8       | _    | ms   |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of XTAL

| Symbol              | с | C Parameter                                        |                                               | Conditions <sup>(1)</sup>                                                                 | Va    | Unit                 |                       |  |  |  |

|---------------------|---|----------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------|-------|----------------------|-----------------------|--|--|--|

| Symbol              |   |                                                    |                                               | Conditions                                                                                | Min   | Max                  | Onic                  |  |  |  |

|                     |   |                                                    | Short-term jitter <sup>(10)</sup>             | f <sub>SYS</sub> maximum                                                                  | -4    | 4                    | % f <sub>CLKOUT</sub> |  |  |  |

| C <sub>JITTER</sub> | т | CLKOUT period<br>jitter <sup>(6),(7),(8),(9)</sup> | Long-term jitter (avg.<br>over 2 ms interval) | f <sub>PLLIN</sub> = 16 MHz<br>(resonator), f <sub>PLLCLK</sub> at<br>64 MHz, 4000 cycles | _     | 10                   | ns                    |  |  |  |

| t <sub>lpll</sub>   | D | PLL lock time (11), (12)                           |                                               | —                                                                                         | _     | 200                  | μs                    |  |  |  |

| t <sub>dc</sub>     | D | Duty cycle of reference                            |                                               | —                                                                                         | 40    | 60                   | %                     |  |  |  |

| f <sub>LCK</sub>    | D | Frequency LOCK range                               |                                               | —                                                                                         | -6    | 6                    | % f <sub>SYS</sub>    |  |  |  |

| f <sub>UL</sub>     | D | Frequency un-LOCK range                            |                                               | —                                                                                         | -18   | 18                   | % f <sub>SYS</sub>    |  |  |  |

| f <sub>CS</sub>     | D | Madulation danth                                   |                                               | Center spread                                                                             | ±0.25 | ±4.0 <sup>(13)</sup> | 0/ f                  |  |  |  |

| f <sub>DS</sub>     |   | Modulation depth                                   |                                               | Down spread                                                                               | -0.5  | -8.0                 | % f <sub>SYS</sub>    |  |  |  |

| f <sub>MOD</sub>    | D | Modulation freque                                  | ency <sup>(14)</sup>                          | —                                                                                         |       | 70                   | kHz                   |  |  |  |

Table 31.

FMPLL electrical characteristics (continued)

1.  $V_{DD_{L}V_{C}ORx}$  = 1.2 V ±10%;  $V_{SS}$  = 0 V;  $T_A$  = -40 to 125 °C, unless otherwise specified

2. Considering operation with PLL not bypassed

3. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self-clocked mode.

4. Self-clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

6. This value is determined by the crystal manufacturer and board design.

7. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

8. Proper PC board layout procedures must be followed to achieve specifications.

- Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- 10. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

- 11. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 12. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 13. This value is true when operating at frequencies above 60 MHz, otherwise  $f_{CS}$  is 2% (above 64 MHz).

- 14. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

| Symbol | С                               | Parameter                                    | Conditions <sup>(1)</sup> | Max value | Unit |

|--------|---------------------------------|----------------------------------------------|---------------------------|-----------|------|

| f      | 6                               | Maximum working frequency at given number of | 2 wait states             | 66        | MHz  |

| Imax   | wait states in worst conditions | wait states in worst conditions              | 0 wait states             | 18        |      |

#### Table 36. Flash memory read access timing

1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

# 3.16 AC specifications

### 3.16.1 Pad AC specifications

#### Table 37.Output pin transition times

| Sumh                            |                    | с                    | Parameter                                        |                                                  | onditions <sup>(1)</sup>                       | Value             |                         |                   | Unit                   |                                |             |   |   |   |

|---------------------------------|--------------------|----------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------------|-------------------|-------------------------|-------------------|------------------------|--------------------------------|-------------|---|---|---|

| Symb                            | 101                | C                    | Farameter                                        |                                                  | Shallons, 2                                    | Min               | Тур                     | Max               | Unit                   |                                |             |   |   |   |

|                                 | D                  |                      | C <sub>L</sub> = 25 pF                           |                                                  | —                                              | —                 | 50                      |                   |                        |                                |             |   |   |   |

|                                 | t <sub>tr</sub> CC |                      | 4 –                                              | C <sub>L</sub> = 50 pF                           | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0  | _                 | _                       | 100               |                        |                                |             |   |   |   |

| +                               |                    |                      |                                                  | C <sub>L</sub> = 100 pF                          |                                                | _                 | _                       | 125               | ne                     |                                |             |   |   |   |

| <sup>L</sup> tr                 |                    | D                    | SLOW configuration                               | C <sub>L</sub> = 25 pF                           |                                                | _                 | _                       | 40                | ns                     |                                |             |   |   |   |

|                                 |                    | Т                    |                                                  | C <sub>L</sub> = 50 pF                           | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1  | _                 | _                       | 50                |                        |                                |             |   |   |   |

|                                 |                    | D                    |                                                  | C <sub>L</sub> = 100 pF                          |                                                | _                 | _                       | 75                |                        |                                |             |   |   |   |

|                                 | 1                  | D                    | -                                                | C <sub>L</sub> = 25 pF                           | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0      | _                 | _                       | 10                |                        |                                |             |   |   |   |

|                                 |                    | Т                    |                                                  | C <sub>L</sub> = 50 pF                           |                                                | _                 | _                       | 20                |                        |                                |             |   |   |   |

| t <sub>tr</sub> CC              | <u> </u>           |                      |                                                  | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                        | SIUL.PCRx.SRC = 1 | _                       | _                 | 40                     | <b>n</b> 0                     |             |   |   |   |

|                                 | D                  | MEDIUM configuration | C <sub>L</sub> = 25 pF                           | V <sub>DD</sub> = 3.3 V ± 10%,                   | _                                              | _                 | 12                      | ns                |                        |                                |             |   |   |   |

|                                 |                    | Т                    |                                                  | C <sub>L</sub> = 50 pF                           | PAD3V5V = 1                                    | _                 | _                       | 25                |                        |                                |             |   |   |   |

|                                 |                    | D                    |                                                  | C <sub>L</sub> = 100 pF                          | SIUL.PCRx.SRC = 1                              | _                 | _                       | 40                |                        |                                |             |   |   |   |

|                                 |                    |                      |                                                  |                                                  |                                                |                   |                         |                   | C <sub>L</sub> = 25 pF | V <sub>DD</sub> = 5.0 V ± 10%, | _           | _ | 4 |   |

|                                 |                    |                      |                                                  |                                                  |                                                |                   |                         |                   |                        | C <sub>L</sub> = 50 pF         | PAD3V5V = 0 | _ | _ | 6 |

| +                               | сс                 | П                    | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                          | SIUL.PCRx.SRC = 1                              | _                 | _                       | 12                | ne                     |                                |             |   |   |   |

| t <sub>tr</sub>                 | 00                 |                      | FAST configuration                               | C <sub>L</sub> = 25 pF                           | _V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                 | _                       | 4                 | ns                     |                                |             |   |   |   |

|                                 |                    |                      |                                                  | C <sub>L</sub> = 50 pF                           |                                                | —                 | —                       | 7                 |                        |                                |             |   |   |   |

|                                 |                    |                      |                                                  |                                                  |                                                |                   | C <sub>L</sub> = 100 pF | SIUL.PCRx.SRC = 1 | —                      | —                              | 12          |   |   |   |

| t <sub>SYM</sub> <sup>(3)</sup> | сс                 | т                    | Symmetric transition time, same drive            | V <sub>DD</sub> = 5.0 V ±                        | ± 10%, PAD3V5V = 0                             |                   | —                       | 4                 | ne                     |                                |             |   |   |   |

| 'SYM`'                          |                    |                      | strength between N and P transistor              | V <sub>DD</sub> = 3.3 V ±                        | ± 10%, PAD3V5V = 1                             | —                 | _                       | 5                 | ns                     |                                |             |   |   |   |

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

2. CL includes device and package capacitances (CPKG < 5 pF).

3. Transition timing of both positive and negative slopes will differ maximum 50%

| No. Svr |                        | Symbol C |   | Parameter                   | Va  | Unit |     |      |

|---------|------------------------|----------|---|-----------------------------|-----|------|-----|------|

| NO.     | Sym                    | Symbol   |   | Parameter                   | Min | Тур  | Max | Unit |

| 6       | t <sub>NTDIS</sub>     | CC       | D | TDI data setup time         | 6   | —    | —   | ns   |

| 0       | t <sub>NTMSS</sub>     | CC       | D | TMS data setup time         | 6   | —    | —   | ns   |

| 7       | t <sub>NTDIH</sub>     | CC       | D | TDI data hold time          | 10  | —    | —   | ns   |

| 1       | t <sub>NTMSH</sub>     | CC       | D | TMS data hold time          | 10  | —    | —   | ns   |

| 8       | t <sub>TDOV</sub> CC D |          | D | TCK low to TDO data valid   | —   | —    | 35  | ns   |

| 9       | t <sub>TDOI</sub>      | CC       | D | TCK low to TDO data invalid | 6   | —    | _   | ns   |

Table 40.

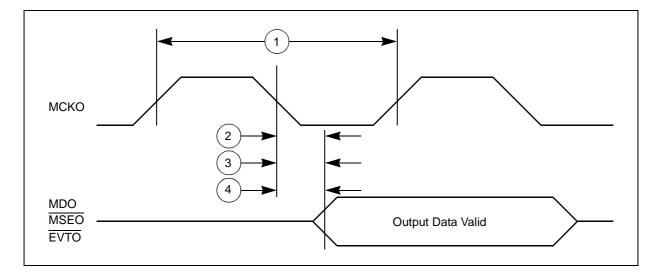

Nexus debug port timing<sup>(1)</sup> (continued)

1. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

2. MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

3. Lower frequency is required to be fully compliant to standard.

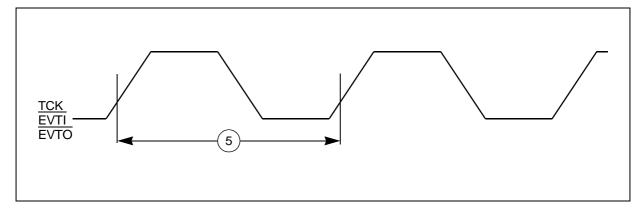

Figure 25. Nexus output timing

Figure 26. Nexus event trigger and test clock timings

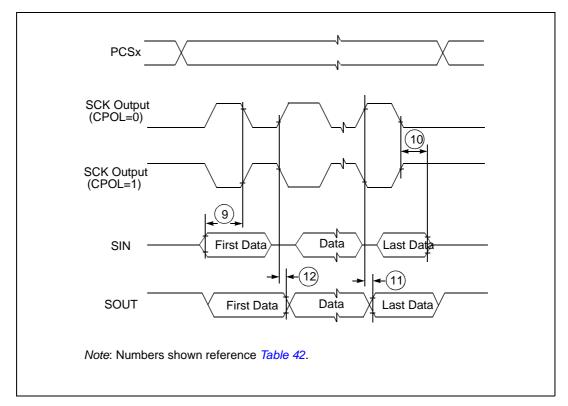

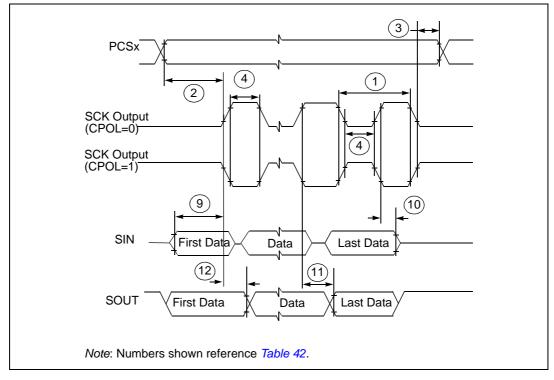

Figure 30. DSPI classic SPI timing – Master, CPHA = 1

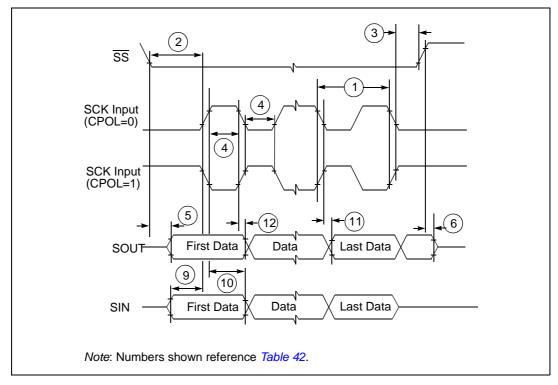

Figure 31. DSPI classic SPI timing – Slave, CPHA = 0

57

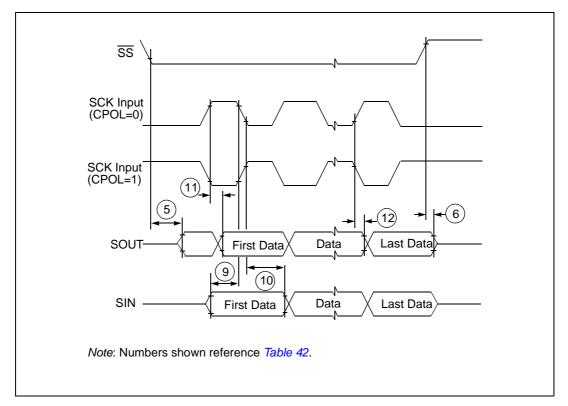

Figure 32. DSPI classic SPI timing – Slave, CPHA = 1

Figure 33. DSPI modified transfer format timing – Master, CPHA = 0

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

IIn order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 4.2 Package mechanical data

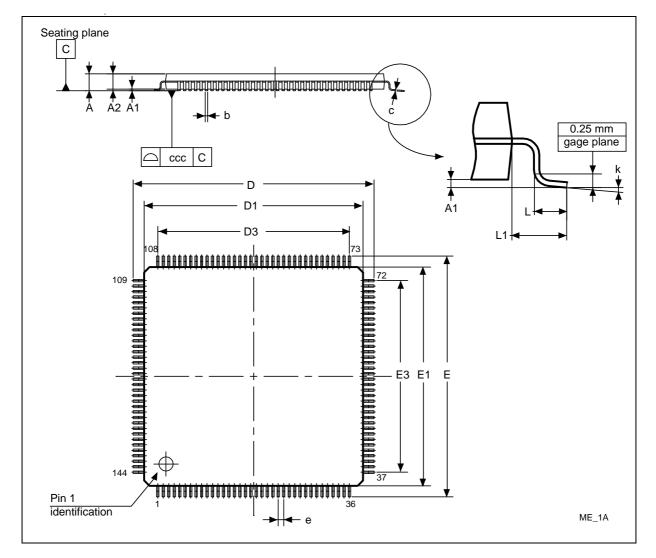

### 4.2.1 LQFP144 mechanical outline drawing

Figure 38. LQFP144 package mechanical drawing

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com