Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 107                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p50l5befbr |

# List of tables

| Table 1.  | Device summary                                                                          | 1   |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Table 2.  | SPC560P44Lx, SPC560P50Lx device comparison                                              | 7   |

| Table 3.  | SPC560P44Lx, SPC560P50Lx device configuration differences                               | 8   |

| Table 4.  | SPC560P44Lx, SPC560P50Lx series block summary                                           |     |

| Table 5.  | Supply pins                                                                             | 32  |

| Table 6.  | System pins                                                                             | 33  |

| Table 7.  | Pin muxing                                                                              | 35  |

| Table 8.  | Parameter classifications                                                               | 49  |

| Table 9.  | Absolute maximum ratings                                                                | 50  |

| Table 10. | Recommended operating conditions (5.0 V)                                                | 53  |

| Table 11. | Recommended operating conditions (3.3 V)                                                | 54  |

| Table 12. | Thermal characteristics for 144-pin LQFP                                                | 56  |

| Table 13. | Thermal characteristics for 100-pin LQFP                                                | 57  |

| Table 14. | EMI testing specifications                                                              | 59  |

| Table 15. | ESD ratings,                                                                            | 59  |

| Table 16. | Approved NPN ballast components (configuration with resistor on base)                   |     |

| Table 17. | Voltage regulator electrical characteristics (configuration with resistor on base)      |     |

| Table 18. | Voltage regulator electrical characteristics (configuration without resistor on base) . | 62  |

| Table 19. | Low voltage monitor electrical characteristics                                          |     |

| Table 20. | PAD3V5V field description                                                               | 65  |

| Table 21. | DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)                              | 66  |

| Table 22. | Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)                                             |     |

| Table 23. | DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)                              |     |

| Table 24. | Supply current (3.3 V, NVUSRO[PAD3V5V] = 1)                                             | 69  |

| Table 25. | I/O supply segment                                                                      | 70  |

| Table 26. | I/O weight                                                                              |     |

| Table 27. | I/O consumption                                                                         | 74  |

| Table 28. | Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)          |     |

| Table 29. | Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)          |     |

| Table 30. | Input clock characteristics                                                             |     |

| Table 31. | FMPLL electrical characteristics                                                        |     |

| Table 32. | 16 MHz RC oscillator electrical characteristics                                         |     |

| Table 33. | ADC conversion characteristics                                                          |     |

| Table 34. | Program and erase specifications                                                        |     |

| Table 35. | Flash memory module life                                                                |     |

| Table 36. | Flash memory read access timing                                                         |     |

| Table 37. | Output pin transition times                                                             |     |

| Table 38. | RESET electrical characteristics                                                        |     |

| Table 39. | JTAG pin AC electrical characteristics                                                  |     |

| Table 40. | Nexus debug port timing                                                                 |     |

| Table 41. | External interrupt timing                                                               |     |

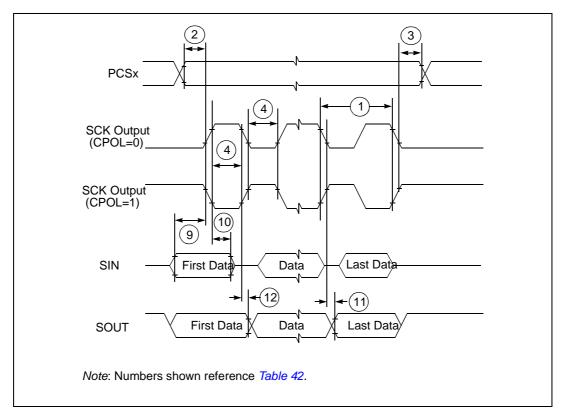

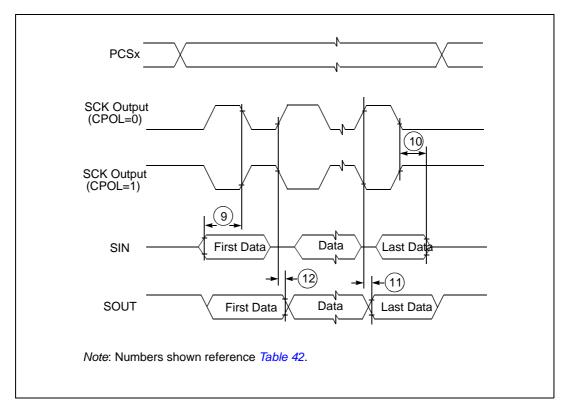

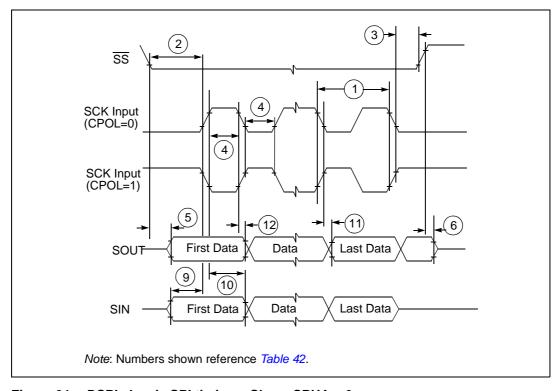

| Table 42. | DSPI timing                                                                             |     |

| Table 43. | LQFP144 mechanical data                                                                 |     |

| Table 44. | LQFP100 package mechanical data                                                         |     |

| Table 45. | Abbreviations                                                                           |     |

| Table 46. | Revision history                                                                        | 107 |

#### 1 Introduction

#### 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the SPC560P44/50 series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

## 1.3 Device comparison

Table 2 provides a summary of different members of the SPC560P44Lx, SPC560P50Lx family and their features—relative to full-featured version—to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

Table 2. SPC560P44Lx, SPC560P50Lx device comparison

| Feature                                              | SPC560P44        | SPC560P50        |

|------------------------------------------------------|------------------|------------------|

| Code flash memory (with ECC)                         | 384 KB           | 512 KB           |

| Data flash memory / EE option (with ECC)             | 64               | KB               |

| SRAM (with ECC)                                      | 36 KB            | 40 KB            |

| Processor core                                       | 32-bit e         | 200z0h           |

| Instruction set                                      | VLE (variable le | ength encoding)  |

| CPU performance                                      | 0–64             | MHz              |

| FMPLL (frequency-modulated phase-locked loop) module | 2                | 2                |

| INTC (interrupt controller) channels                 | 14               | 17               |

| PIT (periodic interrupt timer)                       | 1 (includes fou  | r 32-bit timers) |

Table 2. SPC560P44Lx, SPC560P50Lx device comparison (continued)

|                             | Feature                             | SPC560P44                              | SPC560P50                   |  |

|-----------------------------|-------------------------------------|----------------------------------------|-----------------------------|--|

| eDMA (enhance channels      | ed direct memory access)            | 16                                     |                             |  |

| FlexRay                     |                                     | Ye                                     | s <sup>(1)</sup>            |  |

| FlexCAN (contro             | oller area network)                 | 2 <sup>(2)</sup>                       | ),(3)                       |  |

| Safety port                 |                                     | Yes (via second I                      | FlexCAN module)             |  |

| FCU (fault collec           | ction unit)                         | Ye                                     | es                          |  |

| CTU (cross trigg            | gering unit)                        | Ye                                     | es                          |  |

| eTimer                      |                                     | 2 (16-bit, 6                           | channels)                   |  |

| FlexPWM (pulse              | e-width modulation) channels        | 8 (capturing o                         | n X-channels)               |  |

| ADC (analog-to-             | -digital converter)                 | 2 (10-bit, 15-channel <sup>(4)</sup> ) |                             |  |

| LINFlex                     |                                     | 2                                      |                             |  |

| DSPI (deserial s            | serial peripheral interface)        | 4                                      |                             |  |

| CRC (cyclic red             | undancy check) unit                 | Yes                                    |                             |  |

| JTAG controller             |                                     | Yes                                    |                             |  |

| Nexus port cont             | roller (NPC)                        | Yes (Le                                | evel 2+)                    |  |

|                             | Digital power supply <sup>(5)</sup> | 3.3 V or 5 V single supp               | ly with external transistor |  |

| Supply                      | Analog power supply                 | 3.3 V or 5 V                           |                             |  |

| Supply                      | Internal RC oscillator              | 16 MHz                                 |                             |  |

| External crystal oscillator |                                     | 4–40 MHz                               |                             |  |

| Packages                    |                                     | LQFP100                                |                             |  |

| 1 ackages                   |                                     | LQFP144                                |                             |  |

| Temperature                 | Standard ambient temperature        | −40 to 125 °C                          |                             |  |

- 1. 32 message buffers, selectable single or dual channel support

- 2. Each FlexCAN module has 32 message buffers.

- 3. One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

- 4. Four channels shared between the two ADCs

- 5. The different supply voltages vary according to the part number ordered.

SPC560P44Lx, SPC560P50Lx is available in two configurations having different features: full-featured and airbag. *Table 3* shows the main differences between the two versions.

Table 3. SPC560P44Lx, SPC560P50Lx device configuration differences

| Feature                     | Full-featured | Airbag |

|-----------------------------|---------------|--------|

| CTU (cross triggering unit) | Yes           | No     |

| FlexPWM                     | Yes           | No     |

Table 4. SPC560P44Lx, SPC560P50Lx series block summary (continued)

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse width modulator (FlexPWM)               | Contains four PWM submodules, each of which is capable of controlling a single half-bridge power stage and two fault input channels                                                                                              |

| Reset generation module (MC_RGM)              | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR <sup>(1)</sup> and operating system tasks                                                                                                                             |

| System watchdog timer (SWT)                   | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, 1 of which can cause non-maskable interrupt requests or wakeup events                                                                          |

<sup>1.</sup> AUTOSAR: AUTomotive Open System ARchitecture (see www.autosar.org)

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

#### 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

#### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P44Lx, SPC560P50Lx:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module can run on an independent clock source

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

#### 1.5.13 System timer module (STM)

The STM module implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

#### 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- 32-bit time-out register to set the time-out period

- Programmable selection of system or oscillator clock for timer operation

- Programmable selection of window mode or regular servicing

- Programmable selection of reset or interrupt on an initial time-out

- Master access protection

- Hard and soft configuration lock bits

- Reset configuration inputs allow timer to be enabled out of reset

#### 1.5.15 Fault collection unit (FCU)

The FCU provides an independent fault reporting mechanism even if the CPU is malfunctioning.

The FCU module has the following features:

- FCU status register reporting the device status

- Continuous monitoring of critical fault signals

- User selection of critical signals from different fault sources inside the device

- Critical fault events trigger 2 external pins (user selected signal protocol) that can be used externally to reset the device and/or other circuitry (for example, safety relay or FlexRay transceiver)

- Faults are latched into a register

#### 1.5.16 System integration unit – Lite (SIUL)

The SPC560P44Lx, SPC560P50Lx SIUL controls MCU pad configuration, external interrupt, general purpose I/O (GPIO), and internal peripheral multiplexing.

The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

The SIU provides the following features:

- Centralized general purpose input output (GPIO) control of as many as 80 input/output pins and 26 analog input-only pads (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins (except ADC channels) can be alternatively configured as both general purpose input or output pins

- ADC channels support alternative configuration as general purpose inputs

- Direct readback of the pin value is supported on all pins through the SIUL

- Configurable digital input filter that can be applied to some general purpose input pins for noise elimination: as many as 4 internal functions can be multiplexed onto 1 pin

#### 1.5.17 Boot and censorship

Different booting modes are available in the SPC560P44Lx, SPC560P50Lx: booting from internal flash memory and booting via a serial link.

The default booting scheme uses the internal flash memory (an internal pull-down is used to select this mode). Optionally, the user can boot via FlexCAN or LINFlex (using the boot assist module software).

A censorship scheme is provided to protect the content of the flash memory and offer increased security for the entire device.

A password mechanism is designed to grant the legitimate user access to the non-volatile memory.

#### **Boot assist module (BAM)**

The BAM is a block of read-only one-time programmed memory and is identical for all SPC560Pxx devices that are based on the e200z0h core. The BAM program is executed every time the device is powered on if the alternate boot mode has been selected by the user.

The BAM provides the following features:

- Serial bootloading via FlexCAN or LINFlex

- Ability to accept a password via the used serial communication channel to grant the legitimate user access to the non-volatile memory

#### 1.5.18 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC560P44Lx, SPC560P50Lx.

Table 7. Pin muxing (continued)

| Table | able 7. Pin muxing (continued) |                              |           |                           |                  |                          |         |         |         |

|-------|--------------------------------|------------------------------|-----------|---------------------------|------------------|--------------------------|---------|---------|---------|

| Port  | Pad                            | 7                            |           |                           | I/O              | Pad speed <sup>(5)</sup> |         | Pin No. |         |

| pin   | configuration register (PCR)   | function <sup>(1),</sup> (2) | Functions | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0                  | SRC = 1 | 100-pin | 144-pin |

|       |                                | ALT0                         | GPIO[23]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[7]  | PCR[23]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 29      | 43      |

| ا ا   | 1 011[20]                      | ALT3                         | _         | _                         | input only       |                          |         | 20      | .0      |

|       |                                | _                            | AN[0]     | ADC_0                     |                  |                          |         |         |         |

|       |                                | _                            | RXD       | LIN_0                     |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[24]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[8]  | PCR[24]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 31      | 47      |

| -[0]  | . 0[= .]                       | ALT3                         | _         | _                         | ,                |                          |         |         |         |

|       |                                | _                            | AN[1]     | ADC_0                     |                  |                          |         |         |         |

|       |                                | _                            | ETC[5]    | eTimer_0                  |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[25]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[9]  | PCR[25]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 35      | 52      |

|       |                                | ALT3                         | _         |                           |                  |                          |         |         |         |

|       |                                | _                            | AN[11]    | ADC_0 / ADC_1             |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[26]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[10] | PCR[26]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 36      | 53      |

|       |                                | ALT3                         | _         | _                         |                  |                          |         |         |         |

|       |                                | _                            | AN[12]    | ADC_0 / ADC_1             |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[27]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[11] | PCR[27]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 37      | 54      |

|       |                                | ALT3                         |           | _                         |                  |                          |         |         |         |

|       |                                | _                            | AN[13]    | ADC_0 / ADC_1             |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[28]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[12] | PCR[28]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 38      | 55      |

|       |                                | ALT3                         | _         | <del>-</del>              |                  |                          |         |         |         |

|       |                                | _                            | AN[14]    | ADC_0 / ADC_1             |                  |                          |         |         |         |

|       |                                | ALT0                         | GPIO[29]  | SIUL                      |                  |                          |         |         |         |

|       |                                | ALT1                         | _         | _                         |                  |                          |         |         |         |

| B[13] | PCR[29]                        | ALT2                         | _         | _                         | Input only       | _                        | _       | 42      | 60      |

| _[]   | [-0]                           | ALT3                         |           | _                         |                  |                          |         |         |         |

|       |                                | _                            | AN[0]     | ADC_1                     |                  |                          |         |         |         |

|       |                                | _                            | RXD       | LIN_1                     |                  |                          |         |         |         |

Table 7. Pin muxing (continued)

| Port  | Pad                          | ad Alternate                      | I/O                             | Pad sp                     | peed <sup>(5)</sup>     | Pin No. |         |         |         |

|-------|------------------------------|-----------------------------------|---------------------------------|----------------------------|-------------------------|---------|---------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup> (2)      | Functions                       | Peripheral <sup>(3)</sup>  | direction<br>(4)        | SRC = 0 | SRC = 1 | 100-pin | 144-pin |

| F[5]  | PCR[85]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[85]<br>MDO[2]<br>—<br>—    | SIUL<br>NEXUS_0<br>—<br>—  | 0 0                     | Slow    | Fast    | _       | 5       |

| F[6]  | PCR[86]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[86]<br>MDO[1]<br>—         | SIUL<br>NEXUS_0<br>—       | I/O<br>O<br>—           | Slow    | Fast    | _       | 8       |

| F[7]  | PCR[87]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[87]<br>MCKO<br>—           | SIUL<br>NEXUS_0<br>—<br>—  | I/O<br>O<br>—           | Slow    | Fast    | _       | 19      |

| F[8]  | PCR[88]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[88]<br>MSEO1<br>—<br>—     | SIUL<br>NEXUS_0<br>—<br>—  | I/O O —                 | Slow    | Fast    | _       | 20      |

| F[9]  | PCR[89]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[89]<br>MSEO0<br>—<br>—     | SIUL<br>NEXUS_0<br>—<br>—  | I/O<br>O<br>—<br>—      | Slow    | Fast    | _       | 23      |

| F[10] | PCR[90]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[90]<br>EVTO<br>—<br>—      | SIUL<br>NEXUS_0<br>—<br>—  | 0 0                     | Slow    | Fast    | _       | 24      |

| F[11] | PCR[91]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[91]<br>—<br>—<br>—<br>EVTI | SIUL NEXUS_0               | I/O<br>—<br>—<br>—<br>— | Slow    | Medium  | _       | 25      |

| F[12] | PCR[92]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[92]<br>ETC[3]<br>—         | SIUL<br>eTimer_1<br>—<br>— | I/O<br>I/O<br>—         | Slow    | Medium  | _       | 106     |

| F[13] | PCR[93]                      | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[92]<br>ETC[4]<br>—<br>—    | SIUL<br>eTimer_1<br>—<br>— | I/O<br>I/O<br>—         | Slow    | Medium  | _       | 112     |

# 3.3 Absolute maximum ratings

Table 9. Absolute maximum ratings<sup>(1)</sup>

| Symbol                                |     | Parameter                                                                                                             | Conditions                         | Value |                                       |      |  |

|---------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|-------|---------------------------------------|------|--|

| Symbol                                |     | Parameter                                                                                                             | Conditions                         | Min   | Max <sup>(2)</sup>                    | Unit |  |

| V <sub>SS</sub>                       | SR  | Device ground                                                                                                         | _                                  | 0     | 0                                     | V    |  |

| V <sub>DD_HV_IOx</sub> (3)            | SR  | 3.3 V / 5.0 V input/output supply voltage with respect to ground (V <sub>SS</sub> )                                   | _                                  | -0.3  | 6.0                                   | V    |  |

| V <sub>SS_HV_IOx</sub>                | SR  | Input/output ground voltage with respect to ground (V <sub>SS</sub> )                                                 | _                                  | -0.1  | 0.1                                   | V    |  |

|                                       |     | 3.3 V / 5.0 V code and data flash                                                                                     | _                                  |       | 6.0                                   |      |  |

| $V_{DD\_HV\_FL}$                      | SR  | supply voltage with respect to ground $(V_{SS})$                                                                      | Relative to V <sub>DD_HV_IOx</sub> | -0.3  | $V_{DD\_HV\_IOx} + 0.3$               | V    |  |

| V <sub>SS_HV_FL</sub>                 | SR  | Code and data flash ground with respect to ground (V <sub>SS</sub> )                                                  | _                                  | -0.1  | 0.1                                   | V    |  |

|                                       |     | 3.3 V / 5.0 V crystal oscillator                                                                                      | _                                  |       | 6.0                                   |      |  |

| V <sub>DD_HV_OSC</sub>                | SR  | amplifier supply voltage with respect to ground (V <sub>SS</sub> )                                                    | Relative to V <sub>DD_HV_IOx</sub> | -0.3  | $V_{DD\_HV\_IOx} + 0.3$               | V    |  |

| V <sub>SS_HV_OSC</sub>                | SR  | 3.3 V / 5.0 V crystal oscillator amplifier reference voltage with respect to ground (V <sub>SS</sub> )                |                                    | -0.1  | 0.1                                   | V    |  |

|                                       |     | 2.2 V / F.O. V voltage regulator supply                                                                               | _                                  |       | 6.0                                   |      |  |

| $V_{DD\_HV\_REG}$                     | SR  | 3.3 V / 5.0 V voltage regulator supply voltage with respect to ground (V <sub>SS</sub> )                              | Relative to V <sub>DD_HV_IOx</sub> | -0.3  | $V_{DD\_HV\_IOx} + 0.3$               | V    |  |

| V <sub>DD_HV_ADC0</sub>               | SR  | 3.3 V / 5.0 V ADC_0 supply and high reference voltage with respect to                                                 | V <sub>DD_HV_REG</sub> < 2.7 V     | -0.3  | V <sub>DD_HV_REG</sub> + 0.3          | V    |  |

| (4)                                   | SIX | ground (V <sub>SS</sub> )                                                                                             | V <sub>DD_HV_REG</sub> > 2.7 V     | -0.5  | 6.0                                   | V    |  |

| V <sub>SS_HV_ADC0</sub>               | SR  | ADC_0 ground and low reference voltage with respect to ground (V <sub>SS</sub> )                                      | _                                  | -0.1  | 0.1                                   | V    |  |

| V <sub>DD_HV_</sub> ADC1 <sup>(</sup> | SR  | 3.3 V / 5.0 V ADC_0 supply and high reference voltage with respect to                                                 | V <sub>DD_HV_REG</sub> < 2.7 V     | -0.3  | V <sub>DD_HV_REG</sub> + 0.3          | V    |  |

| <sup>-</sup> 4) <sup>-</sup>          | SIX | ground (V <sub>SS</sub> )                                                                                             | V <sub>DD_HV_REG</sub> > 2.7 V     | -0.5  | 6.0                                   | V    |  |

| V <sub>SS_HV_ADC1</sub>               | SR  | ADC_1 ground and low reference voltage with respect to ground (V <sub>SS</sub> )                                      | _                                  | -0.1  | 0.1                                   | V    |  |

| TV <sub>DD</sub>                      | SR  | Slope characteristics on all V <sub>DD</sub> during power up <sup>(5)</sup> with respect to ground (V <sub>SS</sub> ) | _                                  | 3.0   | 500 x 10 <sup>3</sup><br>(0.5 [V/µs]) | V/s  |  |

|                                       |     | Voltage on any pin with respect to                                                                                    | _                                  |       | 6.0                                   |      |  |

| $V_{IN}$                              | SR  | ground ( $V_{SS\_HV\_IOx}$ ) with respect to ground ( $V_{SS}$ )                                                      | Relative to V <sub>DD_HV_IOx</sub> | -0.3  | $V_{DD\_HV\_IOx} + 0.3$               | V    |  |

# 3.4 Recommended operating conditions

Table 10. Recommended operating conditions (5.0 V)

| 0                                             |    |                                                      | 0 111                              | Value                        |                              |      |

|-----------------------------------------------|----|------------------------------------------------------|------------------------------------|------------------------------|------------------------------|------|

| Symbol                                        |    | Parameter                                            | Conditions                         | Min                          | Max <sup>(1)</sup>           | Unit |

| V <sub>SS</sub>                               | SR | Device ground                                        | _                                  | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup>         | SR | 5.0 V input/output supply voltage                    | _                                  | 4.5                          | 5.5                          | ٧    |

| V <sub>SS_HV_IOx</sub>                        | SR | Input/output ground voltage                          | _                                  | 0                            | 0                            | V    |

|                                               |    | 5.0 V code and data flash                            | _                                  | 4.5                          | 5.5                          |      |

| $V_{DD\_HV\_FL}$                              | SR | supply voltage                                       | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | $V_{DD\_HV\_IOx} + 0.1$      | V    |

| V <sub>SS_HV_FL</sub>                         | SR | Code and data flash ground                           | _                                  | 0                            | 0                            | V    |

|                                               |    | 5.0 V crystal oscillator amplifier                   | _                                  | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_OSC</sub>                        | SR | supply voltage                                       | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | $V_{DD\_HV\_IOx} + 0.1$      | V    |

| V <sub>SS_HV_OSC</sub>                        | SR | 5.0 V crystal oscillator amplifier reference voltage | _                                  | 0                            | 0                            | V    |

|                                               |    | 5.0 V voltage regulator supply                       | _                                  | 4.5                          | 5.5                          |      |

| $V_{DD\_HV\_REG}$                             | SR | voltage                                              | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

|                                               |    | 5.0 V ADC_0 supply and high                          | _                                  | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_ADC0</sub> <sup>(3)</sup>        | SR | reference voltage                                    | Relative to V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> - 0.1 | _                            | V    |

| V <sub>SS_HV_ADC0</sub>                       | SR | ADC_0 ground and low reference voltage               | _                                  | 0                            | 0                            | V    |

| (2)                                           |    | 5.0 V ADC_1 supply and high                          | _                                  | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_ADC1</sub> <sup>(3)</sup>        | SR | reference voltage                                    | Relative to V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | _                            | V    |

| V <sub>SS_HV_ADC1</sub>                       | SR | ADC_1 ground and low reference voltage               | _                                  | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>(4),</sup> (5) | СС | Internal supply voltage                              | _                                  | _                            | _                            | ٧    |

| V <sub>SS_LV_REGCOR</sub> <sup>(4)</sup>      | SR | Internal reference voltage                           | _                                  | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> (4),(5)               |    | Internal supply voltage                              | _                                  | _                            | _                            | V    |

| V <sub>SS_LV_CORx</sub> <sup>(4)</sup>        |    | Internal reference voltage                           | _                                  | 0                            | 0                            | V    |

| T <sub>A</sub>                                | SR | Ambient temperature under                            | f <sub>CPU</sub> = 64 MHz          | -40                          | 105                          | - °C |

| 'A                                            |    | bias                                                 | f <sub>CPU</sub> = 60 MHz          | -40                          | 125                          |      |

Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2.</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD\_HV\_IOy} - V_{DD\_HV\_IOx}| < 100$  mV.

common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

#### Equation 2 $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)  $R_{\theta JC}$  = junction to case thermal resistance (°C/W)  $R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{ heta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{ heta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using *Equation 3*:

#### Equation 3 $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)  $P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### References:

Semiconductor Equipment and Materials International

3081 Zanker Road

San Jose, CA 95134 U.S.A.

(408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

## 3.10.2 DC electrical characteristics (5 V)

*Table 21* gives the DC electrical characteristics at 5 V (4.5 V < V<sub>DD\_HV\_IOx</sub> < 5.5 V, NVUSRO[PAD3V5V] = 0); see *Figure 14*.

Table 21. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol            | • | Dovemeter                                            | Canditions                             | Value                       |                               |      |

|-------------------|---|------------------------------------------------------|----------------------------------------|-----------------------------|-------------------------------|------|

| Symbol            | С | Parameter                                            | Conditions                             | Min                         | Max                           | Unit |

| V                 | D | Low lovel input voltage                              | _                                      | -0.1 <sup>(1)</sup>         | _                             | V    |

| $V_{IL}$          | Р | Low level input voltage                              | _                                      | _                           | 0.35 V <sub>DD_HV_IOx</sub>   | V    |

| V                 | Р | High level input voltage                             | _                                      | 0.65 V <sub>DD_HV_IOx</sub> | _                             | V    |

| V <sub>IH</sub>   | D | Inigit level iriput voltage                          | _                                      | _                           | $V_{DD\_HV\_IOx} + 0.1^{(1)}$ | V    |

| V <sub>HYS</sub>  | Т | Schmitt trigger hysteresis                           | _                                      | 0.1 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| V <sub>OL_S</sub> | Р | Slow, low level output voltage                       | $I_{OL} = 3 \text{ mA}$                |                             | 0.1 V <sub>DD_HV_IOx</sub>    | V    |

| V <sub>OH_S</sub> | Р | Slow, high level output voltage                      | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| V <sub>OL_M</sub> | Р | Medium, low level output voltage                     | $I_{OL} = 3 \text{ mA}$                |                             | 0.1 V <sub>DD_HV_IOx</sub>    | V    |

| V <sub>OH_M</sub> | Р | Medium, high level output voltage                    | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| $V_{OL\_F}$       | Р | Fast, low level output voltage                       | $I_{OL} = 3 \text{ mA}$                | _                           | 0.1 V <sub>DD_HV_IOx</sub>    | V    |

| V <sub>OH_F</sub> | Р | Fast, high level output voltage                      | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| $V_{OL\_SYM}$     | Р | Symmetric, low level output voltage                  | $I_{OL} = 3 \text{ mA}$                |                             | 0.1 V <sub>DD_HV_IOx</sub>    | V    |

| $V_{OH\_SYM}$     | Р | Symmetric, high level output voltage                 | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| 1                 | Р | Equivalent pull-up current                           | $V_{IN} = V_{IL}$                      | -130                        | _                             | μA   |

| I <sub>PU</sub>   | L | Equivalent pull-up current                           | $V_{IN} = V_{IH}$                      |                             | -10                           | μΑ   |

| I                 | Р | Equivalent pull-down current                         | $V_{IN} = V_{IL}$                      | 10                          | _                             | μA   |

| I <sub>PD</sub>   | • | Equivalent pull-down current                         | $V_{IN} = V_{IH}$                      | _                           | 130                           | μΛ   |

| I <sub>IL</sub>   |   | Input leakage current (all bidirectional ports)      | $T_A = -40 \text{ to } 125 \text{ °C}$ | -1                          | 1                             | μΑ   |

| I <sub>IL</sub>   |   | Input leakage current (all ADC input-<br>only ports) | $T_A = -40 \text{ to } 125 \text{ °C}$ | -0.5                        | 0.5                           | μΑ   |

| C <sub>IN</sub>   | D | Input capacitance                                    | _                                      | _                           | 10                            | pF   |

|                   | _ | RESET, equivalent pull-up current                    | $V_{IN} = V_{IL}$                      | -130                        | _                             | ^    |

| I <sub>PU</sub>   | ט | neser, equivalent pull-up current                    | $V_{IN} = V_{IH}$                      | _                           | -10                           | μA   |

<sup>1. &</sup>quot;SR" parameter values must not exceed the absolute maximum ratings shown in  $\it Table 9$ .

Table 26. I/O weight (continued)

| Ded      | LQI       | FP144       | LQFP100   |             |  |

|----------|-----------|-------------|-----------|-------------|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[72]  | 1%        | 1%          | _         | _           |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[73]  | 1%        | 1%          | _         | _           |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[74]  | 1%        | 1%          | _         | _           |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[75]  | 1%        | 1%          | _         | _           |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[76]  | 1%        | 1%          | _         | _           |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |

| PAD[107] | 20%       | 17%         | _         | _           |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |

| PAD[106] | 18%       | 16%         | _         | _           |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |

| PAD[105] | 16%       | 14%         | _         | _           |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |

| PAD[104] | 14%       | 13%         | _         | _           |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |

| PAD[103] | 12%       | 11%         | _         | _           |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |

| PAD[101] | 11%       | 9%          | _         | _           |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |

| TCK      | 1%        | 1%          | 1%        | 1%          |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |

| PAD[102] | 11%       | 10%         | _         | _           |  |

Table 26. I/O weight (continued)

| Ded      | LQ        | FP144       | LQFP100   |             |  |

|----------|-----------|-------------|-----------|-------------|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[60]  | 11%       | 10%         | 11%       | 10%         |  |

| PAD[100] | 12%       | 10%         | _         | _           |  |

| PAD[45]  | 12%       | 10%         | 12%       | 10%         |  |

| PAD[98]  | 12%       | 11%         | _         | _           |  |

| PAD[46]  | 12%       | 11%         | 12%       | 11%         |  |

| PAD[99]  | 13%       | 11%         | _         | _           |  |

| PAD[62]  | 13%       | 11%         | 13%       | 11%         |  |

| PAD[92]  | 13%       | 12%         | _         | _           |  |

| VPP_TEST | 1%        | 1%          | 1%        | 1%          |  |

| PAD[4]   | 14%       | 12%         | 14%       | 12%         |  |

| PAD[16]  | 13%       | 12%         | 13%       | 12%         |  |

| PAD[17]  | 13%       | 11%         | 13%       | 11%         |  |

| PAD[42]  | 13%       | 11%         | 13%       | 11%         |  |

| PAD[93]  | 12%       | 11%         | _         | _           |  |

| PAD[95]  | 12%       | 11%         | _         | _           |  |

| PAD[18]  | 12%       | 10%         | 12%       | 10%         |  |

| PAD[94]  | 11%       | 10%         | _         | _           |  |

| PAD[19]  | 11%       | 10%         | 11%       | 10%         |  |

| PAD[77]  | 10%       | 9%          | _         | _           |  |

| PAD[10]  | 10%       | 9%          | 10%       | 9%          |  |

| PAD[78]  | 9%        | 8%          | _         | _           |  |

| PAD[11]  | 9%        | 8%          | 9%        | 8%          |  |

| PAD[79]  | 8%        | 7%          | _         | _           |  |

| PAD[12]  | 7%        | 7%          | 7%        | 7%          |  |

| PAD[41]  | 7%        | 6%          | 7%        | 6%          |  |

| PAD[47]  | 5%        | 4%          | 5%        | 4%          |  |

| PAD[48]  | 4%        | 4%          | 4%        | 4%          |  |

| PAD[51]  | 4%        | 4%          | 4%        | 4%          |  |

| PAD[52]  | 5%        | 4%          | 5%        | 4%          |  |

| PAD[40]  | 5%        | 5%          | 6%        | 5%          |  |

| PAD[80]  | 9%        | 8%          | _         | _           |  |

| PAD[9]   | 10%       | 9%          | 11%       | 10%         |  |

| PAD[81]  | 10%       | 9%          | _         | _           |  |

Table 29. Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)

| Symple           | al.    | С | Parameter                         | Va  | lue | Unit |  |

|------------------|--------|---|-----------------------------------|-----|-----|------|--|

| Symb             | Symbol |   | Farameter                         | Min | Max | Oill |  |

| fosc             | SR     | _ | Oscillator frequency              | 4   | 40  | MHz  |  |

| g <sub>m</sub>   | _      | Р | Transconductance                  | 4   | 20  | mA/V |  |

| V <sub>OSC</sub> | _      | Т | Oscillation amplitude on XTAL pin | 1   | _   | V    |  |

| toscsu           | _      | Т | Start-up time <sup>(1),(2)</sup>  | 8   | _   | ms   |  |

The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

Table 30. Input clock characteristics

| Symbol            |    | Parameter -              |      | Value |      |      |

|-------------------|----|--------------------------|------|-------|------|------|

|                   |    |                          |      | Тур   | Max  | Unit |

| fosc              | SR | Oscillator frequency     | 4    | _     | 40   | MHz  |

| f <sub>CLK</sub>  | SR | Frequency in bypass      | _    | _     | 64   | MHz  |

| t <sub>rCLK</sub> | SR | Rise/fall time in bypass | _    | _     | 1    | ns   |

| t <sub>DC</sub>   | SR | Duty cycle               | 47.5 | 50    | 52.5 | %    |

#### 3.12 FMPLL electrical characteristics

Table 31. FMPLL electrical characteristics

| Symbol                                           | С | Parameter                                                | Conditions <sup>(1)</sup>                     | Va  | Unit                 |           |  |

|--------------------------------------------------|---|----------------------------------------------------------|-----------------------------------------------|-----|----------------------|-----------|--|

| Syllibol                                         | ) | Farameter                                                | Conditions                                    | Min | Max                  | <b>5.</b> |  |

| f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | D | PLL reference frequency range <sup>(2)</sup>             | Crystal reference                             | 4   | 40                   | MHz       |  |

| f <sub>PLLIN</sub>                               | D | Phase detector input frequency range (after pre-divider) | _                                             | 4   | 16                   | MHz       |  |

| f <sub>FMPLLOUT</sub>                            | D | Clock frequency range in normal mode                     | _                                             | 16  | 120                  | MHz       |  |

| f <sub>FREE</sub>                                | Р | Free-running frequency                                   | Measured using clock division — typically /16 | 20  | 150                  | MHz       |  |

| t <sub>CYC</sub>                                 | D | System clock period                                      | _                                             | _   | 1 / f <sub>SYS</sub> | ns        |  |

| f <sub>LORL</sub>                                | D | Loss of reference frequency window <sup>(3)</sup>        | Lower limit                                   | 1.6 | 3.7                  | MHz       |  |

| fLORH                                            |   | Loss of reference frequency willdow                      | Upper limit                                   | 24  | 56                   | IVII IZ   |  |

| f <sub>SCM</sub>                                 | D | Self-clocked mode frequency <sup>(4),(5)</sup>           | _                                             | 20  | 150                  | MHz       |  |

<sup>2.</sup> Value captured when amplitude reaches 90% of XTAL

Table 36. Flash memory read access timing

| Symbol           | С | Parameter                                    | Conditions <sup>(1)</sup> | Max value | Unit   |

|------------------|---|----------------------------------------------|---------------------------|-----------|--------|

| f                | _ | Maximum working frequency at given number of | 2 wait states             | 66        | MHz    |

| <sup>I</sup> max | C | wait states in worst conditions              | 0 wait states             | 18        | IVIITZ |

<sup>1.</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40 \text{ to } 125 \,^{\circ}\text{C}$ , unless otherwise specified

# 3.16 AC specifications

### 3.16.1 Pad AC specifications

Table 37. Output pin transition times

| Sumb                            | Symbol |    | Parameter                                                                             | Conditions <sup>(1)</sup>    |                                                                    | Value                   |                   | )   | Unit    |                        |                                    |                        |             |   |   |   |  |

|---------------------------------|--------|----|---------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------|-------------------------|-------------------|-----|---------|------------------------|------------------------------------|------------------------|-------------|---|---|---|--|

| Sym                             |        |    | Parameter                                                                             |                              |                                                                    | Min                     | Тур               | Max | Onne    |                        |                                    |                        |             |   |   |   |  |

|                                 |        | D  | <u> </u>                                                                              | $C_L = 25 \text{ pF}$        |                                                                    | _                       | _                 | 50  |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        | Т  |                                                                                       | C <sub>L</sub> = 50 pF       | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0                  | _                       | _                 | 100 |         |                        |                                    |                        |             |   |   |   |  |

|                                 | СС     | D  | Output transition time output pin <sup>(2)</sup>                                      | C <sub>L</sub> = 100 pF      |                                                                    | _                       | _                 | 125 | no      |                        |                                    |                        |             |   |   |   |  |

| t <sub>tr</sub>                 | CC     | D  | SLOW configuration                                                                    | C <sub>L</sub> = 25 pF       |                                                                    | _                       | _                 | 40  | ns      |                        |                                    |                        |             |   |   |   |  |

|                                 |        | Т  |                                                                                       | C <sub>L</sub> = 50 pF       | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1                  | _                       | _                 | 50  |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        | D  |                                                                                       | C <sub>L</sub> = 100 pF      |                                                                    | _                       | _                 | 75  |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        | D  |                                                                                       | C <sub>L</sub> = 25 pF       | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0                  | _                       | _                 | 10  | _       |                        |                                    |                        |             |   |   |   |  |

|                                 |        | Т  |                                                                                       | C <sub>L</sub> = 50 pF       |                                                                    | _                       | _                 | 20  |         |                        |                                    |                        |             |   |   |   |  |

|                                 | СС     | CC | D                                                                                     | D                            | Output transition time output pin <sup>(2)</sup>                   | C <sub>L</sub> = 100 pF | SIUL.PCRx.SRC = 1 | _   | _       | 40                     | no                                 |                        |             |   |   |   |  |

| t <sub>tr</sub>                 | CC     | D  | MEDIUM configuration                                                                  | C <sub>L</sub> = 25 pF       | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | _                       | _                 | 12  | ns<br>- |                        |                                    |                        |             |   |   |   |  |

|                                 |        | Т  |                                                                                       | C <sub>L</sub> = 50 pF       |                                                                    | _                       | -                 | 25  |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        | D  |                                                                                       | C <sub>L</sub> = 100 pF      |                                                                    | _                       | _                 | 40  |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        |    |                                                                                       |                              |                                                                    |                         |                   |     |         | C <sub>L</sub> = 25 pF | $V_{DD} = 5.0 \text{ V} \pm 10\%,$ | _                      | _           | 4 |   |   |  |

|                                 |        |    |                                                                                       |                              |                                                                    |                         |                   |     |         |                        |                                    | C <sub>L</sub> = 50 pF | PAD3V5V = 0 | _ | _ | 6 |  |

|                                 | СС     | D  | Output transition time output pin <sup>(2)</sup>                                      | C <sub>L</sub> = 100 pF      | SIUL.PCRx.SRC = 1                                                  | _                       | _                 | 12  | ns      |                        |                                    |                        |             |   |   |   |  |

| t <sub>tr</sub>                 | CC     | ט  | FAST configuration                                                                    | C <sub>L</sub> = 25 pF       | V <sub>DD</sub> = 3.3 V ± 10%,                                     | _                       | _                 | 4   |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        |    |                                                                                       | C <sub>L</sub> = 50 pF       | PAD3V5V = 1                                                        | _                       | _                 | 7   |         |                        |                                    |                        |             |   |   |   |  |

|                                 |        |    | C <sub>L</sub> = 100 pF                                                               | SIUL.PCRx.SRC = 1            | _                                                                  | _                       | 12                |     |         |                        |                                    |                        |             |   |   |   |  |

| + (3)                           | СС     | т  | Symmetric transition time, same drive $V_{DD} = 5.0 \text{ V} \pm 10\%$ , PAD3V5V = 0 | ± 10%, PAD3V5V = 0           | _                                                                  | _                       | 4                 | na  |         |                        |                                    |                        |             |   |   |   |  |

| t <sub>SYM</sub> <sup>(3)</sup> |        | 1  | strength between N and P transistor                                                   | $V_{DD} = 3.3 \text{ V} \pm$ | ± 10%, PAD3V5V = 1                                                 | _                       | _                 | 5   | ns      |                        |                                    |                        |             |   |   |   |  |

<sup>1.</sup>  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_{A}$  = -40 °C to  $T_{A~MAX}$ , unless otherwise specified

<sup>2.</sup>  $C_L$  includes device and package capacitances ( $C_{PKG}$  < 5 pF).

<sup>3.</sup> Transition timing of both positive and negative slopes will differ maximum 50%

Table 42. DSPI timing<sup>(1)</sup> (continued)

| No  | No. Symbol            | Symbol |    | Symbol C                     |                             | Symbol    |            | Parameter | Conditions | Va   | lue | Unit |  |  |  |  |  |                             |   |    |  |

|-----|-----------------------|--------|----|------------------------------|-----------------------------|-----------|------------|-----------|------------|------|-----|------|--|--|--|--|--|-----------------------------|---|----|--|

| NO. |                       |        |    |                              |                             | Farameter | Conditions | Min       | Max        | Onit |     |      |  |  |  |  |  |                             |   |    |  |

|     |                       |        |    |                              | Master (MTFE = 0)           | _         | 12         |           |            |      |     |      |  |  |  |  |  |                             |   |    |  |

| 11  |                       | o CC D | 00 | _                            | D                           | Slave     | _          | 36        |            |      |     |      |  |  |  |  |  |                             |   |    |  |

| 11  | t <sub>SUO</sub> CC L |        | ט  | Data valid (after SCK edge)  | Master (MTFE = 1, CPHA = 0) | _         | 12         | - ns      |            |      |     |      |  |  |  |  |  |                             |   |    |  |

|     |                       |        |    |                              |                             |           |            |           |            |      |     |      |  |  |  |  |  | Master (MTFE = 1, CPHA = 1) | _ | 12 |  |

|     |                       |        |    |                              | Master (MTFE = 0)           | -2        | _          |           |            |      |     |      |  |  |  |  |  |                             |   |    |  |