#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 107                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p50l5cefay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | 3.14  | Analog   | nalog-to-digital converter (ADC) electrical characteristics |     |  |  |

|---------|-------|----------|-------------------------------------------------------------|-----|--|--|

|         |       | 3.14.1   | Input impedance and ADC accuracy                            | 79  |  |  |

|         |       | 3.14.2   | ADC conversion characteristics                              | 83  |  |  |

|         | 3.15  | Flash n  | nemory electrical characteristics                           | 85  |  |  |

|         | 3.16  | AC spe   | ecifications                                                | 86  |  |  |

|         |       | 3.16.1   | Pad AC specifications                                       | 86  |  |  |

|         | 3.17  | AC timi  | ing characteristics                                         | 87  |  |  |

|         |       | 3.17.1   | RESET pin characteristics                                   | 87  |  |  |

|         |       | 3.17.2   | IEEE 1149.1 interface timing                                | 89  |  |  |

|         |       | 3.17.3   | Nexus timing                                                |     |  |  |

|         |       | 3.17.4   | External interrupt timing (IRQ pin)                         |     |  |  |

|         |       | 3.17.5   | DSPI timing                                                 | 95  |  |  |

| 4       | Packa | age cha  | aracteristics                                               | 101 |  |  |

|         | 4.1   | ECOPA    | ACK®                                                        | 101 |  |  |

|         | 4.2   | Packag   | ge mechanical data                                          | 101 |  |  |

|         |       | 4.2.1    | LQFP144 mechanical outline drawing                          | 101 |  |  |

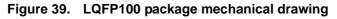

|         |       | 4.2.2    | LQFP100 mechanical outline drawing                          | 103 |  |  |

| 5       | Orde  | ring inf | ormation                                                    | 105 |  |  |

| Appendi | x A A | bbrevia  | ations                                                      | 106 |  |  |

| 6       | Revis | sion his | tory                                                        | 107 |  |  |

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- Up to 8-bytes data length

- Programmable bit rate up to 1 Mbit/s

- 32 message buffers of up to 8-bytes data length

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a six-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

## 1.5.21 Safety port (FlexCAN)

The SPC560P44Lx, SPC560P50Lx MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate as fast as 7.5 Mbit/s at 60 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8 bytes data length

- Can be used as a second independent CAN module

### 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

### 1.5.23 Serial communication interface module (LINFlex)

The LINFlex (local interconnect network flexible) on the SPC560P44Lx, SPC560P50Lx features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and as much as 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors (sync field, delimiter, ID parity, bit framing, checksum, and time-out)

- Classic or extended checksum calculation

- Configurable Break duration as long as 36-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit or 9-bit words)

- Error detection and flagging

- Parity, Noise and Framing errors

- Interrupt-driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with 4 pins (TDI, TMS, TCK, TDO)

- Selectable modes of operation include JTAGC/debug or normal system operation.

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC, ACCESS\_AUX\_TAP\_ONCE

- 3 test data registers: a bypass register, a boundary scan register, and a device identification register.

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry.

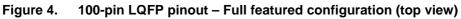

### 1.5.32 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN (negative-positive-negative) transistor

- Regulates external 3.3 V /5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

# 2 Package pinouts and signal descriptions

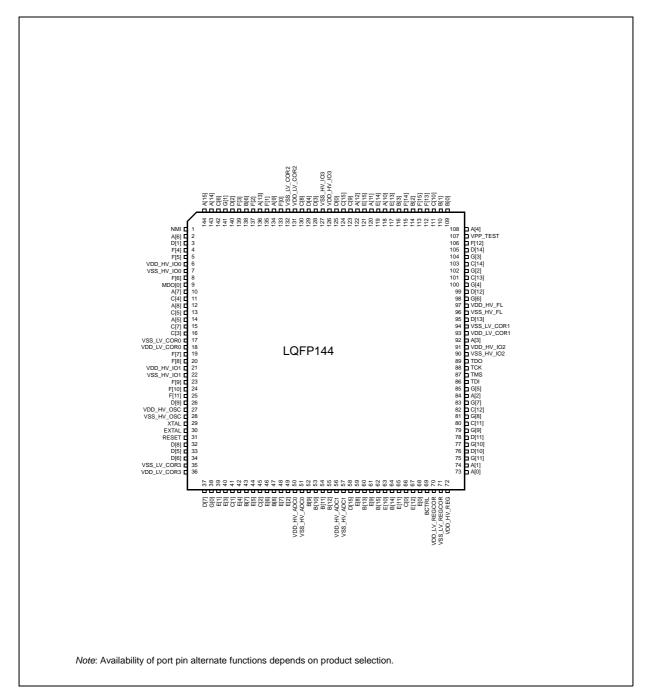

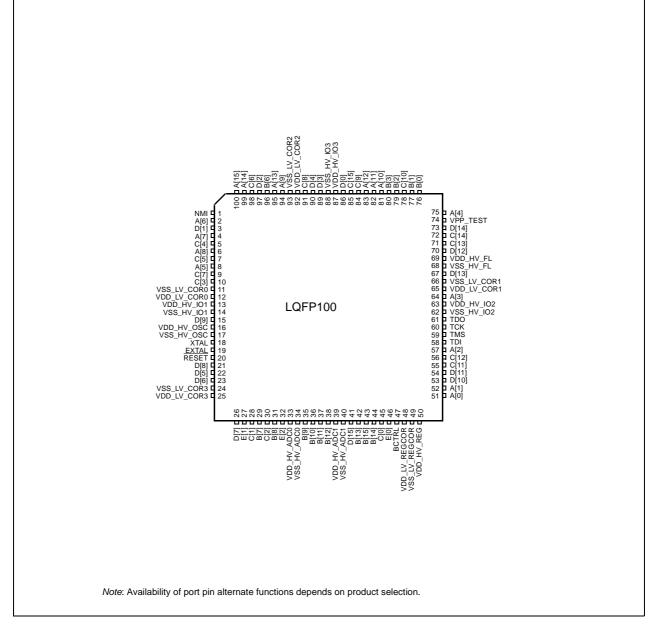

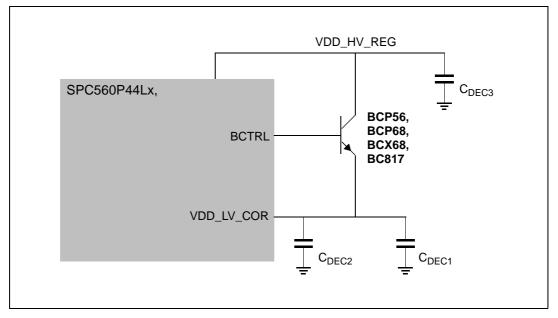

## 2.1 Package pinouts

The LQFP pinouts are shown in the following figures.

Figure 2. 144-pin LQFP pinout – Full featured configuration (top view)

Doc ID 14723 Rev 9

## 2.2 Pin description

The following sections provide signal descriptions and related information about the functionality and configuration of the SPC560P44Lx, SPC560P50Lx devices.

## 2.2.1 Power supply and reference voltage pins

*Table 5* lists the power supply and reference voltage for the SPC560P44Lx, SPC560P50Lx devices.

Doc ID 14723 Rev 9

## **3 Electrical characteristics**

### 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

**Caution:** All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

Table 8.Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

- C.E. Triplett and B. Joiner, An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

## 3.6 Electromagnetic interference (EMI) characteristics

| Symbol           | Parameter          | Conditions                                                                                            | Clocks                                                    | Frequency       | Level<br>(Max) | Unit |

|------------------|--------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|----------------|------|

|                  |                    | 1) ovice contiguration test                                                                           | f <sub>OSC</sub> 8 MHz                                    | 150 kHz–150 MHz | 16             | dBµV |

|                  |                    | adiated emissions<br>Supply voltage = 5 V DC<br>Ambient temperature = 25 °C<br>Worst-case orientation | f <sub>CPU</sub> 64 MHz<br>No PLL frequency<br>modulation | 150–1000 MHz    | 15             | uυμν |

| V                | Padiated emissions |                                                                                                       |                                                           | IEC Level       | М              | —    |

| V <sub>EME</sub> |                    |                                                                                                       | f <sub>OSC</sub> 8 MHz<br>f <sub>CPU</sub> 64 MHz         | 150 kHz–150 MHz | 15             | dBµV |

|                  |                    |                                                                                                       |                                                           | 150–1000 MHz    | 14             | ubµv |

|                  |                    |                                                                                                       | 1% PLL frequency modulation                               | IEC Level       | М              | —    |

#### Table 14. EMI testing specifications

## 3.7 Electrostatic discharge (ESD) characteristics

#### Table 15.ESD ratings(1),(2)

| Symbol                |        | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|--------|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | S<br>R | Electrostatic discharge (Human Body Model)     | _          | 2000          | V    |

|                       | s      | Electrostatic discharge (Charged Device Model) |            | 750 (corners) | v    |

| VESD(CDM)             | R      | Electrostatic discharge (Charged Device Model) | _          | 500 (other)   | v    |

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## **3.8 Power management electrical characteristics**

### 3.8.1 Voltage regulator electrical characteristics

The internal voltage regulator requires an external NPN ballast to be connected as shown in *Figure 9. Table 16* contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the V<sub>DD HV REG</sub>, BCTRL and V<sub>DD LV CORx</sub> pins to less than

Figure 10. Configuration without resistor on base

| Table 18. | Voltage | e reg | gulator electrical characteri | stics (configuration withou | ut resistor on bas | se) |

|-----------|---------|-------|-------------------------------|-----------------------------|--------------------|-----|

|           |         |       |                               |                             |                    |     |

| Symbol                    |    | с | Parameter                                                                | Conditions                                              | Value |     |      | Unit |

|---------------------------|----|---|--------------------------------------------------------------------------|---------------------------------------------------------|-------|-----|------|------|

| Symbol                    |    | C | Falameter                                                                | Conditions                                              | Min   | Тур | Max  | Unit |

| V <sub>DD_LV_REGCOR</sub> | сс | Ρ | Output voltage under<br>maximum load run supply<br>current configuration | Post-trimming                                           | 1.15  | _   | 1.32 | V    |

| C <sub>DEC1</sub>         | SR | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances                                          | 40    | 56  | _    | μF   |

| R <sub>REG</sub>          | SR |   | Resulting ESR of all four<br>C <sub>DEC1</sub>                           | Absolute maximum value<br>between 100 kHz and<br>10 MHz | Ι     |     | 45   | mΩ   |

| C <sub>DEC2</sub>         | SR | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances of 100 nF<br>each                        | 400   | _   | _    | nF   |

| C <sub>DEC3</sub>         | SR |   | External decoupling/stability<br>ceramic capacitor on<br>VDD_HV_REG      | _                                                       | 40    |     | _    | μF   |

| L <sub>Reg</sub>          | SR |   | Resulting ESL of V_DD_HV_REG BCTRL and V_DD_LV_CORx pins                 | —                                                       |       |     | 15   | nH   |

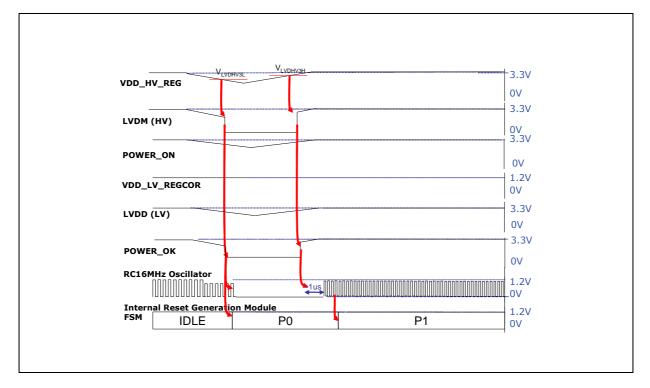

Figure 13. Brown-out typical sequence

## 3.10 DC electrical characteristics

### 3.10.1 NVUSRO register

Portions of the device configuration, such as high voltage supply, and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

### NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. *Table 20* shows how NVUSRO[PAD3V5V] controls the device configuration.

| Table 20. | PAD3V5V field description |

|-----------|---------------------------|

|-----------|---------------------------|

| Value <sup>(1)</sup> | Description                  |

|----------------------|------------------------------|

| 0                    | High voltage supply is 5.0 V |

| 1                    | High voltage supply is 3.3 V |

1. Default manufacturing value before flash initialization is '1' (3.3 V).

| Symbol                  | с | Parameter      |                                  | Conditions                                                    |                                | Value                                                 |       | Unit |    |  |

|-------------------------|---|----------------|----------------------------------|---------------------------------------------------------------|--------------------------------|-------------------------------------------------------|-------|------|----|--|

| Symbol                  | C |                | Farameter                        | Conditions                                                    |                                | Тур                                                   | Max   | Unit |    |  |

|                         |   |                | RUN—Maximum mode <sup>(1)</sup>  |                                                               | 40 MHz                         | 62                                                    | 77    |      |    |  |

|                         | т |                |                                  | V <sub>DD_LV_CORx</sub>                                       | 64 MHz                         | 71                                                    | 89    |      |    |  |

|                         | 1 |                | RUN—Typical mode <sup>(2)</sup>  | externally forced at 1.3 V                                    | 40 MHz                         | 45                                                    | 56    |      |    |  |

|                         |   |                | KON—Typical mode                 |                                                               | 64 MHz                         | 53                                                    | 66    |      |    |  |

| I <sub>DD_LV_CORx</sub> | Ρ |                | RUN—Maximum mode <sup>(3)</sup>  | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | 64 MHz                         | 60                                                    | 75    |      |    |  |

|                         |   | Ρ              | Ρ                                | rent                                                          | HALT mode <sup>(4)</sup>       | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V | _     | 1.5  | 10 |  |

|                         |   | Supply current | STOP mode <sup>(5)</sup>         | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _                              | 1                                                     | 10    | mA   |    |  |

|                         | т | Sup            | Flash during read on single mode | V <sub>DD_HV_FL</sub> at 3.3 V                                |                                | 8                                                     | 10    |      |    |  |

| I <sub>DD_FLASH</sub>   |   | Т              |                                  | Flash during erase operation on single mode                   | V <sub>DD_HV_FL</sub> at 3.3 V | _                                                     | 10    | 12   |    |  |

|                         |   |                | ADC—Maximum mode <sup>(1)</sup>  |                                                               | ADC_1                          | 2.5                                                   | 4     |      |    |  |

| IDD_ADC                 | т |                | VDD_HV_A<br>VDD_HV_A             | V <sub>DD_HV_ADC0</sub> at 3.3 V                              | ADC_0                          | 2                                                     | 4     |      |    |  |

|                         |   |                |                                  | V <sub>DD_HV_ADC1</sub> at 3.3 V<br>f <sub>ADC</sub> = 16 MHz | ADC_1                          | 0.8                                                   | 1     |      |    |  |

|                         |   |                |                                  |                                                               | ADC_0                          | 0.005                                                 | 0.006 |      |    |  |

| I <sub>DD_OSC</sub>     | Т |                | Oscillator                       | V <sub>DD_OSC</sub> at 3.3 V                                  | 8 MHz                          | 2.4                                                   | 3     |      |    |  |

| Table 24. | Supply current ( | 3.3 V, NVUSRO[PAD3V5V] = 1) |

|-----------|------------------|-----------------------------|

|-----------|------------------|-----------------------------|

1. Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

2. Typical mode: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

Code fetched from RAM, PLL\_0: 64 MHz system clock (x4 multiplier with 16 MHz XTAL), PLL\_1 is ON at PHI\_div2 = 120 MHz and PHI\_div3 = 80 MHz, auxiliary clock sources set that all peripherals receive maximum frequency, all peripherals enabled.

4. Halt mode configurations: code fetched from RAM, code and data flash memories in low power mode, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

5. STOP "P" mode Device Under Test (DUT) configuration: code fetched from RAM, code and data flash memories OFF, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

### 3.10.4 Input DC electrical characteristics definition

Figure 14 shows the DC electrical characteristics behavior as function of time.

| Table 26. | I/O weight ( | (continued) |

|-----------|--------------|-------------|

|-----------|--------------|-------------|

| Ded     | LQI       | FP144       | LQFP100   |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[86] | 9%        | 6%          | —         | _           |  |

| MODO[0] | 12%       | 8%          | _         |             |  |

| PAD[7]  | 4%        | 4%          | 11%       | 10%         |  |

| PAD[36] | 5%        | 4%          | 11%       | 9%          |  |

| PAD[8]  | 5%        | 4%          | 10%       | 9%          |  |

| PAD[37] | 5%        | 4%          | 10%       | 9%          |  |

| PAD[5]  | 5%        | 4%          | 9%        | 8%          |  |

| PAD[39] | 5%        | 4%          | 9%        | 8%          |  |

| PAD[35] | 5%        | 4%          | 8%        | 7%          |  |

| PAD[87] | 12%       | 9%          | —         | _           |  |

| PAD[88] | 9%        | 6%          | —         |             |  |

| PAD[89] | 10%       | 7%          | —         | _           |  |

| PAD[90] | 15%       | 11%         | —         | _           |  |

| PAD[91] | 6%        | 5%          | —         | _           |  |

| PAD[57] | 8%        | 7%          | 8%        | 7%          |  |

| PAD[56] | 13%       | 11%         | 13%       | 11%         |  |

| PAD[53] | 14%       | 12%         | 14%       | 12%         |  |

| PAD[54] | 15%       | 13%         | 15%       | 13%         |  |

| PAD[55] | 25%       | 22%         | 25%       | 22%         |  |

| PAD[96] | 27%       | 24%         | —         | _           |  |

| PAD[65] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[67] | 1%        | 1%          | —         | _           |  |

| PAD[33] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[68] | 1%        | 1%          | —         | _           |  |

| PAD[23] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[69] | 1%        | 1%          | —         | _           |  |

| PAD[34] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[70] | 1%        | 1%          | —         | _           |  |

| PAD[24] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[71] | 1%        | 1%          | —         | _           |  |

| PAD[66] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[25] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[26] | 1%        | 1%          | 1%        | 1%          |  |

| Symbol           | С              | Parameter                                    | Conditions <sup>(1)</sup> | Max value | Unit  |

|------------------|----------------|----------------------------------------------|---------------------------|-----------|-------|

| f <sub>max</sub> | 6              | Maximum working frequency at given number of | 2 wait states             | 66        | MHz   |

|                  | wait states in | wait states in worst conditions              | 0 wait states             | 18        | IVIHZ |

#### Table 36. Flash memory read access timing

1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

## 3.16 AC specifications

## 3.16.1 Pad AC specifications

#### Table 37.Output pin transition times

| Symbol C                        |          | ~ | Parameter                                        | Conditions <sup>(1)</sup>                     |                                               | Value |     | )   | Unit |

|---------------------------------|----------|---|--------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------|-----|-----|------|

|                                 |          | C | Farameter                                        |                                               |                                               | Min   | Тур | Max | Unit |

|                                 |          | D |                                                  | C <sub>L</sub> = 25 pF                        |                                               | —     | —   | 50  |      |

|                                 | Т        |   | C <sub>L</sub> = 50 pF                           | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _                                             | _     | 100 |     |      |

| +                               | сс       | D | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                       |                                               | _     | _   | 125 | ne   |

| t <sub>tr</sub>                 |          | D | SLOW configuration                               | C <sub>L</sub> = 25 pF                        |                                               | _     | _   | 40  | ns   |

|                                 |          | Т |                                                  | C <sub>L</sub> = 50 pF                        | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _     | _   | 50  |      |

|                                 |          | D |                                                  | C <sub>L</sub> = 100 pF                       |                                               | _     | _   | 75  |      |

| -                               | D        |   | C <sub>L</sub> = 25 pF                           | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _                                             | _     | 10  |     |      |

|                                 | Т        | C | C <sub>L</sub> = 50 pF                           |                                               | _                                             | _     | 20  |     |      |

| +                               | <u> </u> |   |                                                  | C <sub>L</sub> = 100 pF                       | SIUL.PCRx.SRC = 1                             | _     | _   | 40  | ns   |

| t <sub>tr</sub>                 | 00       |   |                                                  | C <sub>L</sub> = 25 pF                        | $V_{DD} = 3.3 V \pm 10\%$ ,<br>PAD3V5V = 1    | _     | _   | 12  |      |

|                                 |          | Т |                                                  | C <sub>L</sub> = 50 pF                        |                                               | _     | _   | 25  |      |

|                                 |          | D |                                                  | C <sub>L</sub> = 100 pF                       | SIUL.PCRx.SRC = 1                             | _     | _   | 40  |      |

|                                 |          |   |                                                  | C <sub>L</sub> = 25 pF                        | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _     | _   | 4   |      |

|                                 |          |   |                                                  | C <sub>L</sub> = 50 pF                        |                                               | _     | _   | 6   | ns   |

| +                               | сс       | П | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                       | SIUL.PCRx.SRC = 1                             | _     | _   | 12  |      |

| t <sub>tr</sub>                 | 00       |   | FAST configuration                               | C <sub>L</sub> = 25 pF                        | V <sub>DD</sub> = 3.3 V ± 10%,                | _     | _   | 4   |      |

|                                 |          |   | C <sub>L</sub> = 50 pF                           | PAD3V5V = 1                                   | —                                             | —     | 7   |     |      |

|                                 |          |   | C <sub>L</sub> = 100 pF                          | SIUL.PCRx.SRC = 1                             | —                                             | —     | 12  |     |      |

| t <sub>SYM</sub> <sup>(3)</sup> | сс       | т | Symmetric transition time, same drive            | V <sub>DD</sub> = 5.0 V ±                     | ± 10%, PAD3V5V = 0                            |       | —   | 4   | ne   |

| 'SYM`'                          |          |   | strength between N and P transistor              | V <sub>DD</sub> = 3.3 V ±                     | ± 10%, PAD3V5V = 1                            | —     | _   | 5   | ns   |

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

2. CL includes device and package capacitances (CPKG < 5 pF).

3. Transition timing of both positive and negative slopes will differ maximum 50%

| Symbol             |          | с | Deremeter                                                                                                     | Conditions <sup>(1)</sup>                                             | Value |     |     |      |  |                                                                       |   |   |

|--------------------|----------|---|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|--|-----------------------------------------------------------------------|---|---|

|                    |          | C | Parameter                                                                                                     | Conditions                                                            | Min   | Тур | Max | Unit |  |                                                                       |   |   |

|                    |          |   |                                                                                                               | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | —     | —   | 10  |      |  |                                                                       |   |   |

|                    |          |   |                                                                                                               | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _     | _   | 20  |      |  |                                                                       |   |   |

| +                  | <u> </u> | П | Output transition time<br>output pin <sup>(3)</sup>                                                           | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _     | _   | 40  | ns   |  |                                                                       |   |   |

| t <sub>tr</sub>    |          |   | MEDIUM configuration                                                                                          | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _     | —   | 12  | 115  |  |                                                                       |   |   |

|                    |          |   |                                                                                                               | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _     | —   | 25  |      |  |                                                                       |   |   |

|                    |          |   |                                                                                                               |                                                                       |       |     |     |      |  | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _ | _ |

| W <sub>FRST</sub>  | SR       | Ρ | RESET input filtered pulse                                                                                    | _                                                                     | _     | —   | 40  | ns   |  |                                                                       |   |   |

| W <sub>NFRST</sub> | SR       | Ρ | RESET input not<br>filtered pulse                                                                             | _                                                                     | 500   | _   | _   | ns   |  |                                                                       |   |   |

| t <sub>POR</sub>   | сс       | D | Maximum delay before<br>internal reset is<br>released after all<br>V <sub>DD_HV</sub> reach nominal<br>supply | Monotonic V <sub>DD_HV</sub> supply ramp                              | _     | _   | 1   | ms   |  |                                                                       |   |   |

|                    |          |   |                                                                                                               | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                            | 10    | —   | 150 |      |  |                                                                       |   |   |

| I <sub>WPU</sub>   | сс       | Ρ | Weak pull-up current<br>absolute value                                                                        | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                            | 10    | _   | 150 | μA   |  |                                                                       |   |   |

|                    |          |   |                                                                                                               | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(4)</sup>             | 10    | —   | 250 |      |  |                                                                       |   |   |

| Table 38. | <b>RESET</b> electrical characteristics | (continued) | ) |

|-----------|-----------------------------------------|-------------|---|

|           |                                         |             |   |

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified

2. This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of device reference manual).

3.  $C_L$  includes device and package capacitance ( $C_{PKG}$  < 5 pF).

4. The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

## 3.17.2 IEEE 1149.1 interface timing

| Table 39. | JTAG pin AC electrical characteristics |

|-----------|----------------------------------------|

|-----------|----------------------------------------|

| No. | Symbo                                 | 1  | с | Parameter                                              | Conditions | Va  | lue | Unit |

|-----|---------------------------------------|----|---|--------------------------------------------------------|------------|-----|-----|------|

| NO. | Symbo                                 | •  |   | Falameter                                              | Conditions | Min | Max | Unit |

| 1   | t <sub>JCYC</sub>                     | CC | D | TCK cycle time                                         | —          | 100 | —   | ns   |

| 2   | t <sub>JDC</sub>                      | CC | D | TCK clock pulse width (measured at $V_{DD_HV_IOX}/2$ ) | —          | 40  | 60  | ns   |

| 3   | t <sub>TCKRISE</sub>                  | CC | D | TCK rise and fall times (40% – 70%)                    | —          | —   | 3   | ns   |

| 4   | t <sub>TMSS</sub> , t <sub>TDIS</sub> | CC | D | TMS, TDI data setup time                               | —          | 5   | —   | ns   |

57

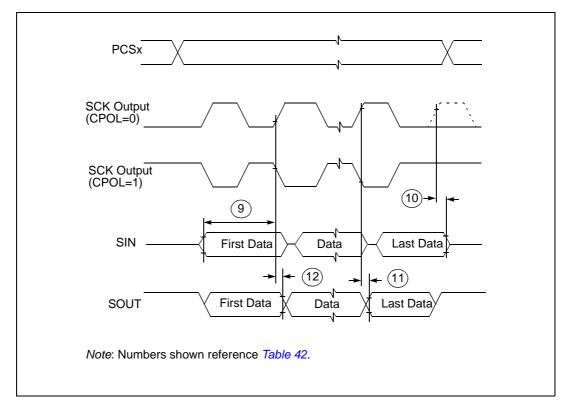

Figure 34. DSPI modified transfer format timing – Master, CPHA = 1

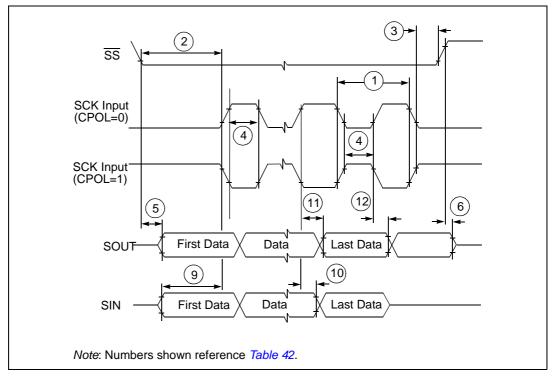

Figure 35. DSPI modified transfer format timing – Slave, CPHA = 0

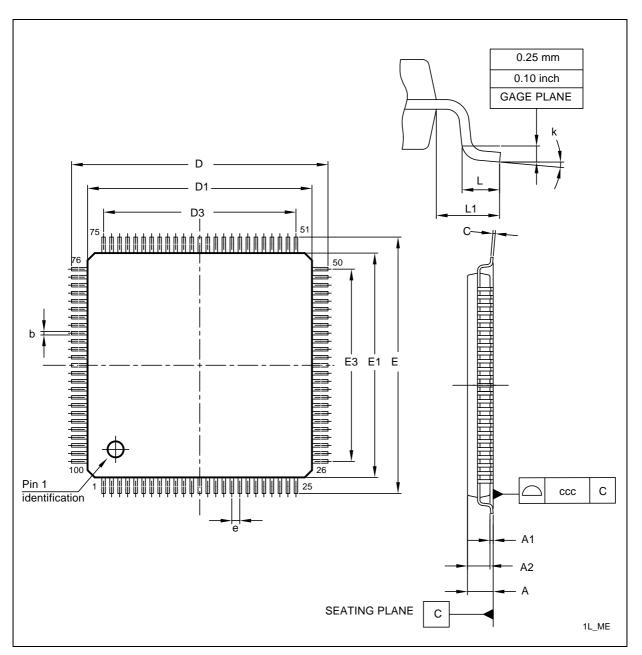

## 4.2.2 LQFP100 mechanical outline drawing

| able 44. L         |            | ige mechanica |        |                       |        |        |  |  |

|--------------------|------------|---------------|--------|-----------------------|--------|--------|--|--|

|                    | Dimensions |               |        |                       |        |        |  |  |

| Symbol             |            | mm            |        | inches <sup>(1)</sup> |        |        |  |  |

|                    | Min        | Тур           | Max    | Min                   | Тур    | Мах    |  |  |

| А                  | —          | —             | 1.600  | —                     | —      | 0.0630 |  |  |

| A1                 | 0.050      | —             | 0.150  | 0.0020                | _      | 0.0059 |  |  |

| A2                 | 1.350      | 1.400         | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b                  | 0.170      | 0.220         | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С                  | 0.090      | —             | 0.200  | 0.0035                | _      | 0.0079 |  |  |

| D                  | 15.800     | 16.000        | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1                 | 13.800     | 14.000        | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| D3                 | —          | 12.000        | —      | —                     | 0.4724 | —      |  |  |

| Е                  | 15.800     | 16.000        | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| E1                 | 13.800     | 14.000        | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3                 | —          | 12.000        | —      | —                     | 0.4724 | —      |  |  |

| е                  | _          | 0.500         | —      | —                     | 0.0197 | —      |  |  |

| L                  | 0.450      | 0.600         | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1                 | —          | 1.000         | —      | —                     | 0.0394 | —      |  |  |

| k                  | 0.0°       | 3.5°          | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |  |

| ccc <sup>(2)</sup> |            | 0.08          | •      |                       | 0.0031 | •      |  |  |

#### Table 44. LQFP100 package mechanical data

1. Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

2. Tolerance

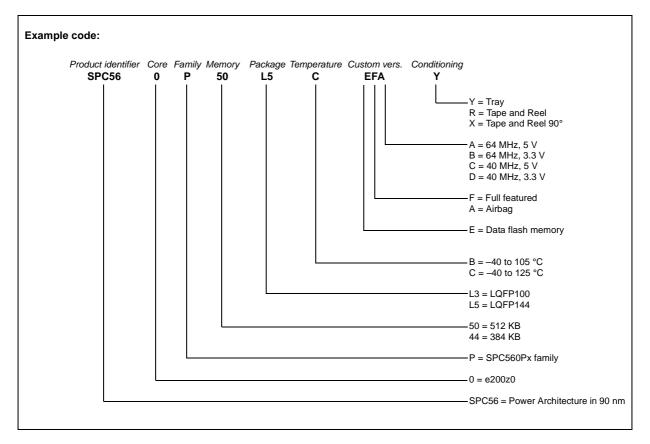

# 5 Ordering information

Figure 40. Commercial product code structure<sup>(a)</sup>

a. Not all configurations are available on the market. Please contact your ST sales representative to get the list of orderable commercial part number.

## Table 46. Revision history (continued)

| Date        | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07-Apr-2011 | 7<br>(cont'd) | SPC560P44Lx, SPC560P50Lx device configuration differences: Removed "temperature"<br>rww (temperature information is provided in Order codes)<br>Updated SPC560P44Lx, SPC560P50Lx block diagram<br>Added SPC560P44Lx, SPC560P50Lx series block summary<br>Added Section 1.5 Feature details<br>Section 2.1, Package pinotts: removed alternate functions from pinout diagrams<br>Supply pins: updated descriptions of power supply pins (1.2 V)<br>System pins: updated table<br>Pin muxing: added rows "B[4]" and "B[5]<br>Section 3.3, Absolute maximum ratings: added voltage specifications to titles of <i>Figure 5</i><br>and <i>Figure 6</i> ; in <i>Table 9</i> , changed row "V <sub>SS_HV</sub> / Digital Ground" to "V <sub>SS</sub> / Device<br>Ground"; updated symbols<br>Section 3.4, Recommended operating conditions: added voltage specifications to titles of<br><i>Figure 7</i> and <i>Figure 8</i><br>Recommended operating conditions (5.0 V), and Recommended operating conditions<br>(3.3 V): changed row "V <sub>SS_HV</sub> / Digital Ground" to "V <sub>SS</sub> / Device Ground"; updated<br>symbols<br>Updated Section 3.6, Electromagnetic interference (EMI) characteristics<br>Section 3.4, 1, Voltage regulator electrical characteristics<br>updated Section 3.6, Electromagnetic interference (EMI) characteristics<br>Section 3.1, 1, Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics: reorganized contents<br>Updated Section 3.10, <i>NUVSRO</i> (PAD3VSV] = 0): updated symbols<br>Corrected parameter descriptions in DC electrical characteristics (3.3 V,<br>NVUSRO[PAD3VSV] = 1):<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage", is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage"; is "Symmetric, low level output<br>voltage"<br>$V_{OL_SYM}$ —was "Symmetric, high level output voltage |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Jul-2012 | 8        | Updated Table 1 (Device summary)<br>Section 1.5.4, Flash memory: Changed "Data flash memory: 32-bit ECC" to "Data flash<br>memory: 64-bit ECC"<br>Figure 40 (Commercial product code structure), replaced "C = 60 MHz, 5 V" and "D = 60<br>MHz, 3.3 V" with respectively "C = 40 MHz, 5 V" and "D = 40 MHz, 3.3 V"<br>Table 9 (Absolute maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum ratings), updated TV <sub>DD</sub> parameter, the minimum value to<br>3.0 V/s and the maximum value to 0.5 V/µs<br>Table 7 (Pin muxing), changed the description in the column "I/O direction" from "I/O" to<br>"O" for the following port pins:<br>A[10] with function B[0]<br>A[11] with function A[2]<br>A[12] with function A[2]<br>A[12] with function B[2]<br>C[7] with function A[3]<br>C[15] with function A[1]<br>D[0] with function A[1]<br>D[10] with function A[1]<br>D[11] with function A[1]<br>D[13] with function A[1]<br>D[14] with function A[1]<br>D[15] with function A[1]<br>D[14] with function B[1]<br>Updated Section 3.8.1, Voltage regulator electrical characteristics<br>Added Table 27 (I/O consumption)<br>Section 3.10, DC electrical characteristics:<br>deleted references to "oscillator margin"<br>deleted subsection "NVUSRO[OSCILLATOR_MARGIN] field description"<br>Table 21 (DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)), added IPU row<br>for RESET pin<br>Table 23 (DC electrical characteristics), added V <sub>INAN</sub> entry<br>Removed "Order codes" table<br>Figure 40 (Commercial product code structure):<br>added a footnote<br>updated "E = Data flash memory" |

| 18-Sep-2013 | 9        | Updated Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 46. Revision history (continued | Table 46. | Revision | history ( | (continued) | ) |

|---------------------------------------|-----------|----------|-----------|-------------|---|

|---------------------------------------|-----------|----------|-----------|-------------|---|