#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| 2 0 0 0 0 0 0                      |                                                                                                   |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                            |

| Core Processor                     | ARM® Cortex®-A8                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 600MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                            |

| RAM Controllers                    | LPDDR, DDR2                                                                                       |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                       |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 (3), USB 2.0 + PHY (1)                                                                    |

| Voltage - I/O                      | 1.2V, 1.875V, 2.775V, 3.0V                                                                        |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 529-LFBGA                                                                                         |

| Supplier Device Package            | 529-BGA (19x19)                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx514ajm6cr2                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block<br>Mnemonic             | Block Name                                                               | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|--------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMI                           | External<br>Memory<br>Interface                                          | Connectivity<br>Peripherals | <ul> <li>The EMI is an external and internal memory interface. It performs arbitration between multi-AXI masters to multi-memory controllers, divided into four major channels: fast memories (Mobile DDR, DDR2) channel, slow memories (NOR-FLASH/PSRAM/NAND-FLASH and so on) channel, internal memory (RAM, ROM) channel and graphical memory (GMEM) Channel.</li> <li>In order to increase the bandwidth performance, the EMI separates the buffering and the arbitration between different channels so parallel accesses can occur. By separating the channels, slow accesses do not interfere with fast accesses. EMI features:</li> <li>64-bit and 32-bit AXI ports</li> <li>Enhanced arbitration scheme for fast channel, including dynamic master priority, and taking into account which pages are open or closed and what type (Read or Write) was the last access</li> <li>Flexible bank interleaving</li> <li>Supports 16/32-bit Mobile DDR up to 200 MHz SDCLK (mDDR400)</li> <li>Supports 16/32-bit Mobile DDR memories</li> <li>Supports 16/32-bit Nobile DDR memories</li> <li>Supports 16-bit (in muxed mode only) PSRAM memories (sync and async operating modes), at slow frequency, for debugging purposes</li> <li>Supports 4/8-ECC, page sizes of 512 Bytes, 2 Kbytes and 4 Kbytes</li> <li>NAND-Flash (including MLC)</li> <li>Multiple chip selects</li> <li>Enhanced Mobile DDR memory controller, supporting access latency hiding</li> <li>Supports Samsung OneNAND<sup>TM</sup> (only in muxed I/O mode)</li> </ul> |

| EPIT-1<br>EPIT-2              | Enhanced<br>Periodic<br>Interrupt<br>Timer                               | Timer<br>Peripherals        | Each EPIT is a 32-bit "set and forget" timer that starts counting after the EPIT is<br>enabled by software. It is capable of providing precise interrupts at regular<br>intervals with minimal processor intervention. It has a 12-bit prescaler for division<br>of input clock frequency to get the required time setting for the interrupts to occur,<br>and counter values can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| eSDHC-1<br>eSDHC-2<br>eSDHC-3 | Enhanced<br>Multi-Media<br>Card/<br>Secure Digital<br>Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>The features of the eSDHC module, when serving as host, include the following:</li> <li>Conforms to SD Host Controller Standard Specification version 2.0</li> <li>Compatible with the MMC System Specification version 4.2</li> <li>Compatible with the SD Memory Card Specification version 2.0</li> <li>Compatible with the SDIO Card Specification version 1.2</li> <li>Designed to work with SD Memory, miniSD Memory, SDIO, miniSDIO, SD Combo, MMC and MMC RS cards</li> <li>Configurable to work in one of the following modes: <ul> <li>—SD/SDIO 1-bit, 4-bit</li> <li>—MMC 1-bit, 4-bit</li> <li>Full-/high-speed mode</li> <li>Host clock frequency variable between 32 kHz to 52 MHz</li> <li>Up to 200 Mbps data transfer for SD/SDIO cards using four parallel data lines</li> <li>Up to 416 Mbps data transfer for MMC cards using eight parallel data lines</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### Table 2. i.MX51A Digital and Analog Modules (continued)

Features

.

| Block<br>Mnemonic          | Block Name                                    | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-----------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TZIC                       | TrustZone<br>Aware<br>Interrupt<br>Controller | ARM/Control                 | The TrustZone Interrupt Controller (TZIC) collects interrupt requests from all i.MX51 sources and routes them to the ARM core. Each interrupt can be configured as a normal or a secure interrupt. Software Force Registers and software Priority Masking are also supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| UART-1<br>UART-2<br>UART-3 | UART<br>Interface                             | Connectivity<br>Peripherals | <ul> <li>Each of the UART modules supports the following serial data transmit/receive protocols and configurations:</li> <li>7 or 8 bit data words, 1 or 2 stop bits, programmable parity (even, odd, or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and previous Freescale UART modules.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| USB                        | USB 2.0<br>High-Speed<br>OTG and 3x<br>Hosts  | Connectivity<br>Peripherals | USB-OTG contains one high-speed OTG module, which is internally connected<br>to the on-chip HS USB PHY. There are an additional three high-speed host<br>modules that require external USB PHYs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VPU                        | Video<br>Processing<br>Unit                   | Multimedia<br>Peripherals   | <ul> <li>A high-performing video processing unit (VPU), which covers many SD-level video decoders and SD-level encoders as a multi-standard video codec engine as well as several important video processing such as rotation and mirroring. VPU Features:</li> <li>MPEG-4 decode: 720p, 30 fps, simple profile and advanced simple profile</li> <li>MPEG-4 encode: D1, 25/30 fps, simple profile</li> <li>H.263 decode: 720p, 30 fps, profile 3</li> <li>H.263 encode: D1, 25/30 fps, baseline, main, and high profile</li> <li>H.264 decode: 720p, 30 fps, baseline profile</li> <li>H.264 encode: D1, 25/30 fps, baseline profile</li> <li>MPEG-2 decode: 720p, 30 fps, baseline profile</li> <li>MPEG-2 decode: 720p, 30 fps, MP-ML</li> <li>MPEG-2 encode: D1, 25/30 fps, MP-ML (in software with partial acceleration in hardware)</li> <li>VC-1 decode: 720p, 30 fps versions 3, 4, and 5</li> <li>RV10 decode: 720p, 30 fps</li> <li>MJPEG decode: 32 Mpix/s</li> <li>MJPEG encode: 64 Mpix/s</li> </ul> |

| WDOG-1                     | Watch Dog                                     | Timer<br>Peripherals        | The Watch Dog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table 2. i.MX51 | A Digital and | I Analog Mo | odules ( | continued) |

|-----------------|---------------|-------------|----------|------------|

|-----------------|---------------|-------------|----------|------------|

Table 13 shows the i.MX51 operating ranges.

| Symbol                                                                                      | Parameter                                                                                                                                                                                                                                                                                                                                                     | Minimum <sup>1</sup> | Nominal <sup>2</sup> | Maximum <sup>1</sup> | Unit |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| VDDGP<br>MCIMX51xA products                                                                 | ARM core supply voltage<br>$0 < f_{ARM} \le 600 \text{ MHz}$                                                                                                                                                                                                                                                                                                  | 0.95                 | 1.0                  | 1.1                  | V    |

|                                                                                             | ARM core supply voltage<br>Stop mode                                                                                                                                                                                                                                                                                                                          | 0.9                  | 0.95                 | 1.05                 | V    |

| VCC<br>MCIMX51xA products                                                                   | Peripheral supply voltage High Performance<br>Mode (HPM) The clock frequencies are derived<br>from AXI and AHB buses using 133 or 166 MHz<br>(as needed). The DDR clock rate is 200 MHz.<br><b>Note:</b> For detailed information about the use of<br>133 or 166 MHz clocks, see i.MX51 Multimedia<br>Applications Processor Reference Manual<br>(MCIMX51RM). | 1.175                | 1.225                | 1.275                | V    |

|                                                                                             | Peripheral supply voltage—Stop mode                                                                                                                                                                                                                                                                                                                           | 0.9                  | 0.95                 | 1.275                | V    |

| VDDA                                                                                        | Memory arrays voltage—Run Mode                                                                                                                                                                                                                                                                                                                                | 1.15                 | 1.20                 | 1.275                | V    |

|                                                                                             | Memory arrays voltage—Stop Mode                                                                                                                                                                                                                                                                                                                               | 0.9                  | 0.95                 | 1.275                | V    |

| VDD_DIG_PLL_A<br>VDD_DIG_PLL_B                                                              | PLL Digital supplies                                                                                                                                                                                                                                                                                                                                          | 1.15                 | 1.2                  | 1.35                 | V    |

| VDD_ANA_PLL_A<br>VDD_ANA_PLL_B                                                              | PLL Analog supplies                                                                                                                                                                                                                                                                                                                                           | 1.75                 | 1.8                  | 1.95                 | V    |

| NVCC_EMI<br>NVCC_PER5<br>NVCC_PER10<br>NVCC_PER11<br>NVCC_PER12<br>NVCC_PER13<br>NVCC_PER14 | GPIO EMI Supply and additional digital power supplies.                                                                                                                                                                                                                                                                                                        | 1.65                 | 1.875 or<br>2.775    | 3.1                  | V    |

| NVCC_IPUx <sup>3</sup><br>NVCC_PER3<br>NVCC_PER8<br>NVCC_PER9                               | GPIO IPU Supply and additional digital power supplies.                                                                                                                                                                                                                                                                                                        | 1.65                 | 1.875 or<br>2.775    | 3.1                  | V    |

| NVCC_EMI_DRAM                                                                               | DDR and Fuse Read Supply                                                                                                                                                                                                                                                                                                                                      | 1.65                 | 1.8                  | 1.95                 | V    |

| VDD_FUSE <sup>4</sup>                                                                       | Fusebox Program Supply (Write Only)                                                                                                                                                                                                                                                                                                                           | 3.0                  | —                    | 3.3                  | V    |

| NVCC_NANDF_x <sup>5</sup>                                                                   | Ultra High voltage I/O (UHVIO) supplies                                                                                                                                                                                                                                                                                                                       |                      | _                    |                      | V    |

| NVCC_PER15<br>NVCC_PER17                                                                    | UHVIO_L                                                                                                                                                                                                                                                                                                                                                       | 1.65                 | 1.875                | 1.95                 |      |

|                                                                                             | UHVIO_H                                                                                                                                                                                                                                                                                                                                                       | 2.5                  | 2.775                | 3.1                  |      |

|                                                                                             | UHVIO_UH                                                                                                                                                                                                                                                                                                                                                      | 3.0                  | 3.3                  | 3.6                  |      |

| NVCC_USBPHY<br>NVCC_OSC                                                                     | USB_PHY analog supply, oscillator analog supply <sup>6</sup>                                                                                                                                                                                                                                                                                                  | 2.25                 | 2.5                  | 2.75                 | V    |

| TVDAC_DHVDD,<br>NVCC_TV_BACK,<br>AHVDDRGB                                                   | TVE-to-DAC level shifter supply, cable detector supply, analog power supply to RGB channel                                                                                                                                                                                                                                                                    | 2.69                 | 2.75                 | 2.91                 | V    |

### Table 13. i.MX51A Operating Ranges

### 4.3.7 USB Port Electrical DC Characteristics

Table 23 and Table 24 list the electrical DC characteristics.

| Table 23. USE | BOTG Interface Electric | al Specification |

|---------------|-------------------------|------------------|

|---------------|-------------------------|------------------|

| Parameter           | Symbol | Signals                                                      | Min        | Мах       | Unit | Test Conditions           |

|---------------------|--------|--------------------------------------------------------------|------------|-----------|------|---------------------------|

| Input High Voltage  | VIH    | USB_VPOUT<br>USB_VMOUT<br>USB_XRXD,<br>USB_VPIN,<br>USB_VMIN | VDD x 0.7  | VDD       | V    | _                         |

| Input low Voltage   | VIL    | USB_VPOUT<br>USB_VMOUT<br>USB_XRXD,<br>USB_VPIN,<br>USB_VMIN | 0          | VDD × 0.3 | V    | _                         |

| Output High Voltage | VOH    | USB_VPOUT<br>USB_VMOUT<br>USB_TXENB                          | VDD – 0.43 | _         | V    | 7 mA Drv<br>at IOH = 5 mA |

| Output Low Voltage  | VOL    | USB_VPOUT<br>USB_VMOUT<br>USB_TXENB                          | _          | 0.43      | V    | 7 mA Drv<br>at IOH = 5 mA |

### Table 24. USB Interface Electrical Specification

| Parameter           | Symbol | Signals                                                     | Min       | Мах       | Unit | Test Conditions            |

|---------------------|--------|-------------------------------------------------------------|-----------|-----------|------|----------------------------|

| Input High Voltage  | VIH    | USB_DAT_VP<br>USB_SE0_VM<br>USB_RCV,<br>USB_VP1,<br>USB_VM1 | VDD x 0.7 | VDD       | V    | _                          |

| Input Low Voltage   | VIL    | USB_DAT_VP<br>USB_SE0_VM<br>USB_RCV,<br>USB_VP1,<br>USB_VM1 | 0         | VDD x 0.3 | V    | _                          |

| Output High Voltage | VOH    | USB_DAT_VP<br>USB_SE0_VM<br>USB_TXOE_B                      | VDD0.43   | —         | V    | 7 mA Drv<br>at lout = 5 mA |

| Output Low Voltage  | VOL    | USB_DAT_VP<br>USB_SE0_VM<br>USB_TXOE_B                      | —         | 0.43      | V    | 7 mA Drv<br>at lout = 5 mA |

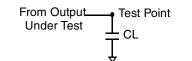

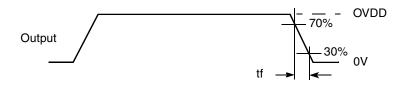

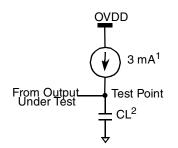

Figure 6 depicts the load circuit for output pads for standard- and fast-mode. Figure 7 depicts the output pad transition time definition. Figure 8 depicts load circuit with external pull-up current source for HS-mode. Figure 9 depicts HS-mode timing definition.

CL includes package, probe and fixture capacitance

### Figure 6. Load Circuit for Standard and Fast-Mode

Figure 7. Definition of Timing for Standard and Fast-Mode

#### Notes:

<sup>1</sup>Load current when output is between 0.3×OVDD and 0.7×OVDD <sup>2</sup>CL includes package, probe, and fixture capacitance.

#### Figure 8. Load Circuit for HS-Mode with External Pull-Up Current Source

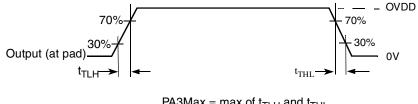

$\begin{array}{l} \mbox{PA3Max} = \mbox{max of } t_{TLH} \mbox{ and } t_{THL} \\ \mbox{PA4Max} = \mbox{max } t_{THL} \end{array}$

- <sup>1</sup> Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5=101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

- <sup>2</sup> Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and -40 °C.

- <sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

AC electrical characteristics in DDR2 mode for Fast mode and for ovdd=1.65–1.95V, ipp\_hve=0 are placed in Table 41.

| Parameter                                                        | Symbol | Test<br>Condition | Min<br>rise/fall       | Тур                    | Max<br>rise/fall       | Units |

|------------------------------------------------------------------|--------|-------------------|------------------------|------------------------|------------------------|-------|

| Output Pad Transition Times <sup>1</sup>                         | tpr    | 15pF<br>35pF      | 0.58/0.57<br>1.29/1.28 | 0.45/0.44<br>0.97/0.93 | 0.45/0.45<br>0.82/0.85 | ns    |

| Output Pad Propagation Delay, 50%-50% <sup>1</sup>               | tpo    | 15pF<br>35pF      | 1.05/1.03<br>1.54/1.56 | 1.40/1.31<br>1.75/1.69 | 2.12/1.96<br>2.43/2.31 | ns    |

| Output Pad Slew Rate <sup>1</sup>                                | tps    | 15pF<br>35pF      | 2.02/2.05<br>0.91/0.91 | 2.40/2.45<br>1.11/1.16 | 2.20/2.20<br>1.21/1.16 | V/ns  |

| Output Pad di/dt <sup>1</sup>                                    | di/dt  | —                 | 390                    | 201                    | 99                     | mA/ns |

| Input Pad Transition Times <sup>2</sup>                          | trfi   | 1.2 pF            | 0.09/0.09              | 0.132/0.128            | 0.212/0.213            | ns    |

| Input Pad Propagation Delay (DDR input),<br>50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.3/0.36               | 0.5/0.52               | 0.82/0.94              | ns    |

| Maximum Input Transition Times <sup>3</sup>                      | trm    | —                 | —                      | _                      | 5                      | ns    |

Table 41. AC Electrical Characteristics of DDR2\_clk IO Pads for Fast mode and for ovdd=1.65–1.95 V

Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5=101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

<sup>2</sup> Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and -40 °C.

<sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

AC electrical characteristics in DDR2 mode for Slow mode and for ovdd=1.65-1.95V, ipp\_hve=0 are placed in Table 42.

Table 42. AC Electrical Characteristics of DDR2\_clk IO Pads for Slow mode and for ovdd=1.65 – 1.95 V (ipp\_hve=0)

| Parameter                                          | Symbol | Test<br>Condition | Min<br>rise/fall       | Тур                    | Max<br>rise/fall       | Units |

|----------------------------------------------------|--------|-------------------|------------------------|------------------------|------------------------|-------|

| Output Pad Transition Times <sup>1</sup>           | tpr    | 15pF<br>35pF      | 0.74/0.76<br>1.40/1.39 | 0.69/0.72<br>1.18/1.20 | 1.04/1.01<br>1.48/1.47 | ns    |

| Output Pad Propagation Delay, 50%-50% <sup>1</sup> | tpo    | 15pF<br>35pF      | 1.56/1.61<br>2.12/2.22 | 2.02/2.08<br>2.49/2.61 | 3.45/3.33<br>4.05/3.98 | ns    |

| Output Pad Slew Rate <sup>1</sup>                  | tps    | 15pF<br>35pF      | 1.58/1.54<br>0.84/0.84 | 1.57/1.50<br>0.92/0.90 | 0.95/0.98<br>0.67/0.67 | V/ns  |

#### Table 42. AC Electrical Characteristics of DDR2\_clk IO Pads for Slow mode and for ovdd=1.65 - 1.95 V (ipp\_hve=0) (continued)

| Parameter                                                        | Symbol | Test<br>Condition | Min<br>rise/fall | Тур         | Max<br>rise/fall | Units |

|------------------------------------------------------------------|--------|-------------------|------------------|-------------|------------------|-------|

| Output Pad di/dt <sup>1</sup>                                    | di/dt  | —                 | 82               | 40          | 19               | mA/ns |

| Input Pad Transition Times <sup>2</sup>                          | trfi   | 1.2 pF            | 0.09/0.09        | 0.132/0.128 | 0.212/0.213      | ns    |

| Input Pad Propagation Delay (DDR input),<br>50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.3/0.36         | 0.5/0.52    | 0.82/0.94        | ns    |

| Maximum Input Transition Times <sup>3</sup>                      | trm    | —                 | —                | _           | 5                | ns    |

<sup>1</sup> Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5=101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

<sup>2</sup> Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and -40 °C.

<sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

AC electrical characteristics in DDR mobile for Fast mode and ovdd=1.65-1.95V, ipp\_hve=0 are placed in Table 43.

### Table 43. AC Electrical Characteristics of DDR\_clk mobile IO Pads for Fast mode and ovdd=1.65 – 1.95 V (ipp\_hve=0)

| Parameter                                                | Symbol | Test<br>Condition | Min<br>rise/fall       | Тур                    | Max<br>rise/fall       | Units |

|----------------------------------------------------------|--------|-------------------|------------------------|------------------------|------------------------|-------|

| Output Pad Transition Times (High Drive) <sup>1</sup>    | tpr    | 15pF<br>35pF      | 1.35/1.32<br>3.01/2.96 | 1.03/1.03<br>2.29/2.30 | 0.89/0.89<br>1.84/1.92 | ns    |

| Output Pad Transition Times (Medium Drive) <sup>1</sup>  | tpr    | 15pF<br>35pF      | 1.98/1.98<br>4.52/4.38 | 1.55/1.54<br>3.46/3.45 | 1.29/1.30<br>2.80/2.88 | ns    |

| Output Pad Transition Times (Low Drive) <sup>1</sup>     | tpr    | 15pF<br>35pF      | 3.99/3.94<br>8.93/8.86 | 3.10/3.04<br>6.77/6.85 | 2.50/2.57<br>5.40/5.68 | ns    |

| Output Pad Propagation Delay (High Drive) <sup>1</sup>   | tpo    | 15pF<br>35pF      | 1.60/1.58<br>2.74/2.81 | 1.85/1.74<br>2.71/2.67 | 2.58/2.31<br>3.26/3.08 | ns    |

| Output Pad Propagation Delay (Medium Drive) <sup>1</sup> | tpo    | 15pF<br>35pF      | 2.07/2.08<br>3.79/3.92 | 2.19/2.12<br>3.46/3.51 | 2.86/2.62<br>3.87/3.77 | ns    |

| Output Pad Propagation Delay (Low Drive) <sup>1</sup>    | tpo    | 15pF<br>35pF      | 3.47/3.57<br>6.94/7.26 | 3.23/3.25<br>5.84/6.06 | 3.69/3.55<br>5.73/5.87 | ns    |

| Output Pad Slew Rate (High Drive) <sup>1</sup>           | tps    | 15pF<br>35pF      | 0.87/0.89<br>0.39/0.40 | 1.05/1.05<br>0.47/0.47 | 1.11/1.11<br>0.54/0.52 | V/ns  |

| Output Pad Slew Rate (Medium Drive) <sup>1</sup>         | tps    | 15pF<br>35pF      | 0.59/0.59<br>0.26/0.27 | 0.70/0.70<br>0.31/0.31 | 0.77/0.76<br>0.35/0.34 | V/ns  |

| Output Pad Slew Rate (Low Drive) <sup>1</sup>            | tps    | 15pF<br>35pF      | 0.29/0.30<br>0.13/0.13 | 0.35/0.36<br>0.16/0.16 | 0.40/0.39<br>0.18/0.17 | V/ns  |

| Output Pad di/dt (High Drive) <sup>1</sup>               | di/dt  | —                 | 185                    | 91                     | 46                     | mA/ns |

| Output Pad di/dt (Medium drive) <sup>1</sup>             | di/dt  | —                 | 124                    | 61                     | 31                     | mA/ns |

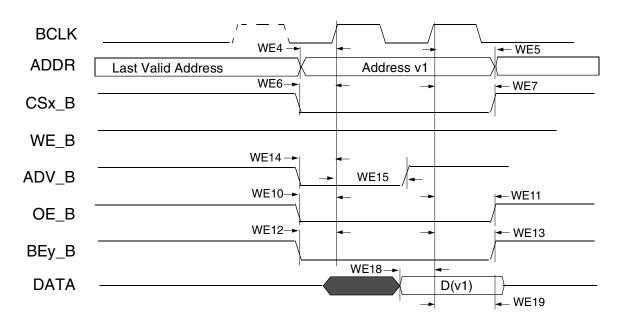

- <sup>1</sup> t is the maximal WEIM logic (axi\_clk) cycle time. The maximum allowed axi\_clk frequency is 133 MHz, whereas the maximum allowed BCLK frequency is 104 MHz. As a result, if BCD = 0, axi\_clk must be ≤ 104 MHz. If BCD = 1, then 133 MHz is allowed for axi\_clk, resulting in a BCLK of 66.5 MHz. When the clock branch to WEIM is decreased to 104 MHz, other busses are impacted which are clocked from this source. See the CCM chapter of the i.MX51 Reference Manual for a detailed clock tree description.

- <sup>2</sup> BCLK parameters are being measured from the 50% point, that is, high is defined as 50% of signal value and low is defined as 50% as signal value.

- <sup>3</sup> For signal measurements "High" is defined as 80% of signal value and "Low" is defined as 20% of signal value.

### 4.6.7.4 Examples of WEIM Synchronous Accesses

Figure 22 to Figure 25 provide few examples of basic WEIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 22. Synchronous Memory Read Access, WSC=1

| ID  | Parameter              | Symbols           | Min | Мах | Unit |

|-----|------------------------|-------------------|-----|-----|------|

| SD7 | eSDHC Input Setup Time | t <sub>ISU</sub>  | 2.5 | —   | ns   |

| SD8 | eSDHC Input Hold Time  | t <sub>IH</sub> ⁵ | 2.5 | —   | ns   |

### Table 69. eSDHCv2 Interface Timing Specification (continued)

<sup>1</sup> In low speed mode, card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

<sup>2</sup> In normal speed mode for SD/SDIO card, clock frequency can be any value between 0–25 MHz. In high-speed mode, clock frequency can be any value between 0–50 MHz.

<sup>3</sup> In normal speed mode for MMC card, clock frequency can be any value between 0–20 MHz. In high-speed mode, clock frequency can be any value between 0–52 MHz.

<sup>4</sup> Measurement taken with CLoad = 20 pF

<sup>5</sup> To satisfy hold timing, the delay difference between clock input and cmd/data input must not exceed 2 ns.

### 4.7.4 FEC AC Timing Parameters

This section describes the electrical information of the Fast Ethernet Controller (FEC) module. The FEC is designed to support both 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The FEC supports the 10/100 Mbps MII (18 pins in total) and the 10 Mbps-only 7-wire interface, which uses 7 of the MII pins, for connection to an external Ethernet transceiver. For the pin list of MII and 7-wire, see i.MX51 Multimedia Applications Processor Reference Manual (MCIMX51RM).

This section describes the AC timing specifications of the FEC.

### 4.7.4.1 MII Receive Signal Timing

The MII receive signal timing involves the FEC\_RXD[3:0], FEC\_RX\_DV, FEC\_RX\_ER, and FEC\_RX\_CLK signals. The receiver functions correctly up to a FEC\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement but the processor clock frequency must exceed twice the FEC\_RX\_CLK frequency. Table 70 lists the MII receive channel signal timing parameters and Figure 43 shows MII receive signal timings.

| Num | Characteristic <sup>1</sup>                            | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | FEC_RXD[3:0], FEC_RX_DV, FEC_RX_ER to FEC_RX_CLK setup | 5   | _   | ns                |

| M2  | FEC_RX_CLK to FEC_RXD[3:0], FEC_RX_DV, FEC_RX_ER hold  | 5   | _   | ns                |

| M3  | FEC_RX_CLK pulse width high                            | 35% | 65% | FEC_RX_CLK period |

| M4  | FEC_RX_CLK pulse width low                             | 35% | 65% | FEC_RX_CLK period |

### Table 70. MII Receive Signal Timing

<sup>1</sup> FEC\_RX\_DV, FEC\_RX\_CLK, and FEC\_RXD0 have same timing in 10 Mbps 7-wire interface mode.

# NP

#### **Electrical Characteristics**

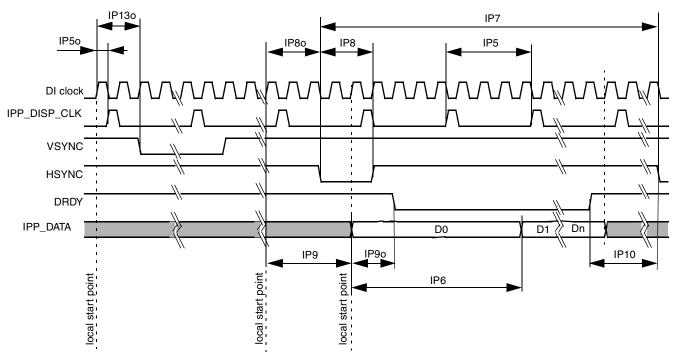

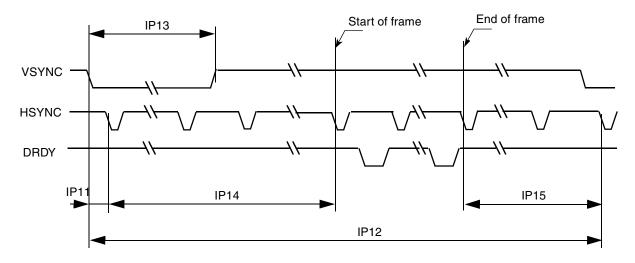

- VSYNC—Vertical synchronization

- DRDY—Active data

All synchronous display controls are generated on base of an internal generated "local start point". The synchronous display controls can be placed on time axis with DI's offset, up and down parameters. The display access can be whole number of DI clock (Tdiclk) only. The IPP\_DATA can not be moved relative to the local start point.

### 4.7.8.5.2 LCD Interface Functional Description

Figure 53 depicts the LCD interface timing for a generic active matrix color TFT panel. In this figure signals are shown with negative polarity. The sequence of events for active matrix interface timing is:

- DI\_CLK internal DI clock, used for calculation of other controls.

- IPP\_DISP\_CLK latches data into the panel on its negative edge (when positive polarity is selected). In active mode, IPP\_DISP\_CLK runs continuously.

- HSYNC causes the panel to start a new line. (Usually IPP\_PIN\_2 is used as HSYNC)

- VSYNC causes the panel to start a new frame. It always encompasses at least one HSYNC pulse. (Usually IPP\_PIN\_3 is used as VSYNC)

- DRDY acts like an output enable signal to the CRT display. This output enables the data to be shifted onto the display. When disabled, the data is invalid and the trace is off. (For DRDY can be used either synchronous or asynchronous generic purpose pin as well.)

|                  | VSYNC        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | HSYNC        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $\left( \right)$ | HSYNC        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | DRDY         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | IPP_DISP_CLK | 1 2 3<br>m-1 m<br>m-1 m<br>m- |

|                  | IPP_DATA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Figure 53. Interface Timing Diagram for TFT (Active Matrix) Panels

### 4.7.8.5.3 TFT Panel Sync Pulse Timing Diagrams

Figure 54 depicts the horizontal timing (timing of one line), including both the horizontal sync pulse and the data. All shown on the figure parameters are programmable. All controls are started by corresponding

internal events—local start points. The timing diagrams correspond to inverse polarity of the IPP\_DISP\_CLK signal and active-low polarity of the HSYNC, VSYNC and DRDY signals.

Figure 54. TFT Panels Timing Diagram—Horizontal Sync Pulse

Figure 55 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

Figure 55. TFT Panels Timing Diagram—Vertical Sync Pulse

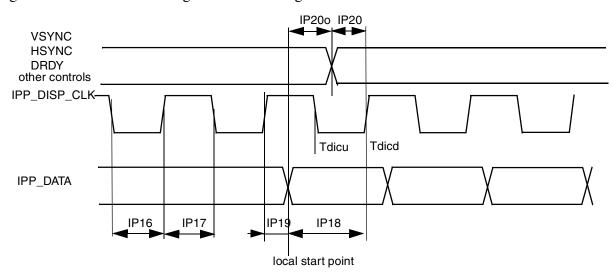

The maximal accuracy of UP/DOWN edge of IPP\_DATA is

Accuracy =  $T_{diclk} \pm 0.75$ ns

The DISP\_CLK\_PERIOD, DI\_CLK\_PERIOD parameters are programmed via registers.

Figure 56 shows the synchronous display interface timing diagram for access level. The DISP\_CLK\_DOWN and DISP\_CLK\_UP parameters are set by using the register. Table 81 shows the timing characteristics for the diagram shown in Figure 56.

Figure 56. Synchronous Display Interface Timing Diagram—Access Level

| Table 81. Synchronous | Display Interf | ace Timing Charact | eristics (Access Level) |

|-----------------------|----------------|--------------------|-------------------------|

|                       |                |                    |                         |

| ID    | Parameter                                                                             | Symbol | Min                   | Typ <sup>1</sup>                      | Мах                   | Unit |

|-------|---------------------------------------------------------------------------------------|--------|-----------------------|---------------------------------------|-----------------------|------|

| IP16  | Display interface clock<br>low time                                                   | Tckl   | Tdicd-Tdicu-1.5       | Tdicd <sup>2</sup> Tdicu <sup>3</sup> | Tdicd-Tdicu+1.5       | ns   |

| IP17  | Display interface clock<br>high time                                                  | Tckh   | Tdicp-Tdicd+Tdicu-1.5 | Tdicp-Tdicd+Tdicu                     | Tdicp-Tdicd+Tdicu+1.5 | ns   |

| IP18  | Data setup time                                                                       | Tdsu   | Tdicd-1.5             | Tdicu                                 | —                     | ns   |

| IP19  | Data holdup time                                                                      | Tdhd   | Tdicp-Tdicd-1.5       | Tdicp-Tdicu                           | —                     | ns   |

| IP20o | Control signals offset<br>times (defines for each<br>pin)                             | Tocsu  | Tocsu–1.5             | Tocsu                                 | Tocsu+1.5             | —    |

| IP20  | Control signals setup<br>time to display interface<br>clock (defines for each<br>pin) | Tcsu   | Tdicd-1.5-Tocsu%Tdicp | Tdicu                                 | _                     | ns   |

<sup>1</sup>The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be chip specific.

joining the internal data lines to the bidirectional external line according to the IPP\_OBE\_DISPB\_SD\_D signal provided by the IPU.

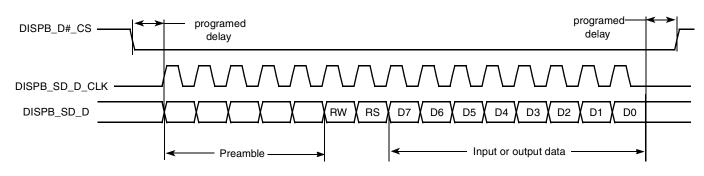

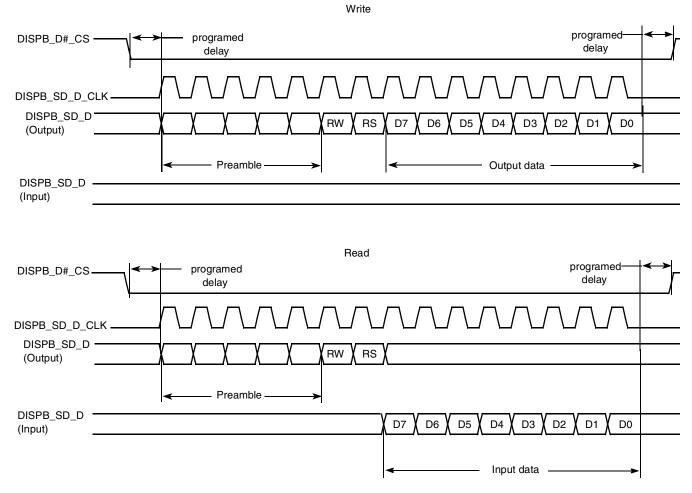

Figure 64. 3-Wire Serial Interface Timing Diagram

Figure 65 depicts timing diagram of the 4-wire serial interface. For this interface, there are separate input and output data lines both inside and outside the chip.

Figure 65. 4-Wire Serial Interface Timing Diagram

| ID   | Parameter                                      | Min  | Max  | Unit |  |  |  |  |

|------|------------------------------------------------|------|------|------|--|--|--|--|

|      | Internal Clock Operation                       |      |      |      |  |  |  |  |

| SS1  | (Tx/Rx) CK clock period                        | 81.4 | _    | ns   |  |  |  |  |

| SS2  | (Tx/Rx) CK clock high period                   | 36.0 | _    | ns   |  |  |  |  |

| SS3  | (Tx/Rx) CK clock rise time                     | —    | 6.0  | ns   |  |  |  |  |

| SS4  | (Tx/Rx) CK clock low period                    | 36.0 | _    | ns   |  |  |  |  |

| SS5  | (Tx/Rx) CK clock fall time                     | —    | 6.0  | ns   |  |  |  |  |

| SS6  | (Tx) CK high to FS (bl) high                   | —    | 15.0 | ns   |  |  |  |  |

| SS8  | (Tx) CK high to FS (bl) low                    | —    | 15.0 | ns   |  |  |  |  |

| SS10 | (Tx) CK high to FS (wl) high                   | —    | 15.0 | ns   |  |  |  |  |

| SS12 | (Tx) CK high to FS (wl) low                    | —    | 15.0 | ns   |  |  |  |  |

| SS14 | (Tx/Rx) Internal FS rise time                  | —    | 6.0  | ns   |  |  |  |  |

| SS15 | (Tx/Rx) Internal FS fall time                  | —    | 6.0  | ns   |  |  |  |  |

| SS16 | (Tx) CK high to STXD valid from high impedance | —    | 15.0 | ns   |  |  |  |  |

| SS17 | (Tx) CK high to STXD high/low                  | —    | 15.0 | ns   |  |  |  |  |

| SS18 | (Tx) CK high to STXD high impedance            | —    | 15.0 | ns   |  |  |  |  |

| SS19 | STXD rise/fall time                            | —    | 6.0  | ns   |  |  |  |  |

|      | Synchronous Internal Clock Operat              | tion |      |      |  |  |  |  |

| SS42 | SRXD setup before (Tx) CK falling              | 30   | _    | ns   |  |  |  |  |

| SS43 | SRXD hold after (Tx) CK falling                | 0.0  |      | ns   |  |  |  |  |

| SS52 | Loading                                        | —    | 25.0 | pF   |  |  |  |  |

### Table 102. SSI Transmitter Timing with Internal Clock

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

| ID                           | Parameter                      | Min   | Мах | Unit |  |  |  |  |

|------------------------------|--------------------------------|-------|-----|------|--|--|--|--|

| Oversampling Clock Operation |                                |       |     |      |  |  |  |  |

| SS47                         | Oversampling clock period      | 15.04 | —   | ns   |  |  |  |  |

| SS48                         | Oversampling clock high period | 6.0   | _   | ns   |  |  |  |  |

| SS49                         | Oversampling clock rise time   | —     | 3.0 | ns   |  |  |  |  |

| SS50                         | Oversampling clock low period  | 6.0   | _   | ns   |  |  |  |  |

| SS51                         | Oversampling clock fall time   | —     | 3.0 | ns   |  |  |  |  |

### Table 103. SSI Receiver Timing with Internal Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

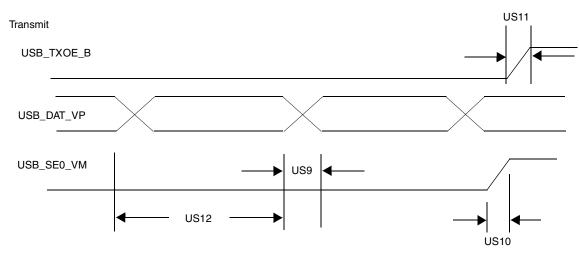

| ID  | Parameter         | Signal Name | Direction | Min  | Мах  | Unit | Conditions/<br>Reference Signal |

|-----|-------------------|-------------|-----------|------|------|------|---------------------------------|

| US1 | TX Rise/Fall Time | USB_DAT_VP  | Out       | _    | 5.0  | ns   | 50 pF                           |

| US2 | TX Rise/Fall Time | USB_SE0_VM  | Out       | _    | 5.0  | ns   | 50 pF                           |

| US3 | TX Rise/Fall Time | USB_TXOE_B  | Out       | _    | 5.0  | ns   | 50 pF                           |

| US4 | TX Duty Cycle     | USB_DAT_VP  | Out       | 49.0 | 51.0 | %    | —                               |

| US7 | RX Rise/Fall Time | USB_DAT_VP  | In        | _    | 3.0  | ns   | 35 pF                           |

| US8 | RX Rise/Fall Time | USB_SE0_VM  | In        | _    | 3.0  | ns   | 35 pF                           |

### Table 114. Definitions of USB Receive Waveform in DAT\_SE0 Bi-Directional Mode

### 4.7.17.1.2 USB DAT\_SE0 Unidirectional Mode

Table 115 shows the signal definitions in DAT\_SE0 unidirectional mode

### Table 115. Signal Definitions—DAT\_SE0 Unidirectional Mode

| Name       | Direction | Signal Description                           |

|------------|-----------|----------------------------------------------|

| USB_TXOE_B | Out       | Transmit enable, active low                  |

| USB_DAT_VP | Out       | TX data when USB_TXOE_B is low               |

| USB_SE0_VM | Out       | SE0 drive when USB_TXOE_B is low             |

| USB_VP1    | In        | Buffered data on DP when USB_TXOE_B is high  |

| USB_VM1    | In        | Buffered data on DM when USB_TXOE_B is high  |

| USB_RCV    | In        | Differential RX data when USB_TXOE_B is high |

Figure 102 and Figure 103 shows the USB transmit/receive waveform in DAT\_SE0 uni-directional mode respectively.

Figure 102. USB Transmit Waveform in DAT\_SE0 Uni-directional Mode

Package Information and Contact Assignments

| Parameter          | Conditions | Min | Тур | Мах | Unit |

|--------------------|------------|-----|-----|-----|------|

| Jitter (peak-peak) | <1.2 MHz   | 0   | —   | 50  | ps   |

| Jitter (peak-peak) | >1.2 MHz   | 0   | —   | 100 | ps   |

| Duty-cycle         | _          | 40  | _   | 60  | %    |

### Table 125. USB PHY System Clocking Parameters (continued)

### 4.7.19.4 USB PHY Voltage Thresholds

Table 126 lists the USB PHY voltage thresholds.

### Table 126. VBUS Comparators Thresholds

| Parameter                                    | Conditions | Min | Тур  | Мах  | Unit |

|----------------------------------------------|------------|-----|------|------|------|

| A-Device Session Valid                       | _          | 0.8 | 1.4  | 2.0  | V    |

| B-Device Session Valid                       | _          | 0.8 | 1.4  | 4.0  | V    |

| B-Device Session End                         | _          | 0.2 | 0.45 | 0.8  | V    |

| VBUS Valid Comparator Threshold <sup>1</sup> | _          | 4.4 | 4.6  | 4.75 | V    |

<sup>1</sup> For VBUS maximum rating, see Table 11 on page 17

## 5 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

### 5.1 19 x 19 mm Package Information

This section contains the outline drawing, signal assignment map, ground/power/reference ID (by ball grid location) for the  $19 \times 19$  mm, 0.8 mm pitch package.

### Package Information and Contact Assignments

| Contact Name             | Contact<br>Assignment | Power Rail | I/O Buffer Type | Direction after<br>Reset <sup>1</sup> | Configuraton<br>after Reset <sup>1</sup> |

|--------------------------|-----------------------|------------|-----------------|---------------------------------------|------------------------------------------|

| DI1_D0_CS                | U21                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_D1_CS                | AB23                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_DISP_CLK             | J18                   | NVCC_IPU6  | GPIO            | Output                                | Low                                      |

| DI1_PIN11                | Y22                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN12                | AA22                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |