Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | SPI                                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.2V ~ 5.5V                                                          |

| Data Converters            | A/D 6x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 28-SO                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72c215g2m6 |

# **Table of Contents**

|    | 9.4  | LOW POWER MODES                    | 34 |

|----|------|------------------------------------|----|

|    | 9.5  | INTERRUPTS                         | 34 |

|    | 9.6  | REGISTER DESCRIPTION               | 34 |

| 10 | MISC | ELLANEOUS REGISTERS                | 36 |

|    | 10.1 | I/O PORT INTERRUPT SENSITIVITY     | 36 |

|    | 10.2 | I/O PORT ALTERNATE FUNCTIONS       | 36 |

|    |      | MISCELLANEOUS REGISTER DESCRIPTION |    |

| 11 |      | HIP PERIPHERALS                    |    |

| •  |      | WATCHDOG TIMER (WDG)               |    |

|    |      | 1.1.1 Introduction                 |    |

|    | _    | 1.1.2 Main Features                |    |

|    | 1    | 1.1.3 Functional Description       |    |

|    | 1    | 1.1.4 Hardware Watchdog Option     | 40 |

|    | -    | 1.1.5 Low Power Modes              |    |

|    |      | 1.1.6 Interrupts                   |    |

|    |      | 1.1.7 Register Description         |    |

|    |      | 16-BIT TIMER                       |    |

|    | _    | 1.2.1 Introduction                 |    |

|    | _    | 1.2.3 Functional Description       |    |

|    | -    | 1.2.4 Low Power Modes              |    |

|    | 1    | 1.2.5 Interrupts                   |    |

|    | 1    | 1.2.6 Summary of Timer modes       | 54 |

|    |      | 1.2.7 Register Description         |    |

|    | 11.3 | SERIAL PERIPHERAL INTERFACE (SPI)  |    |

|    | _    | 1.3.1 Introduction                 |    |

|    |      | 1.3.2 Main Features                |    |

|    |      | 1.3.3 General description          |    |

|    |      | 1.3.5 Low Power Modes              |    |

|    |      | 1.3.6 Interrupts                   |    |

|    |      | 1.3.7 Register Description         |    |

|    | 11.4 | I2C BUS INTERFACE (I2C)            | 73 |

|    | 1    | 1.4.1 Introduction                 | 73 |

|    |      | 1.4.2 Main Features                |    |

|    |      | 1.4.3 General Description          |    |

|    |      | 1.4.4 Functional Description       |    |

|    |      | 1.4.5 Low Power Modes              |    |

|    |      | 1.4.7 Register Description         |    |

|    |      | 8-BIT A/D CONVERTER (ADC)          |    |

|    |      | 1.5.1 Introduction                 |    |

|    |      | 1.5.2 Main Features                |    |

|    |      | 1.5.3 Functional Description       |    |

|    |      | 1.5.4 Low Power Modes              |    |

|    |      | 1.5.5 Interrupts                   |    |

|    | 1    | 1.5.6 Register Description         | 88 |

# **Table of Contents**

| 12 INSTRUCTION SET                                          | . 90 |

|-------------------------------------------------------------|------|

| 12.1 ST7 ADDRESSING MODES                                   | 90   |

| 12.1.1 Inherent                                             |      |

| 12.1.2 Immediate                                            |      |

| 12.1.3 Direct                                               |      |

| 12.1.4 Indexed (No Offset, Short, Long)                     |      |

| 12.1.6 Indirect Indexed (Short, Long)                       |      |

| 12.1.7 Relative Mode (Direct, Indirect)                     |      |

| 12.2 INSTRUCTION GROUPS                                     |      |

| 13 ELECTRICAL CHARACTERISTICS                               | . 96 |

| 13.1 PARAMETER CONDITIONS                                   | . 96 |

| 13.1.1 Minimum and Maximum values                           | . 96 |

| 13.1.2 Typical values                                       | . 96 |

| 13.1.3 Typical curves                                       |      |

| 13.1.4 Loading capacitor                                    |      |

| 13.1.5 Pin input voltage                                    |      |

| 13.2.1 Voltage Characteristics                              |      |

| 13.2.2 Current Characteristics                              |      |

| 13.2.3 Thermal Characteristics                              |      |

| 13.3 OPERATING CONDITIONS                                   |      |

| 13.3.1 General Operating Conditions                         | . 98 |

| 13.3.2 Operating Conditions with Low Voltage Detector (LVD) |      |

| 13.4 SUPPLY CURRENT CHARACTERISTICS                         |      |

| 13.4.1 RUN and SLOW Modes                                   | 102  |

| 13.4.2 WAIT and SLOW WAIT Modes                             |      |

| 13.4.3 HALT Mode                                            |      |

| 13.4.4 Supply and Clock Managers                            |      |

| 13.4.5 On-Chip Peripherals                                  |      |

|                                                             |      |

| 13.5.1 General Timings                                      |      |

| 13.5.3 Crystal and Ceramic Resonator Oscillators            |      |

| 13.5.4 RC Oscillators                                       |      |

| 13.5.5 Clock Security System (CSS)                          |      |

| 13.6 MEMORY CHARACTERISTICS                                 | 112  |

| 13.6.1 RAM and Hardware Registers                           | 112  |

| 13.6.2 FLASH Program Memory                                 |      |

| 13.7 EMC CHARACTERISTICS                                    |      |

| 13.7.1 Functional EMS                                       |      |

| 13.7.2 Absolute Electrical Sensitivity                      |      |

| 13.7.3 ESD Pin Protection Strategy                          |      |

| 13.8 I/O PORT PIN CHARACTERISTICS                           |      |

| 13.8.1 General Characteristics                              |      |

| 13.9 CONTROL PIN CHARACTERISTICS                            |      |

# **2 PIN DESCRIPTION**

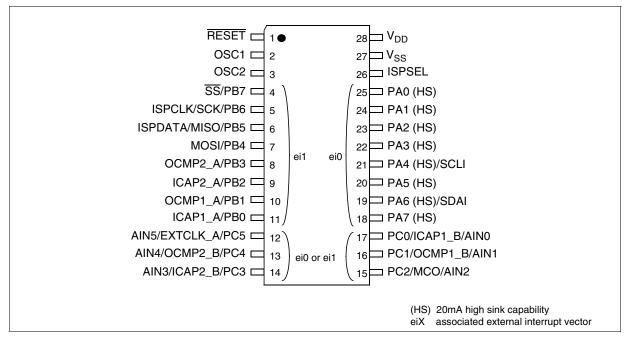

Figure 2. 28-Pin SO Package Pinout

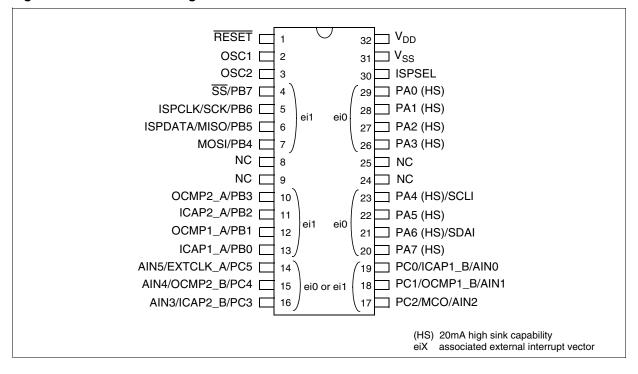

Figure 3. 32-Pin SDIP Package Pinout

## 4 FLASH PROGRAM MEMORY

#### 4.1 INTRODUCTION

FLASH devices have a single voltage non-volatile FLASH memory that may be programmed in-situ (or plugged in a programming tool) on a byte-by-byte basis.

# **4.2 MAIN FEATURES**

- Remote In-Situ Programming (ISP) mode

- Up to 16 bytes programmed in the same cycle

- MTP memory (Multiple Time Programmable)

- Read-out memory protection against piracy

#### 4.3 STRUCTURAL ORGANISATION

The FLASH program memory is organised in a single 8-bit wide memory block which can be used for storing both code and data constants.

The FLASH program memory is mapped in the upper part of the ST7 addressing space and includes the reset and interrupt user vector area.

## 4.4 IN-SITU PROGRAMMING (ISP) MODE

The FLASH program memory can be programmed using Remote ISP mode. This ISP mode allows the contents of the ST7 program memory to be updated using a standard ST7 programming tools after the device is mounted on the application board. This feature can be implemented with a minimum number of added components and board area impact.

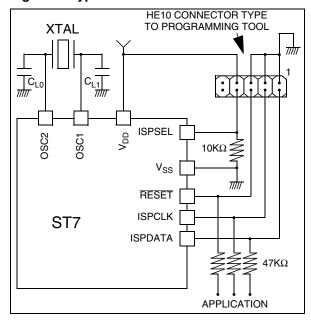

An example Remote ISP hardware interface to the standard ST7 programming tool is described below. For more details on ISP programming, refer to the ST7 Programming Specification.

## **Remote ISP Overview**

The Remote ISP mode is initiated by a specific sequence on the dedicated ISPSEL pin.

The Remote ISP is performed in three steps:

- Selection of the RAM execution mode

- Download of Remote ISP code in RAM

- Execution of Remote ISP code in RAM to program the user program into the FLASH

#### Remote ISP hardware configuration

In Remote ISP mode, the ST7 has to be supplied with power ( $V_{DD}$  and  $V_{SS}$ ) and a clock signal (oscillator and application crystal circuit for example).

This mode needs five signals (plus the V<sub>DD</sub> signal if necessary) to be connected to the programming tool. This signals are:

- RESET: device reset

- V<sub>SS</sub>: device ground power supply

- ISPCLK: ISP output serial clock pin

- ISPDATA: ISP input serial data pin

- ISPSEL: Remote ISP mode selection. This pin must be connected to  $V_{\rm SS}$  on the application board through a pull-down resistor.

If any of these pins are used for other purposes on the application, a serial resistor has to be implemented to avoid a conflict if the other device forces the signal level.

Figure 5 shows a typical hardware interface to a standard ST7 programming tool. For more details on the pin locations, refer to the device pinout description.

Figure 5. Typical Remote ISP Interface

## 4.5 MEMORY READ-OUT PROTECTION

The read-out protection is enabled through an option bit.

For FLASH devices, when this option is selected, the program and data stored in the FLASH memory are protected against read-out piracy (including a re-write protection). When this protection option is removed the entire FLASH program memory is first automatically erased. However, the E<sup>2</sup>PROM data memory (when available) can be protected only with ROM devices.

# **5 CENTRAL PROCESSING UNIT**

#### 5.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

## **5.2 MAIN FEATURES**

- 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes

- Two 8-bit index registers

- 16-bit stack pointer

- Low power modes

- Maskable hardware interrupts

- Non-maskable software interrupt

#### **5.3 CPU REGISTERS**

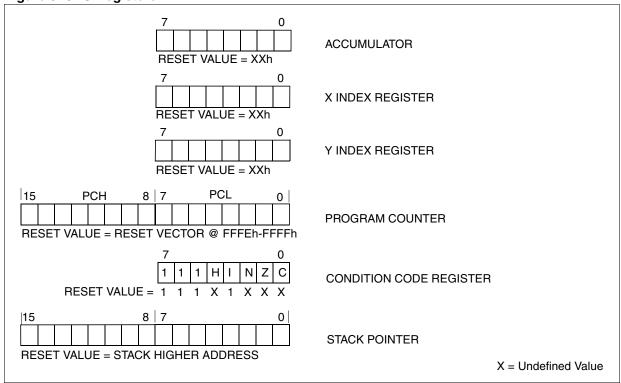

The six CPU registers shown in Figure 1 are not present in the memory mapping and are accessed by specific instructions.

## Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

## Index Registers (X and Y)

In indexed addressing modes, these 8-bit registers are used to create either effective addresses or temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures (not pushed to and popped from the stack).

## **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

Figure 6. CPU Registers

# 7 INTERRUPTS

The ST7 core may be interrupted by one of two different methods: maskable hardware interrupts as listed in the Interrupt Mapping Table and a non-maskable software interrupt (TRAP). The Interrupt processing flowchart is shown in Figure 1.

The maskable interrupts must be enabled by clearing the I bit in order to be serviced. However, disabled interrupts may be latched and processed when they are enabled (see external interrupts subsection).

Note: After reset, all interrupts are disabled.

When an interrupt has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- The I bit of the CC register is set to prevent additional interrupts.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to the Interrupt Mapping Table for vector addresses).

The interrupt service routine should finish with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note:** As a consequence of the IRET instruction, the I bit will be cleared and the main program will resume.

## **Priority Management**

By default, a servicing interrupt cannot be interrupted because the I bit is set by hardware entering in interrupt routine.

In the case when several interrupts are simultaneously pending, an hardware priority defines which one will be serviced first (see the Interrupt Mapping Table).

## **Interrupts and Low Power Mode**

All interrupts allow the processor to leave the WAIT low power mode. Only external and specifically mentioned interrupts allow the processor to leave the HALT low power mode (refer to the "Exit from HALT" column in the Interrupt Mapping Table).

## 7.1 NON-MASKABLE SOFTWARE INTERRUPT

This interrupt is entered when the TRAP instruction is executed regardless of the state of the I bit.

It will be serviced according to the flowchart on Figure 1.

#### 7.2 EXTERNAL INTERRUPTS

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts allow the processor to leave the Halt low power mode.

The external interrupt polarity is selected through the miscellaneous register or interrupt register (if available).

An external interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins, connected to the same interrupt vector, are configured as interrupts, their signals are logically NANDed before entering the edge/level detection block.

Caution: The type of sensitivity defined in the Miscellaneous or Interrupt register (if available) applies to the ei source. In case of a NANDed source (as described on the I/O ports section), a low level on an I/O pin configured as input with interrupt, masks the interrupt request even in case of risingedge sensitivity.

#### 7.3 PERIPHERAL INTERRUPTS

Different peripheral interrupt flags in the status register are able to cause an interrupt when they are active if both:

- The I bit of the CC register is cleared.

- The corresponding enable bit is set in the control register.

If any of these two conditions is false, the interrupt is latched and thus remains pending.

Clearing an interrupt request is done by:

- Writing "0" to the corresponding bit in the status register or

- Access to the status register while the flag is set followed by a read or write of an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (that is, waiting to be enabled) will therefore be lost if the clear sequence is executed.

# I/O PORTS (Cont'd)

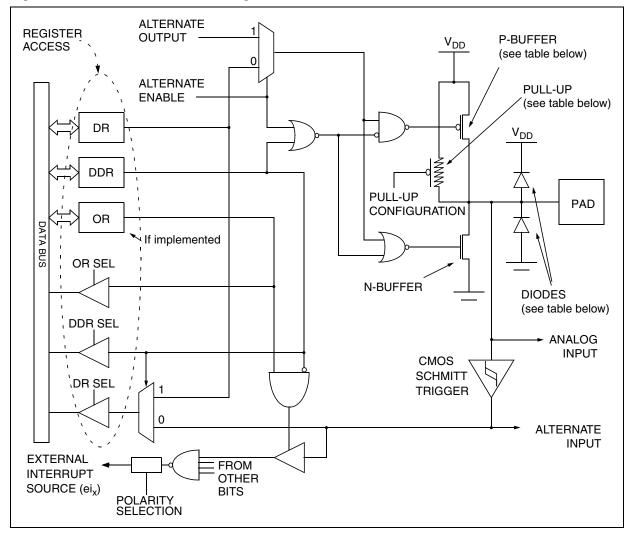

Figure 21. I/O Port General Block Diagram

Table 6. I/O Port Mode Options

|        | Configuration Mode              | Pull-Up | P-Buffer | Diodes             |                    |  |

|--------|---------------------------------|---------|----------|--------------------|--------------------|--|

|        | Configuration Mode              | Pull-op | P-Buller | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input  | Floating with/without Interrupt | Off     | Off      |                    |                    |  |

|        | Pull-up with/without Interrupt  | On      | Oii      | On                 |                    |  |

|        | Push-pull                       | Off     | On       | - On               | On                 |  |

| Output | Open Drain (logic level)        |         | Off      | 1                  |                    |  |

|        | True Open Drain                 | NI      | NI       | NI (see note)      |                    |  |

Legend: NI - not implemented

Off - implemented not activated On - implemented and activated

**Note**: The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

# I/O PORTS (Cont'd)

#### 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the I-bit in the CC register is reset (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |

#### 9.6 REGISTER DESCRIPTION

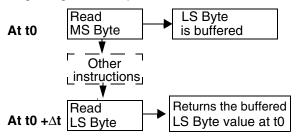

# **DATA REGISTER (DR)**

Port x Data Register PxDR with x = A, B or C.

Read/Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

## Bit 7:0 = D[7:0] Data register 8 bits.

The DR register has a specific behaviour according to the selected input/output configuration. Writing the DR register is always taken into account even if the pin is configured as an input; this allows always having the expected level on the pin when toggling to output mode. Reading the DR register returns either the DR register latch content (pin configured as output) or the digital value applied to the I/O pin (pin configured as input).

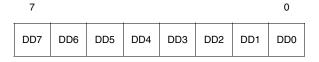

# **DATA DIRECTION REGISTER (DDR)**

Port x Data Direction Register PxDDR with x = A, B or C.

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:0 = **DD[7:0]** Data direction register 8 bits.

The DDR register gives the input/output direction configuration of the pins. Each bit is set and cleared by software.

0: Input mode

1: Output mode

## **OPTION REGISTER (OR)**

Port x Option Register PxOR with x = A, B or C.

Read/Write

Reset Value: 0000 0000 (00h)

## Bit 7:0 = O[7:0] Option register 8 bits.

For specific I/O pins, this register is not implemented. In this case the DDR register is enough to select the I/O pin configuration.

The OR register allows to distinguish: in input mode if the pull-up with interrupt capability or the basic pull-up configuration is selected, in output mode if the push-pull or open drain configuration is selected.

Each bit is set and cleared by software.

Input mode:

0: Floating input

1: Pull-up input with or without interrupt

Output mode:

0: Output open drain (with P-Buffer deactivated)

1: Output push-pull (when available)

## 16-BIT TIMER (Cont'd)

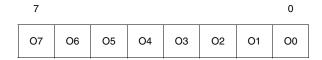

**16-bit Read Sequence:** (from either the Counter Register or the Alternate Counter Register).

Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, One Pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set.

- 2. An access (read or write) to the CLR register.

**Note:** The TOF bit is not cleared by accessing the ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

## 11.2.3.2 External Clock

The external clock (where available) is selected if CC0 = 1 and CC1 = 1 in the CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronized with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

# **16-BIT TIMER** (Cont'd)

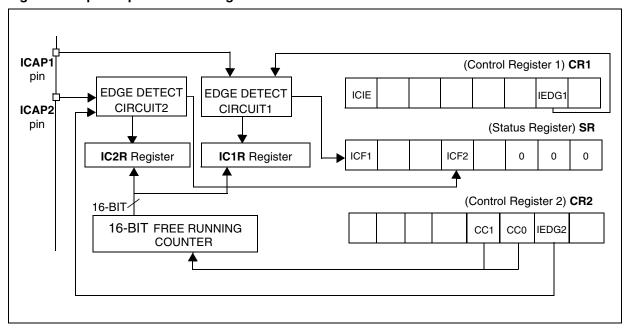

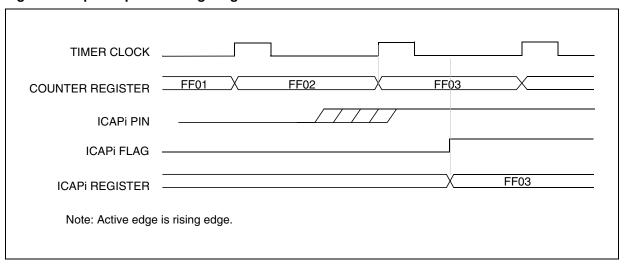

Figure 30. Input Capture Block Diagram

Figure 31. Input Capture Timing Diagram

# 16-BIT TIMER (Cont'd)

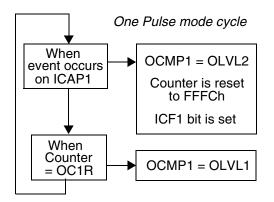

## 11.2.3.5 One Pulse Mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The One Pulse mode uses the Input Capture1 function and the Output Compare1 function.

## **Procedure:**

To use One Pulse mode:

- Load the OC1R register with the value corresponding to the length of the pulse (see the formula in the opposite column).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see Table 1).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and the OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (i.e. clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICFi bit is set.

- 2. An access (read or write) to the IC/LR register.

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OC_iR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits, see Table 1)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{FXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin (see Figure 10).

#### Notes:

- The OCF1 bit cannot be set by hardware in One Pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

- 3. If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4. The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5. When One Pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate that a period of time has elapsed but cannot generate an output waveform because the OLVL2 level is dedicated to One Pulse mode.

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

## **Master Transmitter**

Following the address transmission and after SR1 register has been read, the master sends bytes from the DR register to the SDA line via the internal shift register.

The master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 3 Transfer sequencing EV8).

When the acknowledge bit is received, the interface sets:

EVF and BTF bits with an interrupt if the ITE bit is set.

To close the communication: after writing the last byte to the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

## **Error Cases**

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and BERR bits are set by hardware with an interrupt if ITE is set.

Note that BERR will not be set if an error is detected during the first pulse of each 9-bit transaction:

Single Master Mode

If a Start or Stop is issued during the first pulse of a 9-bit transaction, the BERR flag will not be set and transfer will continue however the BUSY flag will be reset. To work around this, slave devices should issue a NACK when they receive a misplaced Start or Stop. The reception of a NACK or BUSY by the master in the middle of communication gives the possibility to reinitiate transmission.

Multimaster Mode

Normally the BERR bit would be set whenever unauthorized transmission takes place while transfer is already in progress. However, an issue will arise if an external master generates an unauthorized Start or Stop while the I<sup>2</sup>C master is on the first pulse pulse of a 9-bit transaction. It is possible to work around this by polling the BUSY bit during I<sup>2</sup>C master mode transmission. The resetting of the BUSY bit can then be handled in a similar manner as the BERR flag being set.

AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set by hardware with an interrupt if the ITE bit is set. To resume, set the Start or Stop bit.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

ARLO: Detection of an arbitration lost condition.

In this case the ARLO bit is set by hardware (with an interrupt if the ITE bit is set and the interface goes automatically back to slave mode (the M/SL bit is cleared).

**Note**: In all these cases, the SCL line is not held low; however,the SDA line can remain low if the last bits transmitted are all 0. It is then necessary to release both lines by software. The SCL line is not held low while AF=1 but by other flags (SB or BTF) that are set at the same time.

# I2C BUS INTERFACE (Cont'd)

Table 17. I<sup>2</sup>C Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label      | 7          | 6          | 5         | 4         | 3          | 2         | 1         | 0         |

|-------------------|------------------------|------------|------------|-----------|-----------|------------|-----------|-----------|-----------|

| 0028h             | I2CCR<br>Reset Value   | 0          | 0          | PE<br>0   | ENGC<br>0 | START<br>0 | ACK<br>0  | STOP<br>0 | ITE<br>0  |

| 0029h             | I2CSR1<br>Reset Value  | EVF<br>0   | ADD10<br>0 | TRA<br>0  | BUSY<br>0 | BTF<br>0   | ADSL<br>0 | M/SL<br>0 | SB<br>0   |

| 002Ah             | I2CSR2<br>Reset Value  | 0          | 0          | 0         | AF<br>0   | STOPF<br>0 | ARLO<br>0 | BERR<br>0 | GCAL<br>0 |

| 02Bh              | I2CCCR<br>Reset Value  | FM/SM<br>0 | CC6<br>0   | CC5<br>0  | CC4<br>0  | CC3<br>0   | CC2<br>0  | CC1<br>0  | CC0<br>0  |

| 02Ch              | I2COAR1<br>Reset Value | ADD7<br>0  | ADD6<br>0  | ADD5<br>0 | ADD4<br>0 | ADD3<br>0  | ADD2<br>0 | ADD1<br>0 | ADD0<br>0 |

| 002Dh             | I2COAR2<br>Reset Value | FR1<br>0   | FR0<br>1   | 0         | 0         | 0          | ADD9<br>0 | ADD8<br>0 | 0         |

| 002Eh             | I2CDR<br>Reset Value   | MSB<br>0   | 0          | 0         | 0         | 0          | 0         | 0         | LSB<br>0  |

# INSTRUCTION GROUPS (Cont'd)

| Mnemo | Description                | Function/Example    | Dst    | Src |

|-------|----------------------------|---------------------|--------|-----|

| ADC   | Add with Carry             | A = A + M + C       | Α      | М   |

| ADD   | Addition                   | A = A + M           | Α      | М   |

| AND   | Logical And                | A = A . M           | Α      | М   |

| ВСР   | Bit compare A, Memory      | tst (A . M)         | Α      | М   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |

| CALL  | Call subroutine            |                     |        |     |

| CALLR | Call subroutine relative   |                     |        |     |

| CLR   | Clear                      |                     | reg, M |     |

| СР    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |

| DEC   | Decrement                  | dec Y               | reg, M |     |

| HALT  | Halt                       |                     |        |     |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     |

| INC   | Increment                  | inc X               | reg, M |     |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |

| JRA   | Jump relative always       |                     |        |     |

| JRT   | Jump relative              |                     |        |     |

| JRF   | Never jump                 | jrf *               |        |     |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |

| JRNC  | Jump if C = 0              | C = 0 ?             |        |     |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |

| JRUGE | Jump if C = 0              | Jmp if unsigned >=  |        |     |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |

|   |   |   | - | _ |

|---|---|---|---|---|

| Н | I | N | Z | С |

| Н |   | N | Z | С |

| Н |   | N | Z | С |

|   |   | N | Z |   |

|   |   | N | Z |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   | С |

|   |   |   |   | С |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   | 0 | 1 |   |

|   |   | N | Z | С |

|   |   | N | Z | 1 |

|   |   | N | Z |   |

|   | 0 |   |   |   |

| Н | I | N | Z | С |

|   |   | N | Z |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

477

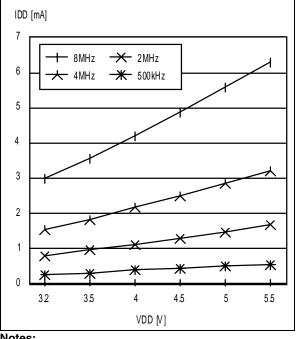

#### 13.4 SUPPLY CURRENT CHARACTERISTICS

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

| Symbol                            | Parameter                                | Conditions                                    | Max | Unit |

|-----------------------------------|------------------------------------------|-----------------------------------------------|-----|------|

| $\Delta I_{\text{DD}(\Delta Ta)}$ | Supply current variation vs. temperature | Constant V <sub>DD</sub> and f <sub>CPU</sub> | 10  | %    |

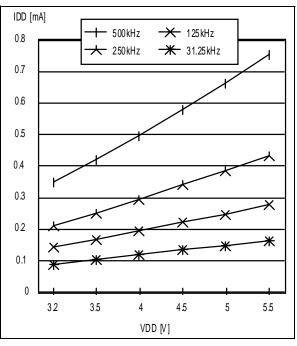

#### 13.4.1 RUN and SLOW Modes

| Symbol          | Parameter                                                 |                           | Conditions                                                                                                                                                  | Typ 1)              | Max <sup>2)</sup>   | Unit |

|-----------------|-----------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|

| I <sub>DD</sub> | Supply current in RUN mode <sup>3)</sup> (see Figure 59)  | V5.5≥ <sub>OC</sub>       | f <sub>OSC</sub> =1MHz, f <sub>CPU</sub> =500kHz<br>f <sub>OSC</sub> =4MHz, f <sub>CPU</sub> =2MHz<br>f <sub>OSC</sub> =16MHz, f <sub>CPU</sub> =8MHz       | 500<br>1500<br>5600 | 900<br>2500<br>9000 |      |

|                 | Supply current in SLOW mode <sup>4)</sup> (see Figure 60) | 4.5V≤V <sub>DD</sub> ≤5   | f <sub>OSC</sub> =1MHz, f <sub>CPU</sub> =31.25kHz<br>f <sub>OSC</sub> =4MHz, f <sub>CPU</sub> =125kHz<br>f <sub>OSC</sub> =16MHz, f <sub>CPU</sub> =500kHz | 150<br>250<br>670   | 450<br>550<br>1250  | иΑ   |

|                 | Supply current in RUN mode <sup>3)</sup> (see Figure 59)  | .2V≤V <sub>DD</sub> ≤3.6V | f <sub>OSC</sub> =1MHz, f <sub>CPU</sub> =500kHz<br>f <sub>OSC</sub> =4MHz, f <sub>CPU</sub> =2MHz<br>f <sub>OSC</sub> =16MHz, f <sub>CPU</sub> =8MHz       | 300<br>970<br>3600  | 550<br>1350<br>4500 | μΑ   |

|                 | Supply current in SLOW mode <sup>4)</sup> (see Figure 60) | 3.2V≤V <sub>[</sub>       | f <sub>OSC</sub> =1MHz, f <sub>CPU</sub> =31.25kHz<br>f <sub>OSC</sub> =4MHz, f <sub>CPU</sub> =125kHz<br>f <sub>OSC</sub> =16MHz, f <sub>CPU</sub> =500kHz | 100<br>170<br>420   | 250<br>300<br>700   |      |

Figure 59. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

Figure 60. Typical I<sub>DD</sub> in SLOW vs. f<sub>CPU</sub>

## Notes:

- 1. Typical data are based on TA=25°C, V<sub>DD</sub>=5V (4.5V≤V<sub>DD</sub>≤5.5V range) and VDD=3.4V (3.2V≤V<sub>DD</sub>≤3.6V range).

- 2. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- 3. CPU running with memory access, all I/O pins in input mode with a static value at VDD or VSS (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, CSS and LVD disabled.

- 4. SLOW mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, CSS and LVD disabled.

## 13.5 CLOCK AND TIMING CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub>.

# 13.5.1 General Timings

| Symbol               | Parameter                                                                   | Conditions             | Min  | Typ <sup>1)</sup> | Max  | Unit             |

|----------------------|-----------------------------------------------------------------------------|------------------------|------|-------------------|------|------------------|

| t <sub>c(INST)</sub> | Instruction cycle time                                                      |                        | 2    | 3                 | 12   | t <sub>CPU</sub> |

|                      |                                                                             | f <sub>CPU</sub> =8MHz | 250  | 375               | 1500 | ns               |

| t <sub>v(IT)</sub>   | Interrupt reaction time <sup>2)</sup> $t_{V(IT)} = \Delta t_{C(INST)} + 10$ |                        | 10   |                   | 22   | t <sub>CPU</sub> |

|                      |                                                                             | f <sub>CPU</sub> =8MHz | 1.25 |                   | 2.75 | μs               |

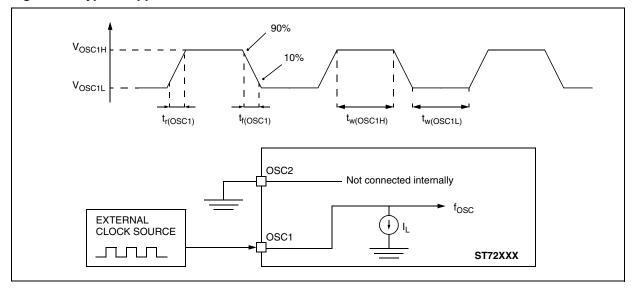

## 13.5.2 External Clock Source

| Symbol                           | Parameter                         | Conditions                       | Min                 | Тур | Max                 | Unit |

|----------------------------------|-----------------------------------|----------------------------------|---------------------|-----|---------------------|------|

| V <sub>OSC1H</sub>               | OSC1 input pin high level voltage |                                  | 0.7xV <sub>DD</sub> |     | $V_{DD}$            | V    |

| V <sub>OSC1L</sub>               | OSC1 input pin low level voltage  | -                                | $V_{SS}$            |     | 0.3xV <sub>DD</sub> | V    |

| $t_{w(OSC1H)}$<br>$t_{w(OSC1L)}$ | OSC1 high or low time 3)          | see Figure 63                    | 15                  |     |                     | ns   |

| $t_{r(OSC1)} \ t_{f(OSC1)}$      | OSC1 rise or fall time 3)         |                                  |                     |     | 15                  | 113  |

| ΙL                               | OSCx Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                     |     | ±1                  | μΑ   |

Figure 63. Typical Application with an External Clock Source

#### Notes:

- 1. Data based on typical application software.

- 2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

- 3. Data based on design simulation and/or technology characteristics, not tested in production.

# **CLOCK CHARACTERISTICS** (Cont'd)

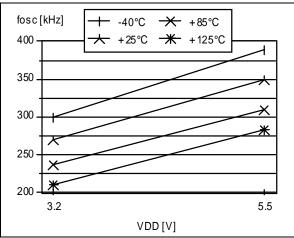

# 13.5.5 Clock Security System (CSS)

| Symbol             | Parameter                    | Conditions                                  | Min | Тур | Max | Unit  |

|--------------------|------------------------------|---------------------------------------------|-----|-----|-----|-------|

| f <sub>SFOSC</sub> | Safe Oscillator Frequency 1) | T <sub>A</sub> =25°C, V <sub>DD</sub> =5.0V | 250 | 340 | 550 | - kHz |

|                    |                              | T <sub>A</sub> =25°C, V <sub>DD</sub> =3.4V | 190 | 260 | 450 |       |

| f <sub>GFOSC</sub> | Glitch Filtered Frequency 2) |                                             |     | 30  |     | MHz   |

Figure 69. Typical Safe Oscillator Frequencies

## Note:

- 1. Data based on characterization results, tested in production between 90KHz and 600KHz.

- 2. Filtered glitch on the  $f_{\mbox{OSC}}$  signal. See functional description in Section 6.5 on page 23 for more details.

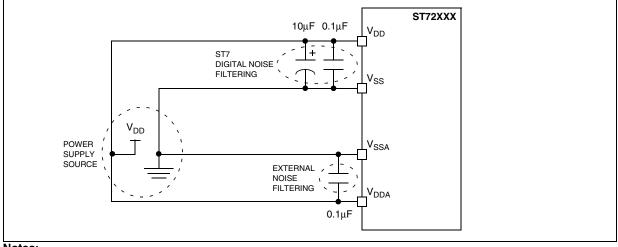

#### 13.7 EMC CHARACTERISTICS

Susceptibility tests are performed on a sample basis during product characterization.

#### 13.7.1 Functional EMS

(Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

| Symbol            | Parameter                                                                                                                                      | Conditions                                                                                     | Neg 1) | Pos 1) | Unit |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|--------|------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                 | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | -1     | 1      |      |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on V <sub>DD</sub> and V <sub>DD</sub> pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | -4     | 4      | kV   |

Figure 70. EMC Recommended star network power supply connection <sup>2)</sup>

#### Notes:

- 1. Data based on characterization results, not tested in production.

- 2. The suggested 10µF and 0.1µF decoupling capacitors on the power supply lines are proposed as a good price vs. EMC performance tradeoff. They have to be put as close as possible to the device power supply pins. Other EMC recommendations are given in other sections (I/Os, RESET, OSCx pin characteristics).

57

# **COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)**

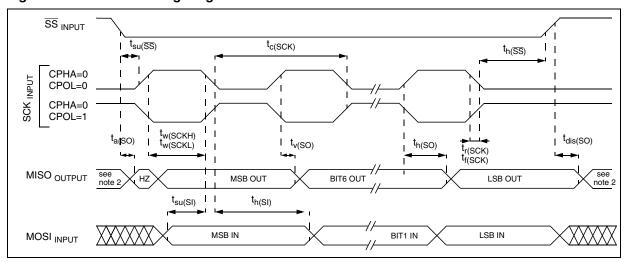

Figure 92. SPI Slave Timing Diagram with CPHA=11)

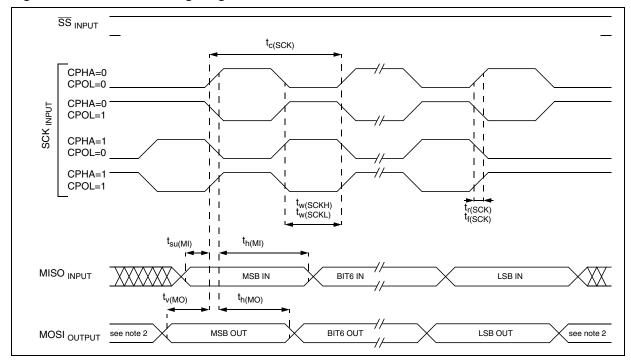

Figure 93. SPI Master Timing Diagram 1)

#### Notes:

- 1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

57

#### 14.3 SOLDERING INFORMATION

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.