#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.2V ~ 5.5V                                                          |

| Data Converters            | A/D 6x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                            |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72c254g1b6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

\_

57

| 13.9.1 Asynchronous RESET Pin                                  | 121 |

|----------------------------------------------------------------|-----|

| 13.9.2 ISPSEL Pin                                              |     |

| 13.10 TIMER PERIPHERAL CHARACTERISTICS                         | 124 |

| 13.10.1 Watchdog Timer                                         | 124 |

| 13.10.2 16-Bit Timer                                           |     |

| 13.11 COMMUNICATION INTERFACE CHARACTERISTICS                  | 125 |

| 13.11.1 SPI - Serial Peripheral Interface                      | 125 |

| 13.11.2 I2C - Inter IC Control Interface                       | 127 |

| 13.12 8-BIT ADC CHARACTERISTICS                                | 128 |

| 14 PACKAGE CHARACTERISTICS                                     | 130 |

| 14.1 PACKAGE MECHANICAL DATA                                   | 130 |

| 14.2 THERMAL CHARACTERISTICS                                   | 131 |

| 14.3 SOLDERING INFORMATION                                     | 132 |

| 15 DEVICE CONFIGURATION AND ORDERING INFORMATION               | 133 |

| 15.1 OPTION BYTES                                              | 133 |

| 15.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 134 |

| 15.3 DEVELOPMENT TOOLS                                         | 136 |

| 15.3.1 PACKAGE/SOCKET FOOTPRINT PROPOSAL                       | 137 |

| 15.4 ST7 APPLICATION NOTES                                     | 138 |

| 16 SUMMARY OF CHANGES                                          | 140 |

|                                                                |     |

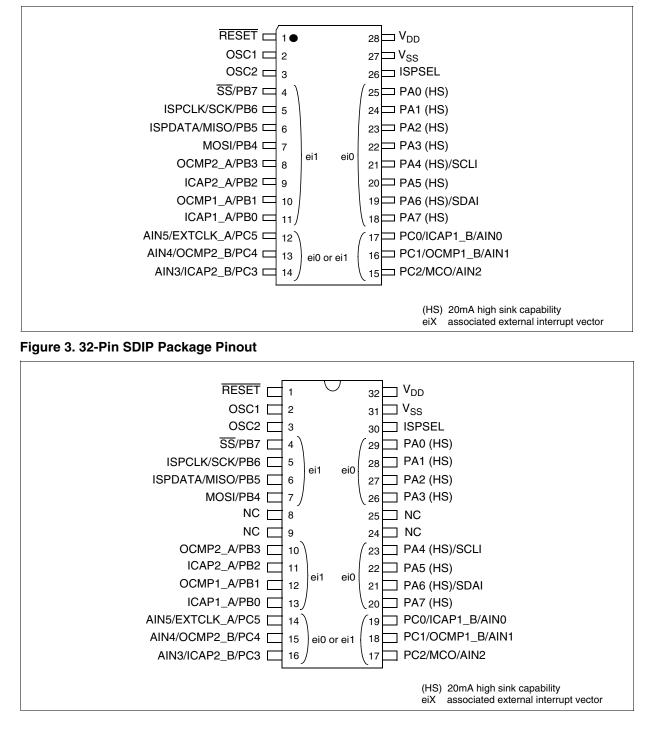

# **2 PIN DESCRIPTION**

5/

# Figure 2. 28-Pin SO Package Pinout

| Pin    | n°   |                  |      | Le    | evel           |       | Ро  | rt / C | Cont | rol |      | Main                                                                      |                                                   |  |  |

|--------|------|------------------|------|-------|----------------|-------|-----|--------|------|-----|------|---------------------------------------------------------------------------|---------------------------------------------------|--|--|

| 32     | 8    | Pin Name         | Type | μ     | ut             |       | Inp | out    |      | Out | tput | Main<br>Function                                                          | Alternate Function                                |  |  |

| SDIP32 | S028 |                  | ŕ    | Input | Output         | float | ndm | int    | ana  | OD  | РР   | (after reset)                                                             |                                                   |  |  |

| 18     | 16   | PC1/OCMP1_B/AIN1 | I/O  | C     | С <sub>т</sub> | x     | ei0 | /ei1   | Х    | х   | х    | Port C1                                                                   | Timer B Output Compare 1 or<br>ADC Analog Input 1 |  |  |

| 19     | 17   | PC0/ICAP1_B/AIN0 | I/O  | C     | С <sub>т</sub> | x     | ei0 | /ei1   | Х    | х   | х    | Port C0                                                                   | Timer B Input Capture 1 or<br>ADC Analog Input 0  |  |  |

| 20     | 18   | PA7              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | Х    | Port A7                                                                   |                                                   |  |  |

| 21     | 19   | PA6 /SDAI        | I/O  | $C_T$ | HS             | Х     |     | ei0    |      | Т   |      | Port A6                                                                   | I <sup>2</sup> C Data                             |  |  |

| 22     | 20   | PA5              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | Х    | Port A5                                                                   |                                                   |  |  |

| 23     | 21   | PA4 /SCLI        | I/O  | $C_T$ | HS             | Х     |     | ei0    |      | Т   |      | Port A4                                                                   | I <sup>2</sup> C Clock                            |  |  |

| 24     |      | NC               |      |       |                |       |     |        |      |     | Not  | Connected                                                                 |                                                   |  |  |

| 25     |      | NC               |      |       |                |       |     |        |      |     | INO  | Connecteu                                                                 |                                                   |  |  |

| 26     | 22   | PA3              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | Х    | Port A3                                                                   |                                                   |  |  |

| 27     | 23   | PA2              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | Х    | Port A2                                                                   |                                                   |  |  |

| 28     | 24   | PA1              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | х    | Port A1                                                                   |                                                   |  |  |

| 29     | 25   | PA0              | I/O  | $C_T$ | HS             | Х     | е   | i0     |      | Х   | х    | Port A0                                                                   |                                                   |  |  |

| 30     | 26   | ISPSEL           | I    | С     |                | х     |     |        |      |     |      | In situ programming selection (Should be tied low in standard user mode). |                                                   |  |  |

| 31     | 27   | V <sub>SS</sub>  | S    |       |                |       |     |        |      |     |      | Ground                                                                    |                                                   |  |  |

| 32     | 28   | V <sub>DD</sub>  | S    |       |                |       |     |        |      |     |      | Main power su                                                             | ipply                                             |  |  |

#### Notes:

<u>ل</u>حک

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to  $V_{DD}$  are not implemented). See Section 9 "I/O PORTS" on page 30 and Section 13.8 "I/O PORT PIN CHARACTERISTICS" on page 118 for more details.

3. OSC1 and OSC2 pins connect a crystal or ceramic resonator, an external RC, or an external source to the on-chip oscillator see Section 2 "PIN DESCRIPTION" on page 7 and Section 13.5 "CLOCK AND TIM-ING CHARACTERISTICS" on page 105 for more details.

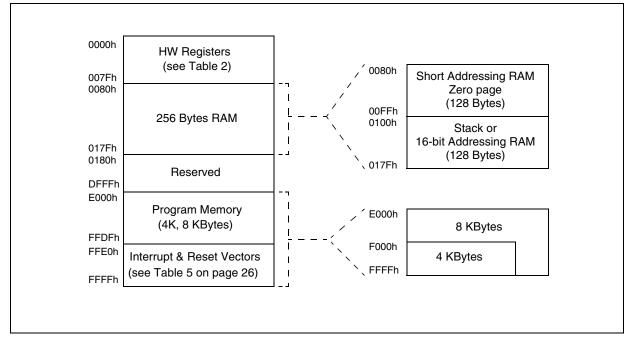

# **3 REGISTER & MEMORY MAP**

As shown in the Figure 4, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register location, 256 bytes of RAM and up to 8Kbytes of user program memory. The RAM space includes up to 128 bytes for the stack from 0100h to 017Fh.

The highest address bytes contain the user reset and interrupt vectors.

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

#### Figure 4. Memory Map

| Address                                                                                                                                      | Block   | Register<br>Label                                                                                                                                             | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reset<br>Status                                                                         | Remarks                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Ch<br>003Ch<br>003Ch<br>003Ch | TIMER A | TACR2<br>TACR1<br>TASR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACLR<br>TACLR<br>TAACLR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2HR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Status Register<br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register<br>Timer A Input Capture 2 Low Register<br>Timer A Output Compare 2 High Register<br>Timer A Output Compare 2 Low Register | 00h<br>00h<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>R/W<br>Read Only<br>Read Only |

| 0040h                                                                                                                                        |         | MISCR2                                                                                                                                                        | Miscellaneous Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00h                                                                                     | R/W                                                                                                                                                                                                                                                                                                 |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Ch          | TIMER B | TBCR2<br>TBCR1<br>TBSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCHR<br>TBCLR<br>TBACHR<br>TBACLR<br>TBIC2HR<br>TBIC2LR<br>TBIC2LR<br>TBOC2LR          | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 High Register<br>Timer B Output Compare 2 Low Register                                                                            | 00h<br>00h<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>R/W<br>Read Only<br>Read Only                            |

| 0050h<br>to<br>006Fh                                                                                                                         |         |                                                                                                                                                               | Reserved (32 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |                                                                                                                                                                                                                                                                                                     |

| 0070h<br>0071h                                                                                                                               | ADC     | ADCDR<br>ADCCSR                                                                                                                                               | Data Register<br>Control/Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00h<br>00h                                                                              | Read Only<br>R/W                                                                                                                                                                                                                                                                                    |

| 0072h<br>to<br>007Fh                                                                                                                         |         | ·                                                                                                                                                             | Reserved (14 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |                                                                                                                                                                                                                                                                                                     |

Legend: x=undefined, R/W=read/write

Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

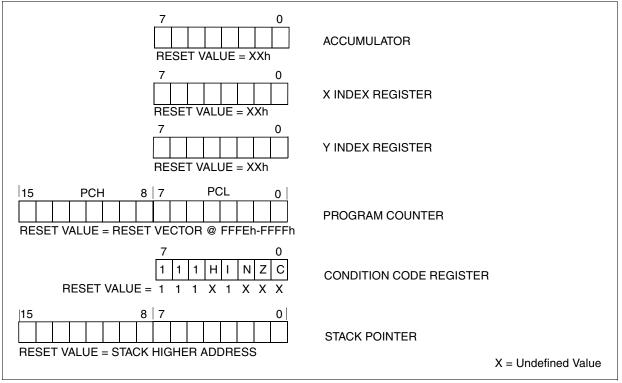

# **5 CENTRAL PROCESSING UNIT**

# **5.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

#### **5.2 MAIN FEATURES**

- 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes

- Two 8-bit index registers

- 16-bit stack pointer

- Low power modes

- Maskable hardware interrupts

- Non-maskable software interrupt

#### **5.3 CPU REGISTERS**

The six CPU registers shown in Figure 1 are not present in the memory mapping and are accessed by specific instructions.

#### Figure 6. CPU Registers

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index Registers (X and Y)

In indexed addressing modes, these 8-bit registers are used to create either effective addresses or temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures (not pushed to and popped from the stack).

#### **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

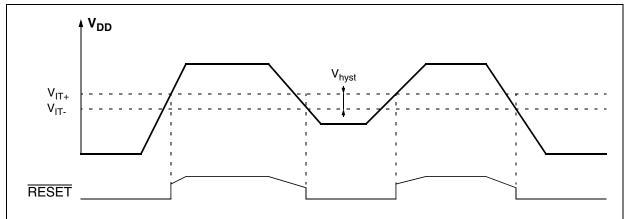

# 6.1 LOW VOLTAGE DETECTOR (LVD)

To allow the integration of power management features in the application, the Low Voltage Detector function (LVD) generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT</sub> reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT</sub> reference value for a voltage drop is lower than the V<sub>IT</sub> reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

$-V_{IT+}$  when  $V_{DD}$  is rising

$-V_{IT-}$  when  $V_{DD}$  is falling

The LVD function is illustrated in the Figure 9.

Provided the minimum  $V_{\text{DD}}$  value (guaranteed for the oscillator frequency) is above  $V_{\text{IT-}}$ , the MCU can only be in two modes:

- under full software control

in static safe reset

#### Figure 9. Low Voltage Detector vs Reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

1. The LVD allows the device to be used without any external RESET circuitry.

2. Three different reference levels are selectable through the option byte according to the application requirement.

#### LVD application note

Application software can detect a reset caused by the LVD by reading the LVDRF bit in the CRSR register.

This bit is set by hardware when a LVD reset is generated and cleared by software (writing zero).

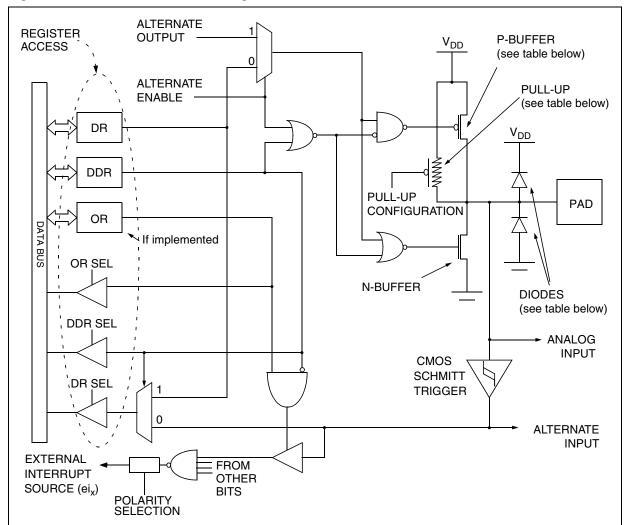

# I/O PORTS (Cont'd)

#### Figure 21. I/O Port General Block Diagram

#### Table 6. I/O Port Mode Options

| Configuration Mode<br>Floating with/without Interrupt |                                 | Bull Up                                                                  | D Ruffor | Diodes             |                    |  |

|-------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------|----------|--------------------|--------------------|--|

|                                                       | Configuration Mode              | Pull-Op                                                                  | F-Bullel | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input                                                 | Floating with/without Interrupt | Off                                                                      | 0#       | 0.5                |                    |  |

| Input                                                 | Pull-up with/without Interrupt  | On                                                                       |          |                    |                    |  |

|                                                       | Push-pull                       | 0#                                                                       | On       |                    | On                 |  |

| Output                                                | Open Drain (logic level)        | Pull-Up     P-Buffer     to V <sub>DD</sub> Off     Off       On     Off |          |                    |                    |  |

|                                                       | True Open Drain                 | NI                                                                       | NI       | NI (see note)      |                    |  |

Legend: NI - not implemented

Off - implemented not activated

On - implemented and activated

**Note**: The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

# MISCELLANEOUS REGISTERS (Cont'd)

## **10.3 MISCELLANEOUS REGISTER DESCRIPTION**

#### **MISCELLANEOUS REGISTER 1 (MISCR1)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |      |      |     |     | 0   |

|------|------|-----|------|------|-----|-----|-----|

| IS11 | IS10 | мсо | IS01 | IS00 | CP1 | CP0 | SMS |

#### Bit 7:6 = IS1[1:0] ei1 sensitivity

The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the ei1 external interrupts. These two bits can be written only when the I bit of the CC register is set to 1 (interrupt masked).

ei1: Port B (C optional)

| External Interrupt Sensitivity | IS11 | IS10 |

|--------------------------------|------|------|

| Falling edge & low level       | 0    | 0    |

| Rising edge only               | 0    | 1    |

| Falling edge only              | 1    | 0    |

| Rising and falling edge        | 1    | 1    |

#### Bit 5 = MCO Main clock out selection

This bit enables the MCO alternate function on the PC2 I/O port. It is set and cleared by software. 0: MCO alternate function disabled (I/O pin free for

- general-purpose I/O)

- 1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

#### Bit 4:3 = **ISO[1:0]** *ei0 sensitivity*

The interrupt sensitivity, defined using the IS0[1:0] bits, is applied to the ei0 external interrupts. These two bits can be written only when the I bit of the CC register is set to 1 (interrupt masked).

#### ei0: Port A (C optional)

5/

| External Interrupt Sensitivity | IS01 | IS00 |

|--------------------------------|------|------|

| Falling edge & low level       | 0    | 0    |

| Rising edge only               | 0    | 1    |

| Falling edge only              | 1    | 0    |

| Rising and falling edge        | 1    | 1    |

#### Bit 2:1 = CP[1:0] CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC</sub> / 4          | 0   | 0   |

| f <sub>OSC</sub> / 8          | 1   | 0   |

| f <sub>OSC</sub> / 16         | 0   | 1   |

| f <sub>OSC</sub> / 32         | 1   | 1   |

Bit 0 = **SMS** *Slow mode select*

This bit is set and cleared by software. 0: Normal mode.  $f_{CPU} = f_{OSC} / 2$

1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0 See low power consumption mode and MCC

chapters for more details.

IEDG1

0

0

0

(Control Register 2) CR2

CC1

CC0 IEDG2

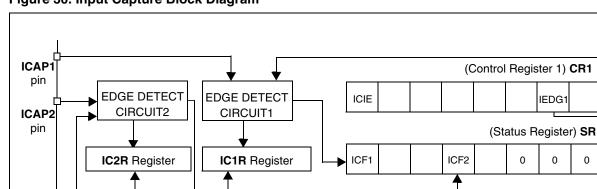

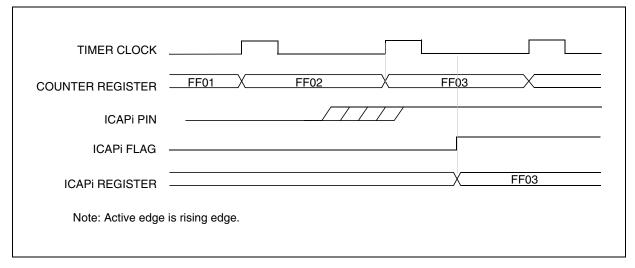

# **16-BIT TIMER** (Cont'd)

#### Figure 30. Input Capture Block Diagram

# Figure 31. Input Capture Timing Diagram

5/

**16-BIT FREE RUNNING**

COUNTER

16-BIT

# 16-BIT TIMER (Cont'd)

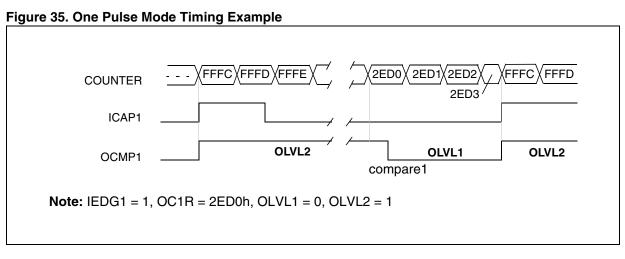

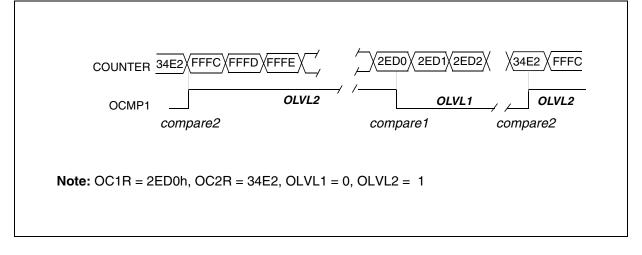

# Figure 36. Pulse Width Modulation Mode Timing Example

## **11.3 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.3.1 Introduction

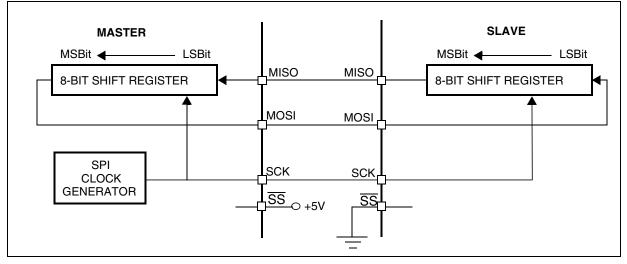

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

The SPI is normally used for communication between the microcontroller and external peripherals or another microcontroller.

Refer to the Pin Description chapter for the devicespecific pin-out.

#### 11.3.2 Main Features

- Full duplex, three-wire synchronous transfers

- Master or slave operation

- Four master mode frequencies

- Maximum slave mode frequency = f<sub>CPU</sub>/4

- Four programmable master bit rates

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision flag protection

- Master mode fault protection capability

#### 11.3.3 General description

The SPI is connected to external devices through 4 alternate pins:

- MISO: Master In Slave Out pin

- MOSI: Master Out Slave In pin

- SCK: Serial Clock pin

- SS: Slave select pin

A basic example of interconnections between a single master and a single slave is illustrated on Figure 1.

The MOSI pins are connected together as are MISO pins. In this way data is transferred serially between master and slave (most significant bit first).

When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex transmission with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

Thus, the byte transmitted is replaced by the byte received and eliminates the need for separate transmit-empty and receiver-full bits. A status flag is used to indicate that the I/O operation is complete.

Four possible data/clock timing relationships may be chosen (see Figure 4) but master and slave must be programmed with the same timing mode.

#### Figure 37. Serial Peripheral Interface Master/Slave

# SERIAL PERIPHERAL INTERFACE (Cont'd) STATUS REGISTER (SR)

Read Only

Reset Value: 0000 0000 (00h)

| 7    |      |   |      |   |   |   | 0 |  |

|------|------|---|------|---|---|---|---|--|

| SPIF | WCOL | - | MODF | - | - | - | - |  |

Bit 7 = **SPIF** Serial Peripheral data transfer flag. This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE=1 in the CR register. It is cleared by a software sequence (an access to the SR register followed by a read or write to the DR register).

- Data transfer is in progress or has been approved by a clearing sequence.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the DR register are inhibited.

#### Bit 6 = WCOL Write Collision status.

This bit is set by hardware when a write to the DR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 5). 0: No write collision occurred 1: A write collision has been detected

Bit 5 = Unused.

#### Bit 4 = **MODF** Mode Fault flag.

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.4.5 Master Mode Fault). An SPI interrupt can be generated if SPIE=1 in the CR register. This bit is cleared by a software sequence (An access to the SR register while MODF=1 followed by a write to the CR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bits 3-0 = Unused.

# DATA I/O REGISTER (DR)

Read/Write

Reset Value: Undefined

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The DR register is used to transmit and receive data on the serial bus. In the master device only a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

#### Warning:

A write to the DR register places data directly into the shift register for transmission.

A read to the DR register returns the value located in the buffer and not the contents of the shift register (See Figure 2).

#### **12.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | CP   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a pre-byte

The instructions are described with one to four bytes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC Opcode

5/

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

- PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

- PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode. It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

- PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

# **13.6 MEMORY CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

# 13.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 13.6.2 FLASH Program Memory

| Symbol               | Parameter                                   | Conditions                          | Min | Тур | Max | Unit   |

|----------------------|---------------------------------------------|-------------------------------------|-----|-----|-----|--------|

| T <sub>A(prog)</sub> | Programming temperature range <sup>2)</sup> |                                     | 0   | 25  | 70  | °C     |

| t <sub>prog</sub>    | Programming time for 1~16 bytes 3)          | T <sub>A</sub> =+25°C               |     | 8   | 25  | ms     |

|                      | Programming time for 4 or 8kBytes           | T <sub>A</sub> =+25°C               |     | 2.1 | 6.4 | sec    |

| t <sub>ret</sub>     | Data retention <sup>5)</sup>                | T <sub>A</sub> =+55°C <sup>4)</sup> | 20  |     |     | years  |

| N <sub>RW</sub>      | Write erase cycles <sup>5)</sup>            | T <sub>A</sub> =+25°C               | 100 |     |     | cycles |

#### Notes:

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Guaranteed by construction, not tested in production.

2. Data based on characterization results, tested in production at T<sub>A</sub>=25°C.

3. Up to 16 bytes can be programmed at a time for a 4kBytes FLASH block (then up to 32 bytes at a time for an 8k device)

4. The data retention time increases when the  $\mathsf{T}_\mathsf{A}$  decreases.

5. Data based on reliability test results and monitored in production.

## EMC CHARACTERISTICS (Cont'd)

#### 13.7.2 Absolute Electrical Sensitivity

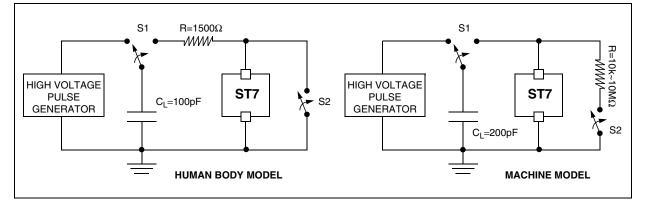

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the AN1181 ST7 application note.

#### 13.7.2.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends of the number of supply pins of the device (3 parts\*(n+1) supply pin). Two models are usually simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard. See Figure 71 and the following test sequences.

#### Human Body Model Test Sequence

- C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to R.

- A discharge from  $C_L$  through R (body resistance) to the ST7 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST7 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

#### Absolute Maximum Ratings

# Machine Model Test Sequence

- C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to ST7.

- A discharge from C<sub>L</sub> to the ST7 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST7 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

- R (machine resistance), in series with S2, ensures a slow discharge of the ST7.

| Symbol                | Ratings                                                | Conditions            | Maximum value 1) | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 2000             | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>A</sub> =+25°C | 200              | V    |

#### Figure 71. Typical Equivalent ESD Circuits

#### Notes:

1. Data based on characterization results, not tested in production.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

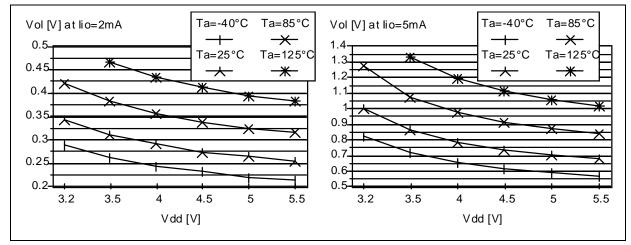

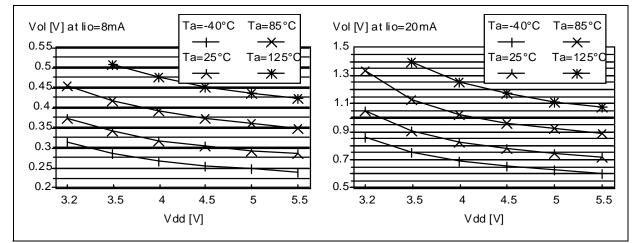

# Figure 83. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard I/Os)

# Figure 84. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (high-sink I/Os)

5

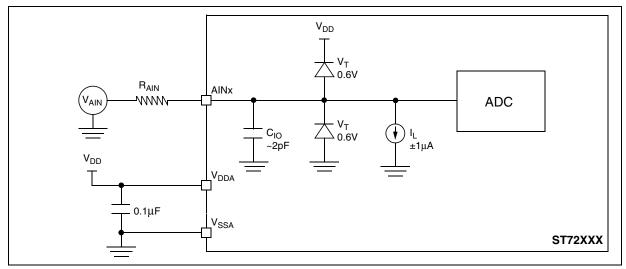

# **13.12 8-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                       | Conditions                                     | Min              | <b>Typ</b> <sup>1)</sup> | Max              | Unit               |

|-------------------|---------------------------------------------------------------------------------|------------------------------------------------|------------------|--------------------------|------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                             |                                                |                  |                          | 4                | MHz                |

| V <sub>AIN</sub>  | Conversion range voltage <sup>2)</sup>                                          |                                                | V <sub>SSA</sub> |                          | $V_{DDA}$        | V                  |

| R <sub>AIN</sub>  | External input resistor                                                         |                                                |                  |                          | 10 <sup>3)</sup> | kΩ                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                              |                                                |                  | 6                        |                  | pF                 |

| t <sub>STAB</sub> | Stabilization time after ADC enable                                             |                                                | 0 <sup>4)</sup>  |                          |                  |                    |

|                   | Conversion time (Sample+Hold)                                                   | f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz | 3                |                          |                  | μs                 |

| t <sub>ADC</sub>  | <ul> <li>Sample capacitor loading time</li> <li>Hold conversion time</li> </ul> |                                                | 4<br>8           |                          |                  | 1/f <sub>ADC</sub> |

## Figure 95. Typical Application with ADC

#### Notes:

1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$  and  $V_{DD}-V_{SS}=5V$ . They are given only as design guide-lines and are not tested.

2. When  $V_{DDA}$  and  $V_{SSA}$  pins are not available on the pinout, the ADC refer to  $V_{DD}$  and  $V_{SS}$  .

3. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

4. The stabilization time of the AD converter is masked by the first  $t_{LOAD}$ . The first conversion after the enable is then always valid.

| IDENTIFICATION | DESCRIPTION                                                                          |

|----------------|--------------------------------------------------------------------------------------|

| AN 982         | USING ST7 WITH CERAMIC RESONATOR                                                     |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                            |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                    |

| AN1040         | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                              |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                                |

| AN1324         | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS                   |

| AN1477         | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                         |

| AN1529         | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY                 |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCIL-<br>LATOR     |

| PROGRAMMING A  | ND TOOLS                                                                             |

| AN 978         | KEY FEATURES OF THE STVD7 ST7 VISUAL DEBUG PACKAGE                                   |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                                    |

| AN 985         | EXECUTING CODE IN ST7 RAM                                                            |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                                          |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                               |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                                |

| AN 989         | GETTING STARTED WITH THE ST7 HIWARE C TOOLCHAIN                                      |

| AN1039         | ST7 MATH UTILITY ROUTINES                                                            |

| AN1064         | WRITING OPTIMIZED HIWARE C LANGUAGE FOR ST7                                          |

| AN1071         | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER               |

| AN1106         | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |

| AN1179         | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |

| AN1446         | USING THE ST72521 EMULATOR TO DEBUG A ST72324 TARGET APPLICATION                     |

| AN1478         | PORTING AN ST7 PANTA PROJECT TO CODEWARRIOR IDE                                      |

| AN1527         | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |

| AN1575         | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |

57

# **16 SUMMARY OF CHANGES**

Description of the changes between the current release of the specification and the previous one.

| Rev. | Main changes                                                                                                                                                                                                                                                                                                    | Date     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

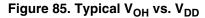

| 2.7  | Changed Status from Preliminary Data to Datasheet<br>Changed V <sub>IN</sub> on page 97 (in the voltage characteristics table).<br>Changed titles of Figure 82 on page 119 and Figure 85 on page 120.<br>Updated Section 15.4 on page 138.<br>Changed description of FMP option bit in Section 15.1 on page 133 | Sept-01  |

| 2.8  | Modified description of external and internal RC in "MULTI-OSCILLATOR (MO)" on page 21                                                                                                                                                                                                                          | June 03  |

| 3    | Removed preliminary status.<br>Updated Section 14.3 on page 132 for Ecopack<br>Removed resonators for automotive applications in Section 13.5.3.2 on page 107                                                                                                                                                   | March 08 |