#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.2V ~ 5.5V                                                          |

| Data Converters            | A/D 6x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                            |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72c254g2b6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 2 PIN D<br>3 REGI | ODUCTION<br>DESCRIPTION<br>STER & MEMORY MAP<br>SH PROGRAM MEMORY | 7<br>10 |

|-------------------|-------------------------------------------------------------------|---------|

| 4.1               |                                                                   | 13      |

| 4.2               | MAIN FEATURES                                                     | 13      |

| 4.3               | STRUCTURAL ORGANISATION                                           | 13      |

| 4.4               | IN-SITU PROGRAMMING (ISP) MODE                                    | 13      |

| 4.5               | MEMORY READ-OUT PROTECTION                                        | 13      |

| 5 CEN             | IRAL PROCESSING UNIT                                              | 14      |

| 5.1               |                                                                   | 14      |

| 5.2               | MAIN FEATURES                                                     | 14      |

| 5.3               | CPU REGISTERS                                                     | 14      |

| 6 SUPF            | PLY, RESET AND CLOCK MANAGEMENT                                   | 17      |

| 6.1               | LOW VOLTAGE DETECTOR (LVD)                                        | 18      |

| 6.2               | RESET SEQUENCE MANAGER (RSM)                                      | 19      |

|                   | 6.2.1 Introduction                                                |         |

|                   | 6.2.2 Asynchronous External RESET pin                             |         |

|                   | 6.2.3 Internal Low Voltage Detection RESET                        |         |

| 6.3               | 6.2.4 Internal Watchdog RESET                                     |         |

| 6.4               | CLOCK SECURITY SYSTEM (CSS)                                       |         |

| 0.4               | 6.4.1 Clock Filter Control                                        |         |

|                   | 6.4.2 Safe Oscillator Control                                     |         |

|                   | 6.4.3 Low Power Modes                                             |         |

|                   | 6.4.4 Interrupts                                                  | 22      |

| 6.5               | CLOCK RESET AND SUPPLY REGISTER DESCRIPTION (CRSR)                |         |

| 6.6               | MAIN CLOCK CONTROLLER (MCC)                                       | 24      |

| 7 INTE            | RRUPTS                                                            |         |

| 7.1               | NON-MASKABLE SOFTWARE INTERRUPT                                   | 25      |

| 7.2               | EXTERNAL INTERRUPTS                                               | 25      |

| 7.3               | PERIPHERAL INTERRUPTS                                             | 25      |

| 8 POW             | ER SAVING MODES                                                   |         |

| 8.1               |                                                                   | 27      |

| 8.2               | SLOW MODE                                                         | 27      |

| 8.3               | WAIT MODE                                                         | 28      |

| 8.4               | HALT MODE                                                         | 29      |

| 9 I/O P           | ORTS                                                              | 30      |

| 9.1               |                                                                   | 30      |

| 9.2               | FUNCTIONAL DESCRIPTION                                            | 30      |

|                   | 9.2.1 Input Modes                                                 |         |

|                   | 9.2.2 Output Modes                                                |         |

|                   | 9.2.3 Alternate Functions                                         |         |

| 9.3               | I/O PORT IMPLEMENTATION                                           | 33      |

**57**

## **10 MISCELLANEOUS REGISTERS**

The miscellaneous registers allow control over several different features such as the external interrupts or the I/O alternate functions.

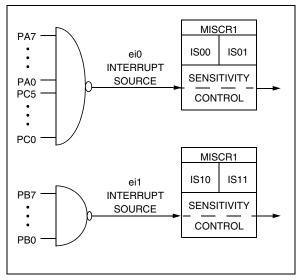

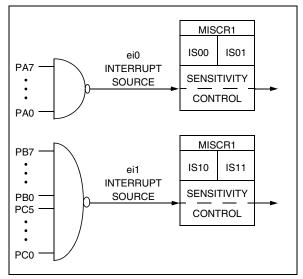

## **10.1 I/O PORT INTERRUPT SENSITIVITY**

The external interrupt sensitivity is controlled by the ISxx bits of the Miscellaneous register and the OPTION BYTE. This control allows having two fully independent external interrupt source sensitivities with configurable sources (using EXTIT option bit) as shown in Figure 23 and Figure 24.

Each external interrupt source can be generated on four different events on the pin:

- Falling edge

- Rising edge

- Falling and rising edge

- Falling edge and low level

To guarantee correct functionality, the sensitivity bits in the MISCR1 register must be modified only when the I bit of the CC register is set to 1 (interrupt masked). See I/O port register and Miscellaneous register descriptions for more details on the programming.

## **10.2 I/O PORT ALTERNATE FUNCTIONS**

The MISCR registers manage four I/O port miscellaneous alternate functions:

- Main clock signal (f<sub>CPU</sub>) output on PC2

- SPI pin configuration:

- SS pin internal control to use the PB7 I/O port function while the SPI is active.

- Master output capability on MOSI pin (PB4) deactivated while the SPI is active.

- Slave output capability on MISO pin (PB5) deactivated while the SPI is active.

These functions are described in detail in the Section 10.3 "MISCELLANEOUS REGISTER DE-SCRIPTION" on page 37.

## Figure 23. Ext. Interrupt Sensitivity (EXTIT=0)

Figure 24. Ext. Interrupt Sensitivity (EXTIT=1)

## MISCELLANEOUS REGISTERS (Cont'd)

## **10.3 MISCELLANEOUS REGISTER DESCRIPTION**

#### **MISCELLANEOUS REGISTER 1 (MISCR1)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |      |      |     |     | 0   |

|------|------|-----|------|------|-----|-----|-----|

| IS11 | IS10 | мсо | IS01 | IS00 | CP1 | CP0 | SMS |

#### Bit 7:6 = IS1[1:0] ei1 sensitivity

The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the ei1 external interrupts. These two bits can be written only when the I bit of the CC register is set to 1 (interrupt masked).

ei1: Port B (C optional)

| External Interrupt Sensitivity | IS11 | IS10 |

|--------------------------------|------|------|

| Falling edge & low level       | 0    | 0    |

| Rising edge only               | 0    | 1    |

| Falling edge only              | 1    | 0    |

| Rising and falling edge        | 1    | 1    |

#### Bit 5 = MCO Main clock out selection

This bit enables the MCO alternate function on the PC2 I/O port. It is set and cleared by software. 0: MCO alternate function disabled (I/O pin free for

- general-purpose I/O)

- 1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

#### Bit 4:3 = **ISO[1:0]** *ei0 sensitivity*

The interrupt sensitivity, defined using the IS0[1:0] bits, is applied to the ei0 external interrupts. These two bits can be written only when the I bit of the CC register is set to 1 (interrupt masked).

#### ei0: Port A (C optional)

5/

| External Interrupt Sensitivity | IS01 | IS00 |

|--------------------------------|------|------|

| Falling edge & low level       | 0    | 0    |

| Rising edge only               | 0    | 1    |

| Falling edge only              | 1    | 0    |

| Rising and falling edge        | 1    | 1    |

#### Bit 2:1 = CP[1:0] CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC</sub> / 4          | 0   | 0   |

| f <sub>OSC</sub> / 8          | 1   | 0   |

| f <sub>OSC</sub> / 16         | 0   | 1   |

| f <sub>OSC</sub> / 32         | 1   | 1   |

Bit 0 = **SMS** *Slow mode select*

This bit is set and cleared by software. 0: Normal mode.  $f_{CPU} = f_{OSC} / 2$

1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0 See low power consumption mode and MCC

chapters for more details.

57/

| CPU CLOCK                 |                                                 |

|---------------------------|-------------------------------------------------|

| INTERNAL RESET            |                                                 |

| TIMER CLOCK               |                                                 |

| -<br>COUNTER REGISTER _   | \ FFFD\ FFFE\ FFFF\ 0000 \ 0001 \ 0002 \ 0003 \ |

| TIMER OVERFLOW FLAG (TOF) |                                                 |

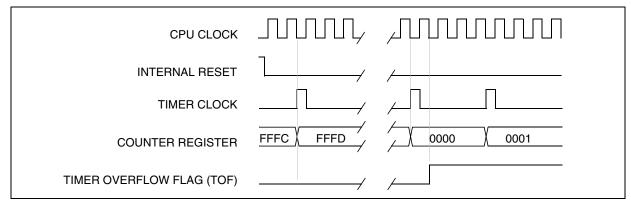

## Figure 27. Counter Timing Diagram, internal clock divided by 2

## Figure 28. Counter Timing Diagram, internal clock divided by 4

## Figure 29. Counter Timing Diagram, internal clock divided by 8

| CPU CLOCK                 |                |

|---------------------------|----------------|

| INTERNAL RESET            | 1              |

| TIMER CLOCK               | /              |

| COUNTER REGISTER          | FFFC FFFD 0000 |

| TIMER OVERFLOW FLAG (TOF) |                |

Note: The MCU is in reset state when the internal reset signal is high. When it is low, the MCU is running.

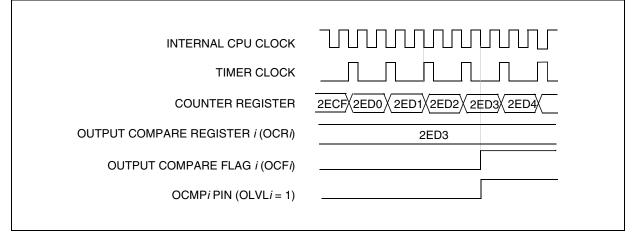

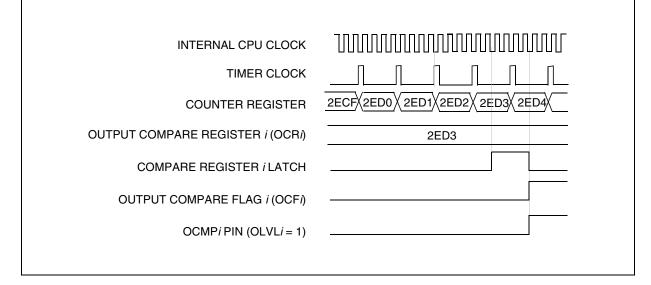

## Figure 33. Output Compare Timing Diagram, f<sub>TIMER</sub> = f<sub>CPU</sub>/2

## Figure 34. Output Compare Timing Diagram, $f_{TIMER} = f_{CPU}/4$

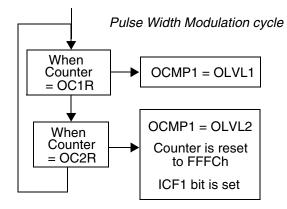

### 11.2.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

The Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so these functions cannot be used when the PWM mode is activated.

#### Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if OLVL1 = 0 and OLVL2 = 1, using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

5/

- Select the timer clock (CC[1:0]) (see Table 1).

If OLVL1 = 1 and OLVL2 = 0, the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OC_{i}R Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 1)

If the timer clock is an external clock the formula is:

$$OC/R = t * f_{EXT} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 11)

#### Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode, therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected from the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset after each period and ICF1 can also generate an interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

#### 11.2.7 Register Description

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = ICIE Input Capture Interrupt Enable.

- 0: Interrupt is inhibited.

- 1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.*

0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

#### Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse mode and Pulse Width Modulation mode.

#### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

## 16-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |     |     |     |       | 0     |

|------|------|-----|-----|-----|-----|-------|-------|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | EXEDG |

### Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the internal Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the internal Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

#### Bit 5 = **OPM** One Pulse mode.

- 0: One Pulse mode is not active.

- 1: One Pulse mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

## Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

Bits 3:2 = CC[1:0] Clock Control.

The timer clock mode depends on these bits:

#### Table 13. Clock Control Bits

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             | 0   | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) | 1   | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

#### Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin (EXTCLK) will trigger the counter register.

0: A falling edge triggers the counter register.

1: A rising edge triggers the counter register.

# OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## **COUNTER HIGH REGISTER (CHR)**

#### Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## COUNTER LOW REGISTER (CLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the SR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# ALTERNATE COUNTER HIGH REGISTER (ACHR)

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to SR register does not clear the TOF bit in SR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **INPUT CAPTURE 2 HIGH REGISTER (IC2HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## SERIAL PERIPHERAL INTERFACE (Cont'd)

#### **11.3.4 Functional Description**

Figure 1 shows the serial peripheral interface (SPI) block diagram.

This interface contains three dedicated registers:

- A Control Register (CR)

- A Status Register (SR)

- A Data Register (DR)

Refer to the CR, SR and DR registers in Section 0.1.7 for the bit definitions.

## 11.3.4.1 Master Configuration

In a master configuration, the serial clock is generated on the SCK pin.

#### Procedure

- Select the SPR0 & SPR1 bits to define the serial clock baud rate (see CR register).

- Select the CPOL and CPHA bits to define one of the four relationships between the data transfer and the serial clock (see Figure 4).

- The SS pin must be connected to a high level signal during the complete byte transmit sequence.

- The MSTR and SPE <u>bits</u> must be set (they remain set only if the SS pin is connected to a high level signal).

In this configuration the MOSI pin is a data output and to the MISO pin is a data input.

### **Transmit sequence**

The transmit sequence begins when a byte is written the DR register.

The data byte is parallel loaded into the 8-bit shift register (from the internal bus) during a write cycle and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt is generated if the SPIE bit is set and the I bit in the CCR register is cleared.

During the last clock cycle the SPIF bit is set, a copy of the data byte received in the shift register is moved to a buffer. When the DR register is read, the SPI peripheral returns this buffered value.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SR register while the SPIF bit is set

- 2. A read to the DR register.

**Note:** While the SPIF bit is set, all writes to the DR register are inhibited until the SR register is read.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.3.4.2 Slave Configuration

In slave configuration, the serial clock is received on the SCK pin from the master device.

The value of the SPR0 & SPR1 bits is not used for the data transfer.

#### Procedure

- For correct data transfer, the slave device must be in the same timing mode as the master device (CPOL and CPHA bits). See Figure 4.

- The SS pin must be connected to a low level signal during the complete byte transmit sequence.

- Clear the MSTR bit and set the SPE bit to assign the pins to alternate function.

In this configuration the MOSI pin is a data input and the MISO pin is a data output.

#### **Transmit Sequence**

5/

The data byte is parallel loaded into the 8-bit shift register (from the internal bus) during a write cycle and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin. When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt is generated if SPIE bit is set and I bit in CCR register is cleared.

During the last clock cycle the SPIF bit is set, a copy of the data byte received in the shift register is moved to a buffer. When the DR register is read, the SPI peripheral returns this buffered value.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SR register while the SPIF bit is set.

- 2.A read to the DR register.

**Notes:** While the SPIF bit is set, all writes to the DR register are inhibited until the SR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an overrun condition (see Section 0.1.4.6).

Depending on the CPHA bit, the  $\overline{SS}$  pin has to be set to write to the DR register between each data byte transfer to avoid a write collision (see Section 0.1.4.4).

## SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.3.4.4 Write Collision Error

A write collision occurs when the software tries to write to the DR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode.

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

#### In Slave mode

When the CPHA bit is set:

The slave device will receive a clock (SCK) edge prior to the latch of the first data transfer. This first clock edge will freeze the data in the slave device DR register and output the MSBit on to the external MISO pin of the slave device.

The  $\overline{SS}$  pin low state enables the slave device but the output of the MSBit onto the MISO pin does not take place until the first data transfer clock edge. When the CPHA bit is reset:

Data is latched on the occurrence of the first clock transition. The slave device does not have any way of knowing when that transition will occur; therefore, the slave device collision occurs when software attempts to write the DR register after its SS pin has been pulled low.

For this reason, the  $\overline{SS}$  pin must be high, between each data byte transfer, to allow the CPU to write in the DR register without generating a write collision.

#### In Master mode

Collision in the master device is defined as a write of the DR register while the internal serial clock (SCK) is in the process of transfer.

The  $\overline{SS}$  pin signal must be always high on the master device.

#### WCOL bit

The WCOL bit in the SR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

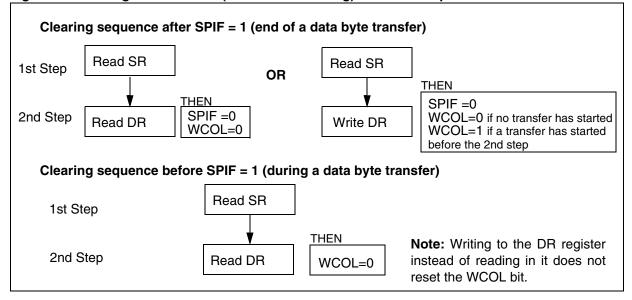

Clearing the WCOL bit is done through a software sequence (see Figure 5).

#### Figure 41. Clearing the WCOL bit (Write Collision Flag) Software Sequence

## SERIAL PERIPHERAL INTERFACE (Cont'd) STATUS REGISTER (SR)

Read Only

Reset Value: 0000 0000 (00h)

| 7    |      |   |      |   |   |   | 0 |  |

|------|------|---|------|---|---|---|---|--|

| SPIF | WCOL | - | MODF | - | - | - | - |  |

Bit 7 = **SPIF** Serial Peripheral data transfer flag. This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE=1 in the CR register. It is cleared by a software sequence (an access to the SR register followed by a read or write to the DR register).

- Data transfer is in progress or has been approved by a clearing sequence.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the DR register are inhibited.

## Bit 6 = WCOL Write Collision status.

This bit is set by hardware when a write to the DR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 5). 0: No write collision occurred 1: A write collision has been detected

Bit 5 = Unused.

#### Bit 4 = **MODF** Mode Fault flag.

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.4.5 Master Mode Fault). An SPI interrupt can be generated if SPIE=1 in the CR register. This bit is cleared by a software sequence (An access to the SR register while MODF=1 followed by a write to the CR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bits 3-0 = Unused.

## DATA I/O REGISTER (DR)

Read/Write

Reset Value: Undefined

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The DR register is used to transmit and receive data on the serial bus. In the master device only a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

#### Warning:

A write to the DR register places data directly into the shift register for transmission.

A read to the DR register returns the value located in the buffer and not the contents of the shift register (See Figure 2).

## I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | ССЗ | CC2 | CC1 | CC0 |

## Bit 7 = **FM/SM** Fast/Standard $l^2C$ mode.

This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard  $I^2C$  mode

1: Fast I<sup>2</sup>C mode

Bit 6:0 = CC[6:0] 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

## I<sup>2</sup>C DATA REGISTER (DR)

#### Read / Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

Bit 7:0 = D[7:0] 8-bit Data Register.

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

## INSTRUCTION GROUPS (Cont'd)

| Mnemo | Description                | Function/Example    | Dst    | Src | Н | I | N | Ζ | С |

|-------|----------------------------|---------------------|--------|-----|---|---|---|---|---|

| ADC   | Add with Carry             | A = A + M + C       | А      | М   | Н |   | Ν | Z | С |

| ADD   | Addition                   | A=A+M               | А      | М   | Н |   | Ν | Z | С |

| AND   | Logical And                | A = A . M           | А      | М   |   |   | Ν | Z |   |

| BCP   | Bit compare A, Memory      | tst (A . M)         | А      | М   |   |   | N | Z |   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |   |   |   |   |   |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| CALL  | Call subroutine            |                     |        |     |   |   |   |   |   |

| CALLR | Call subroutine relative   |                     |        |     |   |   |   |   |   |

| CLR   | Clear                      |                     | reg, M |     |   |   | 0 | 1 |   |

| СР    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |   |   | Ν | Z | С |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |   |   | Ν | Z | 1 |

| DEC   | Decrement                  | dec Y               | reg, M |     |   |   | Ν | Z |   |

| HALT  | Halt                       |                     |        |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     | Н | I | Ν | Z | С |

| INC   | Increment                  | inc X               | reg, M |     |   |   | Ν | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |   |   |   |   |   |

| JRA   | Jump relative always       |                     |        |     |   |   |   |   |   |

| JRT   | Jump relative              |                     |        |     |   |   |   |   |   |

| JRF   | Never jump                 | jrf *               |        |     |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |   |   |   |   |   |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |   |   |   |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |   |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |   |   |   |   |   |

| JRNC  | Jump if $C = 0$            | C = 0 ?             |        |     |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |   |   |   |   |   |

| JRUGE | Jump if $C = 0$            | Jmp if unsigned >=  |        |     |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |   |   |   |   |   |

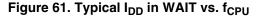

Figure 62. Typical I<sub>DD</sub> in SLOW-WAIT vs. f<sub>CPU</sub>

## SUPPLY CURRENT CHARACTERISTICS (Cont'd) 13.4.2 WAIT and SLOW WAIT Modes

| Symbol          | Parameter                                                      |                            | Conditions                                                                                                                                             | Typ <sup>1)</sup>  | Max <sup>2)</sup>  | Unit |

|-----------------|----------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| I <sub>DD</sub> | Supply current in WAIT mode <sup>3)</sup><br>(see Figure 61)   | <sub>)D</sub> ≤5.5V        | $\begin{array}{l} f_{OSC} = 1 MHz, \ f_{CPU} = 500 kHz \\ f_{OSC} = 4 MHz, \ f_{CPU} = 2 MHz \\ f_{OSC} = 16 MHz, \ f_{CPU} = 8 MHz \end{array}$       | 150<br>560<br>2200 | 280<br>900<br>3000 |      |

|                 | Supply current in SLOW WAIT mode <sup>4)</sup> (see Figure 62) | 4.5V≤V <sub>DD</sub> ≤5    | $\begin{array}{l} f_{OSC} = 1 MHz, \ f_{CPU} = 31.25 kHz \\ f_{OSC} = 4 MHz, \ f_{CPU} = 125 kHz \\ f_{OSC} = 16 MHz, \ f_{CPU} = 500 kHz \end{array}$ | 20<br>90<br>340    | 70<br>190<br>850   | μA   |

|                 | Supply current in WAIT mode <sup>3)</sup><br>(see Figure 61)   | 3.2V≤V <sub>DD</sub> ≤3.6V | $f_{OSC}$ =1MHz, $f_{CPU}$ =500kHz<br>$f_{OSC}$ =4MHz, $f_{CPU}$ =2MHz<br>$f_{OSC}$ =16MHz, $f_{CPU}$ =8MHz                                            | 90<br>350<br>1370  | 200<br>550<br>1900 | μΛ   |

|                 | Supply current in SLOW WAIT mode <sup>4)</sup> (see Figure 62) |                            | $\begin{array}{l} f_{OSC}=1MHz, \ f_{CPU}=31.25kHz\\ f_{OSC}=4MHz, \ f_{CPU}=125kHz\\ f_{OSC}=16MHz, \ f_{CPU}=500kHz \end{array}$                     | 10<br>50<br>200    | 20<br>80<br>350    |      |

#### Notes:

<u>ل</u>حک

1. Typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (4.5V $\leq$ V<sub>DD</sub> $\leq$ 5.5V range) and V<sub>DD</sub>=3.4V (3.2V $\leq$ V<sub>DD</sub> $\leq$ 3.6V range).

2. Data based on characterization results, tested in production at  $V_{\text{DD}}$  max. and  $f_{\text{CPU}}$  max.

3. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, CSS and LVD disabled.

4. SLOW-WAIT mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, CSS and LVD disabled.

## **13.6 MEMORY CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

## 13.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

## 13.6.2 FLASH Program Memory

| Symbol               | Parameter                                   | Conditions                          | Min | Тур | Max | Unit   |

|----------------------|---------------------------------------------|-------------------------------------|-----|-----|-----|--------|

| T <sub>A(prog)</sub> | Programming temperature range <sup>2)</sup> |                                     | 0   | 25  | 70  | °C     |

| t <sub>prog</sub>    | Programming time for 1~16 bytes 3)          | T <sub>A</sub> =+25°C               |     | 8   | 25  | ms     |

|                      | Programming time for 4 or 8kBytes           | T <sub>A</sub> =+25°C               |     | 2.1 | 6.4 | sec    |

| t <sub>ret</sub>     | Data retention <sup>5)</sup>                | T <sub>A</sub> =+55°C <sup>4)</sup> | 20  |     |     | years  |

| N <sub>RW</sub>      | Write erase cycles <sup>5)</sup>            | T <sub>A</sub> =+25°C               | 100 |     |     | cycles |

#### Notes:

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Guaranteed by construction, not tested in production.

2. Data based on characterization results, tested in production at T<sub>A</sub>=25°C.

3. Up to 16 bytes can be programmed at a time for a 4kBytes FLASH block (then up to 32 bytes at a time for an 8k device)

4. The data retention time increases when the  $\mathsf{T}_\mathsf{A}$  decreases.

5. Data based on reliability test results and monitored in production.

## CONTROL PIN CHARACTERISTICS (Cont'd)

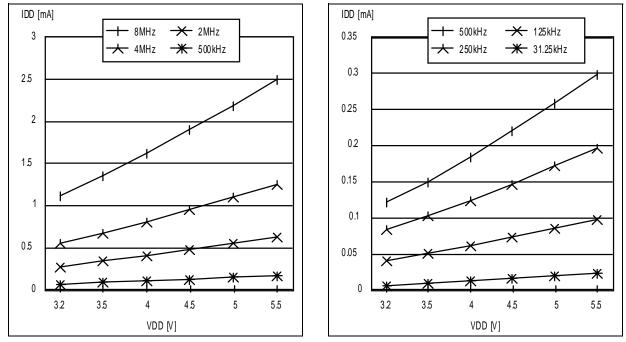

## 13.9.2 ISPSEL Pin

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{OSC}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol          | Parameter                              | Conditions                       | Min                  | Max  | Unit |

|-----------------|----------------------------------------|----------------------------------|----------------------|------|------|

| V <sub>IL</sub> | Input low level voltage <sup>1)</sup>  |                                  | V <sub>SS</sub>      | 0.2  | V    |

| V <sub>IH</sub> | Input high level voltage <sup>1)</sup> |                                  | V <sub>DD</sub> -0.1 | 12.6 | v    |

| ١ <sub>L</sub>  | Input leakage current                  | V <sub>IN</sub> =V <sub>SS</sub> |                      | ±1   | μA   |

## Figure 90. Two typical Applications with ISPSEL Pin<sup>2)</sup>

#### Notes:

57/

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When the ISP Remote mode is not required by the application ISPSEL pin must be tied to  $V_{SS}$ .

## **13.10 TIMER PERIPHERAL CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

#### 13.10.1 Watchdog Timer

| Symbol              | Parameter                  | Conditions             | Min    | Тур | Max     | Unit             |

|---------------------|----------------------------|------------------------|--------|-----|---------|------------------|

| t <sub>w(WDG)</sub> | Watchdog time-out duration |                        | 12,288 |     | 786,432 | t <sub>CPU</sub> |

|                     | Watchdog time-out duration | f <sub>CPU</sub> =8MHz | 1.54   |     | 98.3    | ms               |

#### 13.10.2 16-Bit Timer

| Symbol                 | Parameter                      | Conditions             | Min | Тур | Max                 | Unit             |

|------------------------|--------------------------------|------------------------|-----|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time       |                        | 1   |     |                     | t <sub>CPU</sub> |

| t <sub>res(PWM)</sub>  | PWM resolution time            |                        | 2   |     |                     | t <sub>CPU</sub> |

|                        | F WW Tesolution time           | f <sub>CPU</sub> =8MHz | 250 |     |                     | ns               |

| f <sub>EXT</sub>       | Timer external clock frequency |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| f <sub>PWM</sub>       | PWM repetition rate            |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| Res <sub>PWM</sub>     | PWM resolution                 |                        |     |     | 16                  | bit              |

## **15.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE**

Customer code is made up of the ROM contents and the list of the selected options (if any). The ROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh. The selected options are communicated to STMicroelectronics using the correctly completed OPTION LIST appended.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

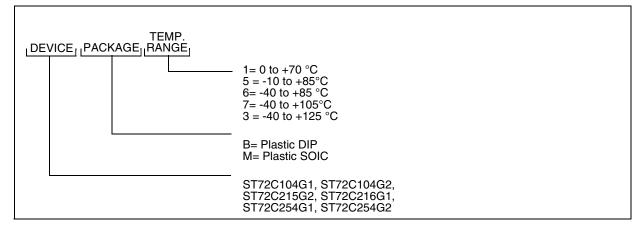

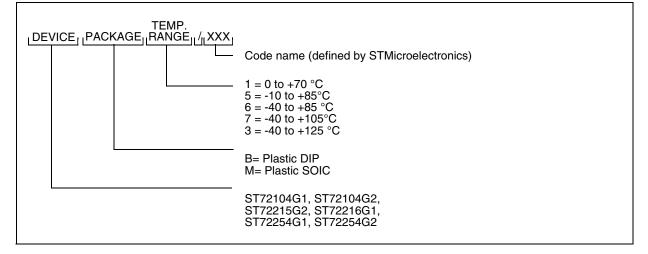

#### Figure 99. ROM Factory Coded Device Types

#### Figure 100. FLASH User Programmable Device Types