## NXP USA Inc. - MCIMX6G2AVM07AB Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A7                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 696MHz                                                                  |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                  |

| RAM Controllers                 | LPDDR2, DDR3, DDR3L                                                     |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | LCD, LVDS                                                               |

| Ethernet                        | 10/100Mbps (2)                                                          |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 + PHY (2)                                                       |

| Voltage - I/O                   | 1.2V, 1.35V, 1.5V, 1.8V, 2.5V, 2.8V, 3.3V                               |

| Operating Temperature           | -40°C ~ 125°C (TJ)                                                      |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                     |

| Package / Case                  | 289-LFBGA                                                               |

| Supplier Device Package         | 289-MAPBGA (14x14)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6g2avm07ab |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

i.MX 6UltraLite introduction

| Peripheral Name | Instance | G0 | G1 | G2 | G3 |

|-----------------|----------|----|----|----|----|

| SDIO            | uSDHC1   | Y  | Y  | Y  | Y  |

|                 | uSDHC2   | Y  | Y  | Y  | Y  |

| UART            | UART1    | Y  | Y  | Y  | Y  |

|                 | UART2    | Y  | Y  | Y  | Y  |

|                 | UART3    | Y  | Y  | Y  | Y  |

|                 | UART4    | Y  | Y  | Y  | Y  |

|                 | UART5    | NA | Y  | Y  | Y  |

|                 | UART6    | NA | Y  | Y  | Y  |

|                 | UART7    | NA | Y  | Y  | Y  |

|                 | UART8    | NA | Y  | Y  | Y  |

| ISO7816-3       | SIM1     | NA | Y  | Y  | Y  |

|                 | SIM2     | NA | Y  | Y  | Y  |

| 12C             | I2C1     | Y  | Y  | Y  | Y  |

|                 | I2C2     | Y  | Y  | Y  | Y  |

|                 | I2C3     | NA | Y  | Y  | Y  |

|                 | I2C4     | NA | Y  | Y  | Y  |

| SPI             | ECSPI1   | Y  | Y  | Y  | Y  |

|                 | ECSPI2   | Y  | Y  | Y  | Y  |

|                 | ECSPI3   | NA | Y  | Y  | Y  |

|                 | ECSPI4   | NA | Y  | Y  | Y  |

| I2S/SAI         | SAI1     | Y  | Y  | Y  | Y  |

|                 | SAI2     | NA | Y  | Y  | Y  |

|                 | SAI3     | NA | Y  | Y  | Y  |

| Table 2. Detailed Peripherals I | Information (continu | ıed) <sup>1,2,3</sup> |

|---------------------------------|----------------------|-----------------------|

|---------------------------------|----------------------|-----------------------|

#### i.MX 6UltraLite introduction

| Peripheral Name | Instance | G0 | G1 | G2 | G3 |

|-----------------|----------|----|----|----|----|

| Timer/PWM       | EPIT1    | Y  | Y  | Y  | Y  |

|                 | EPIT2    | NA | Y  | Y  | Y  |

|                 | GPT1     | Y  | Y  | Y  | Y  |

|                 | GPT2     | NA | Y  | Y  | Y  |

|                 | PWM1     | Y  | Y  | Y  | Y  |

|                 | PWM2     | Y  | Y  | Y  | Y  |

|                 | PWM3     | Y  | Y  | Y  | Y  |

|                 | PWM4     | Y  | Y  | Y  | Y  |

|                 | PWM5     | NA | Y  | Y  | Y  |

|                 | PWM6     | NA | Y  | Y  | Y  |

|                 | PWM7     | NA | Y  | Y  | Y  |

|                 | PWM8     | NA | Y  | Y  | Y  |

| ADC             | ADC1     | Y  | Y  | Y  | Y  |

|                 | ADC2     | NA | NA | Y  | Y  |

Table 2. Detailed Peripherals Information (continued)<sup>1,2,3</sup>

<sup>1</sup>For detailed pin mux information, please refer to "Chapter 4 External Signals and Pin Multiplexing" of *i.MX* 6UltraLite *Reference Manual* (IMX6ULRM).

<sup>2</sup> Y stands for yes, NA stands for not available.

<sup>3</sup> G0 and G3 are offered in automotive grade.

# 1.2 Features

The i.MX 6UltraLite processors are based on ARM Cortex-A7 MPCore<sup>™</sup> Platform, which has the following features:

- Supports single ARM Cortex-A7 MPCore (with TrustZone) with:

- 32 KBytes L1 Instruction Cache

- 32 KBytes L1 Data Cache

- Private Timer

- Cortex-A7 NEON Media Processing Engine (MPE) Co-processor

- General Interrupt Controller (GIC) with 128 interrupts support

- Global Timer

٠

- Snoop Control Unit (SCU)

- 128 KB unified I/D L2 cache

- Single Master AXI bus interface output of L2 cache

- Frequency of the core (including Neon and L1 cache), as per Table 10, "Operating Ranges," on page 23.

## Modules list

| Block Mnemonic   | Block Name                                                                          | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC1<br>uSDHC2 | SD/MMC and SDXC<br>Enhanced Multi-Media<br>Card / Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6UltraLite specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.5/4.2/4.3/4.4/4.41/ including high-capacity (size &gt; 2 GB) cards HC MMC.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDXC cards up to 2 TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v3.0</li> <li>Two ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>4-bit or 8-bit transfer mode specifications for eMMC chips up to 200 MHz in HS200 mode (200 MB/s max)</li> </ul> |

| USB              | Universal Serial Bus 2.0                                                            | Connectivity<br>Peripherals | <ul> <li>USBO2 (USB OTG1 and USB OTG2) contains:</li> <li>Two high-speed OTG 2.0 modules with integrated<br/>HS USB PHYs</li> <li>Support eight Transmit (TX) and eight Receive (Rx)<br/>endpoints, including endpoint 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WDOG1<br>WDOG3   | Watch Dog                                                                           | Timer Peripherals           | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WDOG2<br>(TZ)    | Watch Dog (TrustZone)                                                               | Timer Peripherals           | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW.                                                                                                                                                                                          |

# Table 3. i.MX 6UltraLite Modules List (continued)

**Modules list**

# 3.1 Special signal considerations

Table 4 lists special signal considerations for the i.MX 6UltraLite processors. The signal names are listed in alphabetical order.

The package contact assignments can be found in Section 6, "Package information and contact assignments"." Signal descriptions are provided in the *i.MX 6UltraLite Reference Manual* (IMX6ULRM).

| Signal Name               | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCM_CLK1_P/<br>CCM_CLK1_N | <ul> <li>One general purpose differential high speed clock Input/output is provided.</li> <li>It can be used: <ul> <li>To feed external reference clock to the PLLs and further to the modules inside SoC.</li> <li>To output internal SoC clock to be used outside the SoC as either reference clock or as a functional clock for peripherals.</li> </ul> </li> <li>See the <i>i.MX</i> 6UltraLite Reference Manual (IMX6ULRM) for details on the respective clock trees. Alternatively one may use single ended signal to drive CLK1_P input. In this case corresponding CLK1_N input should be tied to the constant voltage level equal 1/2 of the input signal swing. Termination should be provided in case of high frequency signals.</li> <li>After initialization, the CLK1 input/output can be disabled (if not used). If unused either or both of the CLK1_N/P pairs may remain unconnected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    |

| RTC_XTALI/RTC_XTALO       | If the user wishes to configure RTC_XTALI and RTC_XTALO as an RTC oscillator, a 32.768 kHz crystal, ( $\leq$ 100 k $\Omega$ ESR, 10 pF load) should be connected between RTC_XTALI and RTC_XTALO. Keep in mind the capacitors implemented on either side of the crystal are about twice the crystal load capacitor. To hit the exact oscillation frequency, the board capacitors need to be reduced to account for board and chip parasitics. The integrated oscillation amplifier is self biasing, but relatively weak. Care must be taken to limit parasitic leakage from RTC_XTALI and RTC_XTALO to either power or ground (>100 M $\Omega$ ). This will debias the amplifier and cause a reduction of startup margin. Typically RTC_XTALI and RTC_XTALO should bias to approximately 0.5 V. If it is desired to feed an external low frequency clock into RTC_XTALI, the RTC_XTALO pin must remain unconnected or driven with a complimentary signal. The logic level of this forcing clock should not exceed VDD_SNVS_CAP level and the frequency should be <100 kHz under typical conditions. In case when high accuracy real time clock are not required system may use internal low frequency ring oscillator. It is recommended to connect RTC_XTALI to GND and keep RTC_XTALO unconnected. |

| XTALI/XTALO               | A 24.0 MHz crystal should be connected between XTALI and XTALO.<br>The crystal must be rated for a maximum drive level of 250 $\mu$ W. An ESR (equivalent series resistance) of typical 80 $\Omega$ is recommended. NXP BSP (board support package) software requires 24 MHz on XTALI/XTALO.<br>The crystal can be eliminated if an external 24 MHz oscillator is available in the system. In this case, XTALO must be directly driven by the external oscillator and XTALI is mounted with 18 pF capacitor. Please refer to the EVK board reference design for details. The logic level of this forcing clock cannot exceed NVCC_PLL level.<br>If this clock is used as a reference for USB, then there are strict frequency tolerance and jitter requirements. See OSC24M chapter and relevant interface specifications chapters for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Table 4. Special Signal Considerations

| Rating                     | Test Conditions    | Symbol              | Value | Unit | Notes |

|----------------------------|--------------------|---------------------|-------|------|-------|

| Junction to Board          | —                  | $R_{	hetaJB}$       | 21.8  | °C/W | 5     |

| Junction to Case           | _                  | $R_{	ext{	heta}JC}$ | 19.3  | °C/W | 6     |

| Junction to Package Top    | Natural Convection | $\Psi_{JT}$         | 2.3   | °C/W | 7     |

| Junction to Package Bottom | Natural Convection | $\Psi_{JB}$         | 12.0  | °C/W | 8     |

## Table 9. 14x14 MM (VM) Thermal Resistance Data<sup>1</sup>

<sup>1</sup> As per JEDEC JESD51-2 the intent of (thermal resistance) measurement is solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to and will not predict the performance of a package in an application-specific environment.

<sup>2</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>3</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

<sup>4</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>5</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>6</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

<sup>7</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

<sup>8</sup> Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB

# 4.1.3 Operating ranges

Table 10 provides the operating ranges of the i.MX 6UltraLite processors. For details on the chip's power structure, see the "Power Management Unit (PMU)" chapter of the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

# 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 10 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. LDO\_2P5 supplies the DDR IOs, USB Phy, E-fuse module, and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \ \Omega$

For information on external capacitor requirements for this regulator, see the *Hardware Development Guide for i.MX 6UltraLite Applications Processors* (IMX6ULHDG).

For additional information, see the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

# 4.3.2.3 LDO\_USB

The LDO\_USB module implements a programmable linear-regulator function from the USB VUSB voltages (4.4 V–5.5 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either USB VBUS supply, when both are present. If only one of the USB VBUS voltages is present, then, the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for *i.MX 6UltraLite Applications Processors* (IMX6ULHDG).

For additional information, see the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

# 4.4 PLL's electrical characteristics

# 4.4.1 Audio/Video PLL's electrical parameters

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 650 MHz ~1.3 GHz        |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

## Table 16. Audio/Video PLL's Electrical Parameters

# 4.5 On-Chip oscillators

# 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implement an oscillator. The oscillator is powered from NVCC\_PLL.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implement a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDD\_HIGH\_IN such as the oscillator consumes power from VDD\_HIGH\_IN when that supply is available and transitions to the backup battery when VDD\_HIGH\_IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 K will automatically switch to a crude internal ring oscillator. The frequency range of this block is approximately 10–45 kHz. It highly depends on the process, voltage, and temperature.

The OSC32k runs from VDD\_SNVS\_CAP supply, which comes from the

VDD\_HIGH\_IN/VDD\_SNVS\_IN. The target battery is a ~3 V coin cell. Proper choice of coin cell type is necessary for chosen VDD\_HIGH\_IN range. Appropriate series resistor (Rs) must be used when connecting the coin cell. Rs depends on the charge current limit that depends on the chosen coin cell. For example, for Panasonic ML621:

- Average Discharge Voltage is 2.5 V

- Maximum Charge Current is 0.6 mA

For a charge voltage of 3.2 V, Rs = (3.2-2.5)/0.6 m = 1.17 k.

|                     | Min | Тур        | Max | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|-----|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fosc                | —   | 32.768 KHz |     | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                                                                                                             |

| Current consumption |     | 4 μΑ       |     | The 4 $\mu$ A is the consumption of the oscillator alone (OSC32k). Total supply consumption will depend on what the digital portion of the RTC consumes. The ring oscillator consumes 1 $\mu$ A when ring oscillator is inactive, 20 $\mu$ A when the ring oscillator is running. Another 1.5 $\mu$ A is drawn from vdd_rtc in the power_detect block. So, the total current is 6.5 $\mu$ A on vdd_rtc when the ring oscillator is not running. |

| Bias resistor       |     | 14 MΩ      |     | This integrated bias resistor sets the amplifier into a high gain state. Any leakage through the ESD network, external board leakage, or even a scope probe that is significant relative to this value will debias the amp. The debiasing will result in low gain, and will impact the circuit's ability to start up and maintain oscillations.                                                                                                 |

Table 21. OSC32K Main Characteristics

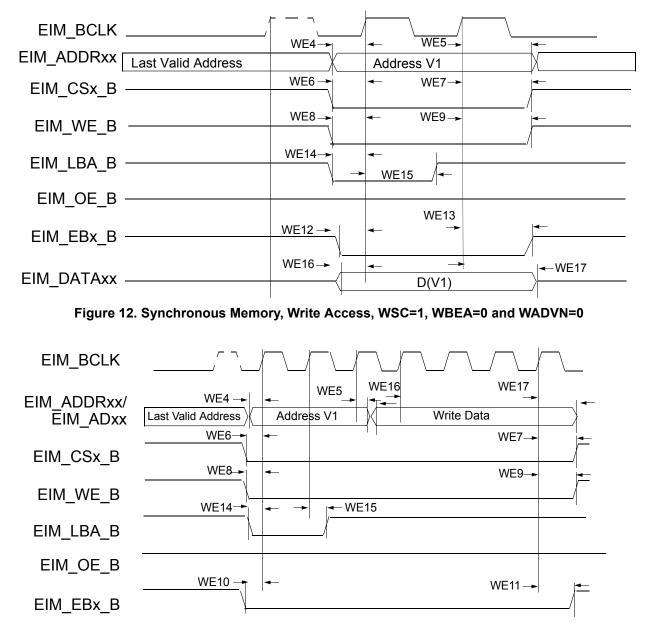

Figure 13. Muxed Address/Data (A/D) Mode, Synchronous Write Access, WSC=6, ADVA=0, ADVN=1, and ADH=1

## NOTE

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

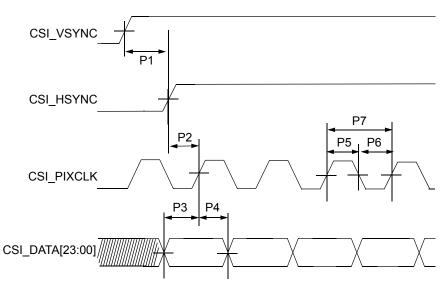

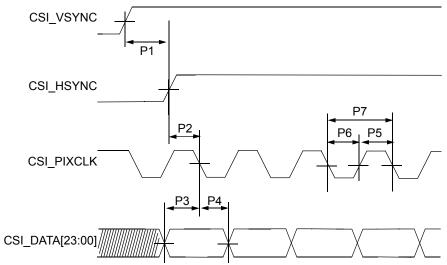

(VSYNC), then CSI\_HSYNC (HSYNC) is asserted and holds for the entire line. The pixel clock, CSI\_PIXCLK (PIXCLK), is valid as long as HSYNC is asserted.

Figure 32. CSI Gated Clock Mode—Sensor Data at Falling Edge, Latch Data at Rising Edge

Figure 33. CSI Gated Clock Mode—Sensor Data at Rising Edge, Latch Data at Falling Edge

| ID | Parameter                   | Symbol | Min. | Max. | Units |

|----|-----------------------------|--------|------|------|-------|

| P1 | CSI_VSYNC to CSI_HSYNC time | tV2H   | 33.5 | _    | ns    |

| P2 | CSI_HSYNC setup time        | tHsu   | 1    | —    | ns    |

| P3 | CSI DATA setup time         | tDsu   | 1    | _    | ns    |

The following subsections describe the CSI timing in gated and ungated clock modes.

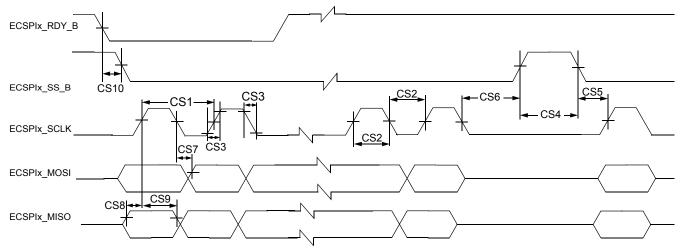

# 4.12.2 ECSPI timing parameters

This section describes the timing parameters of the ECSPI blocks. The ECSPI have separate timing parameters for master and slave modes.

# 4.12.2.1 ECSPI master mode timing

Figure 35 depicts the timing of ECSPI in master mode. Table 46 lists the ECSPI master mode timing characteristics.

Figure 35. ECSPI Master Mode Timing Diagram

| ID   | Parameter                                                               | Symbol                 | Min                         | Мах | Unit |

|------|-------------------------------------------------------------------------|------------------------|-----------------------------|-----|------|

| CS1  | ECSPIx_SCLK Cycle Time-Read<br>ECSPIx_SCLK Cycle Time-Write             | t <sub>clk</sub>       | 43<br>15                    | _   | ns   |

| CS2  | ECSPIx_SCLK High or Low Time-Read<br>ECSPIx_SCLK High or Low Time-Write | t <sub>SW</sub>        | 21.5<br>7                   | —   | ns   |

| CS3  | ECSPIx_SCLK Rise or Fall <sup>1</sup>                                   | t <sub>RISE/FALL</sub> | —                           | —   | ns   |

| CS4  | ECSPIx_SS_B pulse width                                                 | t <sub>CSLH</sub>      | Half ECSPIx_SCLK period     | —   | ns   |

| CS5  | ECSPIx_SS_B Lead Time (CS setup time)                                   | t <sub>SCS</sub>       | Half ECSPIx_SCLK period - 4 | —   | ns   |

| CS6  | ECSPIx_SS_B Lag Time (CS hold time)                                     | t <sub>HCS</sub>       | Half ECSPIx_SCLK period - 2 | —   | ns   |

| CS7  | ECSPIx_MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF)               | t <sub>PDmosi</sub>    | -1                          | 1   | ns   |

| CS8  | ECSPIx_MISO Setup Time                                                  | t <sub>Smiso</sub>     | 14                          | —   | ns   |

| CS9  | ECSPIx_MISO Hold Time                                                   | t <sub>Hmiso</sub>     | 0                           | —   | ns   |

| CS10 | RDY to ECSPIx_SS_B Time <sup>2</sup>                                    | t <sub>SDRY</sub>      | 5                           | —   | ns   |

| Table 46 | ECSPI | Master | Mode | Timing | Parameters |

|----------|-------|--------|------|--------|------------|

|----------|-------|--------|------|--------|------------|

<sup>1</sup> See specific I/O AC parameters Section 4.7, "I/O AC parameters"."

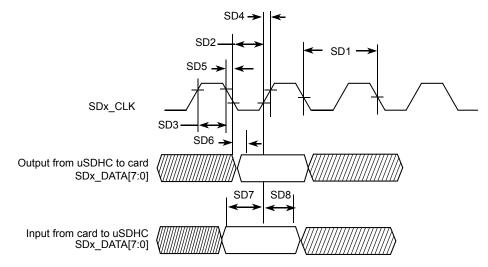

# 4.12.3 Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC timing

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing, eMMC4.4/4.41/4.5 (Dual Date Rate) timing and SDR104/50(SD3.0) timing.

# 4.12.3.1 SD/eMMC4.3 (single data rate) AC timing

Figure 37 depicts the timing of SD/eMMC4.3, and Table 48 lists the SD/eMMC4.3 timing characteristics.

Figure 37. SD/eMMC4.3 Timing

| Table 48. | SD/eMMC4.3 | 8 Interface | Timing | Specification |

|-----------|------------|-------------|--------|---------------|

|-----------|------------|-------------|--------|---------------|

| ID  | Parameter                                                     | Symbols                      | Min  | Мах   | Unit |  |  |

|-----|---------------------------------------------------------------|------------------------------|------|-------|------|--|--|

|     | Card Input Clock                                              | (                            |      |       |      |  |  |

| SD1 | Clock Frequency (Low Speed)                                   | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |  |  |

|     | Clock Frequency (SD/SDIO Full Speed/High Speed)               | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |  |  |

|     | Clock Frequency (MMC Full Speed/High Speed)                   | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |  |  |

|     | Clock Frequency (Identification Mode)                         | f <sub>OD</sub>              | 100  | 400   | kHz  |  |  |

| SD2 | Clock Low Time                                                | t <sub>WL</sub>              | 7    | —     | ns   |  |  |

| SD3 | Clock High Time                                               | t <sub>WH</sub>              | 7    | —     | ns   |  |  |

| SD4 | Clock Rise Time                                               | t <sub>TLH</sub>             | —    | 3     | ns   |  |  |

| SD5 | Clock Fall Time                                               | t <sub>THL</sub>             | —    | 3     | ns   |  |  |

|     | uSDHC Output/Card Inputs SD_CMD, SDx_DATAx (Reference to CLK) |                              |      |       |      |  |  |

| SD6 | uSDHC Output Delay                                            | t <sub>OD</sub>              | -6.6 | 3.6   | ns   |  |  |

| ID | Parameter                                                           | Symbol         | Min | Max | Unit |

|----|---------------------------------------------------------------------|----------------|-----|-----|------|

| L1 | LCD pixel clock frequency                                           | tCLK(LCD)      |     | 150 | MHz  |

| L2 | LCD pixel clock high (falling edge capture)                         | tCLKH(LCD)     | 3   | —   | ns   |

| L3 | LCD pixel clock low (rising edge capture)                           | tCLKL(LCD)     | 3   | —   | ns   |

| L4 | LCD pixel clock high to data valid (falling edge capture)           | td(CLKH-DV)    | -1  | 1   | ns   |

| L5 | LCD pixel clock low to data valid (rising edge capture)             | td(CLKL-DV)    | -1  | 1   | ns   |

| L6 | LCD pixel clock high to control signal valid (falling edge capture) | td(CLKH-CTRLV) | -1  | 1   | ns   |

| L7 | LCD pixel clock low to control signal valid (rising edge capture)   | td(CLKL-CTRLV) | -1  | 1   | ns   |

## Table 59. LCD Timing Parameters

# 4.12.8.1 LCDIF signal mapping

Table 60 lists the details about the mapping signals.

| Pin name                      | 8-bit DOTCLK LCD<br>IF | 16-bit DOTCLK LCD<br>IF | 18-bit DOTCLK LCD<br>IF | 24-bit DOTCLK LCD<br>IF | 8-bit DVI LCD<br>IF |

|-------------------------------|------------------------|-------------------------|-------------------------|-------------------------|---------------------|

| LCD_RS                        | —                      |                         | —                       | —                       | CCIR_CLK            |

| LCD_VSYNC*<br>(Two options)   | LCD_VSYNC              | LCD_VSYNC               | LCD_VSYNC               | LCD_VSYNC               | —                   |

| LCD_HSYNC                     | LCD_HSYNC              | LCD_HSYNC               | LCD_HSYNC               | LCD_HSYNC               | —                   |

| LCD_DOTCLK                    | LCD_DOTCLK             | LCD_DOTCLK              | LCD_DOTCLK              | LCD_DOTCLK              | —                   |

| LCD_ENABLE                    | LCD_ENABLE             | LCD_ENABLE              | LCD_ENABLE              | LCD_ENABLE              | —                   |

| LCD_D23                       | —                      | _                       | _                       | R[7]                    | —                   |

| LCD_D22                       | —                      | _                       | —                       | R[6]                    | —                   |

| LCD_D21                       | —                      | _                       | —                       | R[5]                    | —                   |

| LCD_D20                       | —                      | _                       | —                       | R[4]                    | —                   |

| LCD_D19                       | _                      | _                       | —                       | R[3]                    | —                   |

| LCD_D18                       | _                      | _                       | —                       | R[2]                    | —                   |

| LCD_D17                       | —                      | _                       | R[5]                    | R[1]                    | —                   |

| LCD_D16                       | —                      | _                       | R[4]                    | R[0]                    | —                   |

| LCD_D15 /<br>VSYNC*           | _                      | R[4]                    | R[3]                    | G[7]                    | —                   |

| LCD_D14 /<br>HSYNC**          | —                      | R[3]                    | R[2]                    | G[6]                    | —                   |

| LCD_D13 /<br>LCD_DOTCLK<br>** | —                      | R21]                    | R[1]                    | G[5]                    | —                   |

## Table 60. LCD Signal Parameters

|                         |                                        |                                     |                                        | r                                      | 1      |

|-------------------------|----------------------------------------|-------------------------------------|----------------------------------------|----------------------------------------|--------|

| LCD_D12 /<br>ENABLE**   | _                                      | R[1]                                | R[0]                                   | G[4]                                   | —      |

| LCD_D11                 | —                                      | R[0]                                | G[5]                                   | G[3]                                   | —      |

| LCD_D10                 | —                                      | G[5]                                | G[4]                                   | G[2]                                   | —      |

| LCD_D9                  | _                                      | G[4]                                | G[3]                                   | G[1]                                   | —      |

| LCD_D8                  | _                                      | G[3]                                | G[2]                                   | G[0]                                   | —      |

| LCD_D8                  | _                                      | G[3]                                | G[2]                                   | G[0]                                   | —      |

| LCD_D7                  | R[2]                                   | G[2]                                | G[1]                                   | B[7]                                   | Y/C[7] |

| LCD_D6                  | R[1]                                   | G[1]                                | G[0]                                   | B[6]                                   | Y/C[6] |

| LCD_D5                  | R[0]                                   | G[0]                                | B[5]                                   | B[5]                                   | Y/C[5] |

| LCD_D4                  | G[2]                                   | B[4]                                | B[4]                                   | B[4]                                   | Y/C[4] |

| LCD_D3                  | G[1]                                   | B[3]                                | B[3]                                   | B[3]                                   | Y/C[3] |

| LCD_D2                  | G[0]                                   | B[2]                                | B[2]                                   | B[2]                                   | Y/C[2] |

| LCD_D1                  | B[1]                                   | B[1]                                | B[1]                                   | B[1]                                   | Y/C[1] |

| LCD_D0                  | B[0]                                   | B[0]                                | B[0]                                   | B[0]                                   | Y/C[0] |

| LCD_RESET               | LCD_RESET                              | LCD_RESET                           | LCD_RESET                              | LCD_RESET                              | —      |

| LCD_BUSY /<br>LCD_VSYNC | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | LCD_BUSY (or<br>optional LCD_VSYNC) | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | —      |

## Table 60. LCD Signal Parameters (continued)

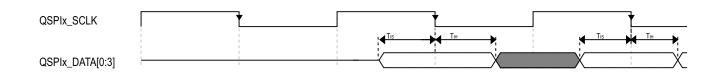

# 4.12.9 QUAD SPI (QSPI) timing parameters

Measurement conditions are with 35 pF load on SCK and SIO pins and input slew rate of 1 V/ns.

# 4.12.9.1 SDR mode

Figure 49. QuadSPI Input/Read Timing (SDR mode with internal sampling)

| Symbol           | Parameter                     | Val | ue  | Unit         |

|------------------|-------------------------------|-----|-----|--------------|

| Cymbol           | i arameter                    | Min | Мах | Onit         |

| T <sub>CSS</sub> | Chip select output setup time | 3   | _   | SCK cycle(s) |

| T <sub>CSH</sub> | Chip select output hold time  | 3   | _   | SCK cycle(s) |

#### Table 66. QuadSPI Output/Write Timing (DDR mode)

## NOTE

$T_{css}$  and  $T_{csh}$  are configured by the QuadSPIx\_FLSHCR register, the default value of 3 are shown on the timing. Please refer to the *i.MX 6UltraLite Reference Manual (IMX6ULRM)* for more details.

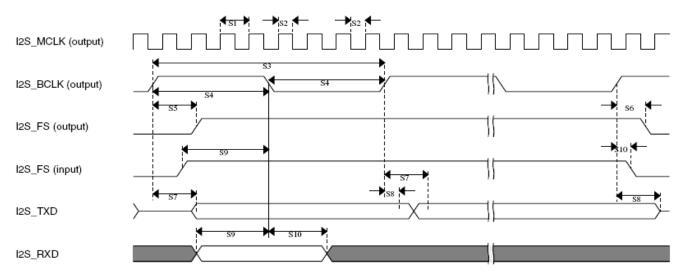

# 4.12.10 SAI/I2S switching specifications

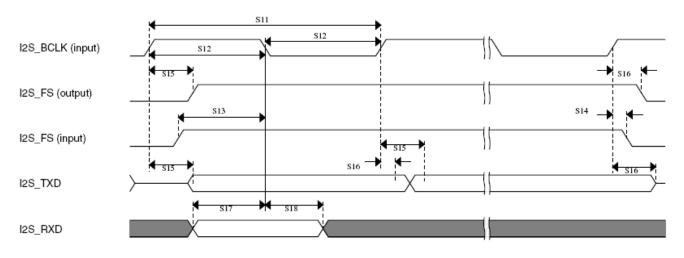

This section provides the AC timings for the SAI in master (clocks driven) and slave (clocks input) modes. All timings are given for non-inverted serial clock polarity (SAI\_TCR[TSCKP] = 0, SAI\_RCR[RSCKP] = 0) and non-inverted frame sync (SAI\_TCR[TFSI] = 0, SAI\_RCR[RFSI] = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timings remain valid by inverting the clock signal (SAI\_BCLK) and/or the frame sync (SAI\_FS) shown in the figures below.

| Num | Characteristic                             | Min                  | Мах | Unit        |

|-----|--------------------------------------------|----------------------|-----|-------------|

| S1  | SAI_MCLK cycle time                        | 2 x t <sub>sys</sub> | —   | ns          |

| S2  | SAI_MCLK pulse width high/low              | 40%                  | 60% | MCLK period |

| S3  | SAI_BCLK cycle time                        | 4 x t <sub>sys</sub> | —   | ns          |

| S4  | SAI_BCLK pulse width high/low              | 40%                  | 60% | BCLK period |

| S5  | SAI_BCLK to SAI_FS output valid            | —                    | 15  | ns          |

| S6  | SAI_BCLK to SAI_FS output invalid          | 0                    | _   | ns          |

| S7  | SAI_BCLK to SAI_TXD valid                  | —                    | 15  | ns          |

| S8  | SAI_BCLK to SAI_TXD invalid                | 0                    | _   | ns          |

| S9  | SAI_RXD/SAI_FS input setup before SAI_BCLK | 15                   | —   | ns          |

| S10 | SAI_RXD/SAI_FS input hold after SAI_BCLK   | 0                    | —   | ns          |

| Table 67. Master | Mode SAI Timing |

|------------------|-----------------|

|------------------|-----------------|

## Figure 55. SAI Timing — Master Modes

| Num | Characteristic                            | Min                  | Max | Unit        |

|-----|-------------------------------------------|----------------------|-----|-------------|

| S11 | SAI_BCLK cycle time (input)               | 4 x t <sub>sys</sub> | _   | ns          |

| S12 | SAI_BCLK pulse width high/low (input)     | 40%                  | 60% | BCLK period |

| S13 | SAI_FS input setup before SAI_BCLK        | 10                   | _   | ns          |

| S14 | SAI_FA input hold after SAI_BCLK          | 2                    | —   | ns          |

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | —                    | 20  | ns          |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0                    | _   | ns          |

| S17 | SAI_RXD setup before SAI_BCLK             | 10                   | —   | ns          |

| S18 | SAI_RXD hold after SAI_BCLK               | 2                    | —   | ns          |

## Figure 56. SAI Timing — Slave Modes

| ID   | Parameter <sup>1,2</sup>                | All Freq | Unit |      |  |

|------|-----------------------------------------|----------|------|------|--|

|      | Falameter /                             | Min Max  |      | onit |  |

| SJ9  | JTAG_TMS, JTAG_TDI data hold time       | 25       | _    | ns   |  |

| SJ10 | JTAG_TCK low to JTAG_TDO data valid     | —        | 44   | ns   |  |

| SJ11 | JTAG_TCK low to JTAG_TDO high impedance | —        | 44   | ns   |  |

| SJ12 | JTAG_TRST_B assert time                 | 100      | —    | ns   |  |

| SJ13 | JTAG_TRST_B set-up time to JTAG_TCK low | 40       | _    | ns   |  |

## Table 69. JTAG Timing (continued)

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

# 4.12.12 SPDIF timing parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 70 and Figure 61 and Figure 62 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SPDIF\_SR\_CLK) for SPDIF in Rx mode and the timing of the modulating Tx clock (SPDIF\_ST\_CLK) for SPDIF in Tx mode.

| Characteristics                                                                                                     | Symbol   | Timing Para | meter Range         | Unit |

|---------------------------------------------------------------------------------------------------------------------|----------|-------------|---------------------|------|

| Characteristics                                                                                                     | Symbol - | Min         | Max                 |      |

| SPDIF_IN Skew: asynchronous inputs, no specs apply                                                                  | —        | —           | 0.7                 | ns   |

| SPDIF_OUT output (Load = 50pf) <ul> <li>Skew</li> <li>Transition rising</li> <li>Transition falling</li> </ul>      |          | _<br>_<br>_ | 1.5<br>24.2<br>31.3 | ns   |

| <ul><li>SPDIF_OUT1 output (Load = 30pf)</li><li>Skew</li><li>Transition rising</li><li>Transition falling</li></ul> | <br>     |             | 1.5<br>13.6<br>18.0 | ns   |

| Modulating Rx clock (SPDIF_SR_CLK) period                                                                           | srckp    | 40.0        | _                   | ns   |

| SPDIF_SR_CLK high period                                                                                            | srckph   | 16.0        | _                   | ns   |

| SPDIF_SR_CLK low period                                                                                             | srckpl   | 16.0        | _                   | ns   |

| Modulating Tx clock (SPDIF_ST_CLK) period                                                                           | stclkp   | 40.0        |                     | ns   |

| SPDIF_ST_CLK high period                                                                                            | stclkph  | 16.0        | —                   | ns   |

| SPDIF_ST_CLK low period                                                                                             | stclkpl  | 16.0        |                     | ns   |

Table 70. SPDIF Timing Parameters

| Characteristic    | Conditions <sup>1</sup> | Symb  | Min | Typ <sup>2</sup> | Max | Unit   | Comment |

|-------------------|-------------------------|-------|-----|------------------|-----|--------|---------|

| Sample Cycles     | ADLSMP=0,<br>ADSTS=00   | Csamp | _   | 2                | _   | cycles | _       |

|                   | ADLSMP=0,<br>ADSTS=01   | -     |     | 4                | -   |        |         |

|                   | ADLSMP=0,<br>ADSTS=10   |       |     | 6                |     |        |         |

|                   | ADLSMP=0,<br>ADSTS=11   |       |     | 8                |     |        |         |

|                   | ADLSMP=1,<br>ADSTS=00   |       |     | 12               |     |        |         |

|                   | ADLSMP=1,<br>ADSTS=01   |       |     | 16               |     |        |         |

|                   | ADLSMP=1,<br>ADSTS=10   |       |     | 20               |     |        |         |

|                   | ADLSMP=1,<br>ADSTS=11   |       |     | 24               |     |        |         |

| Conversion Cycles | ADLSMP=0<br>ADSTS=00    | Cconv | —   | 28               | —   | cycles | —       |

|                   | ADLSMP=0<br>ADSTS=01    |       |     | 30               |     |        |         |

|                   | ADLSMP=0<br>ADSTS=10    |       |     | 32               |     |        |         |

|                   | ADLSMP=0<br>ADSTS=11    |       |     | 34               |     |        |         |

|                   | ADLSMP=1<br>ADSTS=00    |       |     | 38               |     |        |         |

|                   | ADLSMP=1<br>ADSTS=01    |       |     | 42               |     |        |         |

|                   | ADLSMP=1<br>ADSTS=10    |       |     | 46               | ]   |        |         |

|                   | ADLSMP=1,<br>ADSTS=11   |       |     | 50               |     |        |         |

Table 76. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ ) (continued)

#### Boot mode configuration

## Table 80. SPI Boot through ECSPI2 (continued)

| LCD_VSYNC | ecspi2.SS2 | Alt 8 |  | Yes |     |

|-----------|------------|-------|--|-----|-----|

| LCD_RESET | ecspi2.SS3 | Alt 8 |  |     | Yes |

## Table 81. SPI Boot through ECSPI3

| Ball Name     | Signal Name | Mux<br>Mode | Common | BOOT_CFG4<br>[5:4]=00b | BOOT_CFG4[<br>5:4]=01b | BOOT_CFG4[<br>5:4]=10b | BOOT_CFG4<br>[5:4]=11b |

|---------------|-------------|-------------|--------|------------------------|------------------------|------------------------|------------------------|

| UART2_RTS_B   | ecspi3.MISO | Alt 8       | Yes    |                        |                        |                        |                        |

| UART2_CTS_B   | ecspi3.MOSI | Alt 8       | Yes    |                        |                        |                        |                        |

| UART2_RX_DATA | ecspi3.SCLK | Alt 8       | Yes    |                        |                        |                        |                        |

| UART2_TX_DATA | ecspi3.SS0  | Alt 8       |        | Yes                    |                        |                        |                        |

| NAND_ALE      | ecspi3.SS1  | Alt 8       |        |                        | Yes                    |                        |                        |

| NAND_RE_B     | ecspi3.SS2  | Alt 8       |        |                        |                        | Yes                    |                        |

| NAND_WE_B     | ecspi3.SS3  | Alt 8       |        |                        |                        |                        | Yes                    |

## Table 82. SPI Boot through ECSPI4

| Ball Name      | Signal Name | Mux<br>Mode | Common | BOOT_CFG4<br>[5:4]=00b | BOOT_CFG4<br>[5:4]=01b | BOOT_CFG4[<br>5:4]=10b | BOOT_CFG<br>4[5:4]=11b |

|----------------|-------------|-------------|--------|------------------------|------------------------|------------------------|------------------------|

| ENET2_TX_CLK   | ecspi4.MISO | Alt 3       | Yes    |                        |                        |                        |                        |

| ENET2_TX_EN    | ecspi4.MOSI | Alt 3       | Yes    |                        |                        |                        |                        |

| ENET2_TX_DATA1 | ecspi4.SCLK | Alt 3       | Yes    |                        |                        |                        |                        |

| ENET2_RX_ER    | ecspi4.SS0  | Alt 3       |        | Yes                    |                        |                        |                        |

| NAND_DATA01    | ecspi4.SS1  | Alt 8       |        |                        | Yes                    |                        |                        |

| NAND_DATA02    | ecspi4.SS2  | Alt 8       |        |                        |                        | Yes                    |                        |

| NAND_DATA03    | ecspi4.SS3  | Alt 8       |        |                        |                        |                        | Yes                    |

## Table 83. NAND Boot through GPMI

| Ball Name    | Signal Name     | Mux Mode | Common | BOOT_CFG1[3:2]=<br>01b | BOOT_CFG1[3:2]=<br>10b |

|--------------|-----------------|----------|--------|------------------------|------------------------|

| NAND_CLE     | rawnand.CLE     | Alt 0    | Yes    |                        |                        |

| NAND_ALE     | rawnand.ALE     | Alt 0    | Yes    |                        |                        |

| NAND_WP_B    | rawnand.WP_B    | Alt 0    | Yes    |                        |                        |

| NAND_READY_B | rawnand.READY_B | Alt 0    | Yes    |                        |                        |

| NAND_CE0_B   | rawnand.CE0_B   | Alt 0    | Yes    |                        |                        |

| NAND_CE1_B   | rawnand.CE1_B   | Alt 0    |        | Yes                    | Yes                    |

| NAND_RE_B    | rawnand.RE_B    | Alt 0    | Yes    |                        |                        |

| NAND_WE_B    | rawnand.WE_B    | Alt 0    | Yes    |                        |                        |

## Package information and contact assignments

|             |    |           |     | act Assig | giments (continued) |        |                   |

|-------------|----|-----------|-----|-----------|---------------------|--------|-------------------|

| DRAM_ADDR07 | H4 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR07         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR08 | J4 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR08         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR09 | L2 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR09         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR10 | M4 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR10         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR11 | K3 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR11         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR12 | L4 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR12         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR13 | H3 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR13         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR14 | G1 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR14         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR15 | K5 | NVCC_DRAM | DDR | ALT0      | DRAM_ADDR15         | Output | 100 kΩ<br>pull-up |

| DRAM_CAS_B  | J2 | NVCC_DRAM | DDR | ALT0      | DRAM_CAS_B          | Output | 100 kΩ<br>pull-up |

| DRAM_CS0_B  | N2 | NVCC_DRAM | DDR | ALT0      | DRAM_CS0_B          | Output | 100 kΩ<br>pull-up |

| DRAM_CS1_B  | H5 | NVCC_DRAM | DDR | ALT0      | DRAM_CS1_B          | Output | 100 kΩ<br>pull-up |

| DRAM_DATA00 | T4 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA00         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA01 | U6 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA01         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA02 | Т6 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA02         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA03 | U7 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA03         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA04 | U8 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA04         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA05 | T8 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA05         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA06 | T5 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA06         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA07 | U4 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA07         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA08 | U2 | NVCC_DRAM | DDR | ALT0      | DRAM_DATA08         | Input  | 100 kΩ<br>pull-up |

Table 90. 14x14 mm Functional Contact Assignments (continued)

| z             | Σ           | _            | ¥             | 7                                                       | т                           | υ             |

|---------------|-------------|--------------|---------------|---------------------------------------------------------|-----------------------------|---------------|

| DRAM_ODT0     | DRAM_SDBA0  | DRAM_ADDR05  | DRAM_ADDR02   | DRAM_SDWE_B                                             | DRAM_SDBA1                  | DRAM_ADDR14   |

| DRAM_CS0_B    | DRAM_ADDR03 | DRAM_ADDR09  | DRAM_SDBA2    | DRAM_CAS_B                                              | DRAM_ADDR01                 | DRAM_ADDR06   |

| VSS           | DRAM_SDCKE0 | VSS          | DRAM_ADDR11   | DRAM_SDCKE1                                             | DRAM_ADDR13                 | VSS           |

| DRAM_ZQPAD    | DRAM_ADDR10 | DRAM_ADDR12  | DRAM_ADDR04   | DRAM_ADDR08                                             | DRAM_ADDR07                 | DRAM_RESET    |

| VSS           | DRAM_RAS_B  | DRAM_ADDR00  | DRAM_ADDR15   | NSS                                                     | DRAM_CS1_B                  | VSS           |

| NVCC_DRAM_2P5 | NVCC_DRAM   | NVCC_DRAM    | NVCC_DRAM     | NVCC_DRAM                                               | NVCC_DRAM                   | NVCC_DRAM     |

| TEST_MODE     | VSS         | VSS          | VSS           | NSS                                                     | NSS                         | VSS           |

| SNVS_TAMPER5  | VSS         | VDD_SOC_CAP  | VDD_SOC_CAP   | VDD_SOC_CAP                                             | VDD_SOC_CAP                 | VDD_SOC_CAP   |

| SNVS_TAMPER8  | VSS         | VDD_SOC_CAP  | VDD_SOC_IN    | VDD_SOC_IN                                              | VDD_SOC_IN                  | VDD_ARM_CAP   |

| SNVS_TAMPER7  | VSS         | VDD_SOC_CAP  | VDD_SOC_IN    | VDD_SOC_IN                                              | VDD_SOC_IN                  | VDD_ARM_CAP   |

| SNVS_TAMPER6  | VSS         | VDD_SOC_CAP  | VDD_SOC_CAP   | VDD_SOC_CAP                                             | VDD_ARM_CAP                 | VDD_ARM_CAP   |

| VDD_SNVS_CAP  | NGND_KEL0   | VSS          | VSS           | NSS                                                     | VSS                         | VSS           |

| VDD_HIGH_IN   | ADC_VREFH   | VDDA_ADC_3P3 | GPI01_1000    | NVCC_GPIO                                               | NVCC_UART                   | UART5_RX_DATA |

| JTAG_TRST_B   | JTAG_TCK    | GPI01_I002   | UART1_TX_DATA | UART1_RTS_B                                             | UART2_RTS_B                 | UART3_RTS_B   |

| JTAG_TDO      | GPI01_I009  | GPI01_I001   | UART1_CTS_B   | UART2_CTS_B                                             | UART3_CTS_B                 | VSS           |

| JTAG_TDI      | GPI01_I004  | GPI01_I007   | UART1_RX_DATA | UART1_RX_DATA UART2_RX_DATA UART3_RX_DATA UART4_RX_DATA | UART3_RX_DATA               | UART4_RX_DATA |

| GPI01_1008    | GPI01_1005  | GPI01_1003   | GPI01_1006    | UART2_TX_DATA                                           | UART2_TX_DATA UART3_TX_DATA | UART4_TX_DATA |

| z             | Σ           | _            | ¥             | 7                                                       | т                           | U             |

Package information and contact assignments