#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8SX                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI, SmartCard                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 74                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b, 6x16b; D/A 2x8b                                                      |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f61622n50fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

| Sectio | on 23 C   | Clock Pulse Generator                                                   | 869 |

|--------|-----------|-------------------------------------------------------------------------|-----|

| 23.1   | Register  | Description                                                             | 871 |

|        | 23.1.1    | System Clock Control Register (SCKCR)                                   | 871 |

|        | 23.1.2    | $\Delta\Sigma$ A/D Mode Register (DSADMR)                               | 874 |

| 23.2   | Oscillato | r                                                                       | 875 |

|        | 23.2.1    | Connecting Crystal Resonator                                            | 875 |

|        | 23.2.2    | External Clock Input                                                    | 876 |

| 23.3   | PLL Circ  | zuit                                                                    | 877 |

| 23.4   | Frequenc  | y Divider                                                               | 877 |

|        | 23.4.1    | 1φ, Bφ, Pφ Frequency Dividers                                           | 877 |

|        | 23.4.2    | A                                                                       | 877 |

| 23.5   | Usage No  | otes                                                                    | 878 |

|        | 23.5.1    | Notes on Clock Pulse Generator                                          | 878 |

|        | 23.5.2    | Notes on Resonator                                                      | 879 |

|        | 23.5.3    | Notes on Board Design                                                   | 879 |

|        |           |                                                                         |     |

| Sectio | on 24 P   | ower-Down Modes                                                         | 881 |

| 24.1   | Features  |                                                                         | 881 |

| 24.2   | Register  | Descriptions                                                            | 884 |

|        | 24.2.1    | Standby Control Register (SBYCR)                                        | 884 |

|        | 24.2.2    | Module Stop Control Registers A and B (MSTPCRA and MSTPCRB)             | 887 |

|        | 24.2.3    | Module Stop Control Register C (MSTPCRC)                                | 890 |

|        | 24.2.4    | Deep Standby Control Register (DPSBYCR)                                 | 891 |

|        | 24.2.5    | Deep Standby Wait Control Register (DPSWCR)                             | 894 |

|        | 24.2.6    | Deep Standby Interrupt Enable Register (DPSIER)                         | 896 |

|        | 24.2.7    | Deep Standby Interrupt Flag Register (DPSIFR)                           | 897 |

|        | 24.2.8    | Deep Standby Interrupt Edge Register (DPSIEGR)                          | 899 |

|        | 24.2.9    | Reset Status Register (RSTSR)                                           | 900 |

|        | 24.2.10   | Deep Standby Backup Register (DPSBKRn)                                  | 901 |

| 24.3   | Multi-Cl  | ock Function                                                            | 901 |

| 24.4   | Module S  | Stop State                                                              | 901 |

| 24.5   | Sleep Mo  | ode                                                                     | 902 |

|        | 24.5.1    | Entry to Sleep Mode                                                     | 902 |

|        | 24.5.2    | Exit from Sleep Mode                                                    | 902 |

| 24.6   | All-Mod   | ule-Clock-Stop Mode                                                     | 903 |

| 24.7   | Software  | Standby Mode                                                            | 904 |

|        | 24.7.1    | Entry to Software Standby Mode                                          | 904 |

|        | 24.7.2    | Exit from Software Standby Mode                                         | 904 |

|        | 24.7.3    | Setting Oscillation Settling Time after Exit from Software Standby Mode | 905 |

|        | 24.7.4    | Software Standby Mode Application Example                               | 907 |

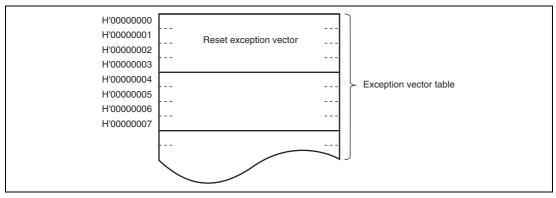

Figure 2.6 Exception Vector Table (Maximum Modes)

The memory indirect (@@aa:8) and extended memory indirect (@@vec:7) addressing modes are used in the JMP and JSR instructions. An 8-bit absolute address included in the instruction code specifies a memory location. Execution branches to the contents of the memory location. In maximum mode, an operand is a 32-bit (longword) operand, providing a 32-bit branch address.

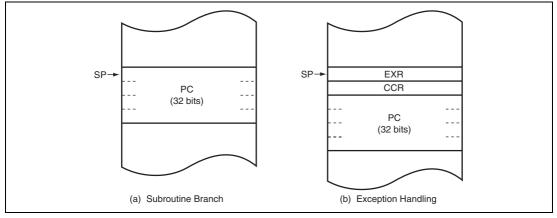

Stack Structure

The stack structure of PC at a subroutine branch and that of PC and CCR at an exception handling are shown in figure 2.7. The PC contents are saved or restored in 32-bit units. The EXR contents are saved or restored regardless of whether or not EXR is in use.

Figure 2.7 Stack Structure (Maximum Mode)

Section 6 Interrupt Controller

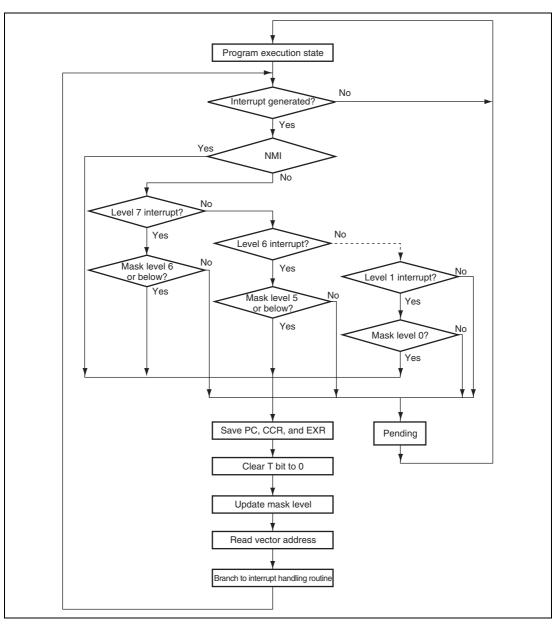

Figure 6.4 Flowchart of Procedure Up to Interrupt Acceptance in Interrupt Control Mode 2

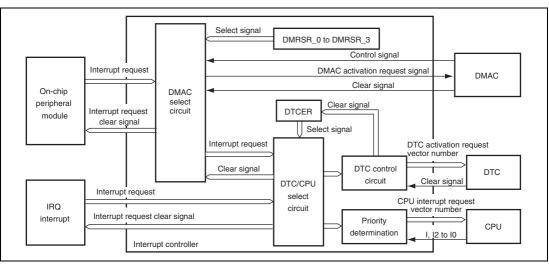

Figure 6.6 Block Diagram of DTC, DMAC, and Interrupt Controller

### (1) Selection of Interrupt Sources

The activation source for each DMAC channel is selected by DMRSR. The selected activation source is input to the DMAC through the select circuit. When transfer by an on-chip module interrupt is enabled (DTF1 = 1, DTF0 = 0, and DTE = 1 in DMDR) and the DTA bit in DMDR is set to 1, the interrupt source selected for the DMAC activation source is controlled by the DMAC and cannot be used as a DTC activation source or CPU interrupt source.

Interrupt sources that are not controlled by the DMAC are set for DTC activation sources or CPU interrupt sources by the DTCE bit in DTCERA to DTCERG of the DTC.

Specifying the DISEL bit in MRB of the DTC generates an interrupt request to the CPU by clearing the DTCE bit to 0 after the individual DTC data transfer.

Note that when the DTC performs a predetermined number of data transfers and the transfer counter indicates 0, an interrupt request is made to the CPU by clearing the DTCE bit to 0 after the DTC data transfer.

When the same interrupt source is set as both the DTC and DMAC activation source and CPU interrupt source, the DTC and DMAC must be given priority over the CPU. If the IPSETE bit in CPUPCR is set to 1, the priority is determined according to the IPR setting. Therefore, the CPUP setting or the IPR setting corresponding to the interrupt source must be set to lower than or equal to the DTCP and DMAP setting. If the CPU is given priority over the DTC or DMAC, the DTC or DMAC may not be activated, and the data transfer may not be performed.

## (3) P63/TMRI3/ **IRQ11**

The pin function is switched as shown below according to the P63DDR bit setting.

|             |                              | Setting  |

|-------------|------------------------------|----------|

|             |                              | I/O Port |

| Module Name | Pin Function                 | P63DDR   |

| I/O port    | P63 output                   | 1        |

|             | P63 input<br>(initial value) | 0        |

#### (4) P62/TMO2/SCK4/IRQ10

The pin function is switched as shown below according to the combination of the TMR and SCI register settings and P62DDR bit setting.

|             |                              | Setting |         |          |  |  |

|-------------|------------------------------|---------|---------|----------|--|--|

|             |                              | TMR     | SCI     | I/O Port |  |  |

| Module Name | Pin Function                 | TMO2_OE | SCK4_OE | P62DDR   |  |  |

| TMR         | TMO2 output                  | 1       |         |          |  |  |

| SCI         | SCK4 output                  | 0       | 1       | _        |  |  |

| I/O port    | P62 output                   | 0       | 0       | 1        |  |  |

|             | P62 input<br>(initial value) | 0       | 0       | 0        |  |  |

#### Table 12.22 TIORL\_0

|               |               |               |               |                                     | Description                                   |

|---------------|---------------|---------------|---------------|-------------------------------------|-----------------------------------------------|

| Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0 | TGRC_0<br>Function                  | TIOCC0 Pin Function                           |

| 0             | 0             | 0             | 0             | Output                              | Output disabled                               |

| 0             | 0             | 0             | 1             | compare<br>register* <sup>2</sup>   | Initial output is 0 output                    |

|               |               |               |               | register                            | 0 output at compare match                     |

| 0             | 0             | 1             | 0             | _                                   | Initial output is 0 output                    |

|               |               |               |               |                                     | 1 output at compare match                     |

| 0             | 0             | 1             | 1             | _                                   | Initial output is 0 output                    |

|               |               |               |               |                                     | Toggle output at compare match                |

| 0             | 1             | 0             | 0             | _                                   | Output disabled                               |

| 0             | 1             | 0             | 1             | _                                   | Initial output is 1 output                    |

|               |               |               |               |                                     | 0 output at compare match                     |

| 0             | 1             | 1             | 0             | _                                   | Initial output is 1 output                    |

|               |               |               |               |                                     | 1 output at compare match                     |

| 0             | 1             | 1             | 1             |                                     | Initial output is 1 output                    |

|               |               |               |               |                                     | Toggle output at compare match                |

| 1             | 0             | 0             | 0             | Input                               | Capture input source is TIOCC0 pin            |

|               |               |               |               | capture<br>– register* <sup>2</sup> | Input capture at rising edge                  |

| 1             | 0             | 0             | 1             | - register                          | Capture input source is TIOCC0 pin            |

|               |               |               |               |                                     | Input capture at falling edge                 |

| 1             | 0             | 1             | Х             | _                                   | Capture input source is TIOCC0 pin            |

|               |               |               |               |                                     | Input capture at both edges                   |

| 1             | 1             | Х             | Х             | _                                   | Capture input source is channel 1/count clock |

|               |               |               |               |                                     | Input capture at TCNT_1 count-up/count-down*1 |

[Legend]

X: Don't care

Notes: 1. When bits TPSC2 to TPSC0 in TCR\_1 are set to B'000 and  $P\phi/1$  is used as the TCNT\_1 count clock, this setting is invalid and input capture is not generated.

2. When the BFA bit in TMDR\_0 is set to 1 and TGRC\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

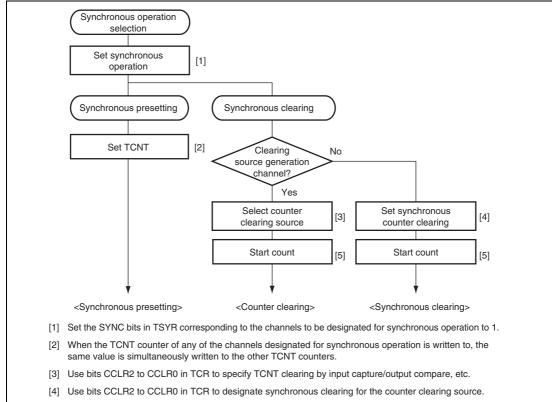

#### 12.4.2 Synchronous Operation

In synchronous operation, the values in multiple TCNT counters can be rewritten simultaneously (synchronous presetting). Also, multiple TCNT counters can be cleared simultaneously (synchronous clearing) by making the appropriate setting in TCR.

Synchronous operation enables TGR to be incremented with respect to a single time base.

Channels 0 to 5 can all be designated for synchronous operation.

#### (1) Example of Synchronous Operation Setting Procedure

Figure 12.10 shows an example of the synchronous operation setting procedure.

[5] Set the CST bits in TSTR for the relevant channels to 1, to start the count operation.

#### Figure 12.10 Example of Synchronous Operation Setting Procedure

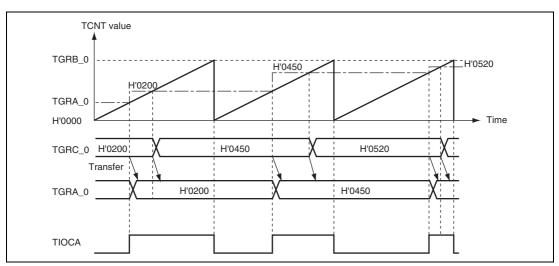

#### (2) Examples of Buffer Operation

#### (a) When TGR is an output compare register

Figure 12.15 shows an operation example in which PWM mode 1 has been designated for channel 0, and buffer operation has been designated for TGRA and TGRC. The settings used in this example are TCNT clearing by compare match B, 1 output at compare match A, and 0 output at compare match B.

As buffer operation has been set, when compare match A occurs, the output changes and the value in buffer register TGRC is simultaneously transferred to timer general register TGRA. This operation is repeated each time compare match A occurs.

For details on PWM modes, see section 12.4.5, PWM Modes.

Figure 12.15 Example of Buffer Operation (1)

| Bit | Bit Name     | Initial<br>Value | R/W | Description                                                                                                 |

|-----|--------------|------------------|-----|-------------------------------------------------------------------------------------------------------------|

| 3   | <b>G3NOV</b> | 0                | R/W | Group 3 Non-Overlap                                                                                         |

|     |              |                  |     | Selects normal or non-overlapping operation for pulse output group 3.                                       |

|     |              |                  |     | 0: Normal operation (output values updated at compare match A in the selected TPU channel)                  |

|     |              |                  |     | 1: Non-overlapping operation (output values updated at<br>compare match A or B in the selected TPU channel) |

| 2   | G2NOV        | 0                | R/W | Group 2 Non-Overlap                                                                                         |

|     |              |                  |     | Selects normal or non-overlapping operation for pulse output group 2.                                       |

|     |              |                  |     | 0: Normal operation (output values updated at compare match A in the selected TPU channel)                  |

|     |              |                  |     | 1: Non-overlapping operation (output values updated at<br>compare match A or B in the selected TPU channel) |

| 1   | G1NOV        | 0                | R/W | Group 1 Non-Overlap                                                                                         |

|     |              |                  |     | Selects normal or non-overlapping operation for pulse output group 1.                                       |

|     |              |                  |     | 0: Normal operation (output values updated at compare match A in the selected TPU channel)                  |

|     |              |                  |     | 1: Non-overlapping operation (output values updated at<br>compare match A or B in the selected TPU channel) |

| 0   | <b>G0NOV</b> | 0                | R/W | Group 0 Non-Overlap                                                                                         |

|     |              |                  |     | Selects normal or non-overlapping operation for pulse output group 0.                                       |

|     |              |                  |     | 0: Normal operation (output values updated at compare match A in the selected TPU channel)                  |

|     |              |                  |     | 1: Non-overlapping operation (output values updated at<br>compare match A or B in the selected TPU channel) |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                            |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TIE      | 0                | R/W | Transmit Interrupt Enable                                                                                                                                                                                                                                                                                                              |

|     |          |                  |     | When this bit is set to 1, a TXI interrupt request is enabled.                                                                                                                                                                                                                                                                         |

|     |          |                  |     | A TXI interrupt request can be cancelled by reading 1 from the TDRE flag and then clearing the flag to 0, or by clearing the TIE bit to 0.                                                                                                                                                                                             |

| 6   | RIE      | 0                | R/W | Receive Interrupt Enable                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | When this bit is set to 1, RXI and ERI interrupt requests are enabled.                                                                                                                                                                                                                                                                 |

|     |          |                  |     | RXI and ERI interrupt requests can be cancelled by reading 1 from the RDRF, FER, PER, or ORER flag and then clearing the flag to 0, or by clearing the RIE bit to 0.                                                                                                                                                                   |

| 5   | TE       | 0                | R/W | Transmit Enable                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | When this bit is set to 1, transmission is enabled. Under<br>this condition, serial transmission is started by writing<br>transmit data to TDR, and clearing the TDRE flag in<br>SSR to 0. Note that SMR should be set prior to setting<br>the TE bit to 1 in order to designate the transmission<br>format.                           |

|     |          |                  |     | If transmission is halted by clearing this bit to 0, the TDRE flag in SSR is fixed 1.                                                                                                                                                                                                                                                  |

| 4   | RE       | 0                | R/W | Receive Enable                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | When this bit is set to 1, reception is enabled. Under<br>this condition, serial reception is started by detecting<br>the start bit in asynchronous mode or the synchronous<br>clock input in clocked synchronous mode. Note that<br>SMR should be set prior to setting the RE bit to 1 in<br>order to designate the reception format. |

|     |          |                  |     | Even if reception is halted by clearing this bit to 0, the RDRF, FER, PER, and ORER flags are not affected and the previous value is retained.                                                                                                                                                                                         |

### Bit Functions in Normal Serial Communication Interface Mode (When SMIF in SCMR = 0):

| Bit | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                |

|-----|----------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE     | 1                | R/(W)* | Transmit Data Register Empty                                                                                                                               |

|     |          |                  |        | Indicates whether TDR contains transmit data.                                                                                                              |

|     |          |                  |        | [Setting conditions]                                                                                                                                       |

|     |          |                  |        | • When the TE bit in SCR is 0                                                                                                                              |

|     |          |                  |        | When data is transferred from TDR to TSR                                                                                                                   |

|     |          |                  |        | [Clearing conditions]                                                                                                                                      |

|     |          |                  |        | • When 0 is written to TDRE after reading TDRE = 1                                                                                                         |

|     |          |                  |        | (When the CPU is used to clear this flag by writing 0<br>while the corresponding interrupt is enabled, be sure<br>to read the flag after writing 0 to it.) |

|     |          |                  |        | When a TXI interrupt request is issued allowing                                                                                                            |

|     |          |                  |        | DMAC or DTC to write data to TDR                                                                                                                           |

| 6   | RDRF     | 0                | R/(W)* | Receive Data Register Full                                                                                                                                 |

|     |          |                  |        | Indicates whether receive data is stored in RDR.                                                                                                           |

|     |          |                  |        | [Setting condition]                                                                                                                                        |

|     |          |                  |        | <ul> <li>When serial reception ends normally and receive<br/>data is transferred from RSR to RDR</li> </ul>                                                |

|     |          |                  |        | [Clearing conditions]                                                                                                                                      |

|     |          |                  |        | • When 0 is written to RDRF after reading RDRF = 1                                                                                                         |

|     |          |                  |        | (When the CPU is used to clear this flag by writing 0<br>while the corresponding interrupt is enabled, be<br>sure to read the flag after writing 0 to it.) |

|     |          |                  |        | <ul> <li>When an RXI interrupt request is issued allowing<br/>DMAC or DTC to read data from RDR</li> </ul>                                                 |

|     |          |                  |        | The RDRF flag is not affected and retains its previous value when the RE bit in SCR is cleared to 0.                                                       |

|     |          |                  |        | Note that when the next serial reception is completed<br>while the RDRF flag is being set to 1, an overrun error<br>occurs and the received data is lost.  |

### Bit Functions in Normal Serial Communication Interface Mode (When SMIF in SCMR = 0):

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                      |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | NAKIE    | 0                | R/W | NACK Receive Interrupt Enable                                                                                                                                                                                    |

|     |          |                  |     | This bit enables or disables the NACK receive interrupt (NAKI) request when the NACKF and AL bits in ICSR are set to 1. The NAKI request can be canceled by clearing the NACKF or AL bit, or the NAKIE bit to 0. |

|     |          |                  |     | 0: NACK receive interrupt (NAKI) request is disabled                                                                                                                                                             |

|     |          |                  |     | 1: NACK receive interrupt (NAKI) request is enabled                                                                                                                                                              |

| 3   | STIE     | 0                | R/W | Stop Condition Detection Interrupt Enable                                                                                                                                                                        |

|     |          |                  |     | 0: Stop condition detection interrupt (STPI) request is<br>disabled                                                                                                                                              |

|     |          |                  |     | 1: Stop condition detection interrupt (STPI) request is<br>enabled                                                                                                                                               |

| 2   | ACKE     | 0                | R/W | Acknowledge Bit Decision Select                                                                                                                                                                                  |

|     |          |                  |     | 0: The value of the acknowledge bit is ignored and<br>continuous transfer is performed                                                                                                                           |

|     |          |                  |     | 1: If the acknowledge bit is 1, continuous transfer is<br>suspended                                                                                                                                              |

| 1   | ACKBR    | 0                | R   | Receive Acknowledge                                                                                                                                                                                              |

|     |          |                  |     | In transmit mode, this bit stores the acknowledge data that are returned by the receive device. This bit cannot be modified.                                                                                     |

|     |          |                  |     | 0: Receive acknowledge = 0                                                                                                                                                                                       |

|     |          |                  |     | 1: Receive acknowledge = 1                                                                                                                                                                                       |

| 0   | ACKBT    | 0                | R/W | Transmit Acknowledge                                                                                                                                                                                             |

|     |          |                  |     | In receive mode, this bit specifies the bit to be sent at the acknowledge timing.                                                                                                                                |

|     |          |                  |     | 0: 0 is sent at the acknowledge timing                                                                                                                                                                           |

|     |          |                  |     | 1: 1 is sent at the acknowledge timing                                                                                                                                                                           |

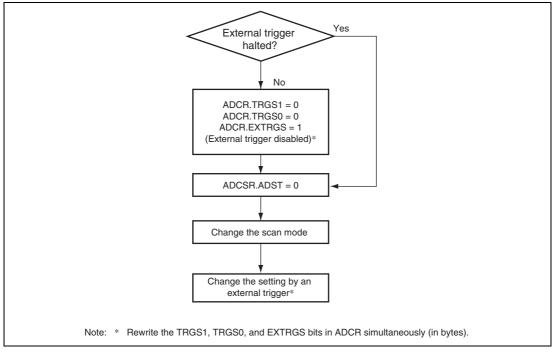

If any of the above points apply, make the corresponding settings listed below.

• If point 1 is applicable

Do not perform writing to change the value of the ADST bit in ADCSR from 0 to 1 when the setting for activation by an external trigger is in use.

• If point 2 or 3 is applicable

When the setting for activation by an external trigger is in use, only execute switching from activation by an external trigger to prohibition of activation by an external trigger or changing of the scan mode (ADSTLCR and SCANE bits) after external trigger input has been disabled. External trigger input can be disabled by writing specific values to the TRGS1, TRGS0, and EXTRGS bits in ADCR.

For details on the procedure in cases where point 2 or 3 is applicable, see figure 18.9.

Figure 18.9 Procedure for Changing the Mode When Setting for Activation by an External Trigger is in Use

### **19.3.1** $\Delta\Sigma$ A/D Mode Register (DSADMR)

DSADMR controls the biasing circuit and selects a clock for the  $\Delta\Sigma$  A/D converter. DSADMR can be read by the CPU at any time, but must be written to while the  $\Delta\Sigma$  A/D converter is in the module stop state.

| Bit            | 7     | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|----------------|-------|---|---|---|---|------|------|------|

| Bit Name       | BIASE | — | — | — | — | ACK2 | ACK1 | ACK0 |

| Initial Value: | 0     | 0 | 0 | 0 | 0 | 0    | 0    | 0    |

| R/W:           | R/W   | R | R | R | R | R/W  | R/W  | R/W  |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                     |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | BIASE    | 0                | R/W | Biasing Circuit Control                                                                                                                                                                                                         |

|        |          |                  |     | Controls whether the biasing circuit is stopped or runs.                                                                                                                                                                        |

|        |          |                  |     | 0: Biasing circuit is stopped.                                                                                                                                                                                                  |

|        |          |                  |     | 1: Biasing circuit runs.                                                                                                                                                                                                        |

| 6 to 3 | _        | All 0            | R   | Reserved                                                                                                                                                                                                                        |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                            |

| 2      | ACK2     | 0                | R/W | $\Delta\Sigma$ A/D Converter Clock Select                                                                                                                                                                                       |

| 1      | ACK1     | 0                | R/W | These bits select the frequency of the $\Delta\Sigma$ A/D converter                                                                                                                                                             |

| 0      | ACK0     | 0                | R/W | clock (A $\phi$ ). The values shown below for each setting are<br>frequency multipliers for the input clock. Set these bits so<br>that A $\phi$ is approximately 25 MHz. See section 23, Clock<br>Pulse Generator, for details. |

|        |          |                  |     | 000: × 1/6                                                                                                                                                                                                                      |

|        |          |                  |     | 001: × 1/5                                                                                                                                                                                                                      |

|        |          |                  |     | 010: × 1/4                                                                                                                                                                                                                      |

|        |          |                  |     | 011: × 1/3                                                                                                                                                                                                                      |

|        |          |                  |     | 1xx: Setting prohibited                                                                                                                                                                                                         |

[Legend] x: Don't care.

### 19.6.3 State of the $\Delta\Sigma$ A/D Converter in Software Standby Mode

If the LSI enters software standby mode with A/D conversion enabled, the  $\Delta\Sigma$  A/D converter is initialized and placed in an idle state. The  $\Delta\Sigma$  A/D data registers (DSADDRn), which hold the results of conversion, are also initialized. The analog power supply current is the current that flows through the biasing circuit. If the analog power supply current in software standby mode must be reduced, clear the BIASE bit in DSDMR to 0 to stop the biasing circuit before initiating software standby mode.

### **19.6.4** Changing the Settings of $\Delta\Sigma$ A/D Converter Registers

To avoid malfunctions during A/D conversion, do not change the settings of the  $\Delta\Sigma$  A/D converter registers while the ADST bit in DSADCSR is set to 1. Always write to the registers with the ADST bit cleared to 0. The exceptions are clearing of the ADST bit and clearing of the ADF bit after reading a 1 from it.

When the TRGS1 and TRGS0 bits in DSADCSR are set to a value other than B'00, the ADST bit may be set automatically by the trigger signal. Accordingly, before setting registers of the  $\Delta\Sigma$  A/D converter, set the TRGS1 and TRGS0 bits to B'00 or take measures to ensure that no trigger signal will be input.

#### 19.6.5 DSE Bit

Use the  $\Delta\Sigma$  A/D converter with the DSE bit in DSADCR set to 1.

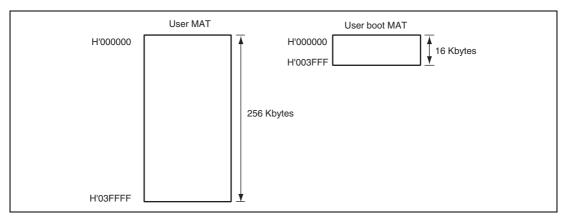

## 22.3 Memory MAT Configuration

The memory MATs of flash memory in this LSI consists of the 256-Kbyte user MAT and 16-Kbyte user boot MAT. The start addresses of the user MAT and user boot MAT are allocated to the same address. Therefore, when the program execution or data access is performed between the two memory MATs, the memory MATs must be switched by the flash MAT select register (FMATS).

The user MAT or user boot MAT can be read in all modes. However, the user boot MAT can be programmed or erased only in boot mode and programmer mode.

The size of the user MAT is different from that of the user boot MAT. Addresses which exceed the size of the 16-Kbyte user boot MAT should not be accessed. If an attempt is made, data is read as an undefined value.

Figure 22.3 Memory MAT Configuration

#### (g) User Boot MAT Information Inquiry

The boot program will return the number of user boot MATs and their addresses.

Command

H'24

• Command, H'24, (one byte): Inquiry regarding user boot MAT information

Response

### H'34 Size Number of areas

| 1101     | 0120      |    |                   |

|----------|-----------|----|-------------------|

| Area-sta | rt addres | SS | Area-last address |

|          |           |    |                   |

| SUM      |           |    |                   |

- Response, H'34, (one byte): Response to user boot MAT information inquiry

- Size (one byte): The number of bytes that represents the number of areas, area-start addresses, and area-last address

- Number of Areas (one byte): The number of consecutive user boot MAT areas When user boot MAT areas are consecutive, the number of areas returned is H'01.

- Area-start address (four byte): Start address of the area

- Area-last address (four byte): Last address of the area There are as many groups of data representing the start and last addresses as there are areas.

- SUM (one byte): Checksum

### (h) User MAT Information Inquiry

The boot program will return the number of user MATs and their addresses.

Command

H'25

• Command, H'25, (one byte): Inquiry regarding user MAT information

#### Response

| H'35     | Size      | Number of areas |                   |

|----------|-----------|-----------------|-------------------|

| Start ac | dress are | ea              | Last address area |

|          |           |                 |                   |

|          |           |                 |                   |

SUM

- Response, H'35, (one byte): Response to the user MAT information inquiry

- Size (one byte): The number of bytes that represents the number of areas, area-start address and area-last address

- Number of areas (one byte): The number of consecutive user MAT areas When the user MAT areas are consecutive, the number of areas is H'01.

- Area-start address (four bytes): Start address of the area

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module   |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|----------|

| TCR_6                    | CMIEB             | CMIEA             | OVIE              | CCLR1             | CCLR0             | CKS2              | CKS1             | CKS0             | TMR_6    |

| TCR_7                    | CMIEB             | CMIEA             | OVIE              | CCLR1             | CCLR0             | CKS2              | CKS1             | CKS0             | TMR_7    |

| TCSR_6                   | CMFB              | CMFA              | OVF               | ADTE              | OS3               | OS2               | OS1              | OS0              | TMR_6    |

| TCSR_7                   | CMFB              | CMFA              | OVF               | _                 | OS3               | OS2               | OS1              | OS0              | TMR_7    |

| TCORA_6                  |                   |                   |                   |                   |                   |                   |                  |                  | TMR_6    |

| TCORA_7                  |                   |                   |                   |                   |                   |                   |                  |                  | TMR_7    |

| TCORB_6                  |                   |                   |                   |                   |                   |                   |                  |                  | TMR_6    |

| TCORB_7                  |                   |                   |                   |                   |                   |                   |                  |                  | TMR_7    |

| TCNT_6                   |                   |                   |                   |                   |                   |                   |                  |                  | TMR_6    |

| TCNT_7                   |                   |                   |                   |                   |                   |                   |                  |                  | TMR_7    |

| TCCR_6                   | _                 | _                 | _                 |                   | TMRIS             | —                 | ICKS1            | ICKS0            | TMR_6    |

| TCCR_7                   | _                 |                   |                   |                   | TMRIS             |                   | ICKS1            | ICKS0            | TMR_7    |

| P1DDR                    | P17DDR            | P16DDR            | P15DDR            | P14DDR            | P13DDR            | P12DDR            | P11DDR           | P10DDR           | I/O port |

| P2DDR                    | P27DDR            | P26DDR            | P25DDR            | P24DDR            | P23DDR            | P22DDR            | P21DDR           | P20DDR           | _        |

| P3DDR                    | P37DDR            | P36DDR            | P35DDR            | P34DDR            | P33DDR            | P32DDR            | P31DDR           | P30DDR           | -        |

| P6DDR                    | _                 |                   | P65DDR            | P64DDR            | P63DDR            | P62DDR            | P61DDR           | P60DDR           | _        |

| PADDR                    | PA7DDR            | PA6DDR            | PA5DDR            | PA4DDR            | PA3DDR            | PA2DDR            | PA1DDR           | PA0DDR           | _        |

| PDDDR                    | PD7DDR            | PD6DDR            | PD5DDR            | PD4DDR            | PD3DDR            | PD2DDR            | PD1DDR           | PD0DDR           | _        |

| PEDDR                    | PE7DDR            | PE6DDR            | PE5DDR            | PE4DDR            | PE3DDR            | PE2DDR            | PE1DDR           | PE0DDR           | -        |

| PFDDR                    |                   |                   | _                 | PF4DDR            | PF3DDR            | PF2DDR            | PF1DDR           | PF0DDR           | -        |

| P1ICR                    | P17ICR            | P16ICR            | P15ICR            | P14ICR            | P13ICR            | P12ICR            | P11ICR           | P10ICR           | _        |

| P2ICR                    | P27ICR            | P26ICR            | P25ICR            | P24ICR            | P23ICR            | P22ICR            | P21ICR           | P20ICR           | -        |

| P3ICR                    | P37ICR            | P36ICR            | P35ICR            | P34ICR            | P33ICR            | P32ICR            | P31ICR           | P30ICR           | -        |

| P4ICR                    | P47ICR            | P46ICR            | P45ICR            | P44ICR            | P43ICR            | P42ICR            | P41ICR           | P40ICR           | -        |

| P5ICR                    | P57ICR            | P56ICR            | P55ICR            | P54ICR            | P53ICR            | P52ICR            | P51ICR           | P50ICR           | _        |

| P6ICR                    | _                 | _                 | P65ICR            | P64ICR            | P63ICR            | P62ICR            | P61ICR           | P60ICR           | _        |

| PAICR                    | PA7ICR            | PA6ICR            | PA5ICR            | PA4ICR            | PA3ICR            | PA2ICR            | PA1ICR           | PA0ICR           | -        |

| PDICR                    | PD7ICR            | PD6ICR            | PD5ICR            | PD4ICR            | PD3ICR            | PD2ICR            | PD1ICR           | PD0ICR           | -        |

| PEICR                    | PE7ICR            | PE6ICR            | PE5ICR            | PE4ICR            | <b>PE3ICR</b>     | PE2ICR            | PE1ICR           | PE0ICR           | -        |

| PFICR                    |                   |                   |                   | PF4ICR            | PF3ICR            | PF2ICR            | PF1ICR           | <b>PF0ICR</b>    | _        |

| Item                     |                               | Symbol          | Min. | Тур. | Max. | Unit | Test<br>Conditions                                    |

|--------------------------|-------------------------------|-----------------|------|------|------|------|-------------------------------------------------------|

| Input leakage<br>current | RES                           | I <sub>in</sub> | —    | —    | 10.0 | μA   | $V_{in} = 0.5 \text{ to}$<br>$V_{cc} - 0.5 \text{ V}$ |

|                          | MD, <u>STBY,</u><br>EMLE, NMI |                 | _    | _    | 1.0  |      |                                                       |

|                          | Port 4                        |                 | _    | —    | 1.0  |      | $Vin = 0.5 to$ $AV_{cc}P - 0.5 V$                     |

|                          | Port 5                        |                 |      | _    | 1.0  |      | $V_{in} = 0.5 \text{ to}$<br>AV <sub>cc</sub> - 0.5 V |