# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 320                                                        |

| Number of Logic Elements/Cells | -                                                          |

| Total RAM Bits                 | 64160                                                      |

| Number of I/O                  | 70                                                         |

| Number of Gates                | 6000                                                       |

| Voltage - Supply               | 4.25V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 84-LCC (J-Lead)                                            |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3190a-3pc84c |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Introduction

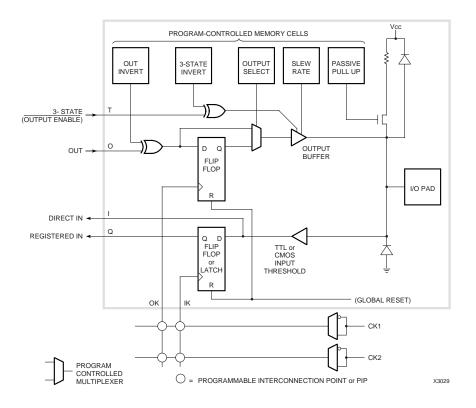

XC3000-Series Field Programmable Gate Arrays (FPGAs) provide a group of high-performance, high-density, digital integrated circuits. Their regular, extendable, flexible, user-programmable array architecture is composed of a configuration program store plus three types of configurable elements: a perimeter of I/O Blocks (IOBs), a core array of Configurable Logic Bocks (CLBs) and resources for interconnection. The general structure of an FPGA is shown in Figure 2. The development system provides schematic capture and auto place-and-route for design entry. Logic and timing simulation, and in-circuit emulation are available as design verification alternatives. The design editor is used for interactive design optimization, and to compile the data pattern that represents the configuration program.

The FPGA user logic functions and interconnections are determined by the configuration program data stored in internal static memory cells. The program can be loaded in any of several modes to accommodate various system requirements. The program data resides externally in an EEPROM, EPROM or ROM on the application circuit board, or on a floppy disk or hard disk. On-chip initialization logic provides for optional automatic loading of program data at power-up. The companion XC17XX Serial Configuration program storage in a one-time programmable package.

The XC3000 Field Programmable Gate Array families provide a variety of logic capacities, package styles, temperature ranges and speed grades.

# **XC3000 Series Overview**

There are now four distinct family groupings within the XC3000 Series of FPGA devices:

- XC3000A Family

- XC3000L Family

- XC3100A Family

- XC3100L Family

All four families share a common architecture, development software, design and programming methodology, and also common package pin-outs. An extensive Product Description covers these common aspects.

Detailed parametric information for the XC3000A, XC3000L, XC3100A, and XC3100L product families is then provided. (The XC3000 and XC3100 families are not recommended for new designs.)

Here is a simple overview of those XC3000 products currently emphasized:

- XC3000A Family The XC3000A is an enhanced version of the basic XC3000 family, featuring additional interconnect resources and other user-friendly enhancements.

- XC3000L Family The XC3000L is identical in architecture and features to the XC3000A family, but operates at a nominal supply voltage of 3.3 V. The XC3000L is the right solution for battery-operated and low-power applications.

- XC3100A Family The XC3100A is a performance-optimized relative of the XC3000A family. While both families are bitstream and footprint compatible, the XC3100A family extends toggle rates to 370 MHz and in-system performance to over 80 MHz. The XC3100A family also offers one additional array size, the XC3195A.

- XC3100L Family The XC3100L is identical in architectures and features to the XC3100A family, but operates at a nominal supply voltage of 3.3V.

Figure 1 illustrates the relationships between the families. Compared to the original XC3000 family, XC3000A offers additional functionality and increased speed. The XC3000L family offers the same additional functionality, but reduced speed due to its lower supply voltage of 3.3 V. The XC3100A family offers substantially higher speed and higher density with the XC3195A.

# New XC3000 Series Compared to Original XC3000 Family

For readers already familiar with the original XC3000 family of FPGAs, the major new features in the XC3000A, XC3000L, XC3100A, and XC3100L families are listed in this section.

All of these new families are upward-compatible extensions of the original XC3000 FPGA architecture. Any bitstream used to configure an XC3000 device will configure the corresponding XC3000A, XC3000L, XC3100A, or XC3100L device exactly the same way.

The XC3100A and XC3100L FPGA architectures are upward-compatible extensions of the XC3000A and XC3000L architectures. Any bitstream used to configure an XC3000A or XC3000L device will configure the corresponding XC3100A or XC3100L device exactly the same way.

A re-program is initiated.when a configured XC3000 series device senses a High-to-Low transition and subsequent >6  $\mu$ s Low level on the DONE/PROG package pin, or, if this pin is externally held permanently Low, a High-to-Low transition and subsequent >6  $\mu$ s Low time on the RESET package pin.

The device returns to the Clear state where the configuration memory is cleared and mode lines re-sampled, as for an aborted configuration. The complete configuration program is cleared and loaded during each configuration program cycle.

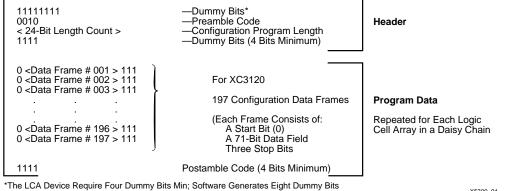

Length count control allows a system of multiple Field Programmable Gate Arrays, of assorted sizes, to begin operation in a synchronized fashion. The configuration program generated by the development system begins with a preamble of 11111110010 followed by a 24-bit length count representing the total number of configuration clocks needed to complete loading of the configuration program(s). The data framing is shown in Figure 21. All FPGAs connected in series read and shift preamble and length count in on positive and out on negative configuration clock edges. A device which has received the preamble and length count then presents a High Data Out until it has intercepted the appropriate number of data frames. When the configuration program memory of an FPGA is full and the length count does not yet compare, the device shifts any additional data through, as it did for preamble and length count. When the FPGA configuration memory is full and the length count compares, the device will execute

| Device                                                        | XC3020A<br>XC3020L<br>XC3120A | XC3030A<br>XC3030L<br>XC3130A | XC3042A<br>XC3042L<br>XC3142A<br>XC3142L | XC3064A<br>XC3064L<br>XC3164A | XC3090A<br>XC3090L<br>XC3190A<br>XC3190L | XC3195A        |

|---------------------------------------------------------------|-------------------------------|-------------------------------|------------------------------------------|-------------------------------|------------------------------------------|----------------|

| Gates                                                         | 1,000 to 1,500                | 1,500 to 2,000                | 2,000 to 3,000                           | 3,500 to 4,500                | 5,000 to 6,000                           | 6,500 to 7,500 |

| CLBs                                                          | 64                            | 100                           | 144                                      | 224                           | 320                                      | 484            |

| Row x Col                                                     | (8 x 8)                       | (10 x 10)                     | (12 x 12)                                | (16 x 14)                     | (20 x 16)                                | (22 x 22)      |

| IOBs                                                          | 64                            | 80                            | 96                                       | 120                           | 144                                      | 176            |

| Flip-flops                                                    | 256                           | 360                           | 480                                      | 688                           | 928                                      | 1,320          |

| Horizontal Longlines                                          | 16                            | 20                            | 24                                       | 32                            | 40                                       | 44             |

| TBUFs/Horizontal LL                                           | 9                             | 11                            | 13                                       | 15                            | 17                                       | 23             |

| Bits per Frame<br>(including1 start and 3 stop bits)          | 75                            | 92                            | 108                                      | 140                           | 172                                      | 188            |

| Frames                                                        | 197                           | 241                           | 285                                      | 329                           | 373                                      | 505            |

| Program Data =<br>Bits x Frames + 4 bits<br>(excludes header) | 14,779                        | 22,176                        | 30,784                                   | 46,064                        | 64,160                                   | 94,944         |

| PROM size (bits) =<br>Program Data<br>+ 40-bit Header         | 14,819                        | 22,216                        | 30,824                                   | 46,104                        | 64,200                                   | 94,984         |

**Figure 21:** Internal Configuration Data Structure for an FPGA. This shows the preamble, length count and data frames generated by the Development System.

The Length Count produced by the program = [(40-bit preamble + sum of program data + 1 per daisy chain device) rounded up to multiple of 8] – ( $2 \le K \le 4$ ) where K is a function of DONE and RESET timing selected. An additional 8 is added if roundup increment is less than K. K additional clocks are needed to complete start-up after length count is reached.

XILINX<sup>®</sup>

# **General XC3000 Series Switching Characteristics**

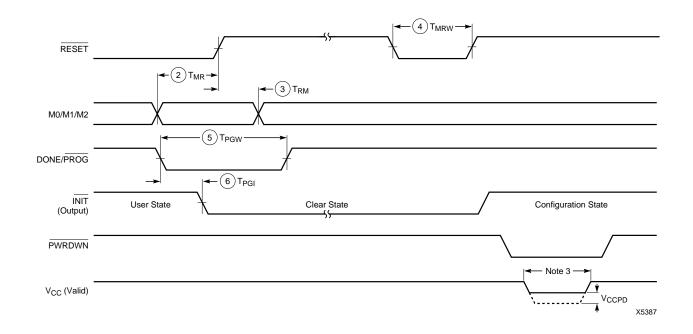

|            | Description                           |   | Symbol            | Min | Max | Units |

|------------|---------------------------------------|---|-------------------|-----|-----|-------|

|            | M0, M1, M2 setup time required        | 2 | T <sub>MR</sub>   | 1   |     | μs    |

| RESET (2)  | M0, M1, M2 hold time required         | 3 | T <sub>RM</sub>   | 4.5 |     | μs    |

|            | RESET Width (Low) req. for Abort      | 4 | T <sub>MRW</sub>  | 6   |     | μs    |

| DONE/PROG  | Width (Low) required for Re-config.   | 5 | T <sub>PGW</sub>  | 6   |     | μs    |

| DONE/FROG  | INIT response after D/P is pulled Low | 6 | T <sub>PGI</sub>  |     | 7   | μs    |

| PWRDWN (3) | Power Down V <sub>CC</sub>            |   | V <sub>CCPD</sub> | 2.3 |     | V     |

Notes: 1. At power-up, V<sub>CC</sub> must rise from 2.0 V to V<sub>CC</sub> min in less than 25 ms. If this is not possible, configuration can be delayed by holding RESET Low until Vcc has reached 4.0 V (2.5 V for XC3000L). A very long Vcc rise time of >100 ms, or a non-monotonically rising V<sub>CC</sub> may require a >1-μs High level on RESET, followed by a >6-μs Low level on RESET and D/P after V<sub>CC</sub> has reached 4.0 V (2.5 V for XC3000L).

RESET timing relative to valid mode lines (M0, M1, M2) is relevant when RESET is used to delay configuration. The rest of t

specified hold time is caused by a shift-register filter slowing down the response to RESET during configuration. 3. PWRDWN transitions must occur while  $V_{CC}$  >4.0 V(2.5 V for XC3000L).

# **Device Performance**

The XC3000 families of FPGAs can achieve very high performance. This is the result of

- A sub-micron manufacturing process, developed and continuously being enhanced for the production of state-of-the-art CMOS SRAMs.

- Careful optimization of transistor geometries, circuit design, and lay-out, based on years of experience with the XC3000 family.

- A look-up table based, coarse-grained architecture that can collapse multiple-layer combinatorial logic into a single function generator. One CLB can implement up to four layers of conventional logic in as little as 1.5 ns.

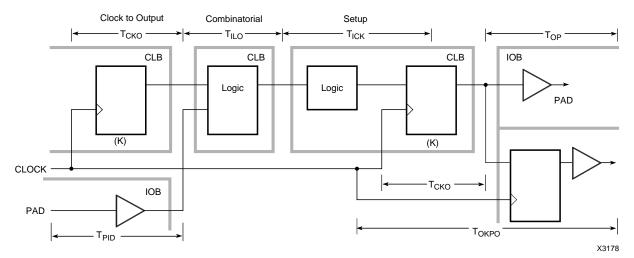

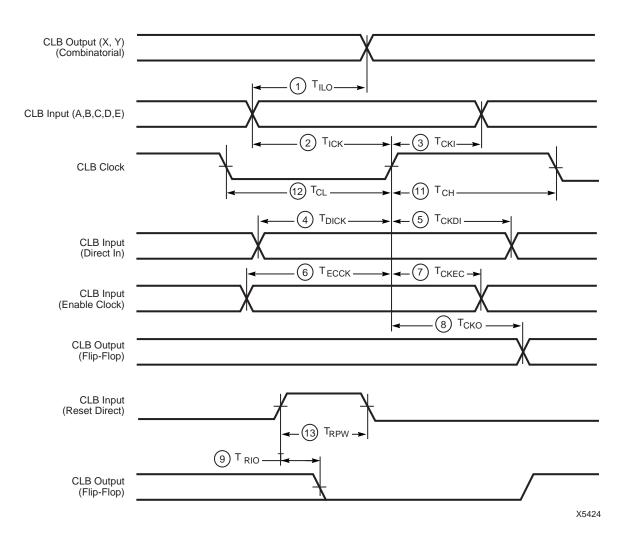

Actual system performance is determined by the timing of critical paths, including the delay through the combinatorial and sequential logic elements within CLBs and IOBs, plus the delay in the interconnect routing. The AC-timing specifications state the worst-case timing parameters for the various logic resources available in the XC3000-families architecture. Figure 31 shows a variety of elements involved in determining system performance.

Logic block performance is expressed as the propagation time from the interconnect point at the input to the block to the output of the block in the interconnect area. Since combinatorial logic is implemented with a memory lookup table within a CLB, the combinatorial delay through the CLB, called  $T_{ILO}$ , is always the same, regardless of the function being implemented. For the combinatorial logic function driving the data input of the storage element, the critical timing is data set-up relative to the clock edge provided to the flip-flop element. The delay from the clock source to the output of the logic block is critical in the timing signals pro-

duced by storage elements. Loading of a logic-block output is limited only by the resulting propagation delay of the larger interconnect network. Speed performance of the logic block is a function of supply voltage and temperature. See Figure 32.

Interconnect performance depends on the routing resources used to implement the signal path. Direct interconnects to the neighboring CLB provide an extremely fast path. Local interconnects go through switch matrices (magic boxes) and suffer an RC delay, equal to the resistance of the pass transistor multiplied by the capacitance of the driven metal line. Longlines carry the signal across the length or breadth of the chip with only one access delay. Generous on-chip signal buffering makes performance relatively insensitive to signal fan-out; increasing fan-out from 1 to 8 changes the CLB delay by only 10%. Clocks can be distributed with two low-skew clock distribution networks.

The tools in the Development System used to place and route a design in an XC3000 FPGA automatically calculate the actual maximum worst-case delays along each signal path. This timing information can be back-annotated to the design's netlist for use in timing simulation or examined with, a static timing analyzer.

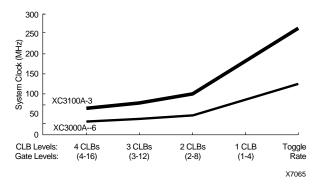

Actual system performance is applications dependent. The maximum clock rate that can be used in a system is determined by the critical path delays within that system. These delays are combinations of incremental logic and routing delays, and vary from design to design. In a synchronous system, the maximum clock rate depends on the number of combinatorial logic layers between re-synchronizing flip-flops. Figure 33 shows the achievable clock rate as a function of the number of CLB layers.

# **Product Obsolete or Under Obsolescence**

#### **XC3000 Series Field Programmable Gate Arrays**

SPECIFIED WORST-CASE VALUES 1.00 MAX MILITARY (4.5-V) 0.80 NORMALIZED DELAY 0.60 TYPICAL COMMERCIAL (+5.0)V, 25°C) TYPICAL MILITARY MIN MILITARY (4.5 V) 0.40 OMMERCIA MIN MILITARY (5.5 0.20 - 55 - 40 - 20 0 25 40 70 80 100 125

Figure 32: Relative Delay as a Function of Temperature, Supply Voltage and Processing Variations

Figure 33: Clock Rate as a Function of Logic Complexity (Number of Combinational Levels between Flip-Flops)

# Power

#### **Power Distribution**

Power for the FPGA is distributed through a grid to achieve high noise immunity and isolation between logic and I/O. Inside the FPGA, a dedicated  $V_{CC}$  and ground ring surrounding the logic array provides power to the I/O drivers. An independent matrix of  $V_{CC}$  and groundlines supplies the interior logic of the device. This power distribution grid provides a stable supply and ground for all internal logic, providing the external package power pins are all connected and appropriately decoupled. Typically a 0.1- $\mu$ F capacitor connected near the  $V_{CC}$  and ground pins will provide adequate decoupling.

Output buffers capable of driving the specified 4- or 8-mA loads under worst-case conditions may be capable of driving as much as 25 to 30 times that current in a best case. Noise can be reduced by minimizing external load capacitance and reducing simultaneous output transitions in the same direction. It may also be beneficial to locate heavily loaded output buffers near the ground pads. The I/O Block output buffers have a slew-limited mode which should be used where output rise and fall times are not speed critical. Slew-limited outputs maintain their dc drive capability, but generate less external reflections and internal noise.

# **Pin Descriptions**

# **Permanently Dedicated Pins**

#### V<sub>CC</sub>

Two to eight (depending on package type) connections to the positive V supply voltage. All must be connected.

#### GND

Two to eight (depending on package type) connections to ground. All must be connected.

#### PWRDWN

A Low on this CMOS-compatible input stops all internal activity, but retains configuration. All flip-flops and latches are reset, all outputs are 3-stated, and all inputs are interpreted as High, independent of their actual level. When PWDWN returns High, the FPGA becomes operational with DONE Low for two cycles of the internal 1-MHz clock. Before and during configuration, PWRDWN must be High. If not used, PWRDWN must be tied to  $V_{CC}$ .

#### RESET

This is an active Low input which has three functions.

Prior to the start of configuration, a Low input will delay the start of the configuration process. An internal circuit senses the application of power and begins a minimal time-out cycle. When the time-out and RESET are complete, the levels of the M lines are sampled and configuration begins.

If RESET is asserted during a configuration, the FPGA is re-initialized and restarts the configuration at the termination of RESET.

If RESET is asserted after configuration is complete, it provides a global asynchronous RESET of all IOB and CLB storage elements of the FPGA.

#### CCLK

During configuration, Configuration Clock is an output of an FPGA in Master mode or Peripheral mode, but an input in Slave mode. During Readback, CCLK is a clock input for shifting configuration data out of the FPGA.

CCLK drives dynamic circuitry inside the FPGA. The Low time may, therefore, not exceed a few microseconds. When used as an input, CCLK must be "parked High". An internal pull-up resistor maintains High when the pin is not being driven.

## DONE/PROG (D/P)

DONE is an open-drain output, configurable with or without an internal pull-up resistor of 2 to 8 k  $\Omega$ . At the completion of configuration, the FPGA circuitry becomes active in a synchronous order; DONE is programmed to go active High one cycle either before or after the outputs go active. Once configuration is done, a High-to-Low transition of this pin will cause an initialization of the FPGA and start a reconfiguration.

#### M0/RTRIG

As Mode 0, this input is sampled on power-on to determine the power-on delay (2<sup>14</sup> cycles if M0 is High, 2<sup>16</sup> cycles if M0 is Low). Before the start of configuration, this input is again sampled together with M1, M2 to determine the configuration mode to be used.

A Low-to-High input transition, after configuration is complete, acts as a Read Trigger and initiates a Readback of configuration and storage-element data clocked by CCLK. By selecting the appropriate Readback option when generating the bitstream, this operation may be limited to a single Readback, or be inhibited altogether.

## M1/RDATA

As Mode 1, this input and M0, M2 are sampled before the start of configuration to establish the configuration mode to be used. If Readback is never used, M1 can be tied directly to ground or  $V_{CC}$ . If Readback is ever used, M1 must use a 5-k $\Omega$  resistor to ground or  $V_{CC}$ , to accommodate the RDATA output.

As an active-Low Read Data, after configuration is complete, this pin is the output of the Readback data.

# User I/O Pins That Can Have Special Functions

#### M2

During configuration, this input has a weak pull-up resistor. Together with M0 and M1, it is sampled before the start of configuration to establish the configuration mode to be used. After configuration, this pin is a user-programmable I/O pin.

#### HDC

During configuration, this output is held at a High level to indicate that configuration is not yet complete. After configuration, this pin is a user-programmable I/O pin.

#### LDC

During Configuration, this output is held at a Low level to indicate that the configuration is not yet complete. After configuration, this pin is a user-programmable I/O pin. LDC is particularly useful in Master mode as a Low enable for an EPROM, but it must then be programmed as a High after configuration.

## INIT

This is an active Low open-drain output with a weak pull-up and is held Low during the power stabilization and internal clearing of the configuration memory. It can be used to indicate status to a configuring microprocessor or, as a wired

# **XC3000A Absolute Maximum Ratings**

| Symbol           | Description                                     |                              | Units |

|------------------|-------------------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND                  | -0.5 to +7.0                 | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND               | –0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output               | –0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)                   | -65 to +150                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in.) | +260                         | °C    |

| т                | Junction temperature plastic                    | +125                         | °C    |

| Τ <sub>J</sub>   | Junction temperature ceramic                    | +150                         | °C    |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

# **XC3000A Global Buffer Switching Characteristics Guidelines**

|                                                                        | Speed Grade       | -7   | -6   |       |

|------------------------------------------------------------------------|-------------------|------|------|-------|

| Description                                                            | Symbol            | Max  | Max  | Units |

| Global and Alternate Clock Distribution <sup>1</sup>                   |                   |      |      |       |

| Either: Normal IOB input pad through clock buffer                      |                   |      |      |       |

| to any CLB or IOB clock input                                          | T <sub>PID</sub>  | 7.5  | 7.0  | ns    |

| Or: Fast (CMOS only) input pad through clock                           |                   |      |      |       |

| buffer to any CLB or IOB clock input                                   | T <sub>PIDC</sub> | 6.0  | 5.7  | ns    |

| <b>TBUF</b> driving a Horizontal Longline (L.L.) <sup>1</sup>          |                   |      |      |       |

| I to L.L. while T is Low (buffer active)                               | Τ <sub>ΙΟ</sub>   | 4.5  | 4.0  | ns    |

| $T \downarrow$ to L.L. active and valid with single pull-up resistor   | T <sub>ON</sub>   | 9.0  | 8.0  | ns    |

| $T \downarrow$ to L.L. active and valid with pair of pull-up resistors | T <sub>ON</sub>   | 11.0 | 10.0 | ns    |

| T <sup>↑</sup> to L.L. High with single pull-up resistor               | T <sub>PUS</sub>  | 16.0 | 14.0 | ns    |

| T↑ to L.L. High with pair of pull-up resistors                         | T <sub>PUF</sub>  | 10.0 | 8.0  | ns    |

| BIDI                                                                   |                   |      |      |       |

| Bidirectional buffer delay                                             | T <sub>BIDI</sub> | 1.7  | 1.5  | ns    |

Note: 1. Timing is based on the XC3042A, for other devices see timing calculator.

XILINX<sup>®</sup>

## **XC3000A CLB Switching Characteristics Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used in the simulator.

|                                                                       |                                                                                            | Sp          | eed Grade                                                  | -                   | 7           | -                   | 6          |                 |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|---------------------|-------------|---------------------|------------|-----------------|

| D                                                                     | escription                                                                                 | S           | ymbol                                                      | Min                 | Max         | Min                 | Max        | Units           |

| Combinatorial Delay<br>Logic Variables                                | A, B, C, D, E, to outputs X or Y<br>FG Mode<br>F and FGM Mode                              | 1           | T <sub>ILO</sub>                                           |                     | 5.1<br>5.6  |                     | 4.1<br>4.6 | ns<br>ns        |

| Sequential delay<br>Clock k to outputs                                |                                                                                            | 8           | т <sub>ско</sub>                                           |                     | 4.5         |                     | 4.0        | ns              |

|                                                                       | X or Y when Q is returned<br>enerators F or G to drive X or Y<br>FG Mode<br>F and FGM Mode |             | T <sub>QLO</sub>                                           |                     | 9.5<br>10.0 |                     | 8.0<br>8.5 | ns<br>ns        |

| Set-up time before cloo<br>Logic Variables                            | ck K<br>A, B, C, D, E<br>FG Mode<br>F and FGM Mode                                         | 2           | Т <sub>ІСК</sub>                                           | 4.5<br>5.0          |             | 3.5<br>4.0          |            | ns<br>ns        |

| Data In<br>Enable Clock                                               | DI<br>EC                                                                                   | 4<br>6      | Т <sub>DICK</sub><br>Т <sub>ЕССК</sub>                     | 4.0<br>4.5          |             | 3.0<br>4.0          |            | ns<br>ns        |

| Hold Time after clock k<br>Logic Variables<br>Data In<br>Enable Clock | (<br>A, B, C, D, E<br>Dl <sup>2</sup><br>EC                                                | 3<br>5<br>7 | Т <sub>СКІ</sub><br>Т <sub>СКDI</sub><br>Т <sub>СКЕС</sub> | 0<br>1.0<br>2.0     |             | 0<br>1.0<br>2.0     |            | ns<br>ns<br>ns  |

| Clock<br>Clock High time<br>Clock Low time<br>Max. flip-flop togg     | Clock<br>Clock High time<br>Clock Low time                                                 |             | T <sub>CH</sub><br>T <sub>CL</sub><br>F <sub>CLK</sub>     | 4.0<br>4.0<br>113.0 |             | 3.5<br>3.5<br>135.0 |            | ns<br>ns<br>MHz |

| Reset Direct (RD)<br>RD width<br>delay from RD to outputs X or Y      |                                                                                            | 13<br>9     | T <sub>RPW</sub><br>T <sub>RIO</sub>                       | 6.0                 | 6.0         | 5.0                 | 5.0        | ns<br>ns        |

| Global Reset (RESET<br>RESET width (Lov<br>delay from RESET           |                                                                                            |             | T <sub>MRW</sub><br>T <sub>MRQ</sub>                       | 16.0                | 19.0        | 14.0                | 17.0       | ns<br>ns        |

**Notes:** 1. Timing is based on the XC3042A, for other devices see timing calculator.

The CLB K to Q output delay (T<sub>CKO</sub>, #8) of any CLB, plus the shortest possible interconnect delay, is always longer than the Data In hold time requirement (T<sub>CKDI</sub>, #5) of any CLB on the same die.

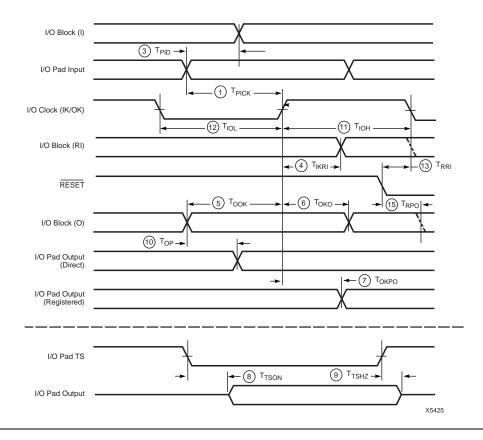

## **XC3000A IOB Switching Characteristics Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used in the simulator.

|                                   |                      | Sp | eed Grade         | -     | 7    | -     | 6    |       |

|-----------------------------------|----------------------|----|-------------------|-------|------|-------|------|-------|

| Description                       |                      | S  | ymbol             | Min   | Max  | Min   | Max  | Units |

| Propagation Delays (Input)        |                      |    |                   |       |      |       |      |       |

| Pad to Direct In (I)              |                      | 3  | T <sub>PID</sub>  |       | 4.0  |       | 3.0  | ns    |

| Pad to Registered In (Q) with la  | tch transparent      |    | T <sub>PTG</sub>  |       | 15.0 |       | 14.0 | ns    |

| Clock (IK) to Registered In (Q)   |                      | 4  | T <sub>IKRI</sub> |       | 3.0  |       | 2.5  | ns    |

| Set-up Time (Input)               |                      |    |                   |       |      |       |      |       |

| Pad to Clock (IK) set-up time     |                      | 1  | T <sub>PICK</sub> | 14.0  |      | 12.0  |      | ns    |

| Propagation Delays (Output)       |                      |    |                   |       |      |       |      |       |

| Clock (OK) to Pad                 | (fast)               | 7  | Т <sub>ОКРО</sub> |       | 8.0  |       | 7.0  | ns    |

| same                              | (slew rate limited)  | 7  | T <sub>OKPO</sub> |       | 18.0 |       | 15.0 | ns    |

| Output (O) to Pad                 | (fast)               | 10 | T <sub>OPF</sub>  |       | 6.0  |       | 5.0  | ns    |

| same                              | (slew-rate limited)  | 10 | T <sub>OPS</sub>  |       | 16.0 |       | 13.0 | ns    |

| 3-state to Pad begin hi-Z         | (fast)               | 9  | T <sub>TSHZ</sub> |       | 10.0 |       | 9.0  | ns    |

| same                              | (slew-rate limited)  | 9  | T <sub>TSHZ</sub> |       | 20.0 |       | 12.0 | ns    |

| 3-state to Pad active and valid   | (fast)               | 8  | T <sub>TSON</sub> |       | 11.0 |       | 10.0 | ns    |

| same                              | (slew -rate limited) | 8  | T <sub>TSON</sub> |       | 21.0 |       | 18.0 | ns    |

| Set-up and Hold Times (Output)    |                      |    |                   |       |      |       |      |       |

| Output (O) to clock (OK) set-up   | time                 | 5  | Т <sub>ООК</sub>  | 8.0   |      | 7.0   |      | ns    |

| Output (O) to clock (OK) hold tir | ne                   | 6  | т <sub>око</sub>  | 0     |      | 0     |      | ns    |

| Clock                             |                      |    |                   |       |      |       |      |       |

| Clock High time                   |                      | 11 | Т <sub>ЮН</sub>   | 4.0   |      | 3.5   |      | ns    |

| Clock Low time                    |                      | 12 | TIOL              | 4.0   |      | 3.5   |      | ns    |

| Max. flip-flop toggle rate        |                      |    | F <sub>CLK</sub>  | 113.0 |      | 135.0 |      | MHz   |

| Global Reset Delays (based on XC  | :3042A)              |    |                   |       |      |       |      |       |

| RESET Pad to Registered In        | (Q)                  | 13 | T <sub>RRI</sub>  |       | 24.0 |       | 23.0 | ns    |

| RESET Pad to output pad           | (fast)               | 15 | T <sub>RPO</sub>  |       | 33.0 |       | 29.0 | ns    |

|                                   | (slew-rate limited)  | 15 | T <sub>RPO</sub>  |       | 43.0 |       | 37.0 | ns    |

Notes: 1. Timing is measured at pin threshold, with 50 pF external capacitive loads (incl. test fixture). Typical slew rate limited output rise/fall times are approximately four times longer.

2. Voltage levels of unused (bonded and unbonded) pads must be valid logic levels. Each can be configured with the internal pull-up resistor or alternatively configured as a driven output or driven from an external source.

3. Input pad set-up time is specified with respect to the internal clock (ik). In order to calculate system set-up time, subtract clock delay (pad to ik) from the input pad set-up time value. Input pad holdtime with respect to the internal clock (ik) is negative. This means that pad level changes immediately before the internal clock edge (ik) will not be recognized.

4.  $T_{PID}$ ,  $T_{PTG}$ , and  $T_{PICK}$  are 3 ns higher for XTL2 when the pin is configured as a user input.

# **XC3000L Switching Characteristics**

Xilinx maintains test specifications for each product as controlled documents. To insure the use of the most recently released device performance parameters, please request a copy of the current test-specification revision.

# **XC3000L Operating Conditions**

| Symbol          | Description                                                     | Min  | Max                  | Units |

|-----------------|-----------------------------------------------------------------|------|----------------------|-------|

| V <sub>CC</sub> | Supply voltage relative to GND Commercial 0°C to +85°C junction | 3.0  | 3.6                  | V     |

| V <sub>IH</sub> | High-level input voltage — TTL configuration                    | 2.0  | V <sub>CC</sub> +0.3 | V     |

| V <sub>IL</sub> | Low-level input voltage — TTL configuration                     | -0.3 | 0.8                  | V     |

| T <sub>IN</sub> | Input signal transition time                                    |      | 250                  | ns    |

Notes: 1. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.3% per °C. 2. Although the present (1996) devices operate over the full supply voltage range from 3.0 to 5.25 V, Xilinx reserves the right to restrict operation to the 3.0 to 3.6 V range later, when smaller device geometries might preclude operation at 5V. Operating conditions are guaranteed in the  $3.0 - 3.6 \text{ V V}_{CC}$  range.

#### XC3000L DC Characteristics Over Operating Conditions

| Symbol            | Description                                                                                                              | Min                  | Мах      | Units    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|----------|----------|

| V <sub>OH</sub>   | High-level output voltage (@ I <sub>OH</sub> = -4.0 mA, V <sub>CC</sub> min)                                             | 2.40                 |          | V        |

| V <sub>OL</sub>   | Low-level output voltage (@ I <sub>OL</sub> = 4.0 mA, V <sub>CC</sub> min)                                               |                      | 0.40     | V        |

| V <sub>OH</sub>   | High-level output voltage (@ I <sub>OH</sub> = -4.0 mA, V <sub>CC</sub> min)                                             | V <sub>CC</sub> -0.2 |          | V        |

| V <sub>OL</sub>   | Low-level output voltage (@ I <sub>OL</sub> = 4.0 mA, V <sub>CC</sub> min)                                               |                      | 0.2      | V        |

| V <sub>CCPD</sub> | Power-down supply voltage (PWRDWN must be Low)                                                                           | 2.30                 |          | V        |

| I <sub>CCPD</sub> | Power-down supply current (V <sub>CC(MAX)</sub> @ T <sub>MAX</sub> )                                                     |                      | 10       | μA       |

| I <sub>CCO</sub>  | Quiescent FPGA supply current in addition to I <sub>CCPD</sub> <sup>1</sup><br>Chip thresholds programmed as CMOS levels |                      | 20       | μA       |

| ۱ <sub>IL</sub>   | Input Leakage Current                                                                                                    | -10                  | +10      | μΑ       |

| 6                 | Input capacitance, all packages except PGA175<br>(sample tested)<br>All Pins except XTL1 and XTL2<br>XTL1 and XTL2       |                      | 10<br>15 | pF<br>pF |

| C <sub>IN</sub>   | Input capacitance, PGA 175<br>(sample tested)<br>All Pins except XTL1 and XTL2<br>XTL1 and XTL2                          |                      | 15<br>20 | pF<br>pF |

| I <sub>RIN</sub>  | Pad pull-up (when selected) @ $V_{IN} = 0 V^3$                                                                           | 0.01                 | 0.17     | mA       |

| I <sub>RLL</sub>  | Horizontal Longline pull-up (when selected) @ logic Low                                                                  |                      | 2.50     | mA       |

Notes: 1. With no output current loads, no active input or Longline pull-up resistors, all package pins at V<sub>CC</sub> or GND, and the FPGA

device configured with a tie option. I<sub>CCO</sub> is in addition to I<sub>CCPD</sub>.

2. Total continuous output sink current may not exceed 100 mA per ground pin. Total continuous output source may not exceed 100 mA per V<sub>CC</sub> pin. The number of ground pins varies from the XC3020L to the XC3090L.

3. Not tested. Allows an undriven pin to float High. For any other purpose, use an external pull-up.

## **XC3000L CLB Switching Characteristics Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used in the simulator.

|                                                            |                                                                | Sp          | eed Grade                                                  | -                  | 8            |                 |

|------------------------------------------------------------|----------------------------------------------------------------|-------------|------------------------------------------------------------|--------------------|--------------|-----------------|

|                                                            | Description                                                    | S           | ymbol                                                      | Min                | Max          | Units           |

| Combinatorial Delay                                        |                                                                |             |                                                            |                    |              |                 |

| Logic Variables                                            | A, B, C, D, E, to outputs X or Y<br>FG Mode<br>F and FGM Mode  | 1           | T <sub>ILO</sub>                                           |                    | 6.7<br>7.5   | ns<br>ns        |

| Sequential delay                                           |                                                                |             |                                                            |                    |              |                 |

| Clock k to outputs<br>Clock k to outputs                   | X or Y when Q is returned                                      | 8           | т <sub>ско</sub>                                           |                    | 7.5          | ns              |

| through function g                                         | jenerators F or G to drive X or Y<br>FG Mode<br>F and FGM Mode |             | T <sub>QLO</sub>                                           |                    | 14.0<br>14.8 | ns<br>ns        |

| Set-up time before clo                                     | ck K                                                           |             |                                                            |                    |              |                 |

| Logic Variables                                            | A, B, C, D, E<br>FG Mode<br>F and FGM Mode                     | 2           | Т <sub>ІСК</sub>                                           | 5.0<br>5.8         |              | ns<br>ns        |

| Data In<br>Enable Clock                                    | DI<br>EC                                                       | 4           | Т <sub>DICK</sub><br>Т <sub>ЕССК</sub>                     | 5.0<br>6.0         |              | ns              |

| Hold Time after clock                                      | <                                                              |             | LOOK                                                       |                    |              |                 |

| Logic Variables<br>Data In<br>Enable Clock                 | A, B, C, D, E<br>DI <sup>2</sup><br>EC                         | 3<br>5<br>7 | Т <sub>СКІ</sub><br>Т <sub>СКDI</sub><br>Т <sub>СКЕС</sub> | 0<br>2.0<br>2.0    |              | ns<br>ns<br>ns  |

| Clock                                                      |                                                                |             |                                                            |                    |              |                 |

| Clock High time<br>Clock Low time<br>Max. flip-flop togg   | le rate                                                        | 11<br>12    | T <sub>CH</sub><br>T <sub>CL</sub><br>F <sub>CLK</sub>     | 5.0<br>5.0<br>80.0 |              | ns<br>ns<br>MHz |

| Reset Direct (RD)                                          |                                                                |             | OLIX                                                       |                    |              |                 |

| RD width<br>delay from RD to outputs X or Y                |                                                                | 13<br>9     | T <sub>RPW</sub><br>T <sub>RIO</sub>                       | 7.0<br>7.0         |              | ns<br>ns        |

| Global Reset (RESET<br>RESET width (Low<br>delay from RESE |                                                                |             | T <sub>MRW</sub><br>T <sub>MRQ</sub>                       | 16.0               | 23.0         | ns<br>ns        |

**Notes:** 1. Timing is based on the XC3042L, for other devices see timing calculator.

The CLB K to Q output delay (T<sub>CKO</sub>, #8) of any CLB, plus the shortest possible interconnect delay, is always longer than the Data In hold time requirement (T<sub>CKDI</sub>, #5) of any CLB on the same die.

**∑**XILINX<sup>®</sup>

# **XC3000L CLB Switching Characteristics Guidelines (continued)**

## **XC3100A CLB Switching Characteristics Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used in the simulator.

| Speed G                                                                                                                                                |             | d Grade     | -                                                          | 4                        | -          | -3 -2                    |            | -1                       |            | -0                       | )9         |                           |             |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------------------------------------------------------|--------------------------|------------|--------------------------|------------|--------------------------|------------|--------------------------|------------|---------------------------|-------------|----------------------|

| Descriptio                                                                                                                                             | n           | S           | ymbol                                                      | Min                      | Max        | Min                      | Max        | Min                      | Max        | Min                      | Max        | Min                       | Max         | Units                |

| Combinatorial Delay<br>Logic Variables A, I<br>to outputs X or Y                                                                                       | B, C, D, E, | 1           | T <sub>ILO</sub>                                           |                          | 3.3        |                          | 2.7        |                          | 2.2        |                          | 1.75       |                           | 1.5         | ns                   |

| Sequential delay<br>Clock k to outputs X or Y<br>Clock k to outputs X or Y when Q is returned<br>through function generators F or G to drive<br>X or Y |             | 8           | Т <sub>ско</sub><br>Т <sub>QLO</sub>                       |                          | 2.5<br>5.2 |                          | 2.1<br>4.3 |                          | 1.7<br>3.5 |                          | 1.4<br>3.1 |                           | 1.25<br>2.7 | ns<br>ns             |

| Set-up time before clock K<br>Logic Variables A, I<br>Data In DI<br>Enable Clock EC<br>Reset Direct inactive RD                                        |             | 2<br>4<br>6 | T <sub>ICK</sub><br>T <sub>DICK</sub><br>T <sub>ECCK</sub> | 2.5<br>1.6<br>3.2<br>1.0 |            | 2.1<br>1.4<br>2.7<br>1.0 |            | 1.8<br>1.3<br>2.5<br>1.0 |            | 1.7<br>1.2<br>2.3<br>1.0 |            | 1.5<br>1.0<br>2.05<br>1.0 |             | ns<br>ns<br>ns<br>ns |

| Hold Time after clock K<br>Logic Variables A, I<br>Data In DI<br>Enable Clock EC                                                                       | B, C, D, E  | 3<br>5<br>7 | T <sub>CKI</sub><br>T <sub>CKDI</sub><br>T <sub>CKEC</sub> | 0<br>1.0<br>0.8          |            | 0<br>0.9<br>0.7          |            | 0<br>0.9<br>0.7          |            | 0<br>0.8<br>0.6          |            | 0<br>0.7<br>0.55          |             | ns<br>ns<br>ns       |

| Clock High time<br>Clock Low time<br>Max. flip-flop toggle rate                                                                                        |             | 11<br>12    | Т <sub>СН</sub><br>Т <sub>СL</sub><br>F <sub>CLK</sub>     | 2.0<br>2.0<br>227        |            | 1.6<br>1.6<br>270        |            | 1.3<br>1.3<br>323        |            | 1.3<br>1.3<br>323        |            | 1.3<br>1.3<br>370         |             | ns<br>ns<br>MHz      |

| Reset Direct (RD)<br>RD width<br>delay from RD to outputs X or Y                                                                                       |             | 13<br>9     | T <sub>RPW</sub><br>T <sub>RIO</sub>                       | 3.2                      | 3.7        | 2.7                      | 3.1        | 2.3                      | 2.7        | 2.3                      | 2.4        | 2.05                      | 2.15        | ns<br>ns             |

| Gl <u>obal Re</u> set (RESET Pad) <sup>1</sup><br>RESET wid <u>th (Low)</u> (XC3142A)<br>delay from RESET pad to outputs X or Y                        |             |             | T <sub>MRW</sub><br>T <sub>MRQ</sub>                       | 14.0                     | 14.0       | 12.0                     | 12.0       | 12.0                     | 12.0       | 12.0                     | 12.0       | 12.0                      | 12.0        | ns<br>ns             |

|                                                                                                                                                        |             |             |                                                            |                          |            |                          |            |                          |            |                          |            | Pre                       | lim         |                      |

Notes: 1. The CLB K to Q output delay (T<sub>CKO</sub>, #8) of any CLB, plus the shortest possible interconnect delay, is always longer than the Data In hold time requirement (T<sub>CKDI</sub>, #5) of any CLB on the same die.

2. T<sub>ILO</sub>, T<sub>QLO</sub> and T<sub>ICK</sub> are specified for 4-input functions. For 5-input functions or base FGM functions, each of these

T<sub>ILO</sub>, T<sub>QLO</sub> and T<sub>ICK</sub> are specified for 4-input functions. For 5-input functions or base FGM functions, each of these specifications for the XC3100A family increases by 0.50 ns (-5), 0.42 ns (-4) and 0.35 ns (-3), 0.35 ns (-2), 0.30 ns (-1), and 0.30 ns (-09).

# **XC3100L Switching Characteristics**

Xilinx maintains test specifications for each product as controlled documents. To insure the use of the most recently released device performance parameters, please request a copy of the current test-specification revision.

# **XC3100L Operating Conditions**

| Symbol          | Description                                                     | Min  | Max                   | Units |

|-----------------|-----------------------------------------------------------------|------|-----------------------|-------|

| V <sub>CC</sub> | Supply voltage relative to GND Commercial 0°C to +85°C junction | 3.0  | 3.6                   | V     |

| VIH             | High-level input voltage                                        | 2.0  | V <sub>CC</sub> + 0.3 | V     |

| V <sub>IL</sub> | Low-level input voltage                                         | -0.3 | 0.8                   | V     |

| T <sub>IN</sub> | Input signal transition time                                    |      | 250                   | ns    |

Notes: 1. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.3% per °C. 2. Although the present (1996) devices operate over the full supply voltage range from 3.0 V to 5.25 V, Xilinx reserves the right to restrict operation to the 3.0 and 3.6 V range later, when smaller device geometries might preclude operation @ 5 V. Operating conditions are guaranteed in the  $3.0 - 3.6 \vee V_{CC}$  range.

#### XC3100L DC Characteristics Over Operating Conditions

| Symbol            | Description                                                                    | Min                  | Max  | Units |

|-------------------|--------------------------------------------------------------------------------|----------------------|------|-------|

| V                 | High-level output voltage (@ I <sub>OH</sub> = -4.0 mA, V <sub>CC</sub> min)   | 2.4                  |      | V     |

| V <sub>OH</sub>   | High-level output voltage (@ I <sub>OH</sub> = -100.0 μA, V <sub>CC</sub> min) | V <sub>CC</sub> -0.2 |      | V     |

| V                 | Low-level output voltage (@ I <sub>OH</sub> = 4.0 mA, V <sub>CC</sub> min)     |                      | 0.40 | V     |

| V <sub>OL</sub>   | Low-level output voltage (@ I <sub>OH</sub> = +100.0 µA, V <sub>CC</sub> min)  |                      | 0.2  | V     |

| V <sub>CCPD</sub> | Power-down supply voltage (PWRDWN must be Low)                                 | 2.30                 |      | V     |

| I <sub>CCO</sub>  | Quiescent FPGA supply current                                                  |                      | 1.5  | mA    |

|                   | Chip thresholds programmed as CMOS levels <sup>1</sup>                         |                      |      |       |

| IIL               | Input Leakage Current                                                          | -10                  | +10  | μΑ    |

|                   | Input capacitance                                                              |                      |      |       |

| C                 | (sample tested)                                                                |                      |      |       |

| C <sub>IN</sub>   | All pins except XTL1 and XTL2                                                  |                      | 10   | pF    |

|                   | XTL1 and XTL2                                                                  |                      | 15   | pF    |

| I <sub>RIN</sub>  | Pad pull-up (when selected) @ $V_{IN} = 0 V^3$                                 | 0.02                 | 0.17 | mA    |

| I <sub>RLL</sub>  | Horizontal long line pull-up (when selected) @ logic Low                       | 0.20                 | 2.80 | mA    |

Notes: 1. With no output current loads, no active input or long line pull-up resistors, all package pins at V<sub>CC</sub> or GND, and the FPGA configured with a tie option.

2. Total continuous output sink current may not exceed 100 mA per ground pin. Total continuous output source current may not exceed 100 mA per V<sub>CC</sub> pin. The number of ground pins varies from the XC3142L to the XC3190L. 3. Not tested. Allows undriven pins to float High. For any other purpose, use an external pull-up.

# **XC3100L IOB Switching Characteristics Guidelines (continued)**

# **XC3000 Series Pin Assignments**

Xilinx offers the six different array sizes in the XC3000 families in a variety of surface-mount and through-hole package types, with pin counts from 44 to 208.

Each chip is offered in several package types to accommodate the available PC board space and manufacturing technology. Most package types are also offered with different chips to accommodate design changes without the need for PC board changes.

Note that there is no perfect match between the number of bonding pads on the chip and the number of pins on a package. In some cases, the chip has more pads than there are pins on the package, as indicated by the information ("unused" pads) below the line in the following table. The IOBs of the unconnected pads can still be used as storage elements if the specified propagation delays and set-up times are acceptable.

In other cases, the chip has fewer pads than there are pins on the package; therefore, some package pins are not connected (n.c.), as shown above the line in the following table.

# XC3000 Series 44-Pin PLCC Pinouts

XC3000A, XC3000L, and XC3100A families have identical pinouts

| Pin No. | XC3030A    |

|---------|------------|

| 1       | GND        |

| 2       | I/O        |

| 3       | I/O        |

| 4       | I/O        |

| 5       | I/O        |

| 6       | I/O        |

| 7       | PWRDWN     |

| 8       | TCLKIN-I/O |

| 9       | I/O        |

| 10      | I/O        |

| 11      | I/O        |

| 12      | VCC        |

| 13      | I/O        |

| 14      | I/O        |

| 15      | I/O        |

| 16      | M1-RDATA   |

| 17      | M0-RTRIG   |

| 18      | M2-I/O     |

| 19      | HDC-I/O    |

| 20      | LDC-I/O    |

| 21      | I/O        |

| 22      | INIT-I/O   |

| Pin No. | XC3030A            |

|---------|--------------------|

| 23      | GND                |

| 24      | I/O                |

| 25      | I/O                |

| 26      | XTL2(IN)-I/O       |

| 27      | RESET              |

| 28      | DONE-PGM           |

| 29      | I/O                |

| 30      | XTL1(OUT)-BCLK-I/O |

| 31      | I/O                |

| 32      | I/O                |

| 33      | I/O                |

| 34      | VCC                |

| 35      | I/O                |

| 36      | I/O                |

| 37      | I/O                |

| 38      | DIN-I/O            |

| 39      | DOUT-I/O           |

| 40      | CCLK               |

| 41      | I/O                |

| 42      | I/O                |

| 43      | I/O                |

| 44      | I/O                |

Peripheral mode and Master Parallel mode are not supported in the PC44 package

# XC3064A/XC3090A/XC3195A 84-Pin PLCC Pinouts

XC3000A, XC3000L, XC3100A, and XC3100L families have identical pinouts

| LCC Pin Number | XC3064A, XC3090A, XC3195A |

|----------------|---------------------------|

| 12             | PWRDN                     |

| 13             | TCLKIN-I/O                |

| 14             | I/O                       |

| 15             | I/O                       |

| 16             | I/O                       |

| 17             | I/O                       |

| 18             | I/O                       |

| 19             | I/O                       |

| 20             | I/O                       |

| 21             | GND*                      |

| 22             | VCC                       |

| 23             | I/O                       |

| 24             | I/O                       |

| 25             | I/O                       |

| 26             | I/O                       |

| 27             | I/O                       |

| 28             | I/O                       |

| 29             | I/O                       |

| 30             | I/O                       |

| 31             | M1-RDATA                  |

| 32             | M0-RTRIG                  |

| 33             | M2-I/O                    |

| 34             | HDC-I/O                   |

| 35             | I/O                       |

| 36             | LDC-I/O                   |

| 37             | I/O                       |

| 38             | I/O                       |

| 39             | I/O                       |

| 40             | 1/O                       |

| 41             | INIT/I/O*                 |

| 42             | VCC*                      |

| 43             | GND                       |

| 44             | 1/0                       |

| 44 45          | 1/O                       |

| 45             | 1/0<br>1/0                |

| 40 47          | 1/O<br>1/O                |

| 48             | 1/O<br>1/O                |

| 48             | I/O                       |

|                |                           |

| 50             | I/O                       |

| 51             | I/O                       |

| 52             |                           |

| 53             | XTL2(IN)-I/O              |

| RESET           DONE-PG           D7-I/O           (TL1(OUT)-BCLKIN-I/O           D6-I/O           I/O           D5-I/O           CS0-I/O           D4-I/O           I/O           VCC           GND*           D3-I/O*           CS1-I/O* |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-I/O<br>(TL1(OUT)-BCLKIN-I/O<br>D6-I/O<br>I/O<br>D5-I/O<br>CS0-I/O<br>D4-I/O<br>I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                |

| (TL1(OUT)-BCLKIN-I/O<br>D6-I/O<br>I/O<br>D5-I/O<br>CS0-I/O<br>D4-I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                 |

| D6-I/O<br>I/O<br>D5-I/O<br>CS0-I/O<br>D4-I/O<br>I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                  |

| I/O         D5-I/O         CS0-I/O         D4-I/O         I/O         VCC         GND*         D3-I/O*         CS1-I/O*                                                                                                                    |

| D5-I/O<br>CS0-I/O<br>D4-I/O<br>I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                                   |

| CS0-I/O           D4-I/O           I/O           VCC           GND*           D3-I/O*           CS1-I/O*                                                                                                                                   |

| D4-I/O<br>I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                                                        |

| I/O<br>VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                                                                  |

| VCC<br>GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                                                                         |

| GND*<br>D3-I/O*<br>CS1-I/O*                                                                                                                                                                                                                |

| D3-I/O*<br>CS1-I/O*                                                                                                                                                                                                                        |

| D3-I/O*<br>CS1-I/O*                                                                                                                                                                                                                        |

| CS1-I/O*                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

| I/O                                                                                                                                                                                                                                        |

| D1-I/O                                                                                                                                                                                                                                     |

| RDY/BUSY-RCLK-I/O                                                                                                                                                                                                                          |

| D0-DIN-I/O                                                                                                                                                                                                                                 |

| DOUT-I/O                                                                                                                                                                                                                                   |

| CCLK                                                                                                                                                                                                                                       |

| A0-WS-I/O                                                                                                                                                                                                                                  |

| A1-CS2-I/O                                                                                                                                                                                                                                 |

| A2-I/O                                                                                                                                                                                                                                     |

| A3-I/O                                                                                                                                                                                                                                     |

| I/O                                                                                                                                                                                                                                        |

| I/O                                                                                                                                                                                                                                        |

| A15-I/O                                                                                                                                                                                                                                    |

| A4-I/O                                                                                                                                                                                                                                     |

| A14-I/O                                                                                                                                                                                                                                    |

| A5-I/O                                                                                                                                                                                                                                     |

| GND                                                                                                                                                                                                                                        |

| VCC*                                                                                                                                                                                                                                       |

| A13-I/O*                                                                                                                                                                                                                                   |

| A6-I/O*                                                                                                                                                                                                                                    |

| A12-I/O*                                                                                                                                                                                                                                   |

| A7-I/O*                                                                                                                                                                                                                                    |

| I/O                                                                                                                                                                                                                                        |

| A11-I/O                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                            |

| A8-I/O                                                                                                                                                                                                                                     |

| A8-I/O<br>A10-I/O                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                            |

Unprogrammed IOBs have a default pull-up. This prevents an undefined pad level for unbonded or unused IOBs. Programmed outputs are default slew-rate limited.

\* In the PC84 package, XC3064A, XC3090A and XC3195A have additional VCC and GND pins and thus a different pin definition than XC3020A/XC3030A/XC3042A.

## XC3000 Series 144-Pin Plastic TQFP Pinouts

XC3000A, XC3000L, XC3100A, and XC3100L families have identical pinouts

| Pin<br>Number | XC3042A<br>XC3064A<br>XC3090A | Pin<br>Number | XC3042A<br>XC3064A<br>XC3090A | Pin<br>Number | XC3042A<br>XC3064A<br>XC3090A |  |

|---------------|-------------------------------|---------------|-------------------------------|---------------|-------------------------------|--|

| 1             | PWRDN                         | 49            | I/O                           | 97            | I/O                           |  |

| 2             | I/O-TCLKIN                    | 50            | I/O*                          | 98            | I/O                           |  |

| 3             | I/O*                          | 51            | I/O                           | 99            | I/O*                          |  |

| 4             | I/O                           | 52            | I/O                           | 100           | I/O                           |  |

| 5             | I/O                           | 53            | INIT-I/O                      | 101           | I/O*                          |  |

| 6             | I/O*                          | 54            | VCC                           | 102           | D1-I/O                        |  |

| 7             | I/O                           | 55            | GND                           | 103           | RDY/BUSY-RCLK-I/O             |  |

| 8             | I/O                           | 56            | I/O                           | 104           | I/O                           |  |

| 9             | I/O*                          | 57            | I/O                           | 105           | I/O                           |  |

| 10            | I/O                           | 58            | I/O                           | 106           | D0-DIN-I/O                    |  |

| 11            | I/O                           | 59            | I/O                           | 107           | DOUT-I/O                      |  |

| 12            | I/O                           | 60            | I/O                           | 108           | CCLK                          |  |

| 13            | I/O                           | 61            | I/O                           | 109           | VCC                           |  |

| 14            | I/O                           | 62            | I/O                           | 110           | GND                           |  |

| 15            | I/O*                          | 63            | I/O*                          | 111           | A0-WS-I/O                     |  |

| 16            | I/O                           | 64            | I/O*                          | 112           | A1-CS2-I/O                    |  |

| 17            | I/O                           | 65            | I/O                           | 113           | I/O                           |  |

| 18            | GND                           | 66            | I/O                           | 114           | I/O                           |  |

| 19            | VCC                           | 67            | I/O                           | 115           | A2-I/O                        |  |

| 20            | I/O                           | 68            | I/O                           | 116           | A3-I/O                        |  |

| 21            | I/O                           | 69            | XTL2(IN)-I/O                  | 117           | I/O                           |  |