Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ХА                                                                    |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 30MHz                                                                 |

| Connectivity               | UART/USART                                                            |

| Peripherals                | PWM, WDT                                                              |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LCC (J-Lead)                                                       |

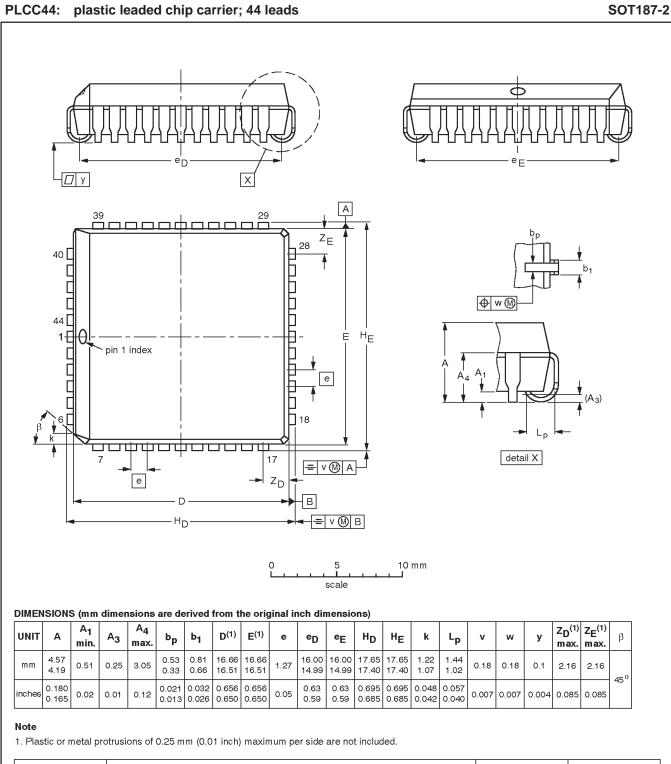

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/pxag37kfa-512 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

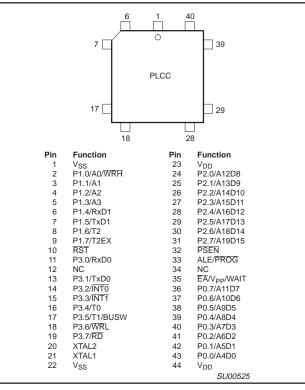

## PIN CONFIGURATIONS 44-Pin PLCC Package

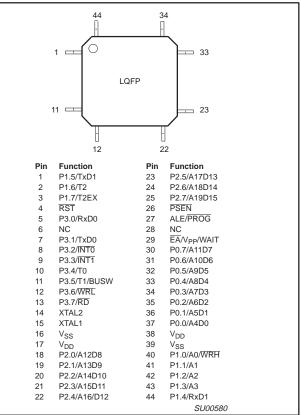

## 44-Pin LQFP Package

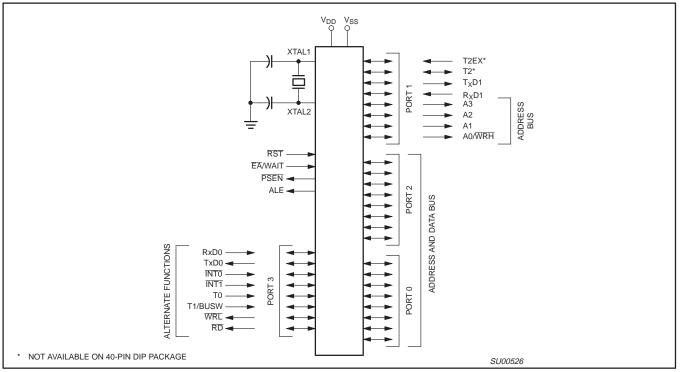

## LOGIC SYMBOL

## **PIN DESCRIPTIONS**

| MNEMONIC        | PIN.         | NO.           | TYPE |                                                                                                                                                                                                                                                              | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|-----------------|--------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| MINEMONIC       | PLCC         | LQFP          | TIPE |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| V <sub>SS</sub> | 1, 22        | 16            | I    | Ground: 0 V referen                                                                                                                                                                                                                                          | nce.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| V <sub>DD</sub> | 23, 44       | 17            | I    | Power Supply: This                                                                                                                                                                                                                                           | Power Supply: This is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| P0.0 – P0.7     | 43–36        | 37–30         | I/O  | written to them and a<br>port 0 pins as inputs<br>configured independ                                                                                                                                                                                        | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. Port 0 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.                                                                                                                   |  |  |  |  |  |  |  |  |

|                 |              |               |      |                                                                                                                                                                                                                                                              | When the external program/data bus is used, Port 0 becomes the multiplexed low data/instruction yte and address lines 4 through 11.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| P1.0 – P1.7     | 2–9          | 40–44,<br>1–3 | I/O  | written to them and<br>port 1 pins as inputs<br>configured independ<br>Characteristics for d                                                                                                                                                                 | <b>Port 1:</b> Port 1 is an 8-bit I/O port with a user-configurable output type. Port 1 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 1 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.                                                                                                                   |  |  |  |  |  |  |  |  |

|                 |              |               |      | Port 1 also provides                                                                                                                                                                                                                                         | special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                 | 2            | 40            | 0    |                                                                                                                                                                                                                                                              | Address bit 0 of the external address bus when the external data bus is configured for an 8 bit width. When the external data bus is configured for a 16 bit width, this pin becomes the high byte write strobe.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                 | 3            | 41            | 0    | A1:                                                                                                                                                                                                                                                          | Address bit 1 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                 | 4            | 42            | 0    | A2:                                                                                                                                                                                                                                                          | Address bit 2 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                 | 5            | 43            | 0    | A3:                                                                                                                                                                                                                                                          | Address bit 3 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                 | 6            | 44            |      |                                                                                                                                                                                                                                                              | Receiver input for serial port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                 | 7            | 1             | 0    | . ,                                                                                                                                                                                                                                                          | Transmitter output for serial port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                 | 8            | 2             | I/O  | . ,                                                                                                                                                                                                                                                          | Timer/counter 2 external count input/clockout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                 | 9            | 3             |      | T2EX (P1.7):                                                                                                                                                                                                                                                 | Timer/counter 2 reload/capture/direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| P2.0 – P2.7     | 24–31        | 18–25         | I/O  | written to them and<br>port 2 pins as inputs<br>configured independ<br>Characteristics for d<br>When the external pr<br>data/instruction byte a                                                                                                              | 8-bit I/O port with a user-configurable output type. Port 2 latches have 1s are configured in the quasi-bidirectional mode during reset. The operation of and outputs depends upon the port configuration selected. Each port pin is lently. Refer to the section on I/O port configuration and the DC Electrical etails.<br>ogram/data bus is used in 16-bit mode, Port 2 becomes the multiplexed high and address lines 12 through 19. When the external program/data bus is used in more of address lines that appear on port 2 is user programmable. |  |  |  |  |  |  |  |  |

| P3.0 – P3.7     | 11,<br>13–19 | 5,<br>7–13    | I/O  | written to them and port 3 pins as inputs                                                                                                                                                                                                                    | 8-bit I/O port with a user configurable output type. Port 3 latches have 1s are configured in the quasi-bidirectional mode during reset. the operation of and outputs depends upon the port configuration selected. Each port pin is lently. Refer to the section on I/O port configuration and the DC Electrical etails.                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|                 |              |               |      | Port 3 also provides                                                                                                                                                                                                                                         | various special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                 | 11           | 5             | 1    | RxD0 (P3.0):                                                                                                                                                                                                                                                 | Receiver input for serial port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                 | 13           | 7             | 0    | TxD0 (P3.1):                                                                                                                                                                                                                                                 | Transmitter output for serial port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                 | 14           | 8             |      | INTO (P3.2):                                                                                                                                                                                                                                                 | External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                 | 15           | 9             |      | INT1 (P3.3):                                                                                                                                                                                                                                                 | External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                 | 16           | 10            | I/O  | T0 (P3.4):                                                                                                                                                                                                                                                   | Timer 0 external input, or timer 0 overflow output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                 | 17           | 11            | I/O  | T1/BUSW (P3.5)                                                                                                                                                                                                                                               | : Timer 1 external input, or timer 1 overflow output. The value on this pin is latched as the external reset input is released and defines the default external data bus width (BUSW). 0 = 8-bit bus and 1 = 16-bit bus.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                 | 18           | 12            | 0    | WRL (P3.6):                                                                                                                                                                                                                                                  | External data memory low byte write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                 | 19           | 13            | 0    | RD (P3.7):                                                                                                                                                                                                                                                   | External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| RST             | 10           | 4             | I    | <b>Reset:</b> A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor to begin execution at the address contained in the reset vector. Refer to the section on Reset for details. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| ALE/PROG        | 33           | 27            | I/O  | latch the address po                                                                                                                                                                                                                                         | ddress Latch Enable/Program Pulse: A high output on the ALE pin signals external circuitry to tch the address portion of the multiplexed address/data bus. A pulse on ALE occurs only when it needed in order to process a bus cycle.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

2002 Mar 25

# XA 16-bit microcontroller family 32K OTP, 512 B RAM, watchdog, 2 UARTs

| NAME             | DESCRIPTION                                                                | SFR<br>ADDRESS | MSB          |              | BIT FUN      |              | AND ADD      | RESSES       |             | LSB          | RESET<br>VALUE |

|------------------|----------------------------------------------------------------------------|----------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|--------------|----------------|

|                  |                                                                            |                | 39F          | 39E          | 39D          | 39C          | 39B          | 39A          | 399         | 398          |                |

| P3*              | Port 3                                                                     | 433            | RD           | WR           | T1           | Т0           | INT1         | INT0         | TxD0        | RxD0         | FF             |

| P0CFGA           | Port 0 configuration A                                                     | 470            |              |              |              |              |              |              |             |              | Note 5         |

| P1CFGA           | Port 1 configuration A                                                     | 471            |              |              |              |              |              |              |             |              | Note 5         |

| P2CFGA           | Port 2 configuration A                                                     | 472            |              |              |              |              |              |              |             |              | Note 5         |

| P3CFGA           | Port 3 configuration A                                                     | 473            |              |              |              |              |              |              |             |              | Note 5         |

| P0CFGB           | Port 0 configuration B                                                     | 4F0            |              |              |              |              |              |              |             |              | Note 5         |

| P1CFGB           | Port 1 configuration B                                                     | 4F1            |              |              |              |              |              |              |             |              | Note 5         |

| P2CFGB           | Port 2 configuration B                                                     | 4F2            |              |              |              |              |              |              |             |              | Note 5         |

| P3CFGB           | Port 3 configuration B                                                     | 4F3            |              |              |              |              |              |              |             |              | Note 5         |

|                  |                                                                            |                | 227          | 226          | 225          | 224          | 223          | 222          | 221         | 220          | 1              |

| PCON*            | Power control register                                                     | 404            | —            | —            | —            | —            | —            | —            | PD          | IDL          | 00             |

|                  |                                                                            |                | 20F          | 20E          | 20D          | 20C          | 20B          | 20A          | 209         | 208          | 1              |

| PSWH*            | Program status word (high byte)                                            | 401            | SM           | TM           | RS1          | RS0          | IM3          | IM2          | IM1         | IM0          | Note 2         |

|                  |                                                                            |                | 207          | 206          | 205          | 204          | 203          | 202          | 201         | 200          | 1              |

| PSWL*            | Program status word (low byte)                                             | 400            | С            | AC           | —            | —            | —            | V            | N           | Z            | Note 2         |

|                  |                                                                            |                | 217          | 216          | 215          | 214          | 213          | 212          | 211         | 210          | 1              |

| PSW51*           | 80C51 compatible PSW                                                       | 402            | С            | AC           | F0           | RS1          | RS0          | V            | F1          | Р            | Note 3         |

| RTH0             | Timer 0 extended reload,<br>high byte                                      | 455            |              |              |              |              |              |              |             |              | 00             |

| RTH1             | Timer 1 extended reload,<br>high byte                                      | 457            |              |              |              |              |              |              |             |              | 00             |

| RTL0             | Timer 0 extended reload, low byte                                          | 454            |              |              |              |              |              |              |             |              | 00             |

| RTL1             | Timer 1 extended reload, low byte                                          | 456            |              |              | 0.05         | 004          |              |              | 004         |              | 00             |

| 00001            |                                                                            | 100            | 307          | 306          | 305          | 304          | 303          | 302          | 301         | 300          | -              |

| S0CON*           | Serial port 0 control register                                             | 420            | SM0_0<br>30F | SM1_0<br>30E | SM2_0<br>30D | REN_0<br>30C | TB8_0<br>30B | RB8_0<br>30A | TI_0<br>309 | RI_0<br>308  | 00             |

| S0STAT*          | Serial port 0 extended status                                              | 421            | 30F          | 30E          | 300          | 300          | FE0          | BR0          | OE0         | STINT0       | 00             |

| SOBUF            | Serial port 0 buffer register                                              | 460            |              |              |              |              | TLO          | BILO         | OLU         | Onitro       | x              |

| SOADDR           | Serial port 0 address register                                             | 461            |              |              |              |              |              |              |             |              | 00             |

| S0ADEN           | Serial port 0 address enable register                                      | 462            |              |              |              |              |              |              |             |              | 00             |

|                  |                                                                            |                | 327          | 326          | 325          | 324          | 323          | 322          | 321         | 320          |                |

| S1CON*           | Serial port 1 control register                                             | 424            | SM0_1        | SM1_1        | SM2_1        | REN_1        | TB8_1        | RB8_1        | TI_1        | RI_1         | 00             |

|                  |                                                                            |                | 32F          | 32E          | 32D          | 32C          | 32B          | 32A          | 329         | 328          | ]              |

| S1STAT*          | Serial port 1 extended status                                              | 425            | —            |              |              |              | FE1          | BR1          | OE1         | STINT1       | 00             |

| S1BUF            | Serial port 1 buffer register                                              | 464            |              |              |              |              |              |              |             |              | x              |

| S1ADDR<br>S1ADEN | Serial port 1 address register<br>Serial port 1 address enable<br>register | 465<br>466     |              |              |              |              |              |              |             |              | 00<br>00       |

| SCR              | System configuration register                                              | 440            | _            | _            | - 1          |              | PT1          | PT0          | СМ          | PZ           | 00             |

|                  |                                                                            |                | 21F          | 21E          | 21D          | 21C          | 21B          | 21A          | 219         | 218          | 1              |

| SSEL*            | Segment selection register                                                 | 403            | ESWEN        | R6SEG        | R5SEG        | R4SEG        | R3SEG        | R2SEG        | R1SEG       | <b>R0SEG</b> | 00             |

| SWE              | Software Interrupt Enable                                                  | 47A            | _            | SWE7         | SWE6         | SWE5         | SWE4         | SWE3         | SWE2        | SWE1         | 00             |

### XA-G37 TIMER/COUNTERS

The XA has two standard 16-bit enhanced Timer/Counters: Timer 0 and Timer 1. Additionally, it has a third 16-bit Up/Down timer/counter, T2. A central timing generator in the XA core provides the time-base for all XA Timers and Counters. The timer/event counters can perform the following functions:

- Measure time intervals and pulse duration

- Count external events

- Generate interrupt requests

- Generate PWM or timed output waveforms

All of the timer/counters (Timer 0, Timer 1 and Timer 2) can be independently programmed to operate either as timers or event counters via the C/T bit in the TnCON register. All timers count up unless otherwise stated. These timers may be dynamically read during program execution.

The base clock rate of all of the timers is user programmable. This applies to timers T0, T1, and T2 when running in timer mode (as opposed to counter mode), and the watchdog timer. The clock driving the timers is called TCLK and is determined by the setting of two bits (PT1, PT0) in the System Configuration Register (SCR). The frequency of TCLK may be selected to be the oscillator input divided by 4 (Osc/4), the oscillator input divided by 16 (Osc/16), or the oscillator input divided by 64 (Osc/64). This gives a range of possibilities for the XA timer functions, including baud rate

generation, Timer 2 capture. Note that this single rate setting applies to all of the timers.

When timers T0, T1, or T2 are used in the counter mode, the register will increment whenever a falling edge (high to low transition) is detected on the external input pin corresponding to the timer clock. These inputs are sampled once every 2 oscillator cycles, so it can take as many as 4 oscillator cycles to detect a transition. Thus the maximum count rate that can be supported is Osc/4. The duty cycle of the timer clock inputs is not important, but any high or low state on the timer clock input pins must be present for 2 oscillator cycles before it is guaranteed to be "seen" by the timer logic.

#### Timer 0 and Timer 1

The "Timer" or "Counter" function is selected by control bits C/T in the special function register TMOD. These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0) in the TMOD register. Timer modes 1, 2, and 3 in XA are kept identical to the 80C51 timer modes for code compatibility. Only the mode 0 is replaced in the XA by a more powerful 16-bit auto-reload mode. This will give the XA timers a much larger range when used as time bases.

The recommended M1, M0 settings for the different modes are shown in Figure 2.

| SCR Ad<br>Not Bit Addressa<br>Reset Value: 00 |                                                                                                                                                                                                      | MSB LSB — PT1 PT0 CM PZ |  |  |  |  |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|--|--|--|

| PT1                                           | PT0                                                                                                                                                                                                  | OPERATING               |  |  |  |  |  |  |  |

|                                               |                                                                                                                                                                                                      | Prescaler selection.    |  |  |  |  |  |  |  |

| 0                                             | 0                                                                                                                                                                                                    | Osc/4                   |  |  |  |  |  |  |  |

| 0                                             | 1                                                                                                                                                                                                    | Osc/16                  |  |  |  |  |  |  |  |

| 1                                             | 0                                                                                                                                                                                                    | Osc/64                  |  |  |  |  |  |  |  |

| 1                                             | 1                                                                                                                                                                                                    | Reserved                |  |  |  |  |  |  |  |

| СМ                                            | CM Compatibility Mode allows the XA to execute most translated 80C51 code on the XA. The XA register file must copy the 80C51 mapping to data memory and mimic the 80C51 indirect addressing scheme. |                         |  |  |  |  |  |  |  |

| PZ                                            |                                                                                                                                                                                                      |                         |  |  |  |  |  |  |  |

Figure 1. System Configuration Register (SCR)

| TMOD Ad<br>Not Bit Addressa<br>Reset Value: 00H                                                                                                                                                |     | MSB<br>GATE C/T                              | MO                                                                                                              | GATE | C/T     | M1 | LSB<br>M0 |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|---------|----|-----------|--|--|--|--|

|                                                                                                                                                                                                |     |                                              | ·                                                                                                               |      |         |    |           |  |  |  |  |

|                                                                                                                                                                                                |     | TIN                                          | IER 1                                                                                                           |      | TIMER 0 |    |           |  |  |  |  |

| GATE Gating control when set. Timer/Counter "n" is enabled only while "INTn" pin is high and<br>"TRn" control bit is set. When cleared Timer "n" is enabled whenever "TRn" control bit is set. |     |                                              |                                                                                                                 |      |         |    |           |  |  |  |  |

|                                                                                                                                                                                                | C/T |                                              | Selector cleared for Timer operation (input from internal system clock.) operation (input from "Tn" input pin). |      |         |    |           |  |  |  |  |

| M1                                                                                                                                                                                             | MO  | OPERATING                                    |                                                                                                                 |      |         |    |           |  |  |  |  |

| 0                                                                                                                                                                                              | 0   | 16-bit auto-reload                           | imer/cou                                                                                                        | nter |         |    |           |  |  |  |  |

| 0                                                                                                                                                                                              | 1   | 16-bit non-auto-rel                          | 16-bit non-auto-reload timer/counter                                                                            |      |         |    |           |  |  |  |  |

| 1                                                                                                                                                                                              | 0   | 8-bit auto-reload timer/counter              |                                                                                                                 |      |         |    |           |  |  |  |  |

| 1                                                                                                                                                                                              | 1   | Dual 8-bit timer mode (timer 0 only) SU00605 |                                                                                                                 |      |         |    |           |  |  |  |  |

Figure 2. Timer/Counter Mode Control (TMOD) Register

For timers T0 or T1 the 13-bit count mode on the 80C51 (current Mode 0) has been replaced in the XA with a 16-bit auto-reload mode. Four additional 8-bit data registers (two per timer: RTHn and RTLn) are created to hold the auto-reload values. In this mode, the TH overflow will set the TF flag in the TCON register and cause both the TL and TH counters to be loaded from the RTL and RTH registers respectively.

These new SFRs will also be used to hold the TL reload data in the 8-bit auto-reload mode (Mode 2) instead of TH.

The overflow rate for Timer 0 or Timer 1 in Mode 0 may be calculated as follows:

Timer\_Rate = Osc / (N \* (65536 - Timer\_Reload\_Value))

where N = the TCLK prescaler value: 4 (default), 16, or 64.

#### Mode 1

Mode 1 is the 16-bit non-auto reload mode.

#### Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of RTLn, which is preset by software. The reload leaves THn unchanged.

Mode 2 operation is the same for Timer/Counter 0.

The overflow rate for Timer 0 or Timer 1 in Mode 2 may be calculated as follows:

Timer\_Rate = Osc / (N \* (256 - Timer\_Reload\_Value))

where N = the TCLK prescaler value: 4, 16, or 64.

#### Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. TL0 uses the Timer 0 control bits: C/T, GATE, TR0, INT0, and TF0. TH0 is locked into a timer function and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

| TCON                       |                                                                                                                                                                                                                                                                 | ess:410 | ſ       | MSB                                                                                                                  |              |             |            |             |             |            | LSB         |          |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|----------------------------------------------------------------------------------------------------------------------|--------------|-------------|------------|-------------|-------------|------------|-------------|----------|

| Bit Address<br>Reset Value |                                                                                                                                                                                                                                                                 |         |         | TF1                                                                                                                  | TR1          | TF0         | TR0        | IE1         | IT1         | IE0        | IT0         |          |

| BIT                        |                                                                                                                                                                                                                                                                 | SYMBOL  | FUNC    | TION                                                                                                                 |              |             |            |             |             |            |             |          |

| тсо                        | TCON.7       TF1       Timer 1 overflow flag. Set by hardware on Timer/Counter overflow.         This flag will not be set if T1OE (TSTAT.2) is set.       Cleared by hardware when processor vectors to interrupt routine, or by clearing the bit in software. |         |         |                                                                                                                      |              |             |            |             |             |            |             |          |

| TCC                        | TCON.6 TR1 Timer 1 Run control bit. Set/cleared by software to turn Timer/Counter 1 on/off.                                                                                                                                                                     |         |         |                                                                                                                      |              |             |            |             |             |            |             |          |

| TCC                        | TCON.5 TF0 Timer 0 overflow flag. Set by hardware on Timer/Counter overflow.<br>This flag will not be set if TOOE (TSTAT.0) is set.<br>Cleared by hardware when processor vectors to interrupt routine, or by clearing the bit in software.                     |         |         |                                                                                                                      |              |             |            |             |             |            |             |          |

| TCC                        | ON.4                                                                                                                                                                                                                                                            | TR0     | Timer ( | 0 Run co                                                                                                             | ntrol bit. S | Set/cleared | d by softw | are to turr | Timer/Co    | ounter 0 o | n/off.      |          |

| TCC                        | ON.3                                                                                                                                                                                                                                                            | IE1     |         |                                                                                                                      |              | by hardw    | are when   | external i  | nterrupt e  | dge detec  | ted.        |          |

| TCC                        | ON.2                                                                                                                                                                                                                                                            | IT1     |         | pt 1 type<br>al interru                                                                                              |              | t. Set/clea | red by so  | ftware to s | pecify fall | ling edge/ | low level t | riggered |

| тсо                        | ON.1                                                                                                                                                                                                                                                            | IE0     |         |                                                                                                                      |              | by hardw    | are when   | external i  | nterrupt e  | dge detec  | ted.        |          |

| TCC                        | ON.0                                                                                                                                                                                                                                                            | IT0     |         | nterrupt 0 Type control bit. Set/cleared by software to specify falling edge/low level riggered external interrupts. |              |             |            |             |             |            |             |          |

|                            |                                                                                                                                                                                                                                                                 |         |         |                                                                                                                      |              |             |            |             |             |            |             | SU00604C |

Figure 3. Timer/Counter Control (TCON) Register

| T2CON Addres                        | ss:418   | MSB                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                               |            |            | LSB       |           |             |              |                |  |  |

|-------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|-----------|-------------|--------------|----------------|--|--|

| Bit Addressable<br>Reset Value: 00H |          | TF2                                                                                                                                                                                                                         | TF2 EXF2 RCLK0 TCLK0 EXEN2                                                                                                                                                                                                                                                                    |            |            |           |           |             | CP or<br>RL2 |                |  |  |

| BIT                                 | SYMBOL   | FUNCTION                                                                                                                                                                                                                    | JNCTION                                                                                                                                                                                                                                                                                       |            |            |           |           |             |              |                |  |  |

| T2CON.7                             | TF2      |                                                                                                                                                                                                                             | ner 2 overflow flag. Set by hardware on Timer/Counter overflow. Must be cleared by software.<br>2 will not be set when RCLK0, RCLK1, TCLK0, TCLK1 or T2OE=1.                                                                                                                                  |            |            |           |           |             |              |                |  |  |

| T2CON.6                             | EXF2     | Timer 2 external flag is set when a capture or reload occurs due to a negative transition on T2EX (and EXEN2 is set). This flag will cause a Timer 2 interrupt when this interrupt is enabled. EXF2 is cleared by software. |                                                                                                                                                                                                                                                                                               |            |            |           |           |             |              |                |  |  |

| T2CON.5                             | RCLK0    | Receive Clock F                                                                                                                                                                                                             | eceive Clock Flag.                                                                                                                                                                                                                                                                            |            |            |           |           |             |              |                |  |  |

| T2CON.4                             | TCLK0    |                                                                                                                                                                                                                             | ransmit Clock Flag. RCLK0 and TCLK0 are used to select Timer 2 overflow rate as a clock source for JART0 instead of Timer T1.                                                                                                                                                                 |            |            |           |           |             |              |                |  |  |

| T2CON.3                             | EXEN2    | Timer 2 external                                                                                                                                                                                                            | enable bit                                                                                                                                                                                                                                                                                    | allows a d | capture or | reload to | occur due | e to a nega | ative trans  | ition on T2EX. |  |  |

| T2CON.2                             | TR2      | Start=1/Stop=0                                                                                                                                                                                                              | control for                                                                                                                                                                                                                                                                                   | Timer 2.   |            |           |           |             |              |                |  |  |

| T2CON.1                             | C2 or T2 | 0=Internal timer                                                                                                                                                                                                            | Timer or counter select.                                                                                                                                                                                                                                                                      |            |            |           |           |             |              |                |  |  |

| T2CON.0                             |          | If CP/RL2 & EXE<br>0, EXEN2=1 auto                                                                                                                                                                                          | Capture/Reload flag.<br>f CP/RL2 & EXEN2=1 captures will occur on negative transitions of T2EX.<br>EXEN2=1 auto reloads occur with either Timer 2 overflows or negative transitions at T2EX.<br>f RCLK or TCLK=1 the timer is set to auto reload on Timer 2 overflow, this bit has no effect. |            |            |           |           |             |              |                |  |  |

|                                     |          |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                               |            |            |           |           |             |              | SU00606        |  |  |

Figure 4. Timer/Counter 2 Control (T2CON) Register

## New Timer-Overflow Toggle Output

In the XA, the timer module now has two outputs, which toggle on overflow from the individual timers. The same device pins that are used for the T0 and T1 count inputs are also used for the new overflow outputs. An SFR bit (TnOE in the TSTAT register) is associated with each counter and indicates whether Port-SFR data or the overflow signal is output to the pin. These outputs could be used in applications for generating variable duty cycle PWM outputs (changing the auto-reload register values). Also variable frequency (Osc/8 to Osc/8,388,608) outputs could be achieved by adjusting the prescaler along with the auto-reload register values. With a 30.0MHz oscillator, this range would be 3.58Hz to 3.75MHz.

#### Timer T2

Timer 2 in the XA is a 16-bit Timer/Counter which can operate as either a timer or as an event counter. This is selected by C/T2 in the special function register T2CON. Upon timer T2 overflow/underflow, the TF2 flag is set, which may be used to generate an interrupt. It can be operated in one of three operating modes: auto-reload (up or down counting), capture, or as the baud rate generator (for either or both UARTs via SFRs T2MOD and T2CON). These modes are shown in Table 1.

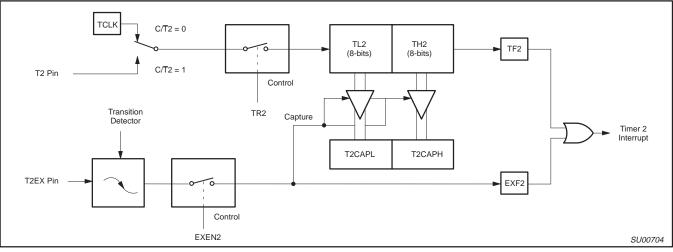

#### Capture Mode

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then timer 2 is a 16-bit timer or counter, which upon overflowing sets bit TF2, the timer 2 overflow bit. This will cause an interrupt when the timer 2 interrupt is enabled.

If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. This will cause an interrupt in the same fashion as TF2 when the Timer 2 interrupt is enabled. The capture mode is illustrated in Figure 7.

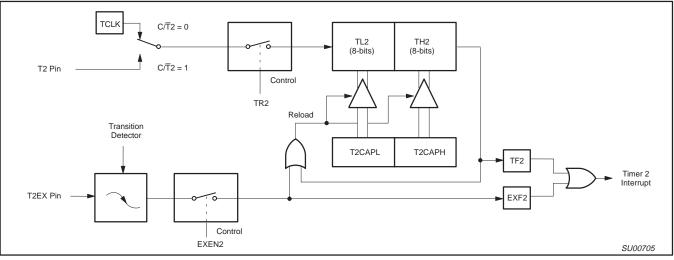

#### Auto-Reload Mode (Up or Down Counter)

In the auto-reload mode, the timer registers are loaded with the 16-bit value in T2CAPH and T2CAPL when the count overflows. T2CAPH and T2CAPL are initialized by software. If the EXEN2 bit in T2CON is set, the timer registers will also be reloaded and the EXF2 flag set when a 1-to-0 transition occurs at input T2EX. The auto-reload mode is shown in Figure 8.

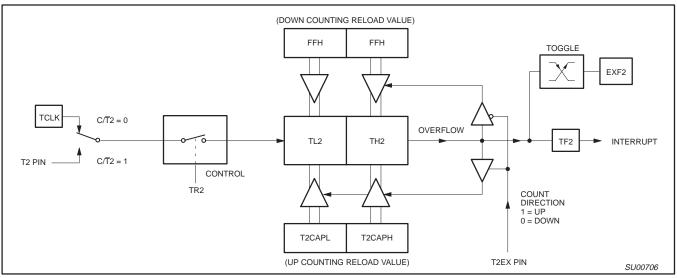

In this mode, Timer 2 can be configured to count up or down. This is done by setting or clearing the bit DCEN (Down Counter Enable) in the T2MOD special function register (see Table 1). The T2EX pin then controls the count direction. When T2EX is high, the count is in the up direction, when T2EX is low, the count is in the down direction.

Figure 8 shows Timer 2, which will count up automatically, since DCEN = 0. In this mode there are two options selected by bit EXEN2 in the T2CON register. If EXEN2 = 0, then Timer 2 counts up to FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This causes the Timer 2 registers to be reloaded with the 16-bit value in T2CAPL and T2CAPH, whose values are preset by software. If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at input T2EX. This transition also sets the EXF2 bit. If enabled, either TF2 or EXF2 bit can generate the Timer 2 interrupt.

In Figure 9, the DCEN = 1; this enables the Timer 2 to count up or down. In this mode, the logic level of T2EX pin controls the direction of count. When a logic '1' is applied at pin T2EX, the Timer 2 will count up. The Timer 2 will overflow at FFFFH and set the TF2 flag, which can then generate an interrupt if enabled. This timer overflow, also causes the 16-bit value in T2CAPL and T2CAPH to be reloaded into the timer registers TL2 and TH2, respectively.

A logic '0' at pin T2EX causes Timer 2 to count down. When counting down, the timer value is compared to the 16-bit value contained in T2CAPH and T2CAPL. When the value is equal, the

Figure 7. Timer 2 in Capture Mode

Figure 8. Timer 2 in Auto-Reload Mode (DCEN = 0)

Figure 9. Timer 2 Auto Reload Mode (DCEN = 1)

## XA 16-bit microcontroller family 32K OTP, 512 B RAM, watchdog, 2 UARTs

#### WATCHDOG TIMER

The watchdog timer subsystem protects the system from incorrect code execution by causing a system reset when the watchdog timer underflows as a result of a failure of software to feed the timer prior to the timer reaching its terminal count. It is important to note that the watchdog timer is running after any type of reset and must be turned off by user software if the application does not use the watchdog function.

## Watchdog Function

The watchdog consists of a programmable prescaler and the main timer. The prescaler derives its clock from the TCLK source that also drives timers 0, 1, and 2. The watchdog timer subsystem consists of a programmable 13-bit prescaler, and an 8-bit main timer. The main timer is clocked (decremented) by a tap taken from one of the top 8-bits of the prescaler as shown in Figure 10. The clock source for the prescaler is the same as TCLK (same as the clock source for the timers). Thus the main counter can be clocked as often as once every 32 TCLKs (see Table 2). The watchdog generates an underflow signal (and is autoloaded from WDL) when the watchdog is at count 0 and the clock to decrement the watchdog occurs. The watchdog is 8 bits wide and the autoload value can range from 0 to FFH. (The autoload value of 0 is permissible since the prescaler is cleared upon autoload).

This leads to the following user design equations. Definitions:  $t_{OSC}$  is the oscillator period, N is the selected prescaler tap value, W is the main counter autoload value, P is the prescaler value from Table 2,  $t_{MIN}$  is the minimum watchdog time-out value (when the autoload value is 0),  $t_{MAX}$  is the maximum time-out value (when the autoload value is FFH),  $t_{D}$  is the design time-out value.

$t_{MIN} = t_{OSC} \times 4 \times 32 \text{ (W} = 0, \text{ N} = 4)$

$t_{MAX} = t_{OSC} \times 64 \times 4096 \times 256 \text{ (W} = 255, \text{ N} = 64)$

$t_D = t_{OSC} \times N \times P \times (W + 1)$

The watchdog timer is not directly loadable by the user. Instead, the value to be loaded into the main timer is held in an autoload register. In order to cause the main timer to be loaded with the appropriate value, a special sequence of software action must take place. This operation is referred to as feeding the watchdog timer.

To feed the watchdog, two instructions must be sequentially executed successfully. No intervening SFR accesses are allowed, so interrupts should be disabled before feeding the watchdog. The instructions should move A5H to the WFEED1 register and then 5AH to the WFEED2 register. If WFEED1 is correctly loaded and WFEED2 is not correctly loaded, then an immediate watchdog reset will occur. The program sequence to feed the watchdog timer or cause new WDCON settings to take effect is as follows:

| clr   | ea          | ; disable global interrupts.  |

|-------|-------------|-------------------------------|

| mov.b | wfeed1,#A5h | ; do watchdog feed part 1     |

| mov.b | wfeed2,#5Ah | ; do watchdog feed part 2     |

| setb  | ea          | ; re-enable global interrupts |

|       |             |                               |

This sequence assumes that the XA interrupt system is enabled and there is a possibility of an interrupt request occurring during the feed sequence. If an interrupt was allowed to be serviced and the service routine contained any SFR access, it would trigger a watchdog reset. If it is known that no interrupt could occur during the feed sequence, the instructions to disable and re-enable interrupts may be removed. The software must be written so that a feed operation takes place every  $t_D$  seconds from the last feed operation. Some tradeoffs may need to be made. It is not advisable to include feed operations in minor loops or in subroutines unless the feed operation is a specific subroutine.

To turn the watchdog timer completely off, the following code sequence should be used:

| mov.b | wdcon,#0    | ; set WD control register to clear WDRUN. |

|-------|-------------|-------------------------------------------|

| mov.b | wfeed1,#A5h | ; do watchdog feed part 1                 |

| mov.b | wfeed2,#5Ah | ; do watchdog feed part 2                 |

This sequence assumes that the watchdog timer is being turned off at the beginning of initialization code and that the XA interrupt system has not yet been enabled. If the watchdog timer is to be turned off at a point when interrupts may be enabled, instructions to disable and re-enable interrupts should be added to this sequence.

## Watchdog Control Register (WDCON)

The reset values of the WDCON and WDL registers will be such that the watchdog timer has a timeout period of  $4\times4096\times t_{OSC}$  and the watchdog is running. WDCON can be written by software but the changes only take effect after executing a valid watchdog feed sequence.

| PRE2 | PRE1 | PRE0 | DIVISOR |  |  |

|------|------|------|---------|--|--|

| 0    | 0    | 0    | 32      |  |  |

| 0    | 0    | 1    | 64      |  |  |

| 0    | 1    | 0    | 128     |  |  |

| 0    | 1    | 1    | 256     |  |  |

| 1    | 0    | 0    | 512     |  |  |

| 1    | 0    | 1    | 1024    |  |  |

| 1    | 1    | 0    | 2048    |  |  |

| 1    | 1    | 1    | 4096    |  |  |

## Table 2. Prescaler Select Values in WDCON

#### Watchdog Detailed Operation

When external RESET is applied, the following takes place:

- Watchdog run control bit set to ON (1).

- Autoload register WDL set to 00 (min. count).

- Watchdog time-out flag cleared.

- Prescaler is cleared.

- Prescaler tap set to the highest divide.

- Autoload takes place.

When coming out of a hardware reset, the software should load the autoload register and then feed the watchdog (cause an autoload).

If the watchdog is running and happens to underflow at the time the external RESET is applied, the watchdog time-out flag will be cleared.

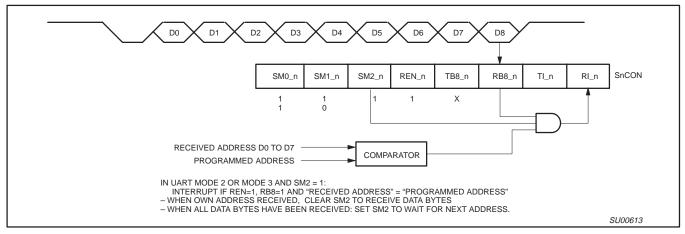

#### Serial Port Control Register

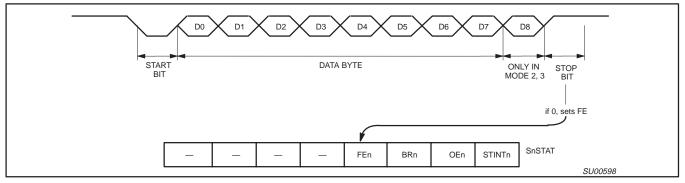

The serial port control and status register is the Special Function Register SnCON, shown in Figure 12. This register contains not only the mode selection bits, but also the 9th data bit for transmit and receive (TB8\_n and RB8\_n), and the serial port interrupt bits (TI\_n and RI\_n).

#### TI Flag

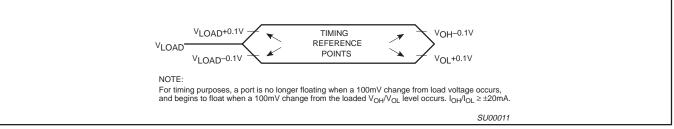

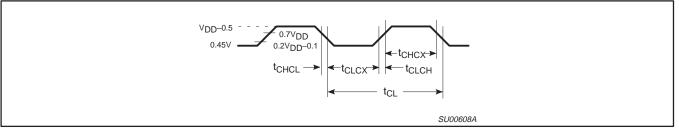

In order to allow easy use of the double buffered UART transmitter feature, the TI\_n flag is set by the UART hardware under two conditions. The first condition is the completion of any byte transmission. This occurs at the end of the stop bit in modes 1, 2, or 3, or at the end of the eighth data bit in mode 0. The second condition is when SnBUF is written while the UART transmitter is idle. In this case, the TI\_n flag is set in order to indicate that the second UART transmitter buffer is still available.