# E·XFLAnalog Devices Inc./Maxim Integrated - <u>MAXQ3100-EMN+ Datasheet</u>

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Obsolete                                                         |

| Core Processor             | -                                                                |

| Core Size                  | 16-Bit                                                           |

| Speed                      | 4MHz                                                             |

| Connectivity               | UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                       |

| Number of I/O              | 27                                                               |

| Program Memory Size        | 16KB (8K x 16)                                                   |

| Program Memory Type        | EEPROM                                                           |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                     |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 80-BQFP                                                          |

| Supplier Device Package    | 80-MQFP (14x20)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/maxq3100-emn |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature Range | 40°C to +85°C           |

|-----------------------------|-------------------------|

| Junction Temperature        |                         |

| Storage Temperature Range   | 65°C to +150°C          |

| Soldering Temperature       | See IPC/JEDEC           |

| <b>C</b> .                  | J-STD-020 Specification |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(DV<sub>DD</sub> = V<sub>RST</sub> to 3.6V, f<sub>32KIN</sub> = 32.768kHz, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                                                                         | MIN  | ТҮР                    | MAX                    | UNITS |

|---------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|------|------------------------|------------------------|-------|

| Digital Supply Voltage                      | DV <sub>DD</sub> |                                                                                                                    | VRST | 3.3                    | 3.6                    | V     |

| Digital Power-Fail Reset                    | V <sub>RST</sub> |                                                                                                                    | 2.34 | 2.5                    | 2.71                   | V     |

| Battery Supply Voltage                      | VBAT             |                                                                                                                    | 2.0  |                        | 3.8                    | V     |

|                                             | IDD1             | /1 mode                                                                                                            |      | 1.9                    | 2.6                    |       |

| Active Current                              | I <sub>DD2</sub> | /2 mode                                                                                                            |      | 1.3                    | 1.8                    |       |

| (Note 2)                                    | I <sub>DD3</sub> | /4 mode                                                                                                            |      | 1.0                    | 1.4                    | mA    |

| (1010 2)                                    | I <sub>DD4</sub> | /8 mode                                                                                                            |      | 0.8                    | 1.2                    |       |

|                                             | I <sub>DD5</sub> | PMM1 mode                                                                                                          |      | 0.7                    | 1.0                    |       |

|                                             |                  | Brownout detector disabled (Note 3), $T_A = +25^{\circ}C$                                                          |      | 1.9                    | 5.0                    |       |

|                                             | ISTOP1           | Brownout detector disabled (Note 3), $T_A = +60^{\circ}C$                                                          |      | 2.1                    | 10.0                   |       |

| Stop-Mode Current                           |                  | Brownout detector disabled (Note 3), $T_A = +85^{\circ}C$                                                          |      | 3.3                    | 35.0                   | μA    |

|                                             | ISTOP2           | Brownout detector enabled (Note 3)                                                                                 |      | 16.3                   | 63.0                   |       |

|                                             | ISTOP3           | Brownout detector enabled, RTC enabled (Note 3)                                                                    |      | 16.4                   | 64.0                   |       |

| ANALOG VOLTAGE COMPARATO                    | OR               |                                                                                                                    |      |                        |                        |       |

| Comparator Input-Voltage Range              | VINPUT           |                                                                                                                    | GND  |                        | DVDD                   | V     |

| Internal Voltage Reference                  | VREF             |                                                                                                                    | 1.15 | 1.25                   | 1.35                   | V     |

| Input Offset Voltage                        | Vos              | (Note 4)                                                                                                           | -10  |                        | +10                    | mV    |

| Input Common-Mode Voltage                   | VCMR             | (Note 4)                                                                                                           | 1    |                        | DVDD                   | V     |

| Common-Mode Rejection Ratio                 | CMMR             | (Note 4)                                                                                                           | 55   |                        |                        | dB    |

| DC Input-Leakage Current                    |                  | $T_A = +25^{\circ}C$ , CMPx pin in tri-state mode                                                                  | -50  |                        | +50                    | nA    |

| Comparator Setup Time                       | tCMP_SETUP       | $f_{SYS} = 4.194 MHz, \Delta V = 20 mV (Note 4)$                                                                   |      | 0.8                    | 1.6                    | μs    |

| Response Time (CMPx Change<br>to CMO Valid) | tCMP_RESP        | $f_{SYS} = 4.194MHz$ , transition CMPx from<br>DGND to DV <sub>DD</sub> in ~2ns, $t_{SYS} = 1/f_{SYS}$<br>(Note 4) |      | 140 +<br>(2 x<br>tsys) | 600 +<br>(2 x<br>tsys) | ns    |

| Current Consumed By<br>Comparator           | IDD_CMP          | Per enabled comparator, CMONx = 1,<br>brownout detector enabled, CMPx pins in<br>tri-state mode                    |      | 18.0                   | 39.0                   | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DV<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $f_{32KIN}$  = 32.768kHz,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                       | SYMBOL            | CONDITIONS                                                                                                | MIN                                           | ТҮР  | MAX                       | UNITS |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|---------------------------|-------|

| DIGITAL I/O                                     | •                 |                                                                                                           |                                               |      |                           |       |

| Input High Voltage (Port 0, 1, 3, RESET)        | VIH1              |                                                                                                           | 0.8 x<br>DV <sub>DD</sub>                     |      | 5.5                       | V     |

| Input High Voltage (Port 2)                     | V <sub>IH2</sub>  |                                                                                                           | 0.8 x<br>DV <sub>DD</sub>                     |      | DV <sub>DD</sub><br>+ 0.3 | V     |

| Input Low Voltage                               | VIL               |                                                                                                           |                                               |      | 0.2 x<br>DV <sub>DD</sub> | V     |

| Output High Voltage (All Ports)                 | V <sub>OH</sub>   | ISOURCE = 3mA                                                                                             | DV <sub>DD</sub> -<br>0.4                     |      | DV <sub>DD</sub>          | V     |

| Output Low Voltage (All Ports,<br>RESET)        | V <sub>OL</sub>   | I <sub>SINK</sub> = 4mA                                                                                   |                                               |      | 0.4                       | V     |

| Input Pullup Current                            | IPULLUP           | $DV_{DD} = 3.6V$ , input mode with weak pullup enabled                                                    | 40                                            | 120  | 250                       | μA    |

| Input Leakage (All Ports)                       | ١L                | Input mode with weak pullup disabled                                                                      | -50                                           |      | +50                       | nA    |

| TEMPERATURE SENSOR                              |                   |                                                                                                           |                                               |      |                           |       |

|                                                 |                   | 10-bit resolution, $f_{SYS} = 4.194MHz$                                                                   |                                               | 12.5 |                           |       |

| Temperature Conversion Time                     | TCONV             | 11-bit resolution, $f_{SYS} = 4.194MHz$                                                                   |                                               | 25   |                           | ms    |

|                                                 | TCONV             | 12-bit resolution, $f_{SYS} = 4.194MHz$                                                                   |                                               | 50   |                           | 1113  |

|                                                 |                   | 13-bit resolution, $f_{SYS} = 4.194MHz$                                                                   |                                               | 100  |                           |       |

| Temperature Sensor Accuracy                     |                   |                                                                                                           |                                               | ±2   |                           | °C    |

| RTC                                             | 1                 | 1                                                                                                         | 1                                             |      |                           |       |

| Battery Supply Current, Battery-<br>Backed Mode | IBAT              | Measured on V <sub>BAT</sub> pin, V <sub>BAT</sub> = 3.6V, $DV_{DD}$ = 0V, RTC enabled                    |                                               | 1.76 | 3.1                       | μA    |

| Battery Supply Leakage Current                  | IBATL             | Measured on V <sub>BAT</sub> pin, V <sub>BAT</sub> = 3.6V, $DV_{DD}$ = 3.6V, RTC enabled                  |                                               | 4    | 200                       | nA    |

| Trimming Resolution                             |                   | One 32.768kHz clock per 10s (Note 4)                                                                      | 3.05                                          |      |                           | ppm   |

| LCD                                             |                   |                                                                                                           |                                               |      |                           |       |

| LCD Supply Voltage                              | VLCD              |                                                                                                           | 2.4                                           |      | DVDD                      | V     |

| LCD Bias Voltage 1                              | VLCD1             | (Note 4)                                                                                                  | V <sub>ADJ</sub> + 2<br>(V <sub>LCD</sub> - V |      |                           | V     |

| LCD Bias Voltage 2                              | V <sub>LCD2</sub> | (Note 4)                                                                                                  | V <sub>ADJ</sub> + 1<br>(V <sub>LCD</sub> - V |      |                           | V     |

| LCD Adjustment Voltage                          | VADJ              | (Note 4)                                                                                                  | 0                                             |      | 0.4 x<br>V <sub>LCD</sub> | V     |

| LCD Digital Operating Current                   | ILCD              | Measured on DV <sub>DD</sub> pin; LCFG = 0xF7,<br>LCRA = 0x1B20, LCDx = 0xFF; LCD pins<br>are unconnected |                                               | 0.1  |                           | μA    |

| LCD Bias Resistor                               | R <sub>LCD</sub>  |                                                                                                           |                                               | 40   |                           | kΩ    |

| LCD Adjust Resistor                             | RLADJ             | LRA3:LRA0 = 1111                                                                                          |                                               | 80   |                           | kΩ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DV<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $f_{32KIN}$  = 32.768kHz,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                  | SYMBOL | CONDITIONS                                                                                           | MIN                         | ТҮР    | MAX                  | UNITS  |

|----------------------------|--------|------------------------------------------------------------------------------------------------------|-----------------------------|--------|----------------------|--------|

|                            |        | Segment is driven at $V_{LCD}$ ; $V_{LCD} = 3V$ ,<br>ISEGxx = -3 $\mu$ A, guaranteed by design       | V <sub>LCD</sub> -<br>0.06  |        | V <sub>LCD</sub>     |        |

| LCD Segment Voltage        |        | Segment is driven at $V_{LCD1}$ ; $V_{LCD1} = 2V$ ,<br>ISEGxx = -3µA, guaranteed by design           | V <sub>LCD1</sub> -<br>0.04 |        | V <sub>LCD1</sub>    | V      |

| LCD Segment Voltage        | VSEGxx | Segment is driven at $V_{LCD2}$ ; $V_{LCD2} = 1V$ ,<br>$I_{SEGxx} = -3\mu A$ , guaranteed by design  | V <sub>LCD2</sub> -<br>0.02 |        | V <sub>LCD2</sub>    | V      |

|                            |        | Segment is driven at $V_{ADJ}$ ; $V_{ADJ} = 0V$ ,<br>I <sub>SEGxx</sub> = +3µA, guaranteed by design | VADJ                        |        | 0.1                  |        |

| CLOCK SOURCES              | ·      |                                                                                                      | •                           |        |                      |        |

| External Crystal Frequency | f32KIN |                                                                                                      |                             | 32.768 |                      | kHz    |

| Internal Clock Frequency   | fCLK   | f <sub>32KIN</sub> = 32.768kHz, DV <sub>DD</sub> = 3.6V                                              | 4.110                       | 4.194  | 4.278                | MHz    |

| System Clock Frequency     | fsys   | f <sub>SYS</sub> = f <sub>CLK</sub> / system clock divisor                                           | fclk /<br>256               |        | fCLK                 |        |

| JTAG-COMPATIBLE PROGRAMM   | /ING   | ·                                                                                                    |                             |        |                      |        |

| TCK Frequency              | fтск   | JTAG programming (Note 4)                                                                            | 0                           |        | f <sub>SYS</sub> / 8 | MHz    |

| MEMORY CHARACTERISTICS     | •      |                                                                                                      |                             |        |                      |        |

| EERROM Write/Erang Cycles  |        | Theta-JA = $+25^{\circ}C$                                                                            | 200,000                     |        |                      | Cycles |

| EEPROM Write/Erase Cycles  |        | Theta-JA = +85°C                                                                                     | 50,000                      |        |                      | Cycles |

| EEPROM Data Retention      |        | Theta-JA = +85°C                                                                                     | 50                          |        |                      | Years  |

|                            |        |                                                                                                      |                             |        |                      |        |

Note 1: Specifications to -40°C are guaranteed by design and are not production tested.

Note 2: Measured on the DV<sub>DD</sub> pin with DV<sub>DD</sub> = 3.6V, V<sub>BAT</sub> = 3.8V, f<sub>32KIN</sub> = 32.768kHz, executing from EEPROM.

**Note 3:** Measured on the DV<sub>DD</sub> pin with DV<sub>DD</sub> = 3.6V, V<sub>BAT</sub> = 3.8V, f<sub>32KIN</sub> = 32.768kHz, all I/O pins disconnected, and not in reset. **Note 4:** Specification guaranteed by design but not production tested.

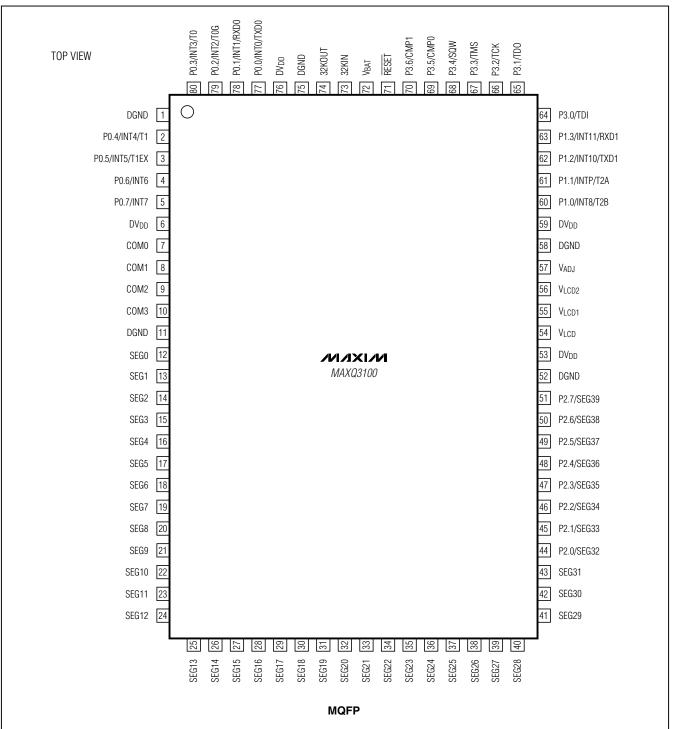

\_Pin Description

| PIN                  | NAME                      |                                     |                                            |                                     | FUNCT                                            | ION                                                                                                                                                 |

|----------------------|---------------------------|-------------------------------------|--------------------------------------------|-------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 11, 52,<br>58, 75 | DGND                      | Digital Gr                          | ound                                       |                                     |                                                  |                                                                                                                                                     |

| 6, 53, 59,<br>76     | DV <sub>DD</sub>          | Digital Su                          | pply Volta                                 | ge (+3.3V)                          |                                                  |                                                                                                                                                     |

|                      |                           | pins funct                          | ion as bid<br>nabled afte                  | rectional I/O p<br>r a reset. All p | oins only. All p                                 | ernal Edge-Selectable Interrupt. These port<br>port pins default to input mode with weak<br>be configured as external interrupt inputs. All<br>are. |

|                      |                           | PIN                                 | N                                          | AME                                 | S                                                | PECIAL/ALTERNATE FUNCTION                                                                                                                           |

|                      |                           | FIN                                 | IN .                                       |                                     | NAME                                             | FUNCTION                                                                                                                                            |

|                      | P0.0-P0.7;                | 77                                  | P0.0                                       | INT0                                | TXD0                                             | Serial Port 0 Transmit                                                                                                                              |

| 2–5, 77–80           | INT0–INT7;<br>TXD0, RXD0, | 78                                  | P0.1                                       | INT1                                | RXD0                                             | Serial Port 0 Receive                                                                                                                               |

|                      | T0G, T0, T1, EX           | 79                                  | P0.2                                       | INT2                                | TOG                                              | Timer 0 Gate Input                                                                                                                                  |

|                      |                           | 80                                  | P0.3                                       | INT3                                | TO                                               | Timer 0 Input                                                                                                                                       |

|                      |                           | 2                                   | P0.4                                       | INT4                                | T1                                               | Timer 1 Input/Output                                                                                                                                |

|                      |                           | 3                                   | P0.5                                       | INT5                                | T1EX                                             | Timer 1 External Capture/Reload Input                                                                                                               |

|                      |                           | 4                                   | P0.6                                       | INT6                                |                                                  | _                                                                                                                                                   |

|                      |                           | 5                                   | P0.7                                       | INT7                                |                                                  | _                                                                                                                                                   |

| 7–10                 | COM0–COM3                 | Dedicated                           | LCD Com                                    | mon-Voltage                         | Outputs                                          |                                                                                                                                                     |

| 12–43                | SEG1-SEG31                |                                     | LCD Driv                                   |                                     |                                                  |                                                                                                                                                     |

|                      |                           | function a                          | s bidirectio                               |                                     |                                                  | <b>Segment-Driver Output.</b> These port pins<br>nent-driver outputs. All alternate functions                                                       |

|                      |                           |                                     |                                            |                                     | S                                                | PECIAL/ALTERNATE FUNCTION                                                                                                                           |

|                      |                           | PIN                                 |                                            | NAME                                | NAME                                             | FUNCTION                                                                                                                                            |

|                      |                           | 44                                  |                                            | P2.0                                | SEG32                                            | LCD Segment 32                                                                                                                                      |

| 44-51                | P2.0–P2.7;<br>SEG32–SEG39 | 45                                  |                                            | P2.1                                | SEG33                                            | LCD Segment 33                                                                                                                                      |

|                      | 3LU32-3LU33               | 46                                  |                                            | P2.2                                | SEG34                                            | LCD Segment 34                                                                                                                                      |

|                      |                           | 47                                  |                                            | P2.3                                | SEG35                                            | LCD Segment 35                                                                                                                                      |

|                      |                           | 48                                  |                                            | P2.4                                | SEG36                                            | LCD Segment 36                                                                                                                                      |

|                      |                           | 49                                  |                                            | P2.5                                | SEG37                                            | LCD Segment 37                                                                                                                                      |

|                      |                           | 50                                  |                                            | P2.6                                | SEG38                                            | _                                                                                                                                                   |

|                      |                           | 51                                  |                                            | P2.7                                | SEG39                                            | _                                                                                                                                                   |

| 54                   | VLCD                      |                                     |                                            | oltage. Highes                      | t LCD drive vo                                   | bltage used in all bias modes. This pin<br>using the LCD display controller.                                                                        |

| 55                   | VLCD1                     | LCD Bias<br>An interna<br>can be us | , Voltage 1<br>al resistor-c<br>ed to chan | . Next highes<br>divider sets th    | LCD drive vo<br>voltage at th<br>ge or drive cap | oltage, used in 1/2 and 1/3 LCD bias modes.<br>his pin. External resistors and capacitors<br>bability at this pin. This pin must be shunted         |

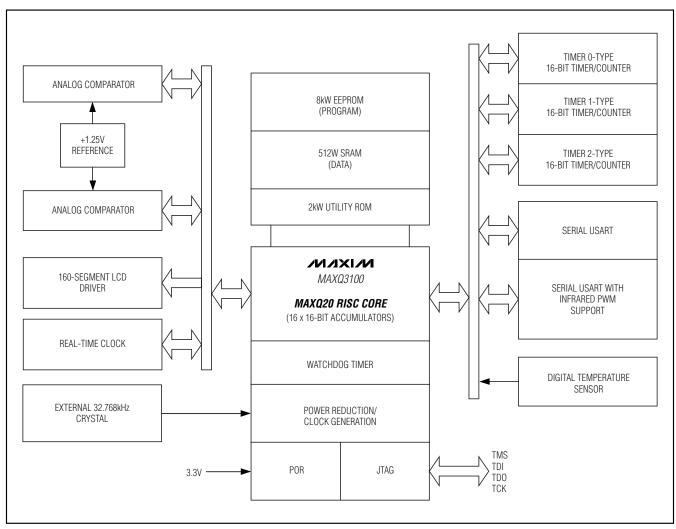

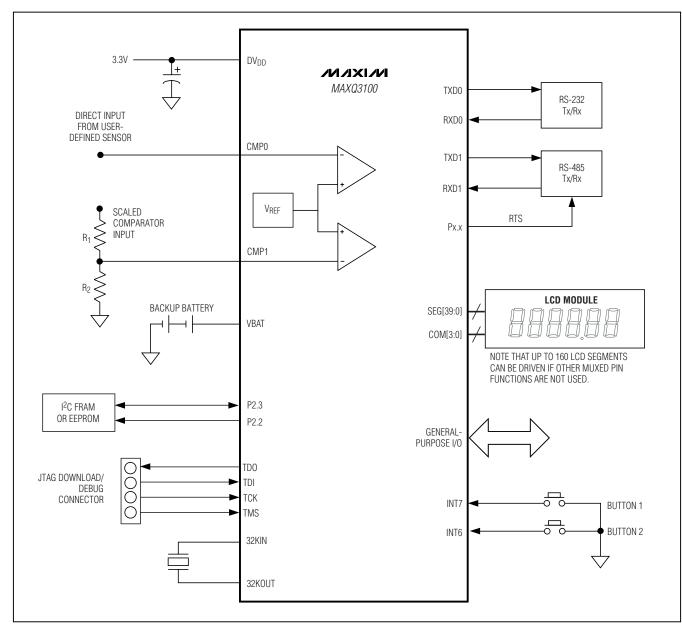

### Functional Diagram

### **Detailed Description**

The following is an introduction to the primary features of the microcontroller. More detailed descriptions of the device features can be found in the data sheets, errata sheets, and user's guides described later in the *Additional Documentation* section.

### \_MAXQ Core Architecture

The MAXQ3100 is a high-performance, CMOS, 16-bit RISC microcontroller with EEPROM and an integrated 160-segment LCD controller. It is structured on a highly advanced, accumulator-based, 16-bit RISC architecture. Fetch and execution operations are completed in one cycle without pipelining, because the instruction contains both the op code and data. The result is a streamlined 4.194 million instructions-per-second (MIPS) microcontroller.

The highly efficient core is supported by a 16-level hardware stack, enabling fast subroutine calling and task switching. Data can be quickly and efficiently manipulated with three internal data pointers. Multiple data pointers allow more than one function to access data memory without having to save and restore data pointers each time. The data pointers can automatically increment or decrement following an operation, eliminating the need for software intervention. As a result, the application speed is greatly increased.

MAXQ3100

### Instruction Set

The instruction set is composed of fixed-length, 16-bit instructions that operate on registers and memory locations. The instruction set is highly orthogonal, allowing arithmetic and logical operations to use any register along with the accumulator. Special-function registers control the peripherals and are subdivided into register modules. The family architecture is modular, so that new devices and modules can reuse code developed for existing products.

The architecture is transport-triggered. This means that writes or reads from certain register locations can also cause side effects to occur. These side effects form the basis for the higher-level op codes defined by the assembler, such as ADDC, OR, JUMP, etc. The op codes are actually implemented as MOVE instructions between certain system register locations, while the assembler handles the encoding, which need not be a concern to the programmer.

The 16-bit instruction word is designed for efficient execution. Bit 15 indicates the format for the source field of the instruction. Bits 0 to 7 of the instruction represent the source for the transfer. Depending on the value of the format field, this can either be an immediate value or a source register. If this field represents a register, the lower four bits contain the module specifier and the upper four bits contain the register index in that module.

Bits 8 to 14 represent the destination for the transfer. This value always represents a destination register, with the lower four bits containing the module specifier and the upper three bits containing the register subindex within that module.

Anytime that it is necessary to directly select one of the upper 24 index locations in a destination module, the prefix register PFX is needed to supply the extra destination bits. This prefix register write is inserted automatically by the assembler and requires only one additional execution cycle.

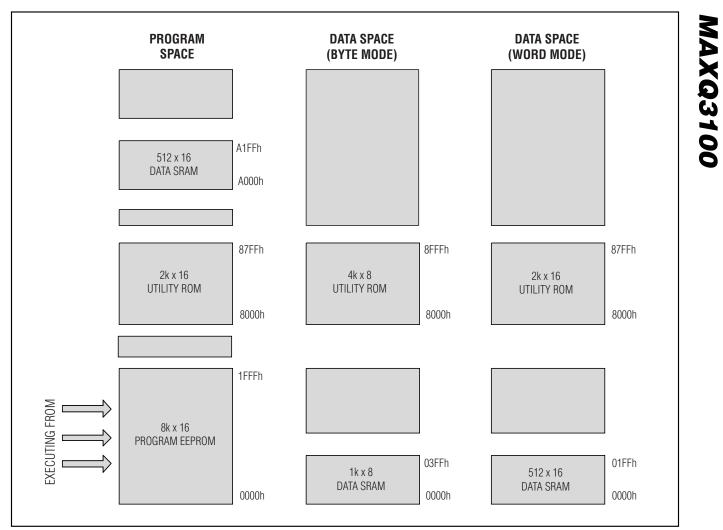

### Memory Organization

The device incorporates several memory areas:

- 2kWords utility ROM

- 8kWords of EEPROM for program storage

- 512 words of SRAM for storage of temporary variables

- 16-level, 16-bit-wide stack memory for storage of program return addresses and general-purpose use

The memory is arranged by default in a Harvard architecture, with separate address spaces for program and

data memory. The configuration of program and data space depends on the current execution location.

- When executing code from EEPROM memory, the SRAM and utility ROM are accessible in data space.

- When executing code from SRAM, the EEPROM and utility ROM are accessible in data space.

- When executing code from the utility ROM, the EEPROM memory and SRAM are accessible in data space.

Refer to the *MAXQ Family User's Guide: MAXQ3100 Supplement* for more details.

In all cases, whichever memory segment is currently being executed from cannot be accessed in data space. To allow the use of lookup tables and similar constructs in the memory, the utility ROM contains a set of lookup and block copy routines (refer to the user's guide supplement for more details).

The incorporation of EEPROM allows the device to be reprogrammed, eliminating the expense of throwing away one-time programmable devices during development and field upgrades. Program memory can be password protected with a 16-word key, denying access to program memory by unauthorized individuals.

### Stack Memory

A 16-bit-wide internal stack provides storage for program return addresses and general-purpose use. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and interrupts serviced. The stack can also be used explicitly to store and retrieve data by using the PUSH, POP, and POPI instructions.

On reset, the stack pointer, SP, initializes to the top of the stack (0Fh). The CALL, PUSH, and interrupt-vectoring operations increment SP, then store a value at the stack location pointed to by SP. The RET, RETI, POP, and POPI operations retrieve the value at the stack location pointed to by SP, and then decrement SP.

### **Utility ROM**

The utility ROM is a 2kWord block of internal ROM memory that defaults to a starting address of 8000h. The utility ROM consists of subroutines that can be called from application software. These include:

- In-system programming (bootloader) over the JTAGcompatible debug port

- In-circuit debug routines

- User-callable routines for in-application flash programming and code space table lookup

Figure 1. Memory Map When Executing from EEPROM

### Table 1. System Register Map

|                   |            |           | MODULE      | NAME (BASE S | PECIFIER)  |             |            |

|-------------------|------------|-----------|-------------|--------------|------------|-------------|------------|

| REGISTER<br>INDEX | AP<br>(8h) | A<br>(9h) | PFX<br>(Bh) | IP<br>(Ch)   | SP<br>(Dh) | DPC<br>(Eh) | DP<br>(Fh) |

| 0h                | AP         | A[0]      | PFX         | IP           | _          |             | _          |

| 1h                | APC        | A[1]      | —           | —            | SP         | —           | —          |

| 2h                | _          | A[2]      | _           | —            | IV         | —           |            |

| 3h                |            | A[3]      |             | —            | _          | Offs        | DP[0]      |

| 4h                | PSF        | A[4]      | —           | —            | _          | DPC         | —          |

| 5h                | IC         | A[5]      | _           | _            | _          | GR          |            |

| 6h                | IMR        | A[6]      | _           | —            | LC[0]      | GRL         | —          |

| 7h                | _          | A[7]      | _           | —            | LC[1]      | BP          | DP[1]      |

| 8h                | SC         | A[8]      | —           | —            | _          | GRS         | —          |

| 9h                | _          | A[9]      | _           | _            | _          | GRH         |            |

| Ah                | _          | A[10]     | _           | —            | —          | GRXL        | —          |

| Bh                | IIR        | A[11]     | —           | —            | —          | BP[offs]    | —          |

| Ch                |            | A[12]     |             |              |            |             |            |

| Dh                |            | A[13]     |             | _            | _          |             |            |

| Eh                | CKCN       | A[14]     |             | —            |            | _           |            |

| Fh                | WDCN       | A[15]     | _           | _            | _          | _           |            |

**Note:** Names that appear in italics indicate that all bits of a register are read-only. Names that appear in bold indicate that a register is 16 bits wide. Registers in module AP are bit addressable.

### Table 2. System Register Bit Functions

| DECISTED |      |      |                |      |              |                               |               | RE   | GISTER     | BIT   |       |       |       |       |         |      |  |  |  |

|----------|------|------|----------------|------|--------------|-------------------------------|---------------|------|------------|-------|-------|-------|-------|-------|---------|------|--|--|--|

| REGISTER | 15   | 14   | 13             | 12   | 11           | 10                            | 9             | 8    | 7          | 6     | 5     | 4     | 3     | 2     | 1       | 0    |  |  |  |

| AP       |      |      |                |      |              |                               |               |      |            | —     | _     |       |       | AP (4 | 1 bits) |      |  |  |  |

| APC      |      |      |                |      |              |                               |               |      | CLR        | IDS   |       |       |       | MOD2  | MOD1    | MOD0 |  |  |  |

| PSF      |      |      |                |      |              |                               |               |      | Z          | S     |       | GPF1  | GPF0  | OV    | С       | Е    |  |  |  |

| IC       |      |      |                |      |              |                               |               |      | _          |       | CGDS  |       |       | —     | INS     | IGE  |  |  |  |

| IMR      |      |      |                |      |              |                               |               |      | IMS        |       |       |       | IM3   | _     | IM1     | IMO  |  |  |  |

| SC       |      |      |                |      |              |                               |               |      | TAP        |       |       |       |       | —     | PWL     | —    |  |  |  |

| IIR      |      |      |                |      |              |                               |               |      | IIS        |       |       |       | 113   | _     | 1       | 110  |  |  |  |

| CKCN     |      |      |                |      |              |                               |               |      | _          |       |       | STOP  | SWB   | PMME  | CD1     | CD0  |  |  |  |

| WDCN     |      |      |                |      |              |                               |               |      | POR        | EWDI  | WD1   | WD0   | WDIF  | WTRF  | EWT     | RWT  |  |  |  |

| A[015]   |      |      |                |      |              |                               |               | A[   | n] (16 bi  | ts)   |       |       |       |       |         |      |  |  |  |

| PFX      |      |      |                |      |              | PFX (16 bits)<br>IP (16 bits) |               |      |            |       |       |       |       |       |         |      |  |  |  |

| IP       |      | -    |                |      |              |                               |               |      |            |       |       |       |       |       |         |      |  |  |  |

| SP       | —    | —    | _              | _    | —            | —                             | _             | _    | _          |       |       |       |       | SP (4 | 1 bits) | 3)   |  |  |  |

| IV       |      |      |                |      |              |                               |               | ľ    | V (16 bits | 3)    |       |       |       |       |         |      |  |  |  |

| LC[0]    |      |      |                |      |              |                               |               | LC   | [0] (16 b  | oits) |       |       |       |       |         |      |  |  |  |

| LC[1]    |      |      |                |      |              |                               |               | LC   | [1] (16 b  | oits) |       |       |       |       |         |      |  |  |  |

| Offs     |      |      |                |      |              |                               | Offs (8 bits) |      |            |       |       |       |       |       |         |      |  |  |  |

| DPC      |      |      | WBS2 WBS1 WBS0 |      |              | SDPS1                         | SDPS0         |      |            |       |       |       |       |       |         |      |  |  |  |

| GR       |      |      |                |      | GR (16 bits) |                               |               | n    |            |       |       |       |       |       |         |      |  |  |  |

| GRL      |      |      |                |      |              |                               | GR.1          | GR.0 |            |       |       |       |       |       |         |      |  |  |  |

| BP       |      | r    |                |      |              | BP (16 bits)                  |               |      | n          |       |       |       |       |       |         |      |  |  |  |

| GRS      | GR.7 | GR.6 | GR.5           | GR.4 | GR.3         | GR.2                          | GR.1          | GR.0 | GR.15      | GR.14 | GR.13 | GR.12 | GR.11 | GR.10 | GR.9    | GR.8 |  |  |  |

| GRH      |      |      |                |      |              |                               |               |      | GR.15      | GR.14 | GR.13 | GR.12 | GR.11 | GR.10 | GR.9    | GR.8 |  |  |  |

| GRXL     | GR.7 | GR.7 | GR.7           | GR.7 | GR.7         | GR.7                          | GR.7          | GR.7 | GR.7       | GR.6  | GR.5  | GR.4  | GR.3  | GR.2  | GR.1    | GR.0 |  |  |  |

| BP[offs] |      |      |                |      |              |                               |               |      | offs] (16  |       |       |       |       |       |         |      |  |  |  |

| DP[0]    |      |      |                |      |              |                               |               | DF   | p[0] (16 b | oits) |       |       |       |       |         |      |  |  |  |

| DP[1]    |      |      |                |      |              |                               |               | DF   | P[1] (16 b | oits) |       |       |       |       |         |      |  |  |  |

| REGISTER |    |    |    |    |    |    |   | REGIST | ER BIT | - |   |   |   |   |   |   |

|----------|----|----|----|----|----|----|---|--------|--------|---|---|---|---|---|---|---|

| REGISTER | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8      | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| AP       |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| APC      |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PSF      |    |    |    |    |    |    |   |        | 1      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| IC       |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| IMR      |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SC       |    |    |    |    |    |    |   |        | 1      | 0 | 0 | 0 | 0 | 0 | S | 0 |

| IIR      |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CKCN     |    |    |    |    |    |    |   |        | 1      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| WDCN     |    |    |    |    |    |    |   |        | S      | S | 0 | 0 | 0 | S | S | 0 |

| A[015]   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PFX      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| IP       | 1  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SP       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| IV       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LC[0]    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LC[1]    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Offs     |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DPC      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| GR       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| GRL      |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| BP       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| GRS      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| GRH      |    |    |    |    |    |    |   |        | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| GRXL     | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| BP[offs] | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DP[0]    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DP[1]    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### **Table 3. System Register Reset Values**

**Note:** Bits marked with an "s" have special behavior upon reset. Refer to the user's guide supplement for this device for more details.

| (continued)                   |  |

|-------------------------------|--|

| <b>Register Bit Functions</b> |  |

| Table 5. Peripheral           |  |

MAXQ3100

| REGISTER |        |        |        |        |        |        | ſ     |       | REGISTER BIT | R BIT   |               | ſ       |         |         |         |         |

|----------|--------|--------|--------|--------|--------|--------|-------|-------|--------------|---------|---------------|---------|---------|---------|---------|---------|

|          | 15     | 14     | 13     | 12     | 1      | 10     | 6     | 8     | 7            | 9       | 5             | 4       | 3       | 2       | -       | 0       |

| T2CNA    |        |        |        |        |        |        |       |       | ET2          | T2OE0   | <b>T2POL0</b> | TR2L    | TR2     | CPRL2   | SS2     | G2EN    |

| T2CFG    |        |        |        |        |        |        |       |       | T2CI         | DIV2    | DIV1          | DIVO    | T2MD    | CCF1    | CCFO    | C/T2    |

| T2V      | T2V.15 | T2V.14 | T2V.13 | T2V.12 | T2V.11 | T2V.10 | T2V.9 | T2V.8 | T2V.7        | T2V.6   | T2V.5         | T2V.4   | T2V.3   | T2V.2   | T2V.1   | T2V.0   |

| T2C      | T2C.15 | T2C.14 | T2C.13 | T2C.12 | T2C.11 | T2C.10 | T2C.9 | T2C.8 | T2C.7        | T2C.6   | TCV.5         | TCV.4   | TCV.3   | TCV.2   | TCV.1   | TCV.0   |

| IRCN     |        |        |        |        |        |        |       |       |              |         |               |         |         | IREN    | IRTX    | IRBB    |

| PD1      |        |        |        |        |        |        |       |       |              | I       | I             |         | PD1.3   | PD1.2   | PD1.1   | PD1.0   |

| T2R      | T2R.15 | T2R.14 | T2R.13 | T2R.12 | T2R.11 | T2R.10 | T2R.9 | T2R.8 | T2R.7        | T2R.6   | T2R.5         | T2R.4   | T2R.3   | T2R.2   | T2R.1   | T2R.0   |

| EIE1     |        |        |        |        |        |        |       |       |              |         |               |         | EX11    | EX10    | EX9     | EX8     |

| EIES1    |        |        |        |        |        |        |       |       | I            | I       | I             |         | IT11    | IT10    | IT9     | IT8     |

| P02      |        |        |        |        |        |        |       |       | PO2.7        | PO2.6   | PO2.5         | PO2.4   | PO2.3   | PO2.2   | PO2.1   | PO2.0   |

| LCFG     |        |        |        |        |        |        |       |       | PCF3         | PCF2    | PCF1          | PCF0    |         | OWS     | MAO     | DPE     |

| LCRA     |        |        |        | DUTY1  | 0λ1υα  | FRM3   | FRM2  | FRM1  | FRMO         |         | LRIG          |         | LRA3    | LRA2    | LRA1    | LRAO    |

| LCD0     |        |        |        |        |        |        |       |       | LCD0.7       | LCD0.6  | LCD0.5        | LCD0.4  | LCD0.3  | LCD0.2  | LCD0.1  | LCD0.0  |

| LCD1     |        |        |        |        |        |        |       |       | LCD1.7       | LCD1.6  | LCD1.5        | LCD1.4  | LCD1.3  | LCD1.2  | LCD1.1  | LCD1.0  |

| LCD2     |        |        |        |        |        |        |       |       | LCD2.7       | LCD2.6  | LCD2.5        | LCD2.4  | LCD2.3  | LCD2.2  | LCD2.1  | LCD2.0  |

| LCD3     |        |        |        |        |        |        |       |       | LCD3.7       | LCD3.6  | LCD3.5        | LCD3.4  | LCD3.3  | LCD3.2  | LCD3.1  | LCD3.0  |

| LCD4     |        |        |        |        |        |        |       |       | LCD4.7       | LCD4.6  | LCD4.5        | LCD4.4  | LCD4.3  | LCD4.2  | LCD4.1  | LCD4.0  |

| PI2      |        |        |        |        |        |        |       |       | P12.7        | PI2.6   | PI2.5         | PI2.4   | PI2.3   | PI2.2   | PI2.1   | P12.0   |

| LCD5     |        |        |        |        |        |        |       |       | LCD5.7       | LCD5.6  | LCD5.5        | LCD5.4  | LCD5.3  | LCD5.2  | LCD5.1  | LCD5.0  |

| LCD6     |        |        |        |        |        |        |       |       | LCD6.7       | LCD6.6  | LCD6.5        | LCD6.4  | LCD6.3  | LCD6.2  | LCD6.1  | LCD6.0  |

| LCD7     |        |        |        |        |        |        |       |       | LCD7.7       | LCD7.6  | LCD7.5        | LCD7.4  | LCD7.3  | LCD7.2  | LCD7.1  | LCD7.0  |

| LCD8     |        |        |        |        |        |        |       |       | LCD8.7       | LCD8.6  | LCD8.5        | LCD8.4  | LCD8.3  | LCD8.2  | LCD8.1  | LCD8.0  |

| LCD9     |        |        |        |        |        |        |       |       | LCD9.7       | LCD9.6  | LCD9.5        | LCD9.4  | LCD9.3  | LCD9.2  | LCD9.1  | LCD9.0  |

| LCD10    |        |        |        |        |        |        |       | _     | LCD10.7      | LCD10.6 | LCD10.5       | LCD10.4 | LCD10.3 | LCD10.2 | LCD10.1 | LCD10.0 |

| LCD11    |        |        |        |        |        |        |       |       | LCD11.7      | LCD11.6 | LCD11.5       | LCD11.4 | LCD11.3 | LCD11.2 | LCD11.1 | LCD11.0 |

| PD2      |        |        |        |        |        |        |       |       | PD2.7        | PD2.6   | PD2.5         | PD2.4   | PD2.3   | PD2.2   | PD2.1   | PD2.0   |

| LCD12    |        |        |        |        |        |        |       |       | LCD12.7      | LCD12.6 | LCD12.5       | LCD12.4 | LCD12.3 | LCD12.2 | LCD12.1 | LCD12.0 |

### LCD14.0 \_CD16.0 \_CD17.0 -CD18.0 -CD19.0 LCD13.0 LCD15.0 TEMPR.0 RTSS.0 RTSH.0 RTSL.0 RSSA.0 RASH.0 RASL.0 PO3.0 RTCE START PD3.0 TRMO PI3.0 BOD 0 LCD13.1 LCD14.4 LCD14.3 LCD14.2 LCD14.1 LCD16.1 LCD17.1 LCD18.1 LCD19.1 TEMPR.1 LCD15.4 LCD15.3 LCD15.2 LCD15.1 CMPOL CMPOL RSSA.1 RASH.1 RASL.1 RTSH.1 PD3.1 PO3.1 TRM1 RESO PI3.1 ADE RTSS.1 RTSL. LCD13.2 LCD17.2 RSSA.2 RASH.2 RASL.2 LCD16.2 LCD18.2 LCD19.2 TEMPR.2 RTSH.2 RTSL.2 PO3.2 RTSS.2 TRM2 PD3.2 CMO CMO PI3.2 ASE RES1 2 LCD17.3 LCD13.4 LCD13.3 LCD16.4 LCD16.3 LCD18.3 LCD19.3 TEMPR.3 RTSH.3 RTSL.3 RSSA.3 RASH.3 RTSS.3 RASL.3 PO3.3 TRM3 BUSY PD3.3 PI3.3 ო LCD17.4 TEMPR.4 LCD18.4 LCD19.4 RTSH.4 RSSA.4 RTSS.4 RTSL.4 RASL.4 PD3.4 PO3.4 TRM4 CMM CMM PI3.4 RDY 4 -CD13.7 LCD13.6 LCD13.5 -CD14.7 LCD14.6 LCD14.5 -CD15.7 LCD15.6 LCD15.5 LCD17.5 \_CD18.5 TEMPR.5 -CD16.7 LCD16.6 LCD16.5 LCD19.5 RTSH.5 RTSL.5 RSSA.5 RTSS.5 ŝ PO3.5 RDYE PD3.5 PI3.5 TRM5 CMF CMF RASL. ŝ LCD17.6 LCD18.6 LCD19.6 TEMPR.5 RTSS.6 RTSH.6 RTSL.6 RSSA.6 œ. PD3.6 PO3.6 TRM6 ALDF CMIE CMIE PI3.6 TPIE RASL. ശ REGISTER BIT LCD17.7 \_CD19.7 TEMPR.7 \_CD18.7 RSSA.7 RTSH.7 RASL.7 CMON RSTL.7 CMON RTSS.7 TSGN ALSF TPIF RASL. 8 TEMPR .8 SQE RTSL. 8 RSSA. 8 RTSH. 8 œ TEMPR .9 RASL. 9 RTSL. 9 RSSA. 9 RTSH. 9 6 Ŀ TEMPR .10 RASL. 10 RSSA. 10 RTSH. 10 RTSL. 10 10 1 TEMPR .11 RSSA. 11 RTSH. 11 RTSL. 11 RASL. 11 11 TEMPR .12 RTSH. 12 RASL. 12 RTSL. 12 RSSA. 12 12 TEMPR .13 RTSH. 13 RSSA. 13 RASL. 13 RTSL. 13 13 TEMPR .14 RASL. 14 RSTL. RSSA. 14 RTSH. 14 14 44 TEMPR .15 RTSH. 15 RTSL. 15 RSSA. 15 RASL. 15 МШ 15 REGISTER LCD13 LCD14 LCD15 LCD16 LCD18 LCD19 TEMPR LCD17 TPCFG RTRM CCNO PWCN RCNT CCN1 RASH PO3 RTSS RTSH RSSA RASL PD3 RTSL ЫЗ

**Mixed-Signal Microcontroller with Analog**

Comparators, LCD, and RTC

# Table 5. Peripheral Register Bit Functions (continued)

MAXQ3100

| REGISTER | REGISTER BIT |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|--------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          | 15           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PO0      |              |    |    |    |    |    |   |   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| SCON0    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SBUF0    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| TOCN     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| TOL      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1CN     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1MD     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIF0     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PI0      |              |    |    |    |    |    |   |   | S | S | S | S | s | S | S | s |

| SMD0     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PR0      | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ТОН      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1L      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1H      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1CL     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T1CH     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PD0      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIE0     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIES0    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PO1      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| SCON1    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SBUF1    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2CNB    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2H      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2RH     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2CH     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIF1     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PI1      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | S | S | S | S |

| SMD1     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PR1      | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2CNA    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2CFG    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2V      | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2C      | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| IRCN     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PD1      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| T2R      | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIE1     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| EIES1    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PO2      |              |    |    |    |    |    |   |   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| LCFG     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Note: Bits marked with an "s" have special behavior upon reset. Refer to the user's guide supplement for this device for more details.

| REGISTER | REGISTER BIT |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|--------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| REGISTER | 15           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LCRA     | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD0     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD1     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD2     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD3     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD4     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PI2      |              |    |    |    |    |    |   |   | S | S | S | S | S | S | s | S |

| LCD5     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD6     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD7     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD8     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD9     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD10    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD11    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PD2      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD12    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD13    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD14    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD15    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD16    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD17    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD18    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| LCD19    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PO3      |              |    |    |    |    |    |   |   | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| RTRM     |              |    |    |    |    |    |   |   | 0 | 0 | S | S | S | S | S | S |

| RCNT     | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | S |

| CCN0     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CCN1     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| TEMPR    | S            | S  | S  | S  | S  | S  | S | S | s | S | S | S | S | S | s | S |

| TPCFG    |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PI3      |              |    |    |    |    |    |   |   | 0 | S | S | S | S | S | S | S |

| RTSS     |              |    |    |    |    |    |   |   | S | S | S | S | S | S | S | S |

| RTSH     | S            | S  | S  | S  | S  | S  | S | S | S | S | S | S | S | S | S | S |

| RTSL     | S            | S  | S  | S  | S  | S  | S | S | S | S | S | S | S | S | S | S |

| RSSA     | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| RASH     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| RASL     | 0            | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PWCN     |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | S |

| PD3      |              |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### Table 6. Peripheral Register Bit Reset Values (continued)

Note: Bits marked with an "s" have special behavior upon reset. Refer to the user's guide supplement for this device for more details.

### Real-Time Clock

A binary real-time clock keeps the time of day in absolute seconds with 1/256-second resolution. The 32-bit second counter can count up to approximately 136 years and be translated to calendar format by the application software. A time-of-day alarm and independent subsecond alarm can cause an interrupt or wake the device from stop mode.

The independent subsecond alarm runs from the same RTC, and allows the application to perform periodic interrupts up to 8 seconds with a granularity of approximately 3.9ms. This creates an additional timer that can be used to measure long periods without performance degradations. Traditionally, long time periods have been measured using multiple interrupts from shorter programmable timers. Each timer interrupt required servicing, with each accompanying interruption slowing system operation. By using the RTC subsecond timer as a long-period timer, only one interrupt is needed, eliminating the performance hit associated with using a shorter timer.

Higher accuracy can be obtained by using the useraccessible digital RTC trim function. This feature allows the designer to fine tune the RTC timing to compensate for crystal inaccuracies and any unintended boardlevel effects that could cause crystal-frequency drift. The user can enable a 1Hz or 512Hz square-wave output on P3.4. Frequency measurements of these signals can show if there is any deviation from the expected frequency, and writes to the RTC trim register can compensate in increments of 1 to 127 steps, with each step approximately 3.05ppm (30.5µs).

If the V<sub>BAT</sub> pin is not directly tied to the DV<sub>DD</sub> pin, then there may be a short increase in I<sub>DD</sub> while the device is switching between V<sub>BAT</sub> and DV<sub>DD</sub> as the RTC power source. I<sub>DD</sub> can temporarily increase up to 300µA while DV<sub>DD</sub> is rising and in the range 1.05 x V<sub>BAT</sub> < DV<sub>DD</sub> < [(1.05 x V<sub>BAT</sub>) + 200mV]. A similar effect may be observed while V<sub>BAT</sub> is falling and in the range [(0.95 x DV<sub>DD</sub>) - 200mV] < V<sub>BAT</sub> < 0.95 x DV<sub>DD</sub>.

### Programmable Timers

The MAXQ3100 incorporates one instance each of the timer 0, timer 1, and timer 2 peripherals. These timers can be used in counter/timer/capture/compare/PWM functions, allowing precise control of internal and external events. Timer 2 supports optional single-shot, external gating, and polarity control options as well as carrier generation support for infrared transmit/receive functions using serial port 0.

### Timer 0

The timer 0 peripheral includes the following:

- 8-bit autoreload timer/counter

- 13-bit or 16-bit timer/counter

- Dual 8-bit timer/counter

- External pulse counter

### Timer 1

MAXQ3100

The timer 1 peripheral includes the following:

- 16-bit autoreload timer/counter

- 16-bit capture

- 16-bit counter

- Clock generation output

### Timer 2

The timer 2 peripheral includes the following:

- 16-bit autoreload timer/counter

- 16-bit capture

- 16-bit counter

- 8-bit capture and 8-bit timer

- 8-bit counter and 8-bit timer

- Infrared carrier generation support

### Watchdog Timer

An internal watchdog timer greatly increases system reliability. The timer resets the processor if software execution is disturbed. The watchdog timer is a freerunning counter designed to be periodically reset by the application software. If software is operating correctly, the counter is periodically reset and never reaches its maximum count. However, if software operation is interrupted, the timer does not reset, triggering a system reset and optionally a watchdog timer interrupt. This protects the system against electrical noise or electrostatic discharge (ESD) upsets that could cause uncontrolled processor operation. The internal watchdog timer is an upgrade to older designs with external watchdog devices, reducing system cost and simultaneously increasing reliability.

The watchdog timer is controlled through bits in the WDCN register. Its timeout period can be set to one of four programmable intervals ranging from 2<sup>12</sup> to 2<sup>21</sup> system clocks in its default mode, allowing flexibility to support different types of applications. The interrupt occurs 512 system clocks before the reset, allowing the system to execute an interrupt and place the system in a known, safe state before the device performs a total system reset. At 4.194MHz, watchdog timeout periods can be programmed from 976µs to 128s, depending on the system clock mode.

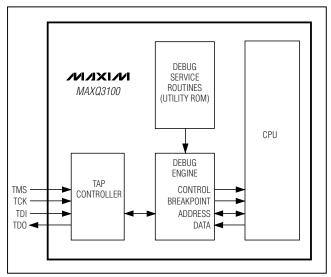

### In-Circuit Debug

Embedded debugging capability is available through the debug port TAP. Embedded debug hardware and embedded ROM firmware provide in-circuit debugging capability to the user application, eliminating the need for an expensive in-circuit emulator. Figure 4 shows a block diagram of the in-circuit debugger. The in-circuit debug features include:

- Hardware debug engine

- Set of registers able to set breakpoints on register, code, or data accesses

- Set of debug service routines stored in the utility ROM

The embedded hardware debug engine is an independent hardware block in the microcontroller. The debug engine can monitor internal activities and interact with selected internal registers while the CPU is executing user code. Collectively, the hardware and software features allow two basic modes of in-circuit debugging:

- Background mode allows the host to configure and set up the in-circuit debugger while the CPU continues to execute the application software at full speed. Debug mode can be invoked from background mode.

- Debug mode allows the debug engine to take control of the CPU, providing read/write access to internal registers and memory, and single-step trace operation.

### Serial Peripherals

The MAXQ3100 incorporates two 8051-style universal synchronous/asynchronous receiver/transmitters. The USARTs allow the device to conveniently communicate with other RS-232 interface-enabled devices, as well as PCs and serial modems when paired with an external RS-232 line driver/receiver. The dual independent USARTs can communicate simultaneously at different baud rates with two separate peripherals. The USART can detect framing errors and indicate the condition through a user-accessible software bit.

Figure 4. In-Circuit Debugger

The time base of the serial ports is derived from either a division of the system clock or the dedicated baud clock generator. The following table summarizes the operating characteristics as well as the maximum baud rate of each mode.

Serial port 0 contains additional functionality to support low-speed infrared transmission in combination with the PWM function of timer 2. When enabled in this mode, the serial port automatically outputs a waveform generated by combining the normal serial port output waveform with the PWM carrier waveform output by timer 2, using a logical OR or logical NOR function. The output of serial port 0 in this mode can be used to drive an infrared LED to communicate using a fixed-frequency carrier modulated signal. Depending on the drive strength required, the output may require a buffer when used for this purpose.

| MODE   | TYPE         | START BITS | DATA BITS | STOP BIT | MAX BAUD RATE AT 4.194MHz |

|--------|--------------|------------|-----------|----------|---------------------------|

| Mode 0 | Synchronous  | —          | 8         |          | 1.05Mbps                  |

| Mode 1 | Asynchronous | 1          | 8         | 1        | 131kbps                   |

| Mode 2 | Asynchronous | 1          | 8 + 1     | 1        | 131kbps                   |

| Mode 3 | Asynchronous | 1          | 8 + 1     | 1        | 131kbps                   |

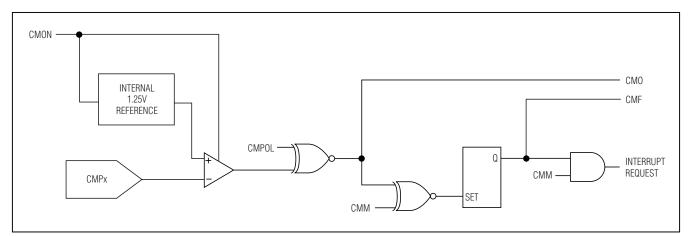

### Analog Comparators

The MAXQ3100 incorporates a pair of 1-bit analog-todigital comparators. The comparator inputs can be connected to a wide range of peripherals, including chemical, motion, or proximity detectors; voltage-supply monitoring; or any other appropriate analog input. The comparator measures the analog inputs against the internal +1.25V reference. The polarity of the internal comparator-output signal can be selected to indicate a value above or below the internal reference. The comparators can be configured to generate an optional interrupt in addition to setting an internal flag when the input is out of range. A combination of the two comparators along with appropriate biasing of an input allows the two comparators to be used as a window comparator. When not in use, the pins associated with the comparator are usable as general-purpose I/O. A useful feature of the comparators is that they can be used to wake the device from stop mode, allowing the device to monitor external voltages while in an ultralow-power mode and only wake when necessary.

### **Temperature Sensor**

The internal temperature sensor has a user-selectable resolution of 10 (0.5°C), 11 (0.25°C), 12 (0.125°C), or 13 (0.0625°C) bits. Higher resolutions require longer conversion times.

Setting the START bit initiates the temperature conversion, and the temperature sensor hardware clears the bit when the conversion is complete. This bit can be polled by software, or, optionally, the temperature conversion complete interrupt can be used to alert the system that the results are ready to be read from the temperature results register (TEMPR).

### Applications Information

### **Grounds and Bypassing**

Careful PC-board layout significantly minimizes crosstalk among the comparator inputs and other digital signals. Keep digital and analog lines separate, and use ground traces as shields between them where possible. Bypass DV<sub>DD</sub> with a capacitor as low as 1µF and keep bypass capacitor leads short for best noise rejection.

This device incorporates both analog and digital components, straddling both the analog and digital ground planes. For increased accuracy, an LC filter can be used to isolate pin 59. This pin powers the analog circuitry, and the additional filtering reduces the noise entering the analog block.

### **Device Applications**

The low-power, high-performance RISC architecture of the MAXQ3100 makes it an excellent fit for many applications that require analog measurements combined with the intelligence of a full-featured microcontroller. Simple voltage-dividers can be used to scale any input into a value in the range of the +1.25V reference. The dual comparators allow the device to function as a simple limit comparator or window comparator in a wide range of analog applications.

Figure 5. Analog Comparator Functional Diagram

### **Additional Documentation**