# E. Renesas Electronics America Inc - UPD70F3801GA-GAM-AX Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                             |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 20MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 34                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 8K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                          |

| Data Converters            | A/D 6x10b; D/A 1x8b                                                                  |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-LQFP Exposed Pad                                                                  |

| Supplier Device Package    | •                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3801ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Generic  | Name                                  |                           |                                       | V850ES/JE3-L                     |                                        |                  |  |  |  |  |

|----------|---------------------------------------|---------------------------|---------------------------------------|----------------------------------|----------------------------------------|------------------|--|--|--|--|

| Part Nur | nber                                  | a PD70F3805               | a PD70F3806                           | a PD70F3807                      | a PD70F3808                            | a PD70F3840      |  |  |  |  |

| Internal | Flash memory                          | 16 KB                     | 32 KB                                 | 64 KB                            | 128 KB                                 | 256 KB           |  |  |  |  |

| memory   |                                       | 8 KB                      | 8 KB                                  | 8 KB                             | 8 KB                                   | 16 KB            |  |  |  |  |

| Memory   | / space                               |                           |                                       | 64 MB                            |                                        |                  |  |  |  |  |

| General  | -purpose register                     | 32 bits ^ 32 reg          | sters                                 |                                  |                                        |                  |  |  |  |  |

|          | Main clock<br>(oscillation frequency) | External clock            |                                       |                                  | clock through med<br>clock through med |                  |  |  |  |  |

|          | Subclock<br>(oscillation frequency)   | Crystal (fr = 32.768 kHz) |                                       |                                  |                                        |                  |  |  |  |  |

|          | Internal oscillator                   | r ≢ 220 kHz (TY           |                                       |                                  |                                        |                  |  |  |  |  |

|          | Minimum instruction execution time    | 50 ns (main cloc          | kxx()f = 20 MHz)                      |                                  |                                        |                  |  |  |  |  |

| I/O port | t                                     | I/O: 50 (5 V toler        | ant/N-ch open-dr                      | ain output selecta               | able: 28)                              |                  |  |  |  |  |

| Timer    | 16-bit TMP                            |                           |                                       | 6 channels                       |                                        |                  |  |  |  |  |

|          | 16-bit TMQ                            | 1 channel                 |                                       |                                  |                                        |                  |  |  |  |  |

|          | 16-bit TMM                            | 1 channel                 |                                       |                                  |                                        |                  |  |  |  |  |

|          | Watch timer                           | 1 channel                 |                                       |                                  |                                        |                  |  |  |  |  |

|          | RTC                                   | 1 channel                 |                                       |                                  |                                        |                  |  |  |  |  |

|          | WDT                                   |                           |                                       | 1 channel                        |                                        |                  |  |  |  |  |

| Real-tim | ne output port                        |                           | 4 bits ^ 1 channe                     | l, 2 bits ^ 1 chann              | nel, or 6 <b>blits</b> hânnel          | l                |  |  |  |  |

| 10-bit A | /D converter                          | 10 channels               |                                       |                                  |                                        |                  |  |  |  |  |

| 8-bit D/ | 'A converter                          |                           |                                       | 1 channel                        |                                        |                  |  |  |  |  |

| Serial   | CSIB                                  |                           |                                       | 3 channels                       |                                        |                  |  |  |  |  |

| interfac | <sup>e</sup> Uarta/CSIB               |                           |                                       | 1 channel                        |                                        |                  |  |  |  |  |

|          | CSIB/I <sup>2</sup> C bus             |                           |                                       | 1 channel                        |                                        |                  |  |  |  |  |

|          | UARTA/I <sup>2</sup> C bus            |                           |                                       | 2 channels                       |                                        |                  |  |  |  |  |

|          | UARTA                                 |                           |                                       | ļ                                |                                        |                  |  |  |  |  |

| DMA co   | ntroller                              | 4 0                       | channels (transfer                    | tangent-chip perip               | heral I/O, internal                    | RAM)             |  |  |  |  |

| Interrup | ot source External                    |                           |                                       | 9 (9 <sup>N</sup> <sup>ote</sup> |                                        |                  |  |  |  |  |

|          | Internal                              |                           |                                       | 48                               |                                        |                  |  |  |  |  |

| Power s  | save function                         |                           | 2/STOP/subclock/<br>2/low-voltage sub | sub-IDLE/<br>clock/low-voltage   | sub-IDLE mode                          |                  |  |  |  |  |

| Reset s  | ource                                 | RESET pin input,          | watchdog timer 2                      | (WDT2), clock mo                 | onitor (CLM), low-                     | voltage detector |  |  |  |  |

| CRC fur  | nction                                | 16-bit error dete         | ction code genera                     | ted for 8-bit unit               | data                                   |                  |  |  |  |  |

Table 1-2. V850ES/JE3-L Product List

RENESAS

(3) V850ES/JE3-L

| Channel | Register name |       |               |         | Bit po  | osition |         |         |               |

|---------|---------------|-------|---------------|---------|---------|---------|---------|---------|---------------|

|         |               | 7     | 6             | 5       | 4       | 3       | 2       | 1       | 0             |

| ТМР0    | TP0CTL0       | TP0CE | 0             | 0       | 0       | 0       | TP0CKS2 | TP0CKS1 | TP0CKS0       |

|         | TP0CTL1       | 0     | TP0EST        | TP0EEE  | 0       | 0       | TP0MD2  | TP0MD1  | TP0MD0        |

|         | TP0IOC0       | 0     | 0             | 0       | 0       | TP0OL1  | TP0OE1  | TP0OL0  | TP0OE0        |

|         | TP0IOC1       | 0     | 0             | 0       | 0       | TP0IS3  | TP0IS2  | TP0IS1  | TP0IS0        |

|         | TP0IOC2       | 0     | 0             | 0       | 0       | TP0EES1 | TP0EES0 | TP0ETS1 | TP0ETS0       |

|         | TP0OPT0       | 0     | 0             | TP0CCS1 | TP0CCS0 | 0       | 0       | 0       | TP00VF        |

| TMP1    | TP1CTL0       | TP1CE | 0             | 0       | 0       | 0       | TP1CKS2 | TP1CKS1 | TP1CKS0       |

|         | TP1CTL1       | 0     | TP1EST        | TP1EEE  | 0       | 0       | TP1MD2  | TP1MD1  | TP1MD0        |

|         | TP1IOC0       | 0     | 0             | 0       | 0       | TP10L1  | TP10E1  | TP1OL0  | TP1OE0        |

|         | TP1IOC1       | 0     | 0             | 0       | 0       | TP1IS3  | TP1IS2  | TP1IS1  | TP1IS0        |

|         | TP1IOC2       | 0     | 0             | 0       | 0       | TP1EES1 | TP1EES0 | TP1ETS1 | TP1ETS0       |

|         | TP1OPT0       | 0     | 0             | TP1CCS1 | TP1CCS0 | 0       | 0       | 0       | TP10VF        |

| TMP2    | TP2CTL0       | TP2CE | 0             | 0       | 0       | 0       | TP2CKS2 | TP2CKS1 | TP2CKS0       |

|         | TP2CTL1       | 0     | TP2EST        | TP2EEE  | 0       | 0       | TP2MD2  | TP2MD1  | TP2MD0        |

|         | TP2IOC0       | 0     | 0             | 0       | 0       | TP2OL1  | TP2OE1  | TP2OL0  | TP2OE0        |

|         | TP2IOC1       | 0     | 0             | 0       | 0       | TP2IS3  | TP2IS2  | TP2IS1  | TP2IS0        |

|         | TP2IOC2       | 0     | 0             | 0       | 0       | TP2EES1 | TP2EES0 | TP2ETS1 | TP2ETS0       |

|         | TP2OPT0       | 0     | 0             | TP2CCS1 | TP2CCS0 | 0       | 0       | 0       | TP2OVF        |

| ТМР3    | TP3CTL0       | TP3CE | 0             | 0       | 0       | 0       | TP3CKS2 | TP3CKS1 | TP3CKS0       |

|         | TP3CTL1       | 0     | <b>TP3EST</b> | 0       | 0       | 0       | TP3MD2  | TP3MD1  | TP3MD0        |

|         | TP3IOC0       | 0     | 0             | 0       | 0       | TP3OL1  | TP3OE1  | 0       | 0             |

|         | TP3IOC1       | 0     | 0             | 0       | 0       | TP3IS3  | TP3IS2  | 0       | 0             |

|         | TP3OPT0       | 0     | 0             | TP3CCS1 | TP3CCS0 | 0       | 0       | 0       | <b>TP3OVF</b> |

| TMP4    | TP4CTL0       | TP4CE | 0             | 0       | 0       | 0       | TP4CKS2 | TP4CKS1 | TP4CKS0       |

|         | TP4CTL1       | 0     | TP4EST        | TP4EEE  | 0       | 0       | TP4MD2  | TP4MD1  | TP4MD0        |

|         | TP4IOC0       | 0     | 0             | 0       | 0       | TP4OL1  | TP4OE1  | TP4OL0  | TP4OE0        |

|         | TP4IOC1       | 0     | 0             | 0       | 0       | TP4IS3  | TP4IS2  | TP4IS1  | TP4IS0        |

|         | TP4IOC2       | 0     | 0             | 0       | 0       | TP4EES1 | TP4EES0 | TP4ETS1 | TP4ETS0       |

|         | TP4OPT0       | 0     | 0             | TP4CCS1 | TP4CCS0 | 0       | 0       | 0       | TP40VF        |

| TMP5    | TP5CTL0       | TP5CE | 0             | 0       | 0       | 0       | TP5CKS2 | TP5CKS1 | TP5CKS0       |

|         | TP5CTL1       | 0     | TP5EST        | TP5EEE  | 0       | 0       | TP5MD2  | TP5MD1  | TP5MD0        |

|         | TP5IOC0       | 0     | 0             | 0       | 0       | TP5OL1  | TP5OE1  | TP5OL0  | TP5OE0        |

|         | TP5IOC1       | 0     | 0             | 0       | 0       | TP5IS3  | TP5IS2  | TP5IS1  | TP5IS0        |

|         | TP5IOC2       | 0     | 0             | 0       | 0       | TP5EES1 | TP5EES0 | TP5ETS1 | TP5ETS0       |

|         | TP5OPT0       | 0     | 0             | TP5CCS1 | TP5CCS0 | 0       | 0       | 0       | TP50VF        |

Remark The TPnCCR0, TPnCCR1, and TPnCNT registers are available for all channels.

#### (2) TMPn control register 1 (TPnCTL1)

The TPnCTL1 register is an 8-bit register that controls the operation of TMPn. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After res    | et: 00H                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                                                                  | Address: ·                                                                                                                 | TP0CTL1                                                                                                                         | FFFFF591                                                                                                | H, TP1CTL                                                                      | 1 FFFFF5                                                                         | 5A1H,                                                                                                  |                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|              |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      | -                                                                                                                          | TP2CTL1                                                                                                                         | FFFFF5B1                                                                                                | H, TP3CTL                                                                      | .1 FFFFF                                                                         | 5C1H,                                                                                                  |                                                                            |

|              |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      | -                                                                                                                          | TP4CTL1                                                                                                                         | FFFFF5D1                                                                                                | H, TP5CTL                                                                      | _1 FFFFF                                                                         | 5E1H                                                                                                   |                                                                            |

|              | 7                                                                                                                                                                                                                                                                                                                                                                                  | <6>                                                                                                                                  | <5>                                                                                                                        | 4                                                                                                                               | 3                                                                                                       | 2                                                                              | 1                                                                                | 0                                                                                                      |                                                                            |

| TPnCTL1      | 0                                                                                                                                                                                                                                                                                                                                                                                  | TPnEST                                                                                                                               | TPnEEE                                                                                                                     | 0                                                                                                                               | 0                                                                                                       | TPnMD2                                                                         | TPnMD1                                                                           | TPnMD0                                                                                                 |                                                                            |

| (n = 0 to 5) |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      |                                                                                                                            |                                                                                                                                 |                                                                                                         |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | TPnEST                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |                                                                                                                            | Softw                                                                                                                           | are trigger                                                                                             | control                                                                        |                                                                                  |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |                                                                                                                            |                                                                                                                                 | -                                                                                                       |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | <ol> <li>Generate a valid signal for external trigger input.</li> <li>In one-shot pulse output mode: A one-shot pulse is output with writing         <ol> <li>to the TPnEST bit as the trigger.</li> <li>In external trigger pulse output mode: A PWM waveform is output with                  writing 1 to the TPnEST bit as the                  trigger.</li> </ol> </li> </ol> |                                                                                                                                      |                                                                                                                            |                                                                                                                                 |                                                                                                         |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | TPnEEE                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |                                                                                                                            | Cour                                                                                                                            | nt clock sele                                                                                           | ection                                                                         |                                                                                  |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  | Disable or                                                                                                                           | peration wit                                                                                                               |                                                                                                                                 | event coun                                                                                              |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | -                                                                                                                                                                                                                                                                                                                                                                                  | (Perform o                                                                                                                           |                                                                                                                            | th the inter                                                                                                                    | nal count c                                                                                             |                                                                                | ed by the                                                                        |                                                                                                        |                                                                            |

|              | 1                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |                                                                                                                            |                                                                                                                                 | event coun<br>dge of the                                                                                |                                                                                | ent count i                                                                      | input                                                                                                  |                                                                            |

|              | -                                                                                                                                                                                                                                                                                                                                                                                  | I                                                                                                                                    | r                                                                                                                          | 1                                                                                                                               |                                                                                                         |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | TPnMD2                                                                                                                                                                                                                                                                                                                                                                             | TPnMD1                                                                                                                               | TPnMD0                                                                                                                     |                                                                                                                                 | Time                                                                                                    | r mode sel                                                                     | ection                                                                           |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                    | 0                                                                                                                          |                                                                                                                                 | timer mode                                                                                              |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                    | 1                                                                                                                          |                                                                                                                                 | event cour                                                                                              |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                    | 0                                                                                                                          |                                                                                                                                 | trigger puls                                                                                            | •                                                                              | node                                                                             |                                                                                                        |                                                                            |

|              | 0                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                    | 1                                                                                                                          |                                                                                                                                 | t pulse out                                                                                             | put mode                                                                       |                                                                                  |                                                                                                        |                                                                            |

|              | 1                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                    | 0                                                                                                                          |                                                                                                                                 | tput mode                                                                                               |                                                                                |                                                                                  |                                                                                                        |                                                                            |

|              | 1                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                    | 1                                                                                                                          |                                                                                                                                 | ning timer                                                                                              |                                                                                | -1-                                                                              |                                                                                                        |                                                                            |

|              | 1                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                    | 0                                                                                                                          |                                                                                                                                 | dth measu                                                                                               | rement mo                                                                      | ae                                                                               |                                                                                                        |                                                                            |

|              |                                                                                                                                                                                                                                                                                                                                                                                    | <ol> <li>The mode<br/>writin</li> <li>Exter<br/>mode</li> <li>Set t</li> <li>opera<br/>be wr<br/>when<br/>mista<br/>again</li> </ol> | TPnEST I<br>or the<br>g 1 to thi<br>nal even<br>e regardle<br>he TPnE<br>ation is st<br>itten whe<br>rewriting<br>kenly pe | bit is val<br>one-sho<br>is bit is ig<br>t count i<br>ess of the<br>EEE and<br>topped (1<br>en the TP<br>g is perfo<br>rformed, | id only i<br>t pulse o<br>nored.<br>nput is s<br>value of<br>TPnMD2<br>PnCTL0.<br>nCE bit =<br>rmed wit | elected i<br>the TPnE<br>to TPn<br>TPnCE bi<br>1.) The<br>h the TPr<br>TPnCE b | ode. In<br>the ex<br>EE bit.<br>MD0 bit<br>it = 0). (T<br>operation<br>nCE bit = | igger puls<br>any oth<br>ternal even<br>s when t<br>he same<br>n is not gu<br>1. If rewr<br>nd then se | er mode,<br>ent count<br>the timer<br>value can<br>uaranteed<br>riting was |

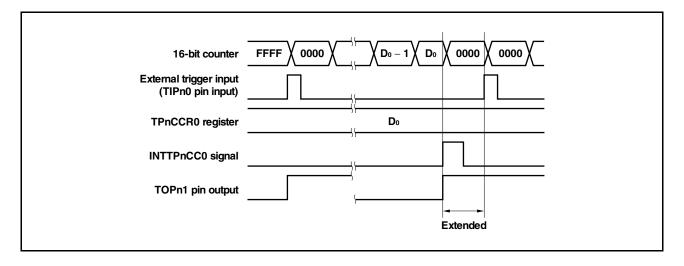

(d) Detection of trigger immediately before or after INTTPnCC0 generation

If the trigger is detected immediately after the INTTPnCC0 signal is generated, the 16-bit counter is cleared to 0000H and continues incrementing. Therefore, the active period of the TOPn1 pin is extended by the amount of time between the generation of the INTTPnCC0 signal and the detection of the trigger.

Figure 6-35. Detection of Trigger Immediately After INTTPnCC0 Signal Was Generated

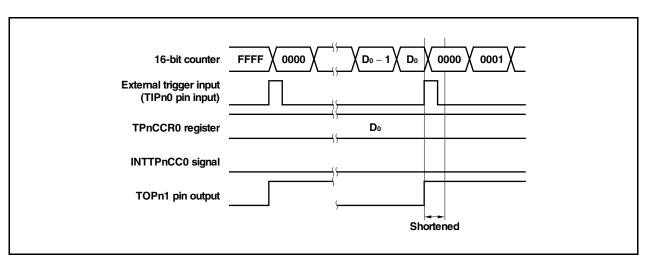

If the trigger is detected immediately before the INTTPnCC0 signal is generated, the INTTPnCC0 signal is not generated. The 16-bit counter is cleared to 0000H, the TOPn1 pin is set to the active level, and the counter continues incrementing. Consequently, the inactive period of the PWM waveform is shortened.

Figure 6-36. Detection of Trigger Immediately Before INTTPnCC0 Signal Is Generated

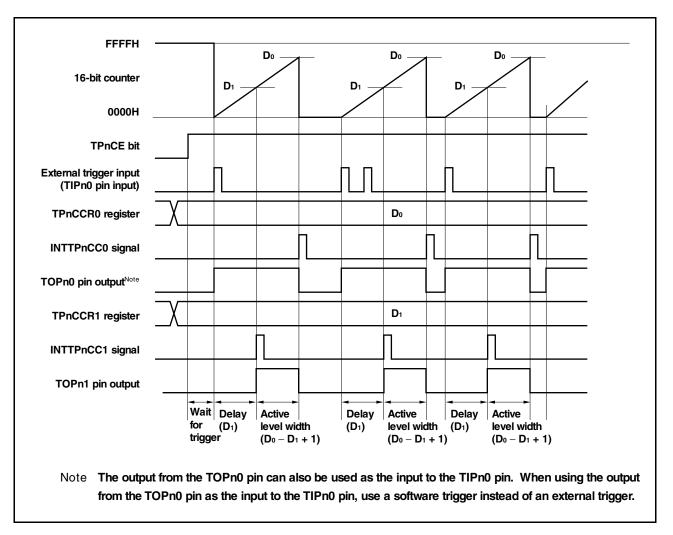

Figure 6-39. Basic Timing of Operations in One-Shot Pulse Output Mode

When the TPnCE bit is set to 1, TMPn waits for a trigger. When the trigger is generated, the 16-bit counter is cleared from FFFFH to 0000H, starts incrementing, and outputs a one-shot pulse from the TOPn1 pin. After the one-shot pulse is output, the 16-bit counter is set to 0000H, stops incrementing, and waits for a trigger. If a trigger is generated again while the one-shot pulse is being output, it is ignored.

The output delay period and active level width of the one-shot pulse can be calculated as follows:

Output delay period = (Set value of TPnCCR1 register) × Count clock cycle Active level width = (Set value of TPnCCR0 register – Set value of TPnCCR1 register + 1) × Count clock cycle

The INTTPnCC0 compare match interrupt request signal is generated when the 16-bit counter increments next time after its value matches the value of the CCR0 buffer register. The INTTPnCC1 compare match interrupt request signal is generated when the value of the 16-bit counter matches the value of the CCR1 buffer register.

Either the valid edge of the external trigger input signal or setting the software trigger (TPnCTL1.TPnEST bit) to 1 is used as the trigger.

#### 7.2.2 Interrupts

The following five types of interrupt signals are used by TMQ0:

#### (1) INTTQ0CC0

This signal is generated when the value of the 16-bit counter matches the value of the CCR0 buffer register, or when a capture signal is input from the TIQ00 pin.

#### (2) INTTQ0CC1

This signal is generated when the value of the 16-bit counter matches the value of the CCR1 buffer register, or when a capture signal is input from the TIQ01 pin.

#### (3) INTTQ0CC2

This signal is generated when the value of the 16-bit counter matches the value of the CCR2 buffer register, or when a capture signal is input from the TIQ02 pin.

#### (4) INTTQ0CC3

This signal is generated when the value of the 16-bit counter matches the value of the CCR3 buffer register, or when a capture signal is input from the TIQ03 pin.

#### (5) INTTQOOV

This signal is generated when the 16-bit counter overflows after incrementing up to FFFFH.

(1) Operations in external event count mode

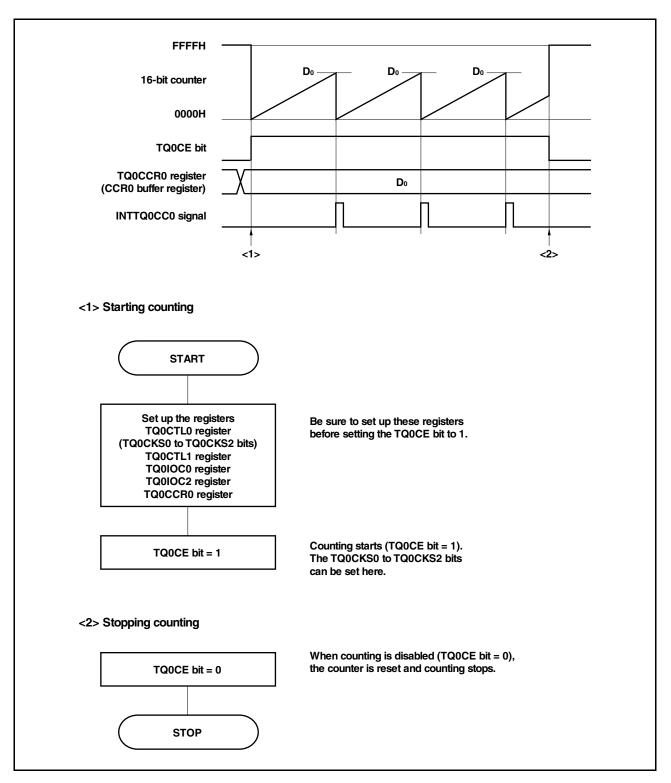

Figure 7-20. Timing and Processing of Operations in External Event Count Mode

(13) Watch error correction register (RC1SUBU)

The RC1SUBU register is an 8-bit register that can be used to correct the watch with high accuracy when the watch is early or late, by changing the value (reference value: 7FFFH) overflowing from the sub-count register (RSUBC) to the second counter register.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

- Remarks 1. The RC1SUBU register can be rewritten only when the real-time counter is set to its initial values. Be sure to see 10.4.1 Initial settings.

- 2. See 10.4.9 Watch error correction example of real-time counter for details of watch error correction.

| After res | et: 00H               | R/W                                          | Address:                                                                                              | FFFFFAD                   | 9H           |              |              |          |  |

|-----------|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|--------------|--------------|--------------|----------|--|

|           | 7                     | 6                                            | 5                                                                                                     | 4                         | 3            | 2            | 1            | 0        |  |

| RC1SUBU   | DEV                   | / F6 F5 F4 F3 F2 F1 F0                       |                                                                                                       |                           |              |              |              |          |  |

|           | DEV                   | DEV Setting of watch error correction timing |                                                                                                       |                           |              |              |              |          |  |

|           | 0                     |                                              | Corrects watch errors when RC1SEC (second counter) is at 00, 20, or<br>40 seconds (every 20 seconds). |                           |              |              |              |          |  |

|           | 1                     |                                              | watch error<br>) seconds).                                                                            | rs when RC                | 1SEC (sec    | ond count    | er) is at 00 | seconds  |  |

|           |                       |                                              |                                                                                                       |                           |              |              |              |          |  |

|           | F6                    |                                              | Se                                                                                                    | etting of wa              | tch error co | prrection va | lue          |          |  |

|           | 0                     | F0 bits (<br>Expressi                        | nts the RC1<br>positive corr<br>on for calcu<br>(Setting val                                          | ection).<br>lating incre  | ment value   | :            | et using th  | ne F5 to |  |

|           | 1                     | F0 bits (I<br>Expressi                       | ents the RC<br>negative cor<br>on for calcu<br>(Inverted va                                           | rection).<br>lating decre | ement value  | e:           | Ū            |          |  |

|           | If the F6<br>performe | to F0 bit va                                 |                                                                                                       | lue of setti              | ng value of  | F5 to F0 b   | ,            |          |  |

### 11.3 Registers

(1) Watchdog timer mode register 2 (WDTM2)

The WDTM2 register sets the overflow time and operation clock of watchdog timer 2. This register can be read or written in 8-bit units. This register can be read any number of times, but it can be written only once following reset release.

Reset sets this register to 67H.

- Caution Accessing the WDTM2 register is prohibited in the following statuses. Moreover, if the system is in the wait status, the only way to cancel the wait status is to execute a reset. For details, see 3.4.9 (1) Accessing specific on-chip peripheral I/O registers.

- When the CPU operates on the subclock and main clock oscillation is stopped

• When the CPU operates on the internal oscillator clock

| WDTM2 |  |

|-------|--|

| WD1W2 |  |

After reset: 67H R/W Address: FFFFF6D0H

| / | 6     | 5     | 4      |        |    |

|---|-------|-------|--------|--------|----|

| 0 | WDM21 | WDM20 | WDCS24 | WDCS23 | i. |

| WDM21 | WDM20 | Selection of operation mode of watchdog timer 2                    |

|-------|-------|--------------------------------------------------------------------|

| 0     | 0     | Stops operation                                                    |

| 0     | 1     | Non-maskable interrupt request mode (generation of INTWDT2 signal) |

| 1     | -     | Reset mode (generation of WDT2RES signal)                          |

WDCS22

WDCS21

WDCS20

## (2) UARTAn control register 1 (UAnCTL1)

The UAnCTL1 register is an 8-bit register that selects the UARTAn base clock. This register can be read or written in 8-bit units. Reset sets this register to 00H.

Caution Clear the UAnCTL0.UAnPWR bit to 0 before rewriting the UAnCTL1 register.

|         | 7       | 6                        | 5        | 4           | 3         | 2                       | 1                    | 0          |

|---------|---------|--------------------------|----------|-------------|-----------|-------------------------|----------------------|------------|

| UAnCTL1 | 0       | 0                        | 0        | 0           | UAnCKS3   | UAnCKS2                 | UAnCKS1              | UAnCKS0    |

|         |         |                          |          |             |           |                         |                      |            |

|         | UAnCKS3 | UAnCKS2                  | UAnCKS1  | UAnCKS0     | B         | ase clock               | (fuclк) <b>selec</b> | ction      |

|         | 0       | 0                        | 0        | 0           | fxx       |                         |                      |            |

|         | 0       | 0                        | 0        | 1           | fxx/2     |                         |                      |            |

|         | 0       | 0                        | 1        | 0           | fxx/4     |                         |                      |            |

|         | 0       | 0                        | 1        | 1           | fxx/8     |                         |                      |            |

|         | 0       | 1                        | 0        | 0           | fxx/16    |                         |                      |            |

|         | 0       | 1                        | 0        | 1           | fxx/32    |                         |                      |            |

|         | 0       | 1                        | 1        | 0           | fxx/64    |                         |                      |            |

|         | 0       | 1                        | 1        | 1           | fxx/128   |                         |                      |            |

|         | 1       | 0                        | 0        | 0           | fxx/256   |                         |                      |            |

|         | 1       | 0                        | 0        | 1           | fxx/512   |                         |                      |            |

|         | 1       | 0                        | 1        | 0           | fxx/1,024 | ł                       |                      |            |

|         | 1       | 0                        | 1        | 1           | External  | clock <sup>Note</sup> ( | ASCKA0 pi            | n)         |

|         |         | Other that               | an above |             | Setting p | orohibited              |                      |            |

|         |         | nly UART/<br>re prohibit |          | ; setting L | JARTA1, L | JART2, Va               | 350ES/JC             | 3-L (40-pi |

Figure 16-18. Continuous Transfer Mode Operation Timing (Master Mode, Transmission Mode)

(4) Start Address Data Start Address Data Stop

| ST                                     | AD6 to AD0                                                                          | R/W                                                        | ĀCK                                                                             | D7 to D0                                              | ACK        | ST       | AD6 to AD0                | R/W            | ĀCK     | D7 to D0 | ACK | SP |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------|------------|----------|---------------------------|----------------|---------|----------|-----|----|--|--|

|                                        |                                                                                     |                                                            | S                                                                               | 51 <b>S</b>                                           | <b>S</b> 2 |          |                           |                | S       | 3        |     |    |  |  |

|                                        | <b>S</b> 1: IICS                                                                    | n registe                                                  | er = 000 <sup>-</sup>                                                           | 1X110B                                                |            |          |                           |                |         |          |     |    |  |  |

| S 2: IICSn register = 0001X000B        |                                                                                     |                                                            |                                                                                 |                                                       |            |          |                           |                |         |          |     |    |  |  |

| <b>S</b> 3: IICSn register = 00000X10B |                                                                                     |                                                            |                                                                                 |                                                       |            |          |                           |                |         |          |     |    |  |  |

| ' 4: IICSn register = 00000001B        |                                                                                     |                                                            |                                                                                 |                                                       |            |          |                           |                |         |          |     |    |  |  |

|                                        | _                                                                                   |                                                            |                                                                                 |                                                       |            |          |                           |                |         |          |     |    |  |  |

|                                        | Remar                                                                               |                                                            | -                                                                               | generated<br>ted only whe                             |            | n hit –  | 1                         |                |         |          |     |    |  |  |

|                                        |                                                                                     |                                                            |                                                                                 | -                                                     |            | 11 Dit – | 1                         |                |         |          |     |    |  |  |

| X: don't care                          |                                                                                     |                                                            |                                                                                 |                                                       |            |          |                           |                |         |          |     |    |  |  |

|                                        |                                                                                     |                                                            | <2> When WTIMn bit = 1 (after restart, address mismatch (= not extension code)) |                                                       |            |          |                           |                |         |          |     |    |  |  |

|                                        | <2> When W                                                                          | 'TIMn t                                                    | oit = 1 (                                                                       | after restart                                         | , addre    | ss mis   | match (= no               | t exten        | sion co | ode))    |     |    |  |  |

|                                        |                                                                                     |                                                            | -                                                                               |                                                       | 1          |          | 1                         |                |         |          |     |    |  |  |

| ST                                     | <2> When W<br>AD6 to AD0                                                            | TIMn b                                                     | ACK                                                                             | D7 to D0                                              | ĀCK        | ST       | match (= no<br>AD6 to AD0 | t exten<br>R/W | ĀCK     | D7 to D0 | ĀCK | SP |  |  |

|                                        | AD6 to AD0                                                                          | R/W                                                        | ACK<br>S                                                                        | D7 to D0                                              | ĀCK        |          | 1                         |                | ĀCK     |          | ĀĊĸ | SP |  |  |

|                                        | AD6 to AD0                                                                          | R/W                                                        | ACK<br>S                                                                        | D7 to D0<br>1<br>1X110B                               | ĀCK        | ST       | 1                         |                | ĀCK     | D7 to D0 | ĀĊĸ | SP |  |  |

|                                        | AD6 to AD0<br><b>S</b> 1: IICS<br><b>S</b> 2: IICS                                  | R/W<br>n registe<br>n registe                              | ACK<br>S<br>er = 000<br>er = 000                                                | D7 to D0<br>1<br>1X110B<br>1XX00B                     | ĀCK        | ST       | 1                         |                | ĀCK     | D7 to D0 | ĀĊĸ | SP |  |  |

|                                        | AD6 to AD0<br><b>S</b> 1: IICS<br><b>S</b> 2: IICS<br><b>S</b> 3: IICS              | R/W<br>n registe<br>n registe<br>n registe                 | ACK<br>S<br>er = 000<br>er = 000<br>er = 000                                    | D7 to D0<br>1<br>1X110B<br>1XX00B<br>00X10B           | ĀCK        | ST       | 1                         |                | ĀCK     | D7 to D0 | ĀĊĸ | SP |  |  |

|                                        | AD6 to AD0<br><b>S</b> 1: IICS<br><b>S</b> 2: IICS                                  | R/W<br>n registe<br>n registe<br>n registe                 | ACK<br>S<br>er = 000<br>er = 000<br>er = 000                                    | D7 to D0<br>1<br>1X110B<br>1XX00B<br>00X10B           | ĀCK        | ST       | 1                         |                | ĀCK     | D7 to D0 | ĀCK | SP |  |  |

|                                        | AD6 to AD0<br><b>S</b> 1: IICS<br><b>S</b> 2: IICS<br><b>S</b> 3: IICS<br>' 4: IICS | R/W<br>n registe<br>n registe<br>n registe                 | ACK<br>S<br>er = 000<br>er = 0000<br>er = 0000<br>er = 0000                     | D7 to D0<br>1<br>1X110B<br>1XX00B<br>00X10B<br>00001B | ĀCK        | ST       | 1                         |                | ĀCK     | D7 to D0 | ĀĊĸ | SP |  |  |

|                                        | AD6 to AD0<br><b>S</b> 1: IICS<br><b>S</b> 2: IICS<br><b>S</b> 3: IICS<br>' 4: IICS | R/W<br>n registe<br>n registe<br>n registe<br>k <b>S</b> : | ACK<br>S<br>er = 000<br>er = 0000<br>er = 0000<br>er = 0000<br>Always           | D7 to D0<br>1<br>1X110B<br>1XX00B<br>00X10B           | S          | ST       | AD6 to AD0                |                | ĀCK     | D7 to D0 | ĀCK | SP |  |  |

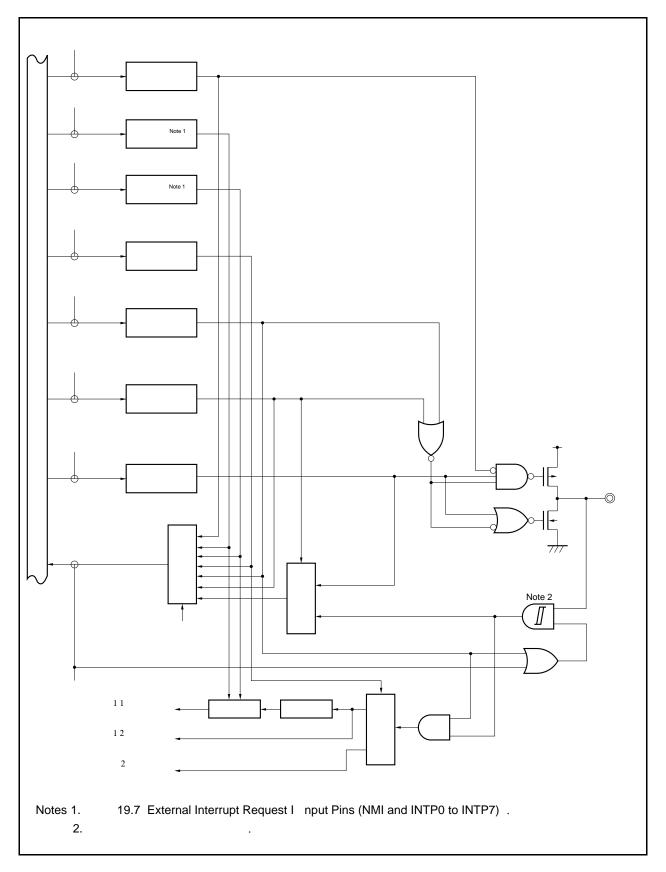

V850ES/JC3-L, V850ES/JE3-L CHAPTER 19 INTERRUPT SERVICING/EXCEPTION PROCESSING FUNCTION

# 29.2.2 Mask function

Only reset signals can be masked.

The maskable signals in the debugger (ID850QB) and the corresponding V850ES/JC3-L and V850ES/JE3-L functions are listed below.

| Maskable Signals in ID850QB | Corresponding V850ES/JC3-L and<br>V850ES/JE3-L Functions       |

|-----------------------------|----------------------------------------------------------------|

| NMIO                        | _                                                              |

| NMI1                        | _                                                              |

| NMI2                        | _                                                              |

| STOP                        | _                                                              |

| HOLD                        | _                                                              |

| RESET                       | Reset signal generation by $\overline{\text{RESET}}$ pin input |

| WAIT                        | _                                                              |

## 31.8.4 UART timing

| Parameter       | Symbol | Conditions                     | MIN. | MAX. | Unit |

|-----------------|--------|--------------------------------|------|------|------|

| Transmit rate   |        | V <sub>DD</sub> = 2.2 to 3.6 V |      | 625  | kbps |

| ASCK0 frequency |        | V <sub>DD</sub> = 2.2 to 3.6 V |      | 5    | MHz  |

|                 |        | V <sub>DD</sub> = 2.7 to 3.6 V |      | 10   | MHz  |

#### 31.8.5 CSIB timing

## (1) Master mode

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{V}_{DD} = \text{EV}_{DD} = \text{AV}_{REF0} = \text{AV}_{REF1}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V}, \text{CL} = 50 \text{ pF})$

| Parameter                                                   | Sy           | mbol | Conditions                                                       | MIN.                         | MAX. | Unit |

|-------------------------------------------------------------|--------------|------|------------------------------------------------------------------|------------------------------|------|------|

| SCKBn cycle time                                            | tkCY1        | <60> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ | 125                          |      | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    | 800                          |      | ns   |

| SCKBn high-level width                                      | tkH1         | <61> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ | tксү1/2 – 8                  |      | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    | <b>t</b> ксү1 <b>/2</b> – 80 |      | ns   |

| SCKBn low-level width                                       | <b>t</b> ĸ∟1 | <62> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ | tксү1/2 – 8                  |      | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    | <b>t</b> ксү1 <b>/2</b> – 80 |      | ns   |

| SIBn setup time (to SCKBn↑)                                 | tsik1        | <63> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ | 27                           |      | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    | 100                          |      | ns   |

| SIBn hold time (from SCKBn↑)                                | tksi1        | <64> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ | 27                           |      | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    | 100                          |      | ns   |

| Delay time from $\overline{SCKBn}\downarrow$ to SOBn output | tkso1        | <65> | $\textbf{2.7 V} \leq \textbf{V}_{\text{DD}} \leq \textbf{3.6 V}$ |                              | 27   | ns   |

|                                                             |              |      | $\textbf{2.2 V} \leq \textbf{V}_{\text{DD}} \textbf{< 2.7 V}$    |                              | 95   | ns   |

Remark **n = 0 to 2, 4**