Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 20MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 34                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | ·                                                                                    |

| RAM Size                   | 8K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                          |

| Data Converters            | A/D 6x10b; D/A 1x8b                                                                  |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-WFQFN Exposed Pad                                                                 |

| Supplier Device Package    | · ·                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3802ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6.6        | Cautions                                                                     | 298 |

|------------|------------------------------------------------------------------------------|-----|

| СНАРТЕР    | R 7 16-BIT TIMER/EVENT COUNTER Q (TMQ)                                       |     |

| 7.1        | Functions                                                                    |     |

| 7.2        | Configuration                                                                |     |

|            | 7.2.1 Pins used by TMQ0                                                      |     |

|            | 7.2.2 Interrupts                                                             |     |

| 7.3        | Registers                                                                    |     |

| 7.4        | Operations                                                                   |     |

|            | 7.4.1 Interval timer mode (TQ0MD2 to TQ0MD0 bits = 000)                      |     |

|            | 7.4.2 External event count mode (TQ0MD2 to TQ0MD0 bits = 001)                |     |

|            | 7.4.3 External trigger pulse output mode (TQ0MD2 to TQ0MD0 bits = 010)       |     |

|            | 7.4.4 One-shot pulse output mode (TQ0MD2 to TQ0MD0 bits = 011)               |     |

|            | 7.4.5 PWM output mode (TQ0MD2 to TQ0MD0 bits = 100)                          |     |

|            | 7.4.6 Free-running timer mode (TQ0MD2 to TQ0MD0 bits = 101)                  |     |

|            | 7.4.7 Pulse width measurement mode (TQ0MD2 to TQ0MD0 bits = 110)             |     |

|            | 7.4.8 Timer output operations                                                | 409 |

| 7.5        | Cautions                                                                     | 410 |

|            |                                                                              |     |

|            | 8 8 16-BIT INTERVAL TIMER M (TMM)                                            |     |

| 8.1        | Features                                                                     |     |

| 8.2        | Configuration                                                                |     |

| 8.3        | Registers                                                                    |     |

| 8.4        | Operation                                                                    |     |

|            | 8.4.1 Interval timer mode                                                    |     |

|            | 8.4.2 Cautions                                                               | 419 |

|            | 9 WATCH TIMER                                                                | 420 |

| 9.1        | Functions                                                                    |     |

| 9.1        | Configuration                                                                |     |

| 9.2<br>9.3 | Control Registers                                                            |     |

| 9.3<br>9.4 | Operation                                                                    |     |

| 5.4        | 9.4.1 Watch timer operations                                                 |     |

|            | 9.4.2 Interval timer operations                                              |     |

| 9.5        | Cautions                                                                     |     |

| 0.0        |                                                                              | 400 |

| CHAPTER    | R 10 REAL-TIME COUNTER                                                       | 431 |

| 10.1       | Functions                                                                    | 431 |

| 10.2       | Configuration                                                                | 432 |

|            | 10.2.1 Pin configuration                                                     | 434 |

|            | 10.2.2 Interrupt functions                                                   | 434 |

| 10.3       | Registers                                                                    | 435 |

| 10.4       | Operation                                                                    | 450 |

|            | 10.4.1 Initial settings                                                      | 450 |

|            | 10.4.2 Rewriting each counter during real-time counter operation             | 451 |

|            | 10.4.3 Reading each counter during real-time counter operation               | 452 |

|            | 10.4.4 Changing INTRTC0 interrupt setting during real-time counter operation | 453 |

|            | 10.4.5 Changing INTRTC1 interrupt setting during real-time counter operation | 454 |

|            | 10.4.6 Initial INTRTC2 interrupt settings                                    |     |

|            | 10.4.7 Changing INTRTC2 interrupt setting during real-time counter operation | 456 |

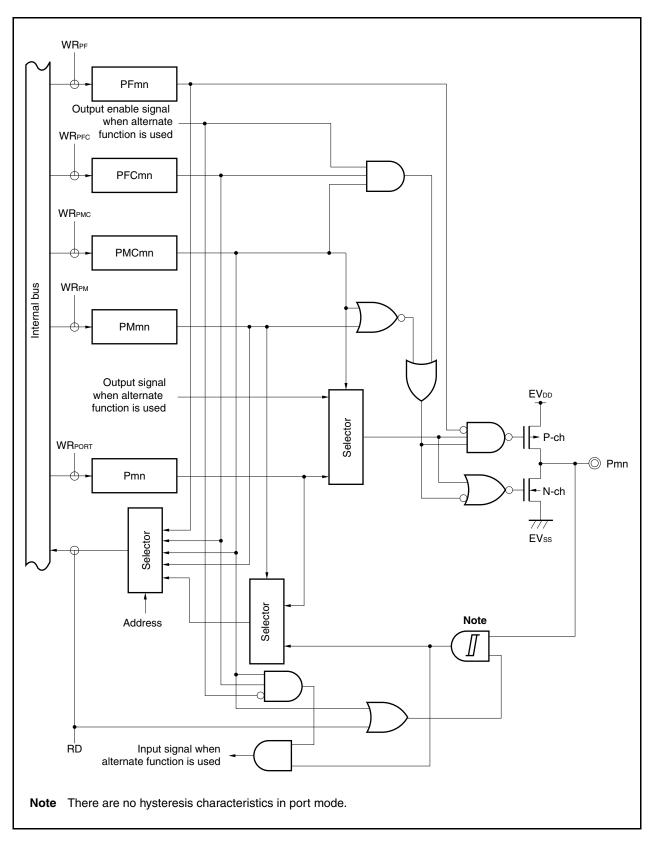

# 2.3 Pin I/O Circuit Types, I/O Buffer Power Supplies, and Connection of Unused Pins

| Pin Alternate Function |                                    | Alternate Function Pin No |                                                  | . I/O Circu |      | Recommended Connection of Unused Pin                                                                                                                                         |

|------------------------|------------------------------------|---------------------------|--------------------------------------------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                    | JC3L<br>(40)              | JC3L<br>(48)                                     | JE3L        | Туре |                                                                                                                                                                              |

| P02                    | 2 NMI                              | NMI 11 13 17 10-D         | Input: Independently connect to EVDD or EVSS via |             |      |                                                                                                                                                                              |

| P03                    | INTP0/ADTRG/RTC1HZ                 | 12                        | 14                                               | 18          |      | a resistor.                                                                                                                                                                  |

| P04                    | INTP1/RTCDIV/RTCCL                 | -                         | -                                                | 19          |      | Output: Leave open.                                                                                                                                                          |

| P05                    | INTP2/DRST                         | 27                        | 31                                               | 41          | 10-N | Input: Independently connect to EVss via a resistor. Fixing to V <sub>DD</sub> level is prohibited.<br>Output: Leave open.<br>Internally pull-down after reset by RESET pin. |

| P06                    | INTP3                              | -                         | -                                                | 20          | 10-D | Input: Independently connect to EVDD or EVSS via                                                                                                                             |

|                        |                                    |                           |                                                  |             |      | a resistor.                                                                                                                                                                  |

| P10                    | ANO0                               |                           | 3                                                | 3           | 12-D | Output: Leave open.<br>Input: Independently connect to AV <sub>REF1</sub> or AV <sub>SS</sub>                                                                                |

| P10                    | ANOU                               | -                         | 3                                                | 3           | 12-0 | Input: Independently connect to AVREF1 or AVss via a resistor.                                                                                                               |

|                        |                                    |                           |                                                  |             |      | Output: Leave open.                                                                                                                                                          |

| P30                    | TXDA0/SOB4                         | _                         | 33                                               | 45          | 10-G | Input: Independently connect to EVDD or EVSS via                                                                                                                             |

|                        | TXDA0                              | 29                        | -                                                | -           |      | a resistor.                                                                                                                                                                  |

| P31                    | RXDA0/INTP7/SIB4                   |                           | 34                                               | 46          | 10-D | Output: Leave open.                                                                                                                                                          |

|                        | RXDA0/INTP7                        | 30                        | -                                                | -           |      |                                                                                                                                                                              |

| P32                    | ASCKA0/SCKB4/TIP00                 | -                         | 35                                               | 47          |      |                                                                                                                                                                              |

| P33                    | TIP01/TOP01                        | _                         | _                                                | 43          |      |                                                                                                                                                                              |

| P34                    | TIP10/TOP10                        | -                         | -                                                | 44          |      |                                                                                                                                                                              |

| P35                    | TIP11/TOP11                        | -                         | -                                                | 23          |      |                                                                                                                                                                              |

| P38                    | TXDA2/SDA00                        | _                         | 18                                               | 26          |      |                                                                                                                                                                              |

| P39                    | RXDA2/SCL00                        | -                         | 19                                               | 27          |      |                                                                                                                                                                              |

| P40                    | SIB0/SDA01                         | 16                        | 20                                               | 28          |      |                                                                                                                                                                              |

| P41                    | SOB0/SCL01                         | 17                        | 21                                               | 29          |      |                                                                                                                                                                              |

| P42                    | SCKB0                              | 18                        | 22                                               | 30          |      |                                                                                                                                                                              |

| P50                    | TIQ01/KR0/TOQ01/RTP00              | 21                        | 25                                               | 35          | 10-D |                                                                                                                                                                              |

| P51                    | TIQ02/KR1/TOQ02/RTP01              | 22                        | 26                                               | 36          |      |                                                                                                                                                                              |

| P52                    | TIQ03/KR2/TOQ03/RTP02/DDI          | 23                        | 27                                               | 37          |      |                                                                                                                                                                              |

| P53                    | SIB2/KR3/TIQ00/TOQ00<br>/RTP03/DDO | 24                        | 28                                               | 38          |      |                                                                                                                                                                              |

| P54                    | SOB2/KR4/RTP04/DCK                 | 25                        | 29                                               | 39          |      |                                                                                                                                                                              |

| P55                    | SCKB2/KR5/RTP05/DMS                | 26                        | 30                                               | 40          |      |                                                                                                                                                                              |

Remark

JC3L (40): V850ES/JC3-L (40-pin products)

JC3L (48): V850ES/JC3-L (48-pin products)

JE3L

: V850ES/JE3-L

Figure 4-15. Block Diagram of Type G-15

## (a) Function as compare register

The TPnCCR1 register can be rewritten even when the TPnCTL0.TPnCE bit = 1.

The set value of the TPnCCR1 register is transferred to the CCR1 buffer register. When the value of the 16-bit counter matches the value of the CCR1 buffer register, a compare match interrupt request signal (INTTPnCC1) is generated. If TOPn1 pin output is enabled at this time, the output of the TOPn1 pin is inverted (For details, see the descriptions of each operating mode.).

## (b) Function as capture register

When the TPnCCR1 register is used as a capture register in the free-running timer mode, the count value of the 16-bit counter is stored in the TPnCCR1 register if the valid edge of the capture trigger input pin (TIPn1 pin) is detected. In the pulse-width measurement mode, the count value of the 16-bit counter is stored in the TPnCCR1 register and the 16-bit counter is cleared (0000H) if the valid edge of the capture trigger input pin (TIPn1) is detected.

Even if the capture operation and reading the TPnCCR1 register conflict, the correct value of the TPnCCR1 register can be read.

The following table shows the functions of the capture/compare register in each mode, and how to write data to the compare register.

| Operation Mode                | Capture/Compare Register | How to Write Compare Register |

|-------------------------------|--------------------------|-------------------------------|

| Interval timer                | Compare register         | Anytime write                 |

| External event counter        | Compare register         | Anytime write                 |

| External trigger pulse output | Compare register         | Batch write                   |

| One-shot pulse output         | Compare register         | Anytime write                 |

| PWM output                    | Compare register         | Batch write                   |

| Free-running timer            | Capture/compare register | Anytime write                 |

| Pulse width measurement       | Capture register         | _                             |

Table 6-4. Function of Capture/Compare Register in Each Mode and How to Write Compare Register

**Remark** For details about anytime write and batch write, see 6.4 (2) Anytime write and batch write.

## (b) Batch write

This writing method is used to transfer data from the TQ0CCR0 to TQ0CCR3 registers to the CCR0 to CCR3 buffer registers all at once while TMQ0 is operating. The data is transferred when the value of the 16-bit counter matches the value of the CCR0 buffer register. Transfer is enabled by writing to the TQ0CCR1 register. Whether transfer of the next data is enabled or not depends on whether the TQ0CCR1 register has been written.

To specify the value of the rewritten TQ0CCR0 to TQ0CCR3 registers as the 16-bit counter compare value (that is, the value to be transferred to the CCR0 to CCR3 buffer registers), the TQ0CCR0 register must be rewritten before the value of the 16-bit counter matches the value of the CCR0 buffer register, and then the TQ0CCR1 register must be written. The value of the TQ0CCR0 to TQ0CCR3 registers is then transferred to the CCR0 to CCR3 buffer registers when the value of the 16-bit counter matches the value of the CCR0 buffer register value of the CCR0 buffer register. Note that even if you wish to rewrite one of the TQ0CCR0, TQ0CCR2 and TQ0CCR3 register values, you must also write the same value to the TQ0CCR1 register (that is, the same value as the value already specified for the TQ0CCR1 register).

# (2) Using pulse width measurement mode

## (a) Clearing the overflow flag (TQ0OVF)

The overflow flag (TQ0OVF) can be cleared to 0 by reading the TQ0OVF bit and, if its value is 1, either clearing the bit to 0 by using the CLR1 instruction or by writing 8-bit data (with bit 0 as "0") to the TQ0OPT0 register.

## 7.4.8 Timer output operations

The following table shows the operations and output levels of the TOQ00 to TOQ03 pins.

| Operation Mode                     | TOQ00 Pin                                               | TOQ01 Pin                     | TOQ02 Pin                     | TOQ03 Pin                     |  |

|------------------------------------|---------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|--|

| Interval timer mode                | Square wave output                                      |                               |                               |                               |  |

| External event count mode          |                                                         | -                             | -                             |                               |  |

| External trigger pulse output mode | Square wave output                                      | External trigger pulse output | External trigger pulse output | External trigger pulse output |  |

| One-shot pulse output mode         |                                                         | One-shot pulse<br>output      | One-shot pulse<br>output      | One-shot pulse<br>output      |  |

| PWM output mode                    |                                                         | PWM output                    | PWM output                    | PWM output                    |  |

| Free-running timer mode            | Square wave output (only when compare function is used) |                               |                               |                               |  |

| Pulse width measurement mode       |                                                         | -                             | _                             |                               |  |

Table 7-8. Timer Output Control in Each Mode

# Table 7-9. Truth Table of TOQ00 to TOQ03 Pins Under Control of Timer Output Control Bits

| TQ0IOC0.TQ0OLm Bit | TQ0IOC0.TQ0OEm Bit | TQ0CTL0.TQ0CE Bit | Level of TOQ0m Pin                                                          |

|--------------------|--------------------|-------------------|-----------------------------------------------------------------------------|

| 0                  | 0                  | ×                 | Low-level output                                                            |

|                    | 1                  | 0                 | Low-level output                                                            |

|                    |                    | 1                 | Low level immediately before counting, high level after counting is started |

| 1                  | 0                  | ×                 | High-level output                                                           |

|                    | 1                  | 0                 | High-level output                                                           |

|                    |                    | 1                 | High level immediately before counting, low level after counting is started |

Remark m = 0 to 3

# 10.2 Configuration

The real-time counter includes the following hardware.

| Item              | Configuration                                 |

|-------------------|-----------------------------------------------|

| Control registers | Real-time counter control register 0 (RC1CC0) |

| -                 | Real-time counter control register 1 (RC1CC1) |

|                   | Real-time counter control register 2 (RC1CC2) |

|                   | Real-time counter control register 3 (RC1CC3) |

|                   | Sub-count register (RC1SUBC)                  |

|                   | Second count register (RC1SEC)                |

|                   | Minute count register (RC1MIN)                |

|                   | Hour count register (RC1HOUR)                 |

|                   | Day count register (RC1DAY)                   |

|                   | Day-of-week count register (RC1WEEK)          |

|                   | Month count register (RC1MONTH)               |

|                   | Year count register (RC1YEAR)                 |

|                   | Watch error correction register (RC1SUBU)     |

|                   | Alarm minute register (RC1ALM)                |

|                   | Alarm hour register (RC1ALH)                  |

|                   | Alarm week register (RC1ALW)                  |

|                   | Prescaler mode register 0 (PRSM0)             |

|                   | Prescaler compare register 0 (PRSCM0)         |

| Table 10-1. Config | guration of | <b>Real-Time</b> | Counter |

|--------------------|-------------|------------------|---------|

|--------------------|-------------|------------------|---------|

# CHAPTER 13 A/D CONVERTER

## 13.1 Overview

The A/D converter of the V850ES/JC3-L and V850ES/JE3-L have a resolution of 10 bits and converts an input analog signal into a digital value.

The number of A/D converter in the V850ES/JC3-L and V850ES/JE3-L are shown below.

| Product Name               | V850ESJC3-L (40-pin)                 | V850ES/JC3-L (48-pin)     | V850ES/JE3-L                         |

|----------------------------|--------------------------------------|---------------------------|--------------------------------------|

| Number of ANI channels (m) | 5 channels (m = 5)                   | 6 channels (m = 6)        | 10 channels (m =10)                  |

| Number of mounted (n)      | ANI0 to ANI4 $(n = 0 \text{ to } 4)$ | ANI0 to ANI5 (n = 0 to 5) | ANI0 to ANI9 $(n = 0 \text{ to } 9)$ |

In this chapter, the number of ANI channels is expressed as m and the number of ANI pins (analog input function pins) is expressed as n.

The A/D converter has the following features.

- O 10-bit resolution

- O Successive approximation method

- O Operating voltage: AVREF0 = 2.7 to 3.6 V

- O Analog input voltage: 0 V to AVREF0

- O The following functions are provided as operation modes.

- Continuous select mode

- Continuous scan mode

- One-shot select mode

- One-shot scan mode

- O The following functions are provided as trigger modes.

- · Software trigger mode

- External trigger mode (external, 1)

- Timer trigger mode

- O Conversion time

- 2.6 to 24  $\mu s@3.0~V \leq AV_{\text{REF0}} \leq 3.6~V$

- 3.9 to 24  $\mu s@2.7~V \leq AV_{\mathsf{REF0}} < 3.0~V$

- O Power-fail monitor function (conversion result compare function)

# 13.2 Functions

## (1) 10-bit resolution A/D conversion

A/D conversion is repeated at a resolution of 10 bits for an analog signal that is input to a channel selected from ANIn. Each time A/D conversion is completed, an interrupt request signal (INTAD) is generated.

## (2) Power-fail detection

This function is used to detect a drop in the battery voltage. The result of A/D conversion (the value of the ADA0CRnH register) is compared with the value of the ADA0PFT register, and the INTAD signal is generated only when the comparison condition specified by the ADA0PFM register is satisfied.

# CHAPTER 15 ASYNCHRONOUS SERIAL INTERFACE A (UARTA)

The number of UARTA channels in the V850ES/JC3-L, V850ES/JE3-L are shown below.

| Product Name       | V850ESJC3-L (40-pin) | V850ES/JC3-L (48-pin) | V850ES/JE3-L     |

|--------------------|----------------------|-----------------------|------------------|

| Number of channels | 2 channels           | 3 channels            | 3 channels       |

|                    | UARTA0, UARTA1       | UARTA0 to UARTA2      | UARTA0 to UARTA2 |

In this chapter, the number of channels is expressed as n.

## 15.1 Features

- O On-chip dedicated baud rate generator

- O Transfer rate: 300 bps to 625 kbps (using dedicated baud rate generator)

- O Full-duplex communication

- O Double buffer configuration Internal UARTAn receive data register (UAnRX)

Internal UARTAn transmit data register (UAnTX)

O Reception error detection function

- Parity error

- Framing error

- Overrun error

O Interrupt sources: 2

- Reception complete interrupt (INTUAnR):

- Transmission enable interrupt (INTUAnT):

This interrupt occurs upon transfer of receive data from the receive shift register to the receive data register after serial transfer completion, in the reception enabled status.

This interrupt occurs upon transfer of transmit data from the transmit data register to the transmit shift register in the transmission enabled status. (Continuous transmission is possible.)

- O Character length: 7, 8 bits

- O Parity function: Odd, even, 0, none

- O Transmission stop bit: 1, 2 bits

- O MSB-/LSB-first transfer selectable

- O Internal digital noise filter

- O Inverted input/output of transmit/receive data possible

- O SBF (Sync Break Field) transmission/reception in the LIN (Local Interconnect Network) communication format

- 13 to 20 bits selectable for SBF transmission

- Recognition of 11 bits or more possible for SBF reception

- SBF reception flag provided

## 15.4 Registers

# (1) UARTAn control register 0 (UAnCTL0)

The UAnCTL0 register is an 8-bit register that controls the UARTAn serial transfer operation. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 10H.

| After re                         | eset: 10H                                                              | R/W A                                                                                            |                                                                                          | A0CTL0 FI<br>A2CTL0 FI                                                                                             |                                                                                           |                                                                                           | ) FFFFFA1                                                                             | 0Н,                                             |

|----------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|

|                                  | <7>                                                                    | <6>                                                                                              | <5>                                                                                      | <4>                                                                                                                | 3                                                                                         | 2                                                                                         | 1                                                                                     | 0                                               |

| JAnCTL0                          | UAnPWR                                                                 | UAnTXE                                                                                           | UAnRXE                                                                                   | UAnDIR                                                                                                             | UAnPS1                                                                                    | UAnPS0                                                                                    | UAnCL                                                                                 | UAnSL                                           |

|                                  |                                                                        |                                                                                                  |                                                                                          |                                                                                                                    |                                                                                           |                                                                                           |                                                                                       |                                                 |

|                                  | UAnPWR                                                                 |                                                                                                  |                                                                                          |                                                                                                                    | n operatior                                                                               |                                                                                           |                                                                                       |                                                 |

|                                  | 0                                                                      |                                                                                                  |                                                                                          | eration (UA                                                                                                        | RTAn rese                                                                                 | t asynchro                                                                                | nously)                                                                               |                                                 |

|                                  | 1                                                                      |                                                                                                  | ARTAn ope                                                                                |                                                                                                                    |                                                                                           |                                                                                           |                                                                                       |                                                 |

|                                  | is fixed to                                                            |                                                                                                  | by clearing                                                                              | rolled by the<br>the UAnP                                                                                          |                                                                                           |                                                                                           | •                                                                                     | ουτρυτ                                          |

|                                  | UAnTXE                                                                 |                                                                                                  |                                                                                          | Transmiss                                                                                                          | sion operat                                                                               | ion enable                                                                                |                                                                                       |                                                 |

|                                  | 0                                                                      | Disable tra                                                                                      | ansmissior                                                                               | operation                                                                                                          |                                                                                           |                                                                                           |                                                                                       |                                                 |

|                                  | 1                                                                      | Enable tra                                                                                       | Insmission                                                                               | operation                                                                                                          |                                                                                           |                                                                                           |                                                                                       |                                                 |

| T<br>• T<br>th<br>m<br>• W<br>tc | To stop<br>• To initia<br>the base<br>may not<br>• When U              | transmission<br>lize the transference<br>clock, and<br>be execut<br>ARTAn op<br>nsmission i      | on, clear th<br>nsmission i<br>d then set t<br>ed (for the<br>eration is e               | UAnPWR I<br>le UAnTXE<br>unit, clear t<br>he UAnTXI<br>base clock<br>enabled (UA<br>after at leas                  | bit to 0 and<br>ne UAnTXE<br>5 bit to 1 ag<br>see <b>15.7</b> (<br>anPWR bit              | d then UAn<br>E bit to 0, w<br>gain. Othe<br>( <b>1) (a) Bas</b><br>= 1) and th           | PWR bit to<br>vait for two<br>rwise, initia<br><b>e clock</b> ).<br>le UAnTXE         | o 0.<br>cycles of<br>alization<br>E bit is set  |

|                                  | UAnRXE                                                                 |                                                                                                  |                                                                                          | Reception                                                                                                          | on operatio                                                                               | n enable                                                                                  |                                                                                       |                                                 |

|                                  | 0                                                                      | Disable re                                                                                       | ception op                                                                               | · · ·                                                                                                              |                                                                                           |                                                                                           |                                                                                       |                                                 |

|                                  | 1                                                                      | Enable re                                                                                        | ception ope                                                                              | eration                                                                                                            |                                                                                           |                                                                                           |                                                                                       |                                                 |

|                                  | To stop<br>• To initia<br>the base<br>may not<br>• When U<br>to 1, rec | reception,<br>lize the rec<br>clock, and<br>be execut<br>ARTAn op<br>eption is e<br>. If a start | clear the U<br>eption unit<br>d then set t<br>ed (for the<br>eration is e<br>nabled afte | nPWR bit t<br>IAnRXE bit<br>, clear the I<br>he UAnRX<br>base clock<br>enabled (UA<br>er at least tw<br>red before | to 0 and th<br>JAnRXE bi<br>E bit to 1 a<br>see <b>15.7</b> (<br>AnPWR bit<br>vo cycles o | en UAnPW<br>t to 0, wait<br>gain. Othe<br><b>(1) (a) Bas</b><br>= 1) and th<br>f the base | VR bit to 0.<br>for two cyu<br>rwise, initia<br>e clock).<br>le UAnRXE<br>clock (fucu | cles of<br>alization<br>E bit is set<br><) have |

# 15.6 Operation

## 15.6.1 Data format

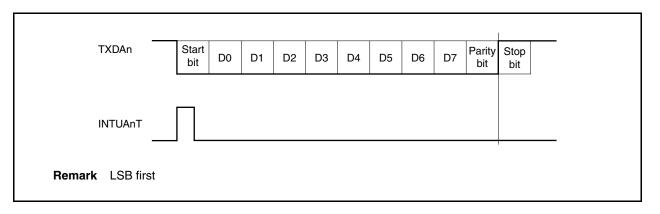

As shown in Figure 15-5, one frame of transmit/receive data consists of a start bit, character bits, parity bit, and stop bit(s).

Specification of the character bit length within 1 data frame, parity selection, specification of the stop bit length, and specification of MSB-first/LSB-first transfer are performed using the UAnCTL0 register.

The UAnOPT0.UAnTDL bit is used to specify normal output/inverted output for the data to be transferred via the TXDAn pin.

The UAnOPT0.UAnRDL bit is used to specify normal input/inverted input for the data to be received via the RXDAn pin.

- Start bit.....1 bit

- Character bits ......7 bits/8 bits

- Parity bit ......Even parity/odd parity/0 parity/no parity

- Stop bit ......1 bit/2 bits

- Input logic ......Normal input/inverted input

- Output logic ......Normal output/inverted output

- Communication direction ......MSB/LSB

# 15.6.2 UART transmission

Transmission is enabled by setting the UAnCTL0.UAnPWR and UAnCTL0.UAnTXE bits to 1, and transmission is started by writing transmit data to the UAnTX register. The start bit, parity bit, and stop bit are automatically added.

Since the CTS (transmit enable signal) input pin is not provided in UARTAn, use a port to check that reception is enabled at the transmit destination.

The data in the UAnTX register is transferred to the UARTAn transmit shift register upon the start of transmission.

A transmission enable interrupt request signal (INTUAnT) is generated upon completion of transmission of the data of the UAnTX register to the UARTAn transmit shift register, and the contents of the UARTAn transmit shift register are output to the TXDAn pin.

Writing the next transmit data to the UAnTX register is enabled after the INTUAnT signal is generated.

#### Figure 15-6. UART Transmission

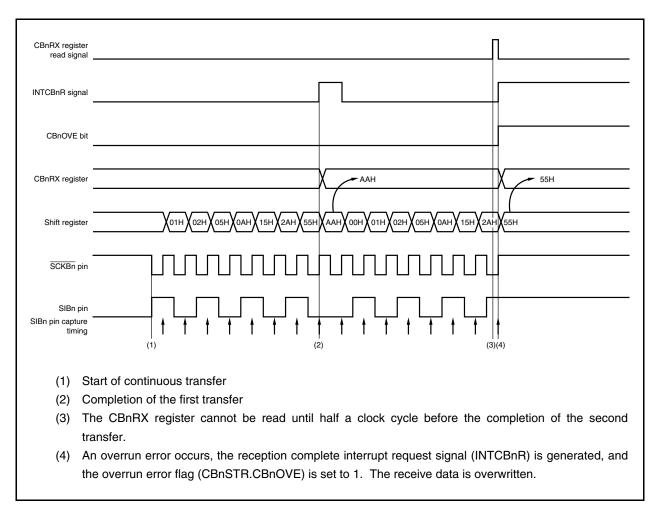

#### 16.6.13 Reception errors

When transfer is performed with reception enabled (CBnCTL0.CBnRXE bit = 1) in the continuous transfer mode, the reception complete interrupt request signal (INTCBnR) is generated again if the next receive operation is completed before the CBnRX register is read after the INTCBnR signal is generated, and the overrun error flag (CBnSTR.CBnOVE) is set to 1.

If an overrun error occurs, the previous receive data is lost because the CBnRX register is updated. Even if a reception error occurs, the INTCBnR signal is generated again upon completion of the next reception if the CBnRX register is not read.

An overrun error occurs if reading the CBnRX register has not been completed half a clock cycle before the last bit of the next receive data is sampled after the INTCBnR signal is generated.

Figure 16-29. Overrun Error Timing

#### (c) Stop condition Processing by master device $IICn \leftarrow address$ llCn $| \text{ IICn} \leftarrow \text{FFH } \textbf{Note}$ ( ACKDn STDn SPDn WTIMn ACKEn MSTSn STTn SPTn Note WRELn INTIICn ~ (when SPIEn = 1) TRCn Transfer lines 1 SCL0n 1 2 3 4 5 6 7 8 9 AD6 SDA0n D7 X D6 X D5 X D4 X D3 X D2 X D1 X D0 NACK Stop Start condition condition Processing by slave device llCn | IICn $\leftarrow$ data ACKDn STDn SPDn (( -{{-WTIMn н ( ACKEn Н MSTSn <u>\_(</u> STTn SPTn -WRELn \_(( INTIICn ( (when SPIEn = 1) TRCn Note To cancel master wait, write FFH to IICn or set WRELn.

## Figure 17-24. Example of Slave to Master Communication (When Wait Is Changed from 8 Clocks to 9 Clocks for Master and 9-Clock Wait Is Selected for Slave) (3/3)

## 18.8 Time Related to DMA Transfer

The time required to respond to a DMA request, and the minimum number of clocks required for DMA transfer are shown below.

Single transfer: DMA response time (<1>) + Transfer source memory access (<2>) + 1<sup>Note 1</sup> + Transfer destination memory access (<2>)

| DN                             | IA Cycle            | Number of Execution Clocks                                                    |  |  |  |  |  |

|--------------------------------|---------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| <1> DMA request response time  |                     | 4 clocks (MIN.) + Noise elimination time <sup>Note 2</sup>                    |  |  |  |  |  |

| <2> Memory access              | Internal RAM access | 2 clocks                                                                      |  |  |  |  |  |

| Peripheral I/O register access |                     | 3 clocks + Number of wait cycles specified by VSWC register $^{\mbox{Note}3}$ |  |  |  |  |  |

Notes 1. One clock is always inserted between a read cycle and a write cycle in DMA transfer.

- If an external interrupt (INTPn) is specified as the trigger to start DMA transfer, noise elimination time is added (n = 0 to 7).

- 3. More wait cycles may be necessary for accessing a special register described in 3.4.9 (1).

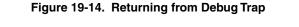

# (2) Restoration

Execution is returned from a debug trap by using the DBRET instruction.

When the DBRET instruction is executed, the CPU performs the following processing and transfers control to the address of the restored PC.

<1> Loads the saved PC and PSW from DBPC and DBPSW.

<2> Transfers control back to address of the restored PC and PSW.

# Caution DBPC and DBPSW can be accessed only during the interval between the execution of the DBTRAP instruction and the DBRET instruction.

The processing for returning from a debug trap is shown below.

## (4) Regulator protection register (REGPR)

The REGPR register is used to protect the regulator output voltage level control register 0 (REGOVL0) so that illegal data is not written to REGOVL0. Data cannot be written to the REGOVL0 register unless enabling data (C9H) is written to the REGPR register. Only two types of data, C9H (enabling data) and 00H (protection data), can be written to the REGPR register. Writing any other value is prohibited. (If a value other than C9H or 00H is written to the REGPR register, the written value is set to prohibit a write access to the REGOVL0 register, but the operation is not guaranteed.)

This register can be read or written only in 8-bit units (accessing it in 1-bit units is prohibited). Reset sets this register to 00H (protection data status).

| Alter lese                                                                                                                             | et: 00H                                                                                         | R/W                                                                                                            | Address: F                                                                            | FFFF331H                                                               |                                |                   |           |            |            |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-----------|------------|------------|

| _                                                                                                                                      | 7                                                                                               | 6                                                                                                              | 5                                                                                     | 4                                                                      | 3                              | 2                 | 1         | 0          | _          |

| REGPR                                                                                                                                  | PR7                                                                                             | PR6                                                                                                            | PR5                                                                                   | PR4                                                                    | PR3                            | PR2               | PR1       | PR0        |            |

|                                                                                                                                        |                                                                                                 |                                                                                                                |                                                                                       |                                                                        |                                |                   |           |            |            |

| Protection data                                                                                                                        |                                                                                                 |                                                                                                                |                                                                                       |                                                                        |                                |                   |           |            |            |

| In this status, the                                                                                                                    |                                                                                                 | -                                                                                                              | -                                                                                     |                                                                        |                                | -                 |           | -          |            |

| status, a value                                                                                                                        | is not w                                                                                        | ritten to t                                                                                                    | he REGO                                                                               | VL0 regis                                                              | ter even                       | if an atte        | mpt is ma | ade to wr  | ite it, an |

|                                                                                                                                        |                                                                                                 |                                                                                                                |                                                                                       |                                                                        |                                |                   |           |            |            |

| REGOVL0 regis                                                                                                                          | ter holds                                                                                       | s the previ                                                                                                    | ous value.                                                                            |                                                                        |                                |                   |           |            |            |

| REGOVL0 regis<br>Be sure to set                                                                                                        |                                                                                                 | •                                                                                                              |                                                                                       |                                                                        | ng the va                      | alue of the       | e REGOV   | /L0 regist | ər, in orc |

| 0                                                                                                                                      | REGPR                                                                                           | to 00H, e                                                                                                      |                                                                                       |                                                                        | ng the va                      | alue of the       | e REGOV   | /L0 regist | ər, in orc |

| Be sure to set                                                                                                                         | REGPR                                                                                           | to 00H, e                                                                                                      |                                                                                       |                                                                        | ng the va                      | alue of the       | e REGOV   | /L0 regist | ər, in orc |

| Be sure to set avoid unexpecte                                                                                                         | REGPR<br>ed malfur                                                                              | to 00H, enction.                                                                                               | except whe                                                                            |                                                                        | ng the va                      | alue of the       | e REGOV   | /L0 regist | ər, in ord |

| Be sure to set avoid unexpecte                                                                                                         | REGPR<br>ed malfur<br>status: R                                                                 | to 00H, enction.                                                                                               | except whe                                                                            | en changi                                                              | -                              |                   | e REGOV   | /L0 regist | er, in ord |

| Be sure to set avoid unexpecte                                                                                                         | REGPR<br>ed malfun<br>status: R<br>write acc                                                    | to 00H, enction.<br>REGPR =                                                                                    | except whe<br><b>C9H</b><br>∋ REGOVL                                                  | en changi<br>.0 register                                               | is enable                      |                   | e REGOV   | /L0 regist | er, in ord |

| Be sure to set I<br>avoid unexpecter<br>Enabling data so<br>In this status, a v<br>• Transition from                                   | REGPR<br>ed malfur<br>status: R<br>write acc<br>n normal                                        | to 00H, $\epsilon$<br>inction.<br><b>REGPR =</b><br>cess to the<br>mode $\rightarrow$                          | except whe<br><b>C9H</b><br>e REGOVL<br>low-voltag                                    | en changi<br>_0 register<br>je STOP r                                  | is enable                      |                   | ₽ REGOV   | /L0 regist | er, in ord |

| Be sure to set avoid unexpecte<br>Enabling data s<br>In this status, a                                                                 | REGPR<br>ed malfun<br>status: R<br>write acc<br>n normal<br>etting ar                           | to 00H, end<br>action.<br><b>REGPR =</b><br>cess to the<br>mode $\rightarrow$<br><b>nd operat</b>              | except whe<br>C9H<br>∋ REGOVL<br>low-voltag                                           | en changi<br>.0 register<br>je STOP r<br><b>s</b> .                    | is enable                      | ed.               |           | /L0 regist | er, in ord |

| Be sure to set I<br>avoid unexpecte<br>Enabling data s<br>In this status, a<br>• Transition from<br>See 21.6.1 So<br>• Transition of s | REGPR<br>ed malfun<br>status: R<br>write acc<br>n normal<br>etting ar<br>ubclock o              | to 00H, end<br>action.<br><b>REGPR =</b><br>cess to the<br>mode $\rightarrow$<br><b>nd operat</b><br>operation | except whe<br>C9H<br>≥ REGOVL<br>low-voltag<br>ion status<br>mode → I                 | en changi<br>_0 register<br>je STOP r<br><b>s.</b><br>ow-voltagi       | is enable                      | ed.               |           | /L0 regist | er, in ord |

| Be sure to set I<br>avoid unexpected<br>Enabling data so<br>In this status, a w<br>• Transition from<br>See 21.6.1 So                  | REGPR<br>ed malfun<br>status: R<br>write acc<br>n normal<br>etting ar<br>ubclock o<br>etting ar | to 00H, end<br>action.<br><b>EEGPR =</b><br>$mode \rightarrow$<br><b>Ind operation</b><br><b>Ind operation</b> | except whe<br>C9H<br>≥ REGOVL<br>low-voltag<br>tion status<br>mode → l<br>tion status | en changi<br>_0 register<br>je STOP r<br>s.<br>ow-voltagi<br><b>s.</b> | is enable<br>node<br>e subcloc | ed.<br>k operatic |           | /L0 regist | ər, in orc |

# CHAPTER 31 ELECTRICAL SPECIFICATIONS (V850ES/JC3-L (48-pin))

# 31.1 Absolute Maximum Ratings

| Parameter            | Symbol             | Conditions                                                                 | Ratings                                                           | Unit |

|----------------------|--------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|------|

| Supply voltage       | VDD                | $V_{\text{DD}} = EV_{\text{DD}} = AV_{\text{REF0}} = AV_{\text{REF1}}$     | –0.5 to +4.6                                                      | V    |

|                      | EVDD               | $V_{\text{DD}} = EV_{\text{DD}} = AV_{\text{REF0}} = AV_{\text{REF1}}$     | –0.5 to +4.6                                                      | V    |

|                      | AV <sub>REF0</sub> | $V_{\text{DD}} = EV_{\text{DD}} = AV_{\text{REF0}} = AV_{\text{REF1}}$     | –0.5 to +4.6                                                      | V    |

|                      | AV <sub>REF1</sub> | $V_{\text{DD}} = EV_{\text{DD}} = AV_{\text{REF0}} = AV_{\text{REF1}}$     | –0.5 to +4.6                                                      | V    |

|                      | Vss                | Vss = EVss = AVss                                                          | –0.5 to +0.5                                                      | V    |

|                      | AVss               | Vss = EVss = AVss                                                          | –0.5 to +0.5                                                      | V    |

|                      | EVss               | Vss = EVss = AVss                                                          | –0.5 to +0.5                                                      | V    |

| Input voltage        | VI1                | P97 to P99, P914, P915, PCM0, PDL5, RESET, FLMD0                           | -0.5 to EV <sub>DD</sub> + 0.5 <sup>Note 1</sup>                  | V    |

|                      | V <sub>12</sub>    | P10                                                                        | -0.5 to AV <sub>REF1</sub> + 0.5 <sup>Note 1</sup>                | V    |

|                      | Vı3                | X1                                                                         | $-0.5$ to V <sub>DD</sub> + $0.5^{Note 1}$                        | V    |

|                      |                    | X2                                                                         | $-0.5$ to $V_{\text{RO}}^{\text{Note 2}}$ + $0.5^{\text{Note 1}}$ |      |

|                      | V <sub>14</sub>    | P02, P03, P05, P30 to P32, P38, P39, P40 to P42, P50 to P55, P90, P91, P96 | –0.5 to +6.0                                                      | V    |

|                      | VI5                | XT1, XT2                                                                   | -0.5 to Vro <sup>Note 2</sup> + 0.5                               | V    |

| Analog input voltage | VIAN               | P70 to P75                                                                 | -0.5 to AV <sub>REF0</sub> + 0.5 <sup>Note 1</sup>                | V    |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (1/2)

**Notes 1.** Be sure not to exceed the absolute maximum ratings (MAX. value) of each supply voltage.

- 2. On-chip regulator output voltage

- Cautions 1. Do not directly connect the output (or I/O) pins of IC products to each other, or to VDD, VCC, and GND. Open-drain pins or open-collector pins, however, can be directly connected to each other. Direct connection of the output pins between an IC product and an external circuit is possible, if the output pins can be set to the high-impedance state and the output timing of the external circuit is designed to avoid output conflict.

- 2. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

The ratings and conditions indicated for DC characteristics, AC characteristics, and operating conditions represent the quality assurance range during normal operation.

**Remark** Unless specified otherwise, the ratings of alternate-function pins are the same as those of port pins.

# CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS

The V850ES/JC3-L should be soldered and mounted under the following recommended conditions. For technical information, see the following website.

Semiconductor Device Mount Manual (http://www.renesas.com/prod/package/manual/)

Table 33-1. Surface Mounting Type Soldering Conditions (1/2)

| (1) μPD70F3797K8-4B4-AX: | 40-pin plastic WQFN (6 × 6) |

|--------------------------|-----------------------------|

| μPD70F3798K8-4B4-AΧ:     | 40-pin plastic WQFN (6 × 6) |

| µPD70F3799K8-4B4-AX:     | 40-pin plastic WQFN (6 × 6) |

| µPD70F3800K8-4B4-AX:     | 40-pin plastic WQFN (6 × 6) |

| μΡD70F3838K8-4B4-AX:     | 40-pin plastic WQFN (6 × 6) |

| Soldering Method | Soldering Conditions                                                                                                                                                                                    | Recommended<br>Condition Symbol |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                  | Package peak temperature: 260°C, Time: 60 seconds max. (at 220°C or higher),<br>Count: Three times or less, Exposure limit: 7 days <sup>Note</sup> (after that, prebake at 125°C for 10<br>to 72 hours) | IR60-107-3                      |

Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.

#### Caution Do not use different soldering methods together (except for partial heating).

Remarks 1. The V850ES/JC3-L is a lead-free product.

- **2.** For soldering methods and conditions other than those recommended above, please contact a Renesas Electronics sales representative.

- (2)  $\mu$ PD70F3801GA-GAM-AX: 48-pin plastic LQFP (fine pitch) (7 × 7)  $\mu$ PD70F3802GA-GAM-AX: 48-pin plastic LQFP (fine pitch) (7 × 7)  $\mu$ PD70F3803GA-GAM-AX: 48-pin plastic LQFP (fine pitch) (7 × 7)  $\mu$ PD70F3804GA-GAM-AX: 48-pin plastic LQFP (fine pitch) (7 × 7)  $\mu$ PD70F3839GA-GAM-AX: 48-pin plastic LQFP (fine pitch) (7 × 7)

| Soldering Method | Soldering Conditions                                                                                                                                                                                    | Recommended<br>Condition Symbol |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                  | Package peak temperature: 260°C, Time: 60 seconds max. (at 220°C or higher),<br>Count: Three times or less, Exposure limit: 7 days <sup>Note</sup> (after that, prebake at 125°C for 10<br>to 72 hours) | IR60-107-3                      |

| Partial heating  | Pin temperature: 350°C max., Time: 3 seconds max. (per pin row)                                                                                                                                         | _                               |

Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.

#### Caution Do not use different soldering methods together (except for partial heating).

**Remarks 1.** The V850ES/JC3-L is a lead-free product.

**2.** For soldering methods and conditions other than those recommended above, please contact a Renesas Electronics sales representative.

|          |                    |                                      |                                                                                                                                                                                                                                                                      |             |                    |             |    |       |   | (6 | 6/6) |  |

|----------|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|-------------|----|-------|---|----|------|--|

| Mnemonic | Operand            | Opcode                               | Operation                                                                                                                                                                                                                                                            |             | Execution<br>Clock |             |    | Flags |   |    |      |  |

|          |                    |                                      |                                                                                                                                                                                                                                                                      | i           | r                  | Ι           | СҮ | ov    | S | Z  | SAT  |  |

| SUB      | reg1,reg2          | rrrr001101RRRRR                      | GR[reg2]←GR[reg2]–GR[reg1]                                                                                                                                                                                                                                           | 1           | 1                  | 1           | ×  | ×     | × | ×  |      |  |

| SUBR     | reg1,reg2          | rrrr001100RRRRR                      | GR[reg2]←GR[reg1]–GR[reg2]                                                                                                                                                                                                                                           | 1           | 1                  | 1           | ×  | ×     | × | ×  |      |  |

| SWITCH   | reg1               | 00000000010RRRR                      | adr←(PC+2) + (GR [reg1] logically shift left by 1)<br>PC←(PC+2) + (sign-extend<br>(Load-memory (adr,Halfword))<br>logically shift left by 1                                                                                                                          | 5           | 5                  | 5           |    |       |   |    |      |  |

| SXB      | reg1               | 00000000101RRRRR                     | GR[reg1]←sign-extend<br>(GR[reg1] (7 : 0))                                                                                                                                                                                                                           | 1           | 1                  | 1           |    |       |   |    |      |  |

| SXH      | reg1               | 00000000111RRRRR                     | GR[reg1]←sign-extend<br>(GR[reg1] (15 : 0))                                                                                                                                                                                                                          | 1           | 1                  | 1           |    |       |   |    |      |  |

| TRAP     | vector             | 000001111111                         | EIPC       ←PC+4 (Restored PC)         EIPSW       ←PSW         ECR.EICC       ←Interrupt code         PSW.EP       ←1         PSW.ID       ←1         PC       ←00000040H         (when vector is 00H to 0FH)         00000050H         (when vector is 10H to 1FH) | 3           | 3                  | 3           |    |       |   |    |      |  |

| TST      | reg1,reg2          | rrrr001011RRRRR                      | result←GR[reg2] AND GR[reg1]                                                                                                                                                                                                                                         | 1           | 1                  | 1           |    | 0     | × | ×  |      |  |

| TST1     | bit#3,disp16[reg1] | 11bbb111110RRRRR<br>ddddddddddddddd  | adr←GR[reg1]+sign-extend(disp16)<br>Z flag←Not (Load-memory-bit (adr,bit#3))                                                                                                                                                                                         | 3<br>Note 3 | 3<br>Note 3        | 3<br>Note 3 |    |       |   | ×  |      |  |

|          | reg2, [reg1]       | rrrrr111111RRRRR<br>0000000011100110 | adr←GR[reg1]<br>Z flag←Not (Load-memory-bit (adr,reg2))                                                                                                                                                                                                              | 3<br>Note 3 | 3<br>Note 3        | 3<br>Note 3 |    |       |   | ×  |      |  |

| XOR      | reg1,reg2          | rrrr001001RRRRR                      | GR[reg2]←GR[reg2] XOR GR[reg1]                                                                                                                                                                                                                                       | 1           | 1                  | 1           |    | 0     | × | ×  |      |  |

| XORI     | imm16,reg1,reg2    | rrrr110101RRRRR                      | GR[reg2]←GR[reg1] XOR zero-extend (imm16)                                                                                                                                                                                                                            | 1           | 1                  | 1           |    | 0     | × | ×  |      |  |

| ZXB      | reg1               | 00000000100RRRR                      | GR[reg1]←zero-extend (GR[reg1] (7 : 0))                                                                                                                                                                                                                              | 1           | 1                  | 1           |    |       |   |    |      |  |