# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 267MHz                                                                  |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 + PHY (1)                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 516-BBGA Exposed Pad                                                    |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8313cvraddb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

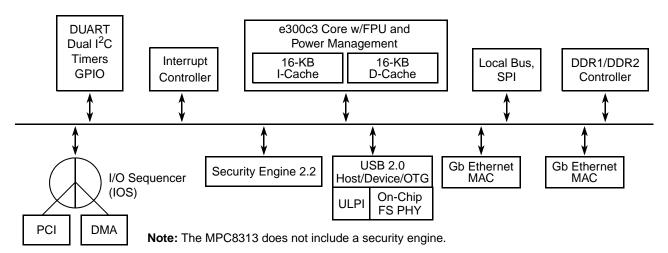

The MPC8313E incorporates the e300c3 core, which includes 16 Kbytes of L1 instruction and data caches and on-chip memory management units (MMUs). The MPC8313E has interfaces to dual enhanced three-speed 10/100/1000 Mbps Ethernet controllers, a DDR1/DDR2 SDRAM memory controller, an enhanced local bus controller, a 32-bit PCI controller, a dedicated security engine, a USB 2.0 dual-role controller and an on-chip high-speed PHY, a programmable interrupt controller, dual I<sup>2</sup>C controllers, a 4-channel DMA controller, and a general-purpose I/O port. This figure shows a block diagram of the MPC8313E.

#### Figure 1. MPC8313E Block Diagram

The MPC8313E security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES, 3DES, AES, SHA-1, and MD-5 algorithms.

### 1.1 MPC8313E Features

The following features are supported in the MPC8313E:

- Embedded PowerPC<sup>TM</sup> e300 processor core built on Power Architecture<sup>TM</sup> technology; operates at up to 333 MHz.

- High-performance, low-power, and cost-effective host processor

- DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both DDR1 and DDR2

- 16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

- Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced local bus interface with up to 66-MHz operation, and USB 2.0 (high speed) with an on-chip PHY.

- Security engine provides acceleration for control and data plane security protocols

- Power management controller for low-power consumption

- High degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration

### 1.6 USB Dual-Role Controller

The MPC8313E USB controller includes the following features:

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

- Compatible with Universal Serial Bus Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed/high-speed PHY

### 1.7 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313E eTSECs include the following features:

- Two RGMII/SGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status

- Three-speed support (10/100/1000 Mbps)

- On-chip high-speed serial interface to external SGMII PHY interface

- Support for IEEE Std 1588<sup>TM</sup>

- Support for two full-duplex FIFO interface modes

- Multiple PHY interface configuration

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>®</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Transmission from up to eight physical queues.

- Reception to up to eight physical queues

### 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

#### 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 1. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

|                                      | Characteristic                                                                                         | Symbol                               | Max Value                                                                    | Unit | Note |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|------|

| Core supply volta                    | age                                                                                                    | V <sub>DD</sub>                      | -0.3 to 1.26                                                                 | V    | —    |

| PLL supply volta                     | ge                                                                                                     | AV <sub>DD</sub>                     | -0.3 to 1.26                                                                 | V    |      |

| Core power supp                      | bly for SerDes transceivers                                                                            | XCOREV <sub>DD</sub>                 | -0.3 to 1.26                                                                 | V    |      |

| Pad power suppl                      | y for SerDes transceivers                                                                              | XPADV <sub>DD</sub>                  | -0.3 to 1.26                                                                 | V    | —    |

| DDR and DDR2                         | DRAM I/O voltage                                                                                       | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                                 | V    |      |

| PCI, local bus, D<br>and JTAG I/O vo | UART, system control and power management, I <sup>2</sup> C, Itage                                     | NV <sub>DD</sub> /LV <sub>DD</sub>   | -0.3 to 3.6                                                                  | V    |      |

| eTSEC, USB                           |                                                                                                        | LV <sub>DDA</sub> /LV <sub>DDB</sub> | -0.3 to 3.6                                                                  | V    | _    |

| Input voltage                        | DDR DRAM signals                                                                                       | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | DDR DRAM reference                                                                                     | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | Enhanced three-speed Ethernet signals                                                                  | LV <sub>IN</sub>                     | -0.3 to (LV <sub>DDA</sub> + 0.3)<br>or<br>-0.3 to (LV <sub>DDB</sub> + 0.3) | V    | 4, 5 |

|                                      | Local bus, DUART, SYS_CLK_IN, system control, and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 3, 5 |

|                                      | PCI                                                                                                    | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 6    |

| Storage tempera                      | ture range                                                                                             | T <sub>STG</sub>                     | -55 to 150                                                                   | °C   | —    |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** NV<sub>IN</sub> must not exceed NV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: LV<sub>IN</sub> must not exceed LV<sub>DDA</sub>/LV<sub>DDB</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

### 2.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for the MPC8313E. Note that the values in this table are the recommended and tested operating conditions. If a particular block is given a voltage falling within the range in the Recommended Value column, the MPC8313E is capable of delivering the amount of current listed in the Current Requirement column; this is the maximum current possible. Proper device operation outside of these conditions is not guaranteed.

#### Table 2. Recommended Operating Conditions (continued)

| Characteristic Symbol Recommended Value <sup>1</sup> Unit | Current<br>Requirement |

|-----------------------------------------------------------|------------------------|

|-----------------------------------------------------------|------------------------|

Note:

- 1. GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. Some GPIO pins may operate from a 2.5-V supply when configured for other functions.

- 3. Min temperature is specified with  $T_A$ ; Max temperature is specified with  $T_J$

- 4. All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.

- 5. All I/O pins should be interfaced with peripherals operating at same voltage level.

- This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

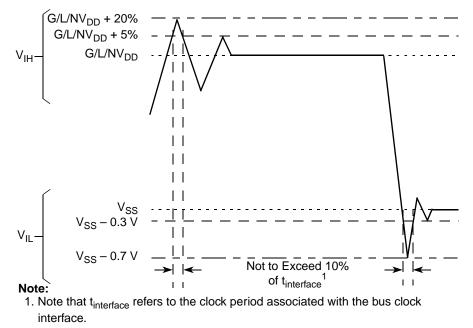

This figure shows the undershoot and overshoot voltages at the interfaces of the MPC8313E.

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/NV<sub>DD</sub>/LV<sub>DD</sub>

#### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

| Driver Type                           | Output Impedance ( $\Omega$ ) | Supply Voltage           |

|---------------------------------------|-------------------------------|--------------------------|

| Local bus interface utilities signals | 42                            | NV <sub>DD</sub> = 3.3 V |

| PCI signals                           | 25                            |                          |

| DDR signal                            | 18                            | GV <sub>DD</sub> = 2.5 V |

### 4.2 AC Electrical Characteristics

The primary clock source for the MPC8313E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the system clock input (SYS\_CLK\_IN/PCI\_CLK) AC timing specifications for the MPC8313E.

| Parameter/Condition           | Symbol                                    | Min | Тур | Max   | Unit | Note |

|-------------------------------|-------------------------------------------|-----|-----|-------|------|------|

| SYS_CLK_IN/PCI_CLK frequency  | f <sub>SYS_CLK_IN</sub>                   | 24  | _   | 66.67 | MHz  | 1    |

| SYS_CLK_IN/PCI_CLK cycle time | t <sub>SYS_CLK_IN</sub>                   | 15  | —   | _     | ns   | —    |

| SYS_CLK_IN rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>         | 0.6 | 0.8 | 4     | ns   | 2    |

| PCI_CLK rise and fall time    | t <sub>PCH</sub> , t <sub>PCL</sub>       | 0.6 | 0.8 | 1.2   | ns   | 2    |

| SYS_CLK_IN/PCI_CLK duty cycle | t <sub>KHK</sub> /t <sub>SYS_CLK_IN</sub> | 40  | —   | 60    | %    | 3    |

| SYS_CLK_IN/PCI_CLK jitter     | _                                         | _   | _   | ±150  | ps   | 4, 5 |

#### Table 8. SYS\_CLK\_IN AC Timing Specifications

Notes:

1. Caution: The system, core, security block must not exceed their respective maximum or minimum operating frequencies.

2. Rise and fall times for SYS\_CLK\_IN/PCI\_CLK are measured at 0.4 and 2.4 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter-short term and long term-and is guaranteed by design.

5. The SYS\_CLK\_IN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYS\_CLK\_IN drivers with the specified jitter.

# 5 **RESET** Initialization

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8313E.

### 5.1 **RESET DC Electrical Characteristics**

This table provides the DC electrical characteristics for the RESET pins.

| Table 9. | RESET Pins | <b>DC Electrical</b> | Characteristics |

|----------|------------|----------------------|-----------------|

|----------|------------|----------------------|-----------------|

| Characteristic      | Symbol          | Condition                                            | Min  | Max                    | Unit |

|---------------------|-----------------|------------------------------------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                                                    | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                                    | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{IN} \leq \text{NV}_{DD}$ | —    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA                            | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                             | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                             | —    | 0.4                    | V    |

| Parameters          | Symbol          | C                                            | conditions                        | Min                   | Мах                                                      | Unit |

|---------------------|-----------------|----------------------------------------------|-----------------------------------|-----------------------|----------------------------------------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -1.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$    | 2.00                  | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1.0 mA                     | $LV_{DDA}$ or $LV_{DDB} = Min$    | V <sub>SS</sub> – 0.3 | 0.40                                                     | V    |

| Input high voltage  | V <sub>IH</sub> | —                                            | $LV_{DDA}$ or $LV_{DDB} = Min$    | 1.7                   | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                            | $LV_{DDA}$ or $LV_{DDB}$ = Min    | -0.3                  | 0.70                                                     | V    |

| Input high current  | Ι <sub>ΙΗ</sub> | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                   | —                     | 10                                                       | μΑ   |

| Input low current   | ١ <sub>١L</sub> | ١                                            | $V_{\rm IN}^{1} = V_{\rm SS}^{1}$ | -15                   | —                                                        | μΑ   |

Table 25. RGMII/RTBI DC Electrical Characteristics (continued)

Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

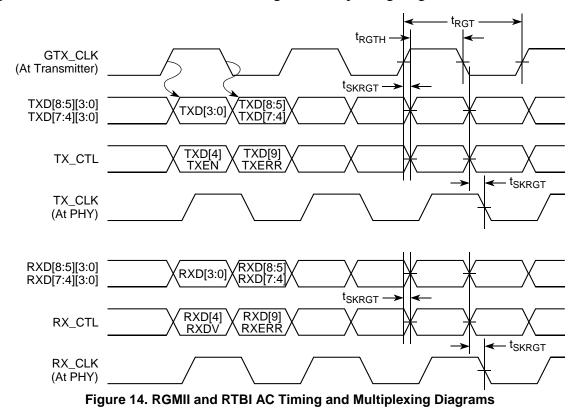

### 8.2 MII, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for MII, RMII, RGMII, and RTBI are presented in this section.

### 8.2.1 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

#### 8.2.1.1 MII Transmit AC Timing Specifications

This table provides the MII transmit AC timing specifications.

#### Table 26. MII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DDA}/LV_{DDB}/NV_{DD}$  of 3.3 V ± 0.3 V.

| Parameter/Condition                                                   | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                                           | t <sub>MTX</sub>                    | _   | 400 | —   | ns   |

| TX_CLK clock period 100 Mbps                                          | t <sub>MTX</sub>                    | _   | 40  | —   | ns   |

| TX_CLK duty cycle                                                     | t <sub>MTXH/</sub> t <sub>MTX</sub> | 35  |     | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay                       | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MTXR</sub>                   | 1.0 |     | 4.0 | ns   |

| TX_CLK data clock fall V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>MTXF</sub>                   | 1.0 | —   | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub></sub>

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

#### 8.3 SGMII Interface Electrical Characteristics

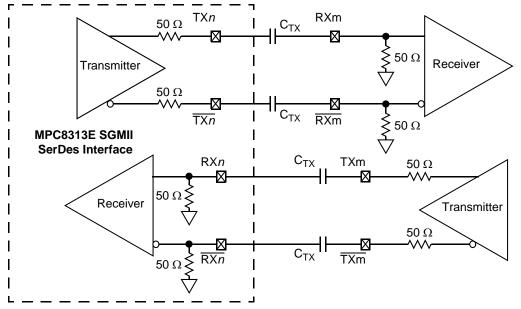

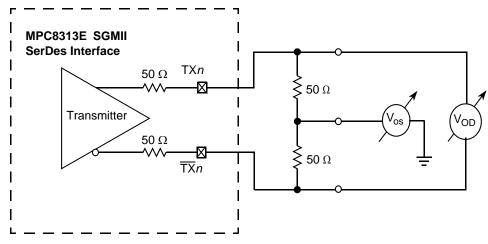

Each SGMII port features a 4-wire AC-coupled serial link from the dedicated SerDes interface of MPC8313E as shown in Figure 15, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features a 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XCOREVSS. The reference circuit of the SerDes transmitter and receiver is shown in Figure 33.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines described in Section 22.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the TSEC\_GTX\_CLK125 clock is not required for this port. Instead, the SerDes reference clock is required on SD\_REF\_CLK and SD\_REF\_CLK pins.

### 8.3.1 DC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 9, "High-Speed Serial Interfaces (HSSI)."

Figure 15. 4-Wire AC-Coupled SGMII Serial Link Connection Example

Figure 16. SGMII Transmitter DC Measurement Circuit

| Table 33. SGMII DC Receive | r Electrical Characteristics |

|----------------------------|------------------------------|

|----------------------------|------------------------------|

| Parameter                             | Symbol                  | Min  | Тур | Max  | Unit | Note |

|---------------------------------------|-------------------------|------|-----|------|------|------|

| Supply voltage                        | XCOREV <sub>DD</sub>    | 0.95 | 1.0 | 1.05 | V    |      |

| DC Input voltage range                |                         |      | N/A |      |      | 1    |

| Input differential voltage            | V <sub>RX_DIFFp-p</sub> | 100  | —   | 1200 | mV   | 2    |

| Loss of signal threshold              | VL <sub>OS</sub>        | 30   | —   | 100  | mV   |      |

| Input AC common mode voltage          | V <sub>CM_ACp-p</sub>   | —    | _   | 100  | mV   | 3    |

| Receiver differential input impedance | Z <sub>RX_DIFF</sub>    | 80   | 100 | 120  | Ω    |      |

| Receiver common mode input impedance  | Z <sub>RX_CM</sub>      | 20   | —   | 35   | Ω    |      |

Table 33. SGMII DC Receiver Electrical Characteristics (continued)

| Parameter                 | Symbol          | Min | Тур                   | Мах | Unit | Note |

|---------------------------|-----------------|-----|-----------------------|-----|------|------|

| Common mode input voltage | V <sub>CM</sub> | _   | V <sub>xcorevss</sub> | —   | V    | 4    |

Notes:

1. Input must be externally AC-coupled.

2.  $V_{RX\_DIFFp-p}$  is also referred to as peak to peak input differential voltage

3.  $V_{CM\_ACp-p}$  is also referred to as peak to peak AC common mode voltage.

4. On-chip termination to XCOREV<sub>SS</sub>.

### 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs  $(TX[n] \text{ and } \overline{TX}[n])$  or at the receiver inputs  $(RX[n] \text{ and } \overline{RX}[n])$  as depicted in Figure 18, respectively.

#### 8.3.4.1 SGMII Transmit AC Timing Specifications

This table provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 34. SGMII Transmit AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                           | Symbol            | Min    | Тур | Мах    | Unit   | Note |

|-------------------------------------|-------------------|--------|-----|--------|--------|------|

| Deterministic jitter                | JD                | _      | _   | 0.17   | UI p-p |      |

| Total jitter                        | JT                | —      | _   | 0.35   | UI p-p |      |

| Unit interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1    |

| V <sub>OD</sub> fall time (80%–20%) | tfall             | 50     | _   | 120    | ps     |      |

| V <sub>OD</sub> rise time (20%–80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     |      |

Note:

1. Each UI is 800 ps  $\pm$  100 ppm.

#### 8.3.4.2 SGMII Receive AC Timing Specifications

This table provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 17 shows the SGMII receiver input compliance mask eye diagram.

#### Table 35. SGMII Receive AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                                          | Symbol | Min  | Тур | Max | Unit   | Note |

|----------------------------------------------------|--------|------|-----|-----|--------|------|

| Deterministic jitter tolerance                     | JD     | 0.37 | —   | —   | UI p-p | 1    |

| Combined deterministic and random jitter tolerance | JDR    | 0.55 | —   | —   | UI p-p | 1    |

| Sinusoidal jitter tolerance                        | JSIN   | 0.1  | —   | —   | UI p-p | 1    |

#### Table 36. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with L/TV\_{DD} of 3.3 V  $\pm$  5%.

| Parameter/Condition                   | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|---------------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK peak-to-peak jitter     | t <sub>T1588CLKINJ</sub>                                | —                           |     | 250 | ps   |      |

| Rise time eTSEC_1588_CLK<br>(20%-80%) | t <sub>T1588CLKINR</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| Fall time eTSEC_1588_CLK<br>(80%–20%) | t <sub>T1588CLKINF</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| TSEC_1588_CLK_OUT clock period        | t <sub>T1588</sub> CLKOUT                               | 2 × t <sub>T1588CLK</sub>   | _   | _   | ns   |      |

| TSEC_1588_CLK_OUT duty cycle          | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    |      |

| TSEC_1588_PULSE_OUT                   | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   |      |

| TSEC_1588_TRIG_IN pulse width         | t <sub>T1588</sub> trigh                                | $2 \times t_{T1588CLK_MAX}$ |     | —   | ns   | 2    |

Notes:

1. T<sub>RX\_CLK</sub> is the max clock period of eTSEC receiving clock selected by TMR\_CTRL[CKSEL]. See the *MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual,* for a description of TMR\_CTRL registers.

2. It need to be at least two times of clock period of clock selected by TMR\_CTRL[CKSEL]. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description of TMR\_CTRL registers.

The maximum value of t<sub>T1588CLK</sub> is not only defined by the value of T<sub>RX\_CLK</sub>, but also defined by the recovered clock. For example, for 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 280, and 56 ns, respectively.

### 8.5 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for MII, RMII, RGMII, SGMII, and RTBI are specified in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics."

### 8.5.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. Table 37 provide the DC electrical characteristics for MDIO and MDC.

| Parameter              | Symbol          | Condi                                            | Min                     | Max             | Unit                   |    |

|------------------------|-----------------|--------------------------------------------------|-------------------------|-----------------|------------------------|----|

| Supply voltage (3.3 V) | $NV_{DD}$       | —                                                |                         | 2.97            | 3.63                   | V  |

| Output high voltage    | V <sub>OH</sub> | I <sub>OH</sub> = -1.0 mA NV <sub>DD</sub> = Min |                         | 2.10            | NV <sub>DD</sub> + 0.3 | V  |

| Output low voltage     | V <sub>OL</sub> | I <sub>OL</sub> = 1.0 mA NV <sub>DD</sub> = Min  |                         | V <sub>SS</sub> | 0.50                   | V  |

| Input high voltage     | V <sub>IH</sub> | -                                                | -                       | 2.0             | _                      | V  |

| Input low voltage      | V <sub>IL</sub> | -                                                | -                       | —               | 0.80                   | V  |

| Input high current     | I <sub>IH</sub> | NV <sub>DD</sub> = Max                           | $V_{IN}^{1} = 2.1 V$    | —               | 40                     | μA |

| Input low current      | ۱ <sub>IL</sub> | NV <sub>DD</sub> = Max                           | V <sub>IN</sub> = 0.5 V | -600            | —                      | μΑ |

Table 37. MII Management DC Electrical Characteristics When Powered at 3.3 V

# 11 Enhanced Local Bus

This section describes the DC and AC electrical specifications for the local bus interface.

### **11.1 Local Bus DC Electrical Characteristics**

This table provides the DC electrical characteristics for the local bus interface.

| Table 44. Local Bus DC Electrica | al Characteristics at 3.3 V |

|----------------------------------|-----------------------------|

|----------------------------------|-----------------------------|

| Parameter                                                                  | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage for Rev 1.0                                       | V <sub>IH</sub> | 2.0                    | LV <sub>DD</sub> + 0.3 | V    |

| High-level input voltage for Rev 2.x or later                              | V <sub>IH</sub> | 2.1                    | LV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                    | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current, $(V_{IN}^{1} = 0 \text{ V or } V_{IN} = LV_{DD})$           | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, ( $LV_{DD} = min$ , $I_{OH} = -2 mA$ )          | V <sub>OH</sub> | LV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage, (LV <sub>DD</sub> = min, I <sub>OH</sub> = 2 mA) | V <sub>OL</sub> | —                      | 0.2                    | V    |

Note: The parameters stated in above table are valid for all revisions unless explicitly mentioned.

### 11.2 Local Bus AC Electrical Specifications

This table describes the general timing parameters of the local bus interface.

Table 45. Local Bus General Timing Parameters

| Parameter                                                   | Symbol <sup>1</sup>   | Min  | Мах | Unit | Note |

|-------------------------------------------------------------|-----------------------|------|-----|------|------|

| Local bus cycle time                                        | t <sub>LBK</sub>      | 15   | —   | ns   | 2    |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>   | 7    | —   | ns   | 3, 4 |

| Input hold from local bus clock                             | t <sub>LBIXKH</sub>   | 1.0  | —   | ns   | 3, 4 |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub>  | 1.5  | —   | ns   | 5    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub>  | 3    | —   | ns   | 6    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub>  | 2.5  | —   | ns   | 7    |

| LALE output rise to LCLK negative edge                      | t <sub>LALEHOV</sub>  | —    | 3.0 | ns   |      |

| LALE output fall to LCLK negative edge                      | t <sub>LALETOT1</sub> | -1.5 | —   | ns   | 5    |

| LALE output fall to LCLK negative edge                      | t <sub>LALETOT2</sub> | -5.0 | —   | ns   | 6    |

| LALE output fall to LCLK negative edge                      | t <sub>LALETOT3</sub> | -4.5 | —   | ns   | 7    |

| Local bus clock to output valid                             | t <sub>LBKHOV</sub>   | —    | 3   | ns   | 3    |

| Local bus clock to output high impedance for LAD            | t <sub>LBKHOZ</sub>   | —    | 4   | ns   | 8    |

# 17 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins.

### **17.1 IPIC DC Electrical Characteristics**

This table provides the DC electrical characteristics for the external interrupt pins.

#### Table 58. IPIC DC Electrical Characteristics

| Characteristic     | Symbol          | Condition                | Min  | Мах                    | Unit |

|--------------------|-----------------|--------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                        | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | _                        | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> |                          | _    | ±5                     | μA   |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _    | 0.5                    | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _    | 0.4                    | V    |

### 17.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

Table 59. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

# 18 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8313E.

### **18.1 SPI DC Electrical Characteristics**

This table provides the DC electrical characteristics for the MPC8313E SPI.

Table 60. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                 | Min | Мах | Unit |

|---------------------|-----------------|---------------------------|-----|-----|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA | 2.4 | _   | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA  | _   | 0.5 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _   | 0.4 | V    |

| Signal                                     | Package Pin Number | Pin Type | Power<br>Supply   | Note  |

|--------------------------------------------|--------------------|----------|-------------------|-------|

| TSEC1_TXD1/TSEC_1588_PP2                   | AD6                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TXD0/USBDR_STP/TSEC_1588_PP3         | AD5                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TX_EN/TSEC_1588_ALARM1               | AB7                | 0        | LV <sub>DDB</sub> | —     |

| TSEC1_TX_ER/TSEC_1588_ALARM2               | AB8                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_GTX_CLK125                           | AE1                | I        | LV <sub>DDB</sub> | _     |

| TSEC1_MDC/LB_POR_CFG_BOOT_ECC_DIS          | AF6                | 0        | NV <sub>DD</sub>  | 9, 11 |

| TSEC1_MDIO                                 | AB9                | I/O      | NV <sub>DD</sub>  | _     |

|                                            | ETSEC2             |          |                   |       |

| TSEC2_COL/GTM1_TIN4/GTM2_TIN3/GPIO15       | AB4                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_CRS/GTM1_TGATE4/GTM2_TGATE3/GPIO16   | AB3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_GTX_CLK/GTM1_TOUT4/GTM2_TOUT3/GPI017 | AC1                | I/O      | LV <sub>DDA</sub> | 12    |

| TSEC2_RX_CLK/GTM1_TIN2/GTM2_TIN1/GPIO18    | AC2                | I/O      | LV <sub>DDA</sub> | _     |

| TSCE2_RX_DV/GTM1_TGATE2/GTM2_TGATE1/GPIO19 | AA3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD3/GPIO20                          | Y5                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD2/GPIO21                          | AA4                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD1/GPIO22                          | AB2                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD0/GPIO23                          | AA5                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RX_ER/GTM1_TOUT2/GTM2_TOUT1/GPIO24   | AA2                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_CLK/GPIO25                        | AB1                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD3/CFG_RESET_SOURCE0               | W3                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD2/CFG_RESET_SOURCE1               | Y1                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD1/CFG_RESET_SOURCE2               | W5                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD0/CFG_RESET_SOURCE3               | Y3                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_EN/GPIO26                         | AA1                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_ER/GPI027                         | W1                 | I/O      | LV <sub>DDA</sub> | _     |

|                                            | SGMII PHY          |          |                   |       |

| ТХА                                        | U3                 | 0        |                   | _     |

| TXA                                        | V3                 | 0        |                   | —     |

| RXA                                        | U1                 | I        |                   | —     |

| RXA                                        | V1                 | I        |                   | —     |

| ТХВ                                        | P4                 | 0        |                   | —     |

| ТХВ                                        | N4                 | 0        |                   | _     |

#### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                                           | Package Pin Number                                                                                                     | Pin Type                                                      | Power<br>Supply  | Note |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------|

|                                                  | SPI                                                                                                                    |                                                               | 11               |      |

| SPIMOSI/GTM1_TIN3/GTM2_TIN4/GPIO28/LSRCID4       | H1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | —    |

| SPIMISO/GTM1_TGATE3/GTM2_TGATE4/GPIO29/<br>LDVAL | H3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | _    |

| SPICLK/GTM1_TOUT3/GPIO30                         | G1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> |      |

| SPISEL/GPIO31                                    | G3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | —    |

| Power                                            | and Ground Supplies                                                                                                    |                                                               | •                |      |

| AV <sub>DD1</sub>                                | F14                                                                                                                    | Power for e300 core<br>APLL<br>(1.0 V)                        | —                | _    |

| AV <sub>DD2</sub>                                | P21                                                                                                                    | Power for system<br>APLL (1.0 V)                              | —                | _    |

| GV <sub>DD</sub>                                 | A2,A3,A4,A24,A25,B3,<br>B4,B5,B12,B13,B20,B21,<br>B24,B25,B26,D1,D2,D8,<br>D9,D16,D17                                  | Power for DDR1<br>and DDR2 DRAM<br>I/O voltage<br>(1.8/2.5 V) | —                | _    |

| LV <sub>DD</sub>                                 | D24,D25,G23,H23,R23,<br>T23,W25,Y25,AA22,AC23                                                                          | Power for local bus<br>(3.3 V)                                | —                |      |

| LV <sub>DDA</sub>                                | W2,Y2                                                                                                                  | Power for eTSEC2<br>(2.5 V, 3.3 V)                            | —                | _    |

| LV <sub>DDB</sub>                                | AC8,AC9,AE4,AE5                                                                                                        | Power for eTSEC1/<br>USB DR<br>(2.5 V, 3.3 V)                 | —                | _    |

| MV <sub>REF</sub>                                | C14,D14                                                                                                                | Reference voltage signal for DDR                              | —                | —    |

| NV <sub>DD</sub>                                 | G4,H4,L2,M2,AC16,AC17,<br>AD25,AD26,AE12,AE13,<br>AE20,AE21,AE24,AE25,<br>AE26,AF24,AF25                               | Standard I/O<br>voltage (3.3 V)                               | —                | _    |

| V <sub>DD</sub>                                  | K11,K12,K13,K14,K15,<br>K16,L10,L17,M10,M17,<br>N10,N17,U12,U13,                                                       | Power for core (1.0<br>V)                                     | —                | _    |

| V <sub>DDC</sub>                                 | F6,F10,F19,K6,K10,K17,<br>K21,P6,P10,P17,R10,R17,<br>T10,T17,U10,U11,U14,<br>U15,U16,U17,W6,W21,<br>AA6,AA10,AA14,AA19 | Internal core logic<br>constant power (1.0<br>V)              | —                | _    |

| Unit                                      | Default<br>Frequency | Options                            |

|-------------------------------------------|----------------------|------------------------------------|

| TSEC1                                     | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| TSEC2                                     | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| Security Core, I <sup>2</sup> C, SAP, TPR | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| USB DR                                    | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| PCI and DMA complex                       | csb_clk              | Off, csb_clk                       |

#### Table 63. Configurable Clock Units

This table provides the operating frequencies for the MPC8313E TEPBGAII under recommended operating conditions (see Table 2).

| Characteristic <sup>1</sup>                      | Maximum Operating<br>Frequency | Unit |

|--------------------------------------------------|--------------------------------|------|

| e300 core frequency (core_clk)                   | 333                            | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> ) | 167                            | MHz  |

| DDR1/2 memory bus frequency (MCK) <sup>2</sup>   | 167                            | MHz  |

| Local bus frequency (LCLKn) <sup>3</sup>         | 66                             | MHz  |

| PCI input frequency (SYS_CLK_IN or PCI_CLK)      | 66                             | MHz  |

#### Table 64. Operating Frequencies for TEPBGAII

#### Note:

- The SYS\_CLK\_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK[0:1], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM] and SCCR[USBDRCM] must be programmed such that the maximum internal operating frequency of the security core and USB modules do not exceed their respective value listed in this table.

- 2. The DDR data rate is 2x the DDR memory bus frequency.

- 3. The local bus frequency is 1/2, 1/4, or 1/8 of the *lbc\_clk* frequency (depending on LCRR[CLKDIV]), which is in turn, 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

### 20.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. This table shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0000       | Reserved                            |

| 0001       | Reserved                            |

| 0010       | × 2                                 |

| 0011       | × 3                                 |

#### Table 65. System PLL Multiplication Factors

### 20.3 Example Clock Frequency Combinations

This table shows several possible frequency combinations that can be selected based on the indicated input reference frequencies, with RCWLR[LBCM] = 0 and RCWLR[DDRCM] =1, such that the LBC operates with a frequency equal to the frequency of  $csb\_clk$  and the DDR controller operates at twice the frequency of  $csb\_clk$ .

|                            |                   |                   |                  |                                        |                  |      | LBC(  | lbc_cl | k)                      | e     | 300 Co | ore(cor    | e_clk) |            |

|----------------------------|-------------------|-------------------|------------------|----------------------------------------|------------------|------|-------|--------|-------------------------|-------|--------|------------|--------|------------|

| SYS_<br>CLK_IN/<br>PCI_CLK | SPMF <sup>1</sup> | VCOD <sup>2</sup> | VCO <sup>3</sup> | CSB<br>( <i>csb_clk</i> ) <sup>4</sup> | DDR<br>(ddr_clk) | /2   | /4    | /8     | USB<br>ref <sup>5</sup> | × 1   | × 1.5  | × <b>2</b> | × 2.5  | × <b>3</b> |

| 25.0                       | 6                 | 2                 | 600.0            | 150.0                                  | 300.0            |      | 37.5  | 18.8   | Note <sup>6</sup>       | 150.0 | 225    | 300        | 375    | _          |

| 25.0                       | 5                 | 2                 | 500.0            | 125.0                                  | 250.0            | 62.5 | 31.25 | 15.6   | Note 6                  | 125.0 | 188    | 250        | 313    | 375        |

| 33.3                       | 5                 | 2                 | 666.0            | 166.5                                  | 333.0            | _    | 41.63 | 20.8   | Note 6                  | 166.5 | 250    | 333        | _      | _          |

| 33.3                       | 4                 | 2                 | 532.8            | 133.2                                  | 266.4            | 66.6 | 33.3  | 16.7   | Note 6                  | 133.2 | 200    | 266        | 333    | 400        |

| 48.0                       | 3                 | 2                 | 576.0            | 144.0                                  | 288.0            | _    | 36    | 18.0   | 48.0                    | 144.0 | 216    | 288        | 360    | —          |

| 66.7                       | 2                 | 2                 | 533.4            | 133.3                                  | 266.7            | 66.7 | 33.34 | 16.7   | Note 6                  | 133.3 | 200    | 267        | 333    | 400        |

| Table 68. System Clock Frequencies | Table | 68. | System | Clock | Frequencies |

|------------------------------------|-------|-----|--------|-------|-------------|

|------------------------------------|-------|-----|--------|-------|-------------|

Note:

1. System PLL multiplication factor.

2. System PLL VCO divider.

3. When considering operating frequencies, the valid core VCO operating range of 400–800 MHz must not be violated.

4. Due to erratum eTSEC40, *csb\_clk* frequencies of less than 133 MHz do not support gigabit Ethernet data rates. The core frequency must be 333 MHz for gigabit Ethernet operation. This erratum will be fixed in revision 2 silicon.

5. Frequency of USB PLL input reference.

6. USB reference clock must be supplied from a separate source as it must be 24 or 48 MHz, the USB reference must be supplied from a separate external source using USB\_CLK\_IN.

# 21 Thermal

This section describes the thermal specifications of the MPC8313E.

### 21.1 Thermal Characteristics

This table provides the package thermal characteristics for the 516,  $27 \times 27$  mm TEPBGAII.

| Table 69. Package Th | ermal Characteristics for TEPBGAII |

|----------------------|------------------------------------|

|----------------------|------------------------------------|

| Characteristic                         | Board Type              | Symbol              | TEPBGA II | Unit | Note    |

|----------------------------------------|-------------------------|---------------------|-----------|------|---------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	ext{	heta}JA}$ | 25        | °C/W | 1, 2    |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$ | 18        | °C/W | 1, 2, 3 |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{	hetaJMA}$      | 20        | °C/W | 1, 3    |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	hetaJMA}$      | 15        | °C/W | 1, 3    |

| Junction-to-board                      | _                       | $R_{	heta JB}$      | 10        | °C/W | 4       |

### 21.3 Heat Sink Attachment

When attaching heat sinks to these devices, an interface material is required. The best method is to use thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces which would lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. Recommended maximum force on the top of the package is 10 lb (4.5 kg) force. If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

# 21.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction to case thermal resistance.

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package  $R_{\theta JC}$  = junction-to-case thermal resistance  $P_D$  = power dissipation

$T_I = T_C + (R_{\theta IC} x P_D)$

# 22 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8313E SYS\_CLK\_IN

### 22.1 System Clocking

The MPC8313E includes three PLLs.

- 1. The platform PLL (AV<sub>DD2</sub>) generates the platform clock from the externally supplied SYS\_CLK\_IN input in PCI host mode or SYS\_CLK\_IN/PCI\_SYNC\_IN in PCI agent mode. The frequency ratio between the platform and SYS\_CLK\_IN is selected using the platform PLL ratio configuration bits as described in Section 20.1, "System PLL Configuration."

- 2. The e300 core PLL (AV<sub>DD1</sub>) generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 20.2, "Core PLL Configuration."

- 3. There is a PLL for the SerDes block.

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal NV<sub>DD</sub>, 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(Not Including PCI<br>Output Clocks) | PCI Output Clocks<br>(Including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | Ω    |

Table 71. Impedance Characteristics

Note: Nominal supply voltages. See Table 1,  $T_J$  = 105 °C.

### 22.7 Configuration Pin Muxing

The MPC8313E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when PORESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

### 22.8 Pull-Up Resistor Requirements

The MPC8313E requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C, and IPIC (integrated programmable interrupt controller).

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 61. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions because most have asynchronous behavior and spurious assertion, which give unpredictable results.

Refer to the PCI 2.2 Specification, for all pull-ups required for PCI.

### 22.9 JTAG Configuration Signals

Boundary scan testing is enabled through the JTAG interface signals. The TRST signal is optional in IEEE 1149.1, but is provided on any Freescale devices that are built on Power Architecture technology. The device requires TRST to be asserted during reset conditions to ensure the JTAG boundary logic does not interfere with normal chip operation. While it is possible to force the TAP controller to the reset state using only the TCK and TMS signals, systems generally assert TRST during power-on reset. Because the JTAG interface is also used for accessing the common on-chip processor (COP) function, simply tying TRST to PORESET is not practical.

### 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8313E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | е                                       | t                                       | рр                                              | aa                                           | а                          | X                                            |

|-----------------|--------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------|----------------------------------------------|----------------------------|----------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range <sup>3</sup>       | Package <sup>1, 4</sup>                         | e300 core<br>Frequency <sup>2</sup>          | DDR<br>Frequency           | Revision<br>Level                            |

| MPC             | 8313               | Blank = Not<br>included<br>E = included | Blank = 0° to 105°C<br>C= -40° to 105°C | ZQ = PB<br>TEPBGAII<br>VR = PB free<br>TEPBGAII | AD = 266 MHz<br>AF = 333 MHz<br>AG = 400 MHz | D = 266 MHz<br>F = 333 MHz | Blank = 1.0<br>A = 2.0<br>B = 2.1<br>C = 2.2 |

#### Table 72. Part Numbering Nomenclature

Note:

1. See Section 19, "Package and Pin Listings," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

- 3. Contact local Freescale office on availability of parts with °C temperature range.

- 4. ZQ package was available for Rev 1.0. For Rev 2.x, only VR package is available.

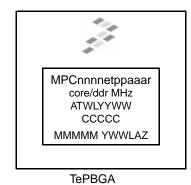

#### 23.2 Part Marking

Parts are marked as shown in this figure.

Notes:

MPCnnnnetppaar is the orderable part number. ATWLYYWW is the standard assembly, test, year, and work week codes. CCCCC is the country code. MMMMM is the mask number.

Figure 62. Part Marking for TEPBGAII Device

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>In Table 63, added LBC_PM_REF_10 &amp; LSRCID3 as muxed with USBDR_PCTL1</li> <li>In Table 63, added LSRCID2 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL2 VBUS</li> <li>In Table 63, moved 71, U2,&amp; V2 from V<sub>DD</sub> to XCOREVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; V4 from V<sub>SS</sub> to XCOREVDS.</li> <li>In Table 63, added impedance control requirements for SD_IMP_CAL_TX (100 ohms to GND) and SD_IMP_CAL_RX (200 ohms to GND).</li> <li>In Table 63, updated muxing in pinout to show new options for selecting IEEE 1588 functionality. Added footnote 8</li> <li>In Table 63, updated muxing in pinout to show new LBC ECC boot enable control muxed with eTSEC1_MDC</li> <li>Added pin type information for power supplies.</li> <li>Removed N1 and N3 from Vss section of Table 63. Added Therm0 and Therm1 (N1 and N3, respectively). Added note 7 to state: "Internal thermally sensitive resistor, resistor value varies linearly with temperature."</li> <li>In Table 65 corrected maximum frequency of Local Bus Frequency from "33–66" to 66 MHz</li> <li>In Table 65 corrected maximum frequency of PCI from "24–66" to 66 MHz</li> <li>Added "which is determined by RCWLR[COREPLL]" to the note in Section 20.2, "Core PLL Configuration" about the VCO divider.</li> <li>Added "Walues.</li> <li>In Table 69, notes were confusing. Added note 3 for VCO column, note 4 for CSB (<i>csb_c.lk</i>) column, note 5 for USB ref column, and note 6 to replace "Note 1". Clarified note 4 to explain errature of Section 20.2, "Core PLL Configuration" about the VCO divider column in Table 68. Added footnote stating that core_clk frequency must not exceed its maximum, so 2.5:1 and 3:1 <i>core_clk:csb_c.lk</i> ratios are invalid for certain <i>csb_c.lk</i> values.</li> <li>In Table 69, updated note 6 to specify U</li></ul> |

| 0              | 6/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |