### NXP USA Inc. - KMPC8313EVRAFFB Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 333MHz                                                                  |

| Co-Processors/DSP               | Security; SEC 2.2                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 + PHY (1)                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | Cryptography                                                            |

| Package / Case                  | 516-BBGA Exposed Pad                                                    |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8313evraffb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

## 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

## 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

## 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

- Full and half-duplex Ethernet support (1000 Mbps supports only full-duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE 802.1 virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound packets

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

## **1.8 Programmable Interrupt Controller (PIC)**

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model supports 5 external and 34 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

## 1.9 Power Management Controller (PMC)

The MPC8313E power management controller includes the following features:

- Provides power management when the device is used in both host and agent modes

- Supports PCI power management 1.2 D0, D1, D2, D3hot, and D3cold states

- On-chip split power supply controlled through external power switch for minimum standby power

- Support for PME generation in PCI agent mode, PME detection in PCI host mode

- Supports wake-up from Ethernet (Magic Packet), USB, GPIO, and PCI (PME input as host)

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 1. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

|                                          | Characteristic                                                                                         | Symbol                               | Max Value                                                                    | Unit | Note |

|------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|------|

| Core supply volta                        | age                                                                                                    | V <sub>DD</sub>                      | -0.3 to 1.26                                                                 | V    | —    |

| PLL supply voltage                       |                                                                                                        | AV <sub>DD</sub>                     | -0.3 to 1.26                                                                 | V    |      |

| Core power supp                          | bly for SerDes transceivers                                                                            | XCOREV <sub>DD</sub>                 | -0.3 to 1.26                                                                 | V    |      |

| Pad power supply for SerDes transceivers |                                                                                                        | XPADV <sub>DD</sub>                  | -0.3 to 1.26                                                                 | V    | —    |

| DDR and DDR2 DRAM I/O voltage            |                                                                                                        | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                                 | V    |      |

| PCI, local bus, D<br>and JTAG I/O vo     | UART, system control and power management, I <sup>2</sup> C, Itage                                     | NV <sub>DD</sub> /LV <sub>DD</sub>   | -0.3 to 3.6                                                                  | V    |      |

| eTSEC, USB                               |                                                                                                        | LV <sub>DDA</sub> /LV <sub>DDB</sub> | -0.3 to 3.6                                                                  | V    | _    |

| Input voltage                            | DDR DRAM signals                                                                                       | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                          | DDR DRAM reference                                                                                     | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                          | Enhanced three-speed Ethernet signals                                                                  | LV <sub>IN</sub>                     | -0.3 to (LV <sub>DDA</sub> + 0.3)<br>or<br>-0.3 to (LV <sub>DDB</sub> + 0.3) | V    | 4, 5 |

|                                          | Local bus, DUART, SYS_CLK_IN, system control, and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 3, 5 |

|                                          | PCI                                                                                                    | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 6    |

| Storage tempera                          | ture range                                                                                             | T <sub>STG</sub>                     | -55 to 150                                                                   | °C   | —    |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** NV<sub>IN</sub> must not exceed NV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: LV<sub>IN</sub> must not exceed LV<sub>DDA</sub>/LV<sub>DDB</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

## 2.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for the MPC8313E. Note that the values in this table are the recommended and tested operating conditions. If a particular block is given a voltage falling within the range in the Recommended Value column, the MPC8313E is capable of delivering the amount of current listed in the Current Requirement column; this is the maximum current possible. Proper device operation outside of these conditions is not guaranteed.

### Table 2. Recommended Operating Conditions (continued)

| Characteristic Symbol Recommended Value <sup>1</sup> Unit | Current<br>Requirement |

|-----------------------------------------------------------|------------------------|

|-----------------------------------------------------------|------------------------|

Note:

- 1. GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. Some GPIO pins may operate from a 2.5-V supply when configured for other functions.

- 3. Min temperature is specified with  $T_A$ ; Max temperature is specified with  $T_J$

- 4. All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.

- 5. All I/O pins should be interfaced with peripherals operating at same voltage level.

- This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

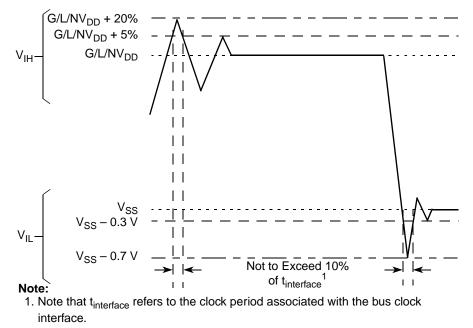

This figure shows the undershoot and overshoot voltages at the interfaces of the MPC8313E.

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/NV<sub>DD</sub>/LV<sub>DD</sub>

### 2.1.3 Output Driver Characteristics

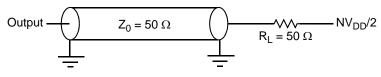

This table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

| Driver Type                           | Output Impedance ( $\Omega$ ) | Supply Voltage           |

|---------------------------------------|-------------------------------|--------------------------|

| Local bus interface utilities signals | 42                            | NV <sub>DD</sub> = 3.3 V |

| PCI signals                           | 25                            |                          |

| DDR signal                            | 18                            | GV <sub>DD</sub> = 2.5 V |

This table provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —    |

This table provides the input AC timing specifications for the DDR2 SDRAM interface.

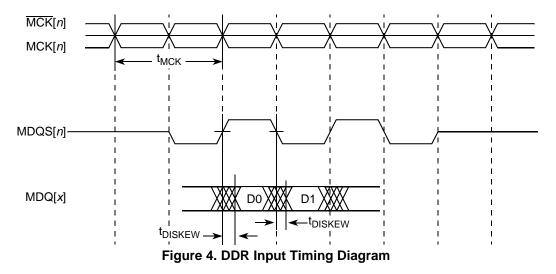

#### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $\text{GV}_{\text{DD}}$  of 2.5 ± 5%.

| Parameter                    | Symbol              | Min  | Мах | Unit | Note |

|------------------------------|---------------------|------|-----|------|------|

| Controller skew for MDQS—MDQ | t <sub>CISKEW</sub> | _    | _   | ps   | 1, 2 |

| 333 MHz                      |                     | -750 | 750 |      | —    |

| 266 MHz                      | _                   | -750 | 750 | _    | —    |

Notes:

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[*n*] and any corresponding bit that is captured with MDQS[*n*]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure illustrates the DDR input timing diagram showing the t<sub>DISKEW</sub> timing parameter.

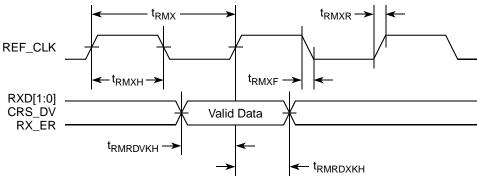

## 8.2.1.4 RMII Receive AC Timing Specifications

This table provides the RMII receive AC timing specifications.

### Table 29. RMII Receive AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock period                                                   | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _   | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                          | t <sub>RMRDVKH</sub>                | 4.0 | _   | —   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                           | t <sub>RMRDXKH</sub>                | 2.0 | -   | —   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>                   | 1.0 | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

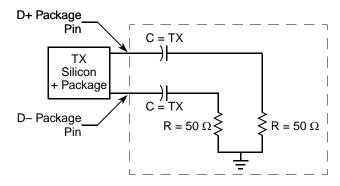

This table provides the AC test load.

Figure 12. AC Test Load

This table shows the RMII receive AC timing diagram.

Figure 13. RMII Receive AC Timing Diagram

## 8.2.2 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

### Table 30. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DDA}/LV_{DDB}$  of 2.5 V ± 5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|---------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                    | -0.5 | —   | 0.5  | ns   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                    | 1.0  | _   | 2.6  | ns   |

| Clock cycle duration <sup>3</sup>                      | t <sub>RGT</sub>                      | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4, 5</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 5</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                     | —    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                     | _    | —   | 0.75 | ns   |

| GTX_CLK125 reference clock period                      | t <sub>G12</sub> <sup>6</sup>         | —    | 8.0 | —    | ns   |

| GTX_CLK125 reference clock duty cycle                  | t <sub>G125H</sub> /t <sub>G125</sub> | 47   | —   | 53   | %    |

Note:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the RTBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is  $LV_{DDA}/2$  or  $LV_{DDB}/2$ .

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. The frequency of RX\_CLK should not exceed the GTX\_CLK125 by more than 300 ppm

Figure 18. SGMII AC Test/Measurement Load

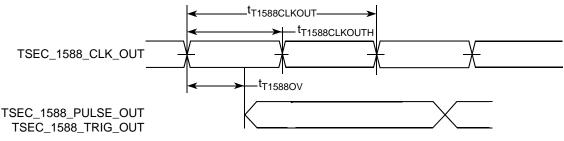

## 8.4 eTSEC IEEE 1588 AC Specifications

This figure provides the data and command output timing diagram.

**Note:** The output delay is count starting rising edge if t<sub>T1588CLKOUT</sub> is non-inverting. Otherwise, it is count starting falling edge.

Figure 19. eTSEC IEEE 1588 Output AC Timing

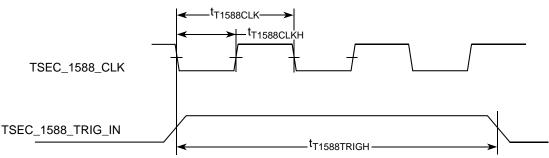

This figure provides the data and command input timing diagram.

Figure 20. eTSEC IEEE 1588 Input AC Timing

This table lists the IEEE 1588 AC timing specifications.

### Table 36. eTSEC IEEE 1588 AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition        | Symbol                                        | Min | Тур | Мах                    | Unit | Note |

|----------------------------|-----------------------------------------------|-----|-----|------------------------|------|------|

| TSEC_1588_CLK clock period | t <sub>T1588CLK</sub>                         | 3.8 | _   | $T_{RX\_CLK} \times 9$ | ns   | 1, 3 |

| TSEC_1588_CLK duty cycle   | t <sub>T1588CLKH</sub> /t <sub>T1588CLK</sub> | 40  | 50  | 60                     | %    |      |

### Table 37. MII Management DC Electrical Characteristics When Powered at 3.3 V (continued)

#### Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the NV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

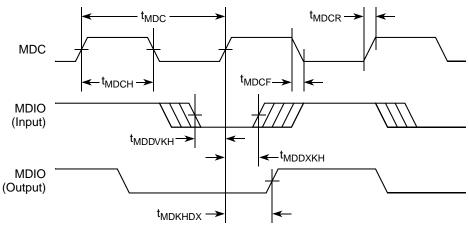

## 8.5.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

#### Table 38. MII Management AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> is  $3.3 \text{ V} \pm 0.3 \text{V}$

| Parameter/Condition        | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Note |

|----------------------------|---------------------|-----|-----|-----|------|------|

| MDC frequency              | f <sub>MDC</sub>    | _   | 2.5 | _   | MHz  | 2    |

| MDC period                 | t <sub>MDC</sub>    | _   | 400 | —   | ns   |      |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32  | —   | —   | ns   |      |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10  | —   | 170 | ns   |      |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5   | —   | —   | ns   |      |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0   | —   | —   | ns   |      |

| MDC rise time              | t <sub>MDCR</sub>   | _   | —   | 10  | ns   |      |

| MDC fall time              | t <sub>MDHF</sub>   | _   | —   | 10  | ns   |      |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

2. This parameter is dependent on the csb\_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC\_MDC.)

This figure shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

Figure 32. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following section for detailed information:

• Section 8.3.2, "AC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK"

### 9.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

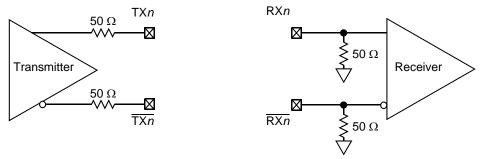

## 9.3 SerDes Transmitter and Receiver Reference Circuits

This figure shows the reference circuits for the SerDes data lane's transmitter and receiver.

Figure 33. SerDes Transmitter and Receiver Reference Circuits

The SerDes data lane's DC and AC specifications are defined in the interface protocol section listed below (SGMII) based on the application usage:

• Section 8.3, "SGMII Interface Electrical Characteristics"

Please note that a external AC-coupling capacitor is required for the above serial transmission protocol with the capacitor value defined in the specifications of the protocol section.

# 17 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins.

## **17.1 IPIC DC Electrical Characteristics**

This table provides the DC electrical characteristics for the external interrupt pins.

### Table 58. IPIC DC Electrical Characteristics

| Characteristic     | Symbol          | Condition                | Min  | Мах                    | Unit |

|--------------------|-----------------|--------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                        | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | _                        | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> |                          | _    | ±5                     | μA   |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _    | 0.5                    | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _    | 0.4                    | V    |

## 17.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

Table 59. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

# 18 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8313E.

## **18.1 SPI DC Electrical Characteristics**

This table provides the DC electrical characteristics for the MPC8313E SPI.

Table 60. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                 | Min | Мах | Unit |

|---------------------|-----------------|---------------------------|-----|-----|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA | 2.4 | _   | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA  | —   | 0.5 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —   | 0.4 | V    |

## **19.3 Pinout Listings**

This table provides the pin-out listing for the MPC8313E, TEPBGAII package.

| Signal                          | Package Pin Number | Pin Type | Power<br>Supply  | Note |  |  |  |  |  |

|---------------------------------|--------------------|----------|------------------|------|--|--|--|--|--|

| DDR Memory Controller Interface |                    |          |                  |      |  |  |  |  |  |

| MEMC_MDQ0                       | A8                 | I/O      | GV <sub>DD</sub> | —    |  |  |  |  |  |

| MEMC_MDQ1                       | A9                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ2                       | C10                | I/O      | GV <sub>DD</sub> | —    |  |  |  |  |  |

| MEMC_MDQ3                       | C9                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ4                       | E9                 | I/O      | GV <sub>DD</sub> | —    |  |  |  |  |  |

| MEMC_MDQ5                       | E11                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ6                       | E10                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ7                       | C8                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ8                       | E8                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ9                       | A6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ10                      | B6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ11                      | C6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ12                      | C7                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ13                      | D7                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ14                      | D6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ15                      | A5                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ16                      | A19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ17                      | D18                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ18                      | A17                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ19                      | E17                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ20                      | E16                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ21                      | C18                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ22                      | D19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ23                      | C19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ24                      | E19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ25                      | A22                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ26                      | C21                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ27                      | C20                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ28                      | A21                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

### Table 62. MPC8313E TEPBGAII Pinout Listing

| Signal     | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|------------|--------------------|----------|------------------|------|

| MEMC_MDQ29 | A20                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDQ30 | C22                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQ31 | B22                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDM0  | B7                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM1  | E6                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM2  | E18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM3  | E20                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDQS0 | A7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS1 | E7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS2 | B19                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS3 | A23                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MBA0  | D15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA1  | A18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA2  | A15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA0   | E12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA1   | D11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA2   | B11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA3   | A11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA4   | A12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA5   | E13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA6   | C12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA7   | E14                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA8   | B15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA9   | C17                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA10  | C13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA11  | A16                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA12  | C15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA13  | C16                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA14  | E15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MWE   | B18                | 0        | GV <sub>DD</sub> |      |

| MEMC_MRAS  | C11                | 0        | GV <sub>DD</sub> |      |

| MEMC_MCAS  | B10                | 0        | GV <sub>DD</sub> |      |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal         | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|----------------|--------------------|----------|------------------|------|

| TMS            | E4                 | l        | NV <sub>DD</sub> | 4    |

| TRST           | E5                 | I        | NV <sub>DD</sub> | 4    |

|                | TEST               |          | I I              |      |

| TEST_MODE      | F4                 | l        | $NV_{DD}$        | 6    |

|                | DEBUG              |          |                  |      |

| QUIESCE        | F5                 | 0        | $NV_{DD}$        | _    |

|                | System Control     |          |                  |      |

| HRESET         | F2                 | I/O      | $NV_{DD}$        | 1    |

| PORESET        | F3                 | I        | NV <sub>DD</sub> | _    |

| SRESET         | F1                 | I        | NV <sub>DD</sub> | _    |

|                | Clocks             |          |                  |      |

| SYS_CR_CLK_IN  | U26                | I        | NV <sub>DD</sub> | _    |

| SYS_CR_CLK_OUT | U25                | 0        | NV <sub>DD</sub> | _    |

| SYS_CLK_IN     | U23                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_IN  | T26                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_OUT | R26                | 0        | NV <sub>DD</sub> | _    |

| USB_CLK_IN     | T22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_OUT   | U24                | 0        | NV <sub>DD</sub> | 3    |

| RTC_PIT_CLOCK  | R22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_IN    | T24                | I        | NV <sub>DD</sub> |      |

|                | MISC               |          | I I              |      |

| THERM0         | N1                 | Ι        | NV <sub>DD</sub> | 7    |

| THERM1         | N3                 | Ι        | NV <sub>DD</sub> | 7    |

|                | PCI                |          | I I              |      |

| PCI_INTA       | AF7                | 0        | NV <sub>DD</sub> | _    |

| PCI_RESET_OUT  | AB11               | 0        | NV <sub>DD</sub> | _    |

| PCI_AD0        | AB20               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD1        | AF23               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD2        | AF22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD3        | AB19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD4        | AE22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD5        | AF21               | I/O      | NV <sub>DD</sub> | _    |

| Signal    | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|-----------|--------------------|----------|------------------|------|

| PCI_AD6   | AD19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD7   | AD20               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD8   | AC18               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD9   | AD18               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD10  | AB18               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD11  | AE19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD12  | AB17               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD13  | AE18               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD14  | AD17               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD15  | AF19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD16  | AB14               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD17  | AF15               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD18  | AD14               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD19  | AE14               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD20  | AF12               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD21  | AE11               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD22  | AD12               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD23  | AB13               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD24  | AF9                | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD25  | AD11               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD26  | AE10               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD27  | AB12               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD28  | AD10               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD29  | AC10               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD30  | AF10               | I/O      | NV <sub>DD</sub> |      |

| PCI_AD31  | AF8                | I/O      | NV <sub>DD</sub> |      |

| PCI_C/BE0 | AC19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_C/BE1 | AB15               | I/O      | NV <sub>DD</sub> | _    |

| PCI_C/BE2 | AF14               | I/O      | NV <sub>DD</sub> | _    |

| PCI_C/BE3 | AF11               | I/O      | NV <sub>DD</sub> | _    |

| PCI_PAR   | AD16               | I/O      | NV <sub>DD</sub> | _    |

| PCI_FRAME | AF16               | I/O      | $NV_{DD}$        | 5    |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

## 20.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in this table should be considered as reserved.

### NOTE

Core VCO frequency = core frequency  $\times$  VCO divider. The VCO divider, which is determined by RCWLR[COREPLL], must be set properly so that the core VCO frequency is in the range of 400–800 MHz.

| RCWL[COREPLL] |      | 'LL] | core_clk : csb_clk Ratio <sup>1</sup>                          | VCO Divider (VCOD) <sup>3</sup>                                |

|---------------|------|------|----------------------------------------------------------------|----------------------------------------------------------------|

| 0–1           | 2–5  | 6    | core_cik : csb_cik Ratio                                       |                                                                |

| nn            | 0000 | 0    | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) |

| 11            | nnnn | n    | n/a                                                            | n/a                                                            |

| 00            | 0001 | 0    | 1:1                                                            | 2                                                              |

| 01            | 0001 | 0    | 1:1                                                            | 4                                                              |

| 10            | 0001 | 0    | 1:1                                                            | 8                                                              |

| 00            | 0001 | 1    | 1.5:1                                                          | 2                                                              |

| 01            | 0001 | 1    | 1.5:1                                                          | 4                                                              |

| 10            | 0001 | 1    | 1.5:1                                                          | 8                                                              |

| 00            | 0010 | 0    | 2:1                                                            | 2                                                              |

| 01            | 0010 | 0    | 2:1                                                            | 4                                                              |

| 10            | 0010 | 0    | 2:1                                                            | 8                                                              |

| 00            | 0010 | 1    | 2.5:1                                                          | 2                                                              |

| 01            | 0010 | 1    | 2.5:1                                                          | 4                                                              |

| 10            | 0010 | 1    | 2.5:1                                                          | 8                                                              |

| 00            | 0011 | 0    | 3:1                                                            | 2                                                              |

| 01            | 0011 | 0    | 3:1                                                            | 4                                                              |

| 10            | 0011 | 0    | 3:1                                                            | 8                                                              |

### Table 67. e300 Core PLL Configuration

Note:

1. For core\_clk:csb\_clk ratios of 2.5:1 and 3:1, the core\_clk must not exceed its maximum operating frequency of 333 MHz.

2. Core VCO frequency = core frequency × VCO divider. Note that VCO divider has to be set properly so that the core VCO frequency is in the range of 400–800 MHz.

## 20.3 Example Clock Frequency Combinations

This table shows several possible frequency combinations that can be selected based on the indicated input reference frequencies, with RCWLR[LBCM] = 0 and RCWLR[DDRCM] =1, such that the LBC operates with a frequency equal to the frequency of  $csb\_clk$  and the DDR controller operates at twice the frequency of  $csb\_clk$ .

|                            |                   |                   |                  |                                        |                  |      | LBC(  | lbc_cl | k)                      | e     | 300 Co | ore(cor    | e_clk) |            |

|----------------------------|-------------------|-------------------|------------------|----------------------------------------|------------------|------|-------|--------|-------------------------|-------|--------|------------|--------|------------|

| SYS_<br>CLK_IN/<br>PCI_CLK | SPMF <sup>1</sup> | VCOD <sup>2</sup> | VCO <sup>3</sup> | CSB<br>( <i>csb_clk</i> ) <sup>4</sup> | DDR<br>(ddr_clk) | /2   | /4    | /8     | USB<br>ref <sup>5</sup> | × 1   | × 1.5  | × <b>2</b> | × 2.5  | × <b>3</b> |

| 25.0                       | 6                 | 2                 | 600.0            | 150.0                                  | 300.0            |      | 37.5  | 18.8   | Note <sup>6</sup>       | 150.0 | 225    | 300        | 375    | _          |

| 25.0                       | 5                 | 2                 | 500.0            | 125.0                                  | 250.0            | 62.5 | 31.25 | 15.6   | Note 6                  | 125.0 | 188    | 250        | 313    | 375        |

| 33.3                       | 5                 | 2                 | 666.0            | 166.5                                  | 333.0            | _    | 41.63 | 20.8   | Note 6                  | 166.5 | 250    | 333        | _      | _          |

| 33.3                       | 4                 | 2                 | 532.8            | 133.2                                  | 266.4            | 66.6 | 33.3  | 16.7   | Note 6                  | 133.2 | 200    | 266        | 333    | 400        |

| 48.0                       | 3                 | 2                 | 576.0            | 144.0                                  | 288.0            | _    | 36    | 18.0   | 48.0                    | 144.0 | 216    | 288        | 360    | —          |

| 66.7                       | 2                 | 2                 | 533.4            | 133.3                                  | 266.7            | 66.7 | 33.34 | 16.7   | Note 6                  | 133.3 | 200    | 267        | 333    | 400        |

| Table 68. System Clock Frequencies | Table | 68. | System | Clock | Frequencies |

|------------------------------------|-------|-----|--------|-------|-------------|

|------------------------------------|-------|-----|--------|-------|-------------|

Note:

1. System PLL multiplication factor.

2. System PLL VCO divider.

3. When considering operating frequencies, the valid core VCO operating range of 400–800 MHz must not be violated.

4. Due to erratum eTSEC40, *csb\_clk* frequencies of less than 133 MHz do not support gigabit Ethernet data rates. The core frequency must be 333 MHz for gigabit Ethernet operation. This erratum will be fixed in revision 2 silicon.

5. Frequency of USB PLL input reference.

6. USB reference clock must be supplied from a separate source as it must be 24 or 48 MHz, the USB reference must be supplied from a separate external source using USB\_CLK\_IN.

# 21 Thermal

This section describes the thermal specifications of the MPC8313E.

## 21.1 Thermal Characteristics

This table provides the package thermal characteristics for the 516,  $27 \times 27$  mm TEPBGAII.

| Table 69. Package Th | ermal Characteristics for TEPBGAII |

|----------------------|------------------------------------|

|----------------------|------------------------------------|

| Characteristic                         | Board Type              | Symbol              | TEPBGA II | Unit | Note    |

|----------------------------------------|-------------------------|---------------------|-----------|------|---------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	ext{	heta}JA}$ | 25        | °C/W | 1, 2    |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$ | 18        | °C/W | 1, 2, 3 |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{	hetaJMA}$      | 20        | °C/W | 1, 3    |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	hetaJMA}$      | 15        | °C/W | 1, 3    |

| Junction-to-board                      | _                       | $R_{	heta JB}$      | 10        | °C/W | 4       |

#### Notes:

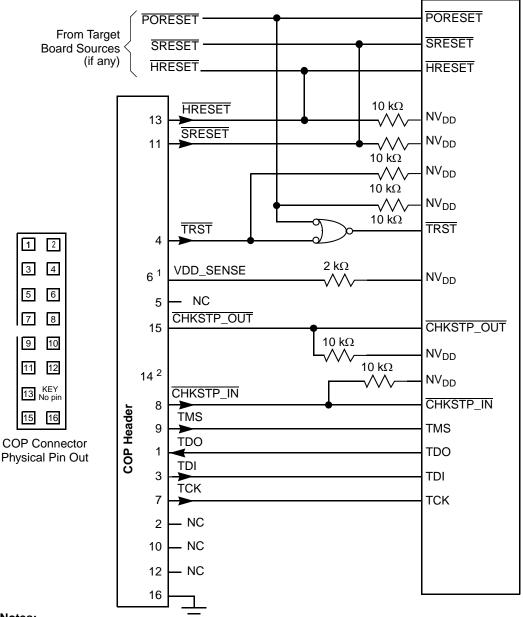

Some systems require power to be fed from the application board into the debugger repeater card via the COP header. In this case the resistor value for VDD\_SENSE should be around 20 Ω.

Key location; pin 14 is not physically present on the COP header.

Figure 61. JTAG Interface Connection

## 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 10/2008 | <ul> <li>Added Note "The information in this document is accurate for revision 1.0, and 2.x and later. See Section 24.1, "Part Numbers Fully Addressed by this Document," before Section 1, "Overview."</li> <li>Added part numbering details for all the silicon revisions in Table 74.</li> <li>Changed V<sub>IH</sub> from 2.7 V to 2.4 V in Table 7.</li> <li>Added a column for maximum power dissipation in low power mode for Rev 2.x or later silicon in Table 6.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added Table 21 for DDR AC Specs on Rev 2.x or later silicon.</li> <li>Added EfWE, LFCLE, LFALE, LOE, LFRE, LFWP, LGTA, LUPWAIT, and LFRB in Table 63.</li> <li>In Table 39, added note 2: "This parameter is dependent on the csb_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC_MDC.)"</li> <li>Removed mentions of SGMII (SGMII has separate specs) from Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/STBI Electrical Characteristics."</li> <li>Corrected Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/SGMII/RTBI Electrical Characteristics," to state that RGMII/RTBI Interfaces only operate at 2.5 V, not 3.3 V.</li> <li>Added ZQ package to ordering information In Table 74 and Section 19.1, "Package Parameters for the MPC8313E TEPBGAII" (applicable to both silicon rev. 1.0 and 2.1)</li> <li>Removed footnotes 5 and 6 from Table 1 (left over when the PCI undershoot/overshoot voltages and maximum AC waveforms were removed from Section 2.1.2, "Power Supply Voltage Specification").</li> <li>Removed SD_PLL_TPD (T2) and SD_PLL_TPA_ANA (R4) from Table 63.</li> <li>Added Section 8.3, "SGMII Interface Electrical Characteristics." Removed Section 8.5.3 SGMII DC Electrical Characteristics.</li> <li>Removed "HRESET negation to S</li></ul> |

### Table 73. Document Revision History (continued)

-

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>Replaced OVDD with NV<sub>DD</sub> everywhere</li> <li>Added XCOREVDD and XPADVDD to Table 1</li> <li>Moved VDD and VDDC to the top of the table before SerDes supplies in Table 2</li> <li>In Table 2 split DDR row into two from total current requirement of 425 mA. One for DDR1 (131 mA) and other for DDR2 (140 mA).</li> <li>In Table 2 corrected current requirement numbers for NV<sub>DD</sub> from 27 mA to 74 mA, LV<sub>DD</sub> from 60 mA to 16 mA, LV<sub>DD</sub> from 85 mA to 22 mA and LV<sub>DDB</sub> from 85 mA to 44 mA.</li> <li>In Table 2 corrected Vdd and Vddc current requirements from 560 mA and 454 mA to 469 and 377 mA, respectively. Corrected Avdd1 and Avdd2 current requirements from 10 mA to 2–3 mA, and XCOREVDD from 100 mA to 170 mA.</li> <li>In Table 2, added row stating junction temperature range of 0 to 105°C. Added footnote 2 stating GPIO pins may operate from 2.5-V supply as well when configured for different functionality.</li> <li>In Section 2.1.2, "Power Supply Voltage Specification," added a note describing the purpose of Table 2.</li> <li>In Section 2.1.2, "Power Sequencing," and added Figure 3.</li> <li>In Table 4, added "but do include core, USB PLL, and a portion of SerDes digital power" to Note 1.</li> <li>In Table 4 corrected "Typical power" to "Maximum power" in note 2 and added a note for Typical Power.</li> <li>In Table 5, moved Local bus typical power dissipation under LVdd.</li> <li>Added Table 6 to show the low power mode power dissipation for D3warm mode.</li> <li>In Table 4, added riminum value of USB input hold t<sub>USIXKH</sub> from 0 to 1ns</li> <li>Added Table 40 and fulle 44 showing USB clock in specifications"</li> <li>In Table 42, added now for rise time (t<sub>L2CF</sub>). Removed minimum value of t<sub>L2CF</sub> Added note 5 stating that the device does not follow the 12C-BUS Specifications version 2.1 regarding the t<sub>L2CF</sub> AC parameter.</li> <li>In Table 46, added nows for tipse time (t<sub>L2CR</sub>). Removed minimum value of t<sub>L2CF</sub> Added note 5 stating that the device does not follow the 12C-BUS Specifications version 2.1 regardin</li></ul> |

### Table 73. Document Revision History (continued)