# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 267MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 516-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8313zqaddb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

### 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

### 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

### 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

## **3** Power Characteristics

The estimated typical power dissipation, not including I/O supply power, for this family of MPC8313E devices is shown in this table. Table 5 shows the estimated typical I/O power dissipation.

| Core Frequency<br>(MHz) | CSB Frequency<br>(MHz) | Typical <sup>2</sup> | Maximum for<br>Rev. 1.0 Silicon <sup>3</sup> | Maximum for<br>Rev. 2.x or Later Silicon <sup>3</sup> | Unit |

|-------------------------|------------------------|----------------------|----------------------------------------------|-------------------------------------------------------|------|

| 333                     | 167                    | 820                  | 1020                                         | 1200                                                  | mW   |

| 400                     | 133                    | 820                  | 1020                                         | 1200                                                  | mW   |

#### Table 4. MPC8313E Power Dissipation<sup>1</sup>

#### Note:

The values do not include I/O supply power or AV<sub>DD</sub>, but do include core, USB PLL, and a portion of SerDes digital power (not including XCOREV<sub>DD</sub>, XPADV<sub>DD</sub>, or SDAV<sub>DD</sub>, which all have dedicated power supplies for the SerDes PHY).

2. Typical power is based on a voltage of  $V_{DD}$  = 1.05 V and an artificial smoker test running at room temperature.

3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoker test.

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                                                                                                                                                               | Parameter           | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|--------------------------|

| DDR 1, 60% utilization,<br>50% read/write<br>$R_s = 22 \Omega$<br>$R_t = 50 \Omega$<br>single pair of clock<br>capacitive load: data = 8 pF,<br>control address = 8 pF,<br>clock = 8 pF | 333 MHz,<br>32 bits | _                           | 0.355                       | _                           | _                                                   | —                                                   | _                           | W    | —                        |

|                                                                                                                                                                                         | 266 MHz,<br>32 bits | _                           | 0.323                       | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| DDR 2, 60% utilization,<br>50% read/write<br>$R_s = 22 \Omega$<br>$R_t = 75 \Omega$<br>single pair of clock<br>capacitive load: data = 8 pF,<br>control address = 8 pF,<br>clock = 8 pF | 333 MHz,<br>32 bits | 0.266                       | —                           | _                           | _                                                   | —                                                   | _                           | W    | —                        |

|                                                                                                                                                                                         | 266 MHz,<br>32 bits | 0.246                       | _                           | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| PCI I/O load = 50 pF                                                                                                                                                                    | 33 MHz              | —                           | —                           | 0.120                       |                                                     | _                                                   | —                           | W    | —                        |

|                                                                                                                                                                                         | 66 MHz              |                             |                             | 0.249                       |                                                     | —                                                   | —                           | W    | —                        |

| Local bus I/O load = 20 pF                                                                                                                                                              | 66 MHz              |                             |                             |                             |                                                     | —                                                   | 0.056                       | W    | —                        |

|                                                                                                                                                                                         | 50 MHz              |                             |                             | _                           | _                                                   | —                                                   | 0.040                       | W    | _                        |

| TSEC I/O load = 20 pF                                                                                                                                                                   | MII,<br>25 MHz      | —                           | —                           | —                           | 0.008                                               | —                                                   | —                           | W    | Multiple by<br>number of |

|                                                                                                                                                                                         | RGMII,<br>125 MHz   | _                           | _                           | —                           | 0.078                                               | 0.044                                               | —                           | W    | interface used           |

Table 5. MPC8313E Typical I/O Power Dissipation

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

| Parameter/Condition                             | Symbol          | Min   | Мах  | Unit | Note |

|-------------------------------------------------|-----------------|-------|------|------|------|

| Output leakage current                          | I <sub>OZ</sub> | -9.9  | -9.9 | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub> | -16.2 | —    | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub> | 16.2  | _    | mA   | _    |

Note:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 15. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

#### Table 16. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Мах | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> | —   | 500 | μΑ   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

### 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM when  $GV_{DD}(typ) = 1.8 V$ .

#### Table 17. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —    |

#### NOTE

For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

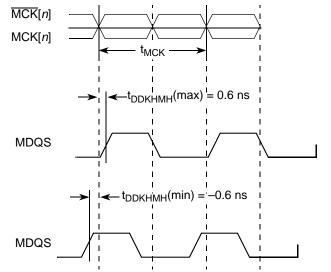

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

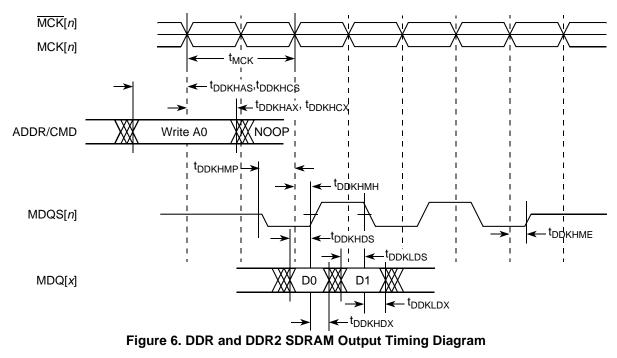

This figure shows the DDR and DDR2 SDRAM output timing diagram.

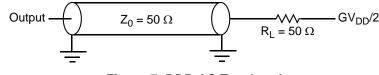

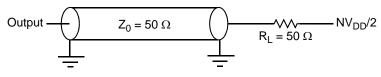

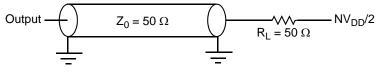

This figure provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

## 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

### 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

| Parameter                                                           | Symbol          | Min                    | Max                    | Unit |

|---------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                            | V <sub>IH</sub> | 2.0                    | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage NV <sub>DD</sub>                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$                  | V <sub>OH</sub> | NV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$                    | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ±5                     | μA   |

### 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

#### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          | _    | 2    |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

## 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all the media independent interface (MII), reduced gigabit media independent interface (RGMII), serial gigabit media independent interface (SGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the MII interface can be operated at 3.3 V. The RMII and SGMII interfaces can be operated at either 3.3 or 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for *Gigabit Ethernet Physical Layer Device Specification Version 1.2a* (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.5, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 **TSEC DC Electrical Characteristics**

All RGMII, RMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 24 and Table 25. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

#### NOTE

eTSEC should be interfaced with peripheral operating at same voltage level.

| Parameter            | Symbol                               | Conditions                                   |                                    | Min             | Max                                                      | Unit |

|----------------------|--------------------------------------|----------------------------------------------|------------------------------------|-----------------|----------------------------------------------------------|------|

| Supply voltage 3.3 V | LV <sub>DDA</sub> /LV <sub>DDB</sub> |                                              | _                                  | 2.97            | 3.63                                                     | V    |

| Output high voltage  | V <sub>OH</sub>                      | I <sub>OH</sub> = -4.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$     | 2.40            | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>                      | I <sub>OL</sub> = 4.0 mA                     | $LV_{DDA}$ or $LV_{DDB}$ = Min     | V <sub>SS</sub> | 0.50                                                     | V    |

| Input high voltage   | V <sub>IH</sub>                      | _                                            | _                                  | 2.0             | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>                      | _                                            | —                                  | -0.3            | 0.90                                                     | V    |

| Input high current   | Ι <sub>ΙΗ</sub>                      | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                    | —               | 40                                                       | μA   |

| Input low current    | ۱ <sub>IL</sub>                      | V                                            | / <sub>IN</sub> <sup>1</sup> = VSS | -600            | —                                                        | μΑ   |

#### Table 24. MII DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

#### Table 25. RGMII/RTBI DC Electrical Characteristics

| Parameters           | Symbol              | Conditions | Min  | Max  | Unit |

|----------------------|---------------------|------------|------|------|------|

| Supply voltage 2.5 V | $LV_{DDA}/LV_{DDB}$ | _          | 2.37 | 2.63 | V    |

### 8.2.1.4 RMII Receive AC Timing Specifications

This table provides the RMII receive AC timing specifications.

#### Table 29. RMII Receive AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock period                                                   | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _   | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                          | t <sub>RMRDVKH</sub>                | 4.0 | _   | —   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                           | t <sub>RMRDXKH</sub>                | 2.0 | -   | —   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>                   | 1.0 | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

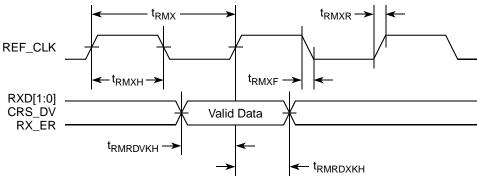

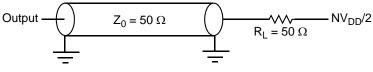

This table provides the AC test load.

Figure 12. AC Test Load

This table shows the RMII receive AC timing diagram.

Figure 13. RMII Receive AC Timing Diagram

#### Table 36. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with L/TV\_{DD} of 3.3 V  $\pm$  5%.

| Parameter/Condition                   | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|---------------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK peak-to-peak jitter     | t <sub>T1588CLKINJ</sub>                                | —                           |     | 250 | ps   |      |

| Rise time eTSEC_1588_CLK<br>(20%-80%) | t <sub>T1588CLKINR</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| Fall time eTSEC_1588_CLK<br>(80%–20%) | t <sub>T1588CLKINF</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| TSEC_1588_CLK_OUT clock period        | t <sub>T1588</sub> CLKOUT                               | 2 × t <sub>T1588CLK</sub>   | _   | _   | ns   |      |

| TSEC_1588_CLK_OUT duty cycle          | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    |      |

| TSEC_1588_PULSE_OUT                   | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   |      |

| TSEC_1588_TRIG_IN pulse width         | t <sub>T1588</sub> trigh                                | $2 \times t_{T1588CLK_MAX}$ |     | —   | ns   | 2    |

Notes:

1. T<sub>RX\_CLK</sub> is the max clock period of eTSEC receiving clock selected by TMR\_CTRL[CKSEL]. See the *MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual,* for a description of TMR\_CTRL registers.

2. It need to be at least two times of clock period of clock selected by TMR\_CTRL[CKSEL]. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description of TMR\_CTRL registers.

The maximum value of t<sub>T1588CLK</sub> is not only defined by the value of T<sub>RX\_CLK</sub>, but also defined by the recovered clock. For example, for 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 280, and 56 ns, respectively.

### 8.5 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for MII, RMII, RGMII, SGMII, and RTBI are specified in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics."

### 8.5.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. Table 37 provide the DC electrical characteristics for MDIO and MDC.

| Parameter              | Symbol          | Conditions                |                         | Min             | Max                    | Unit |

|------------------------|-----------------|---------------------------|-------------------------|-----------------|------------------------|------|

| Supply voltage (3.3 V) | $NV_{DD}$       | _                         | -                       | 2.97            | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub> | I <sub>OH</sub> = -1.0 mA | NV <sub>DD</sub> = Min  | 2.10            | NV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub> | I <sub>OL</sub> = 1.0 mA  | NV <sub>DD</sub> = Min  | V <sub>SS</sub> | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub> | -                         | -                       | 2.0             | _                      | V    |

| Input low voltage      | V <sub>IL</sub> | -                         | -                       | —               | 0.80                   | V    |

| Input high current     | I <sub>IH</sub> | NV <sub>DD</sub> = Max    | $V_{IN}^{1} = 2.1 V$    | —               | 40                     | μA   |

| Input low current      | ۱ <sub>IL</sub> | NV <sub>DD</sub> = Max    | V <sub>IN</sub> = 0.5 V | -600            | —                      | μΑ   |

Table 37. MII Management DC Electrical Characteristics When Powered at 3.3 V

Figure 32. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following section for detailed information:

• Section 8.3.2, "AC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK"

### 9.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

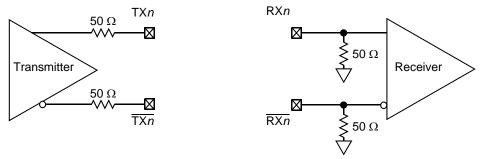

### 9.3 SerDes Transmitter and Receiver Reference Circuits

This figure shows the reference circuits for the SerDes data lane's transmitter and receiver.

Figure 33. SerDes Transmitter and Receiver Reference Circuits

The SerDes data lane's DC and AC specifications are defined in the interface protocol section listed below (SGMII) based on the application usage:

• Section 8.3, "SGMII Interface Electrical Characteristics"

Please note that a external AC-coupling capacitor is required for the above serial transmission protocol with the capacitor value defined in the specifications of the protocol section.

## 12 JTAG

This section describes the DC and AC electrical specifications for the IEEE Std 1149.1<sup>TM</sup> (JTAG) interface.

### 12.1 JTAG DC Electrical Characteristics

This table provides the DC electrical characteristics for the IEEE Std 1149.1 (JTAG) interface.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | _                         | —    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

Table 46. JTAG Interface DC Electrical Characteristics

### 12.2 JTAG AC Timing Specifications

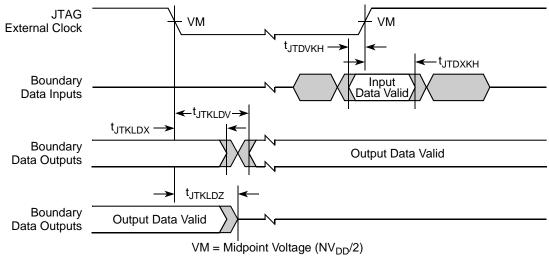

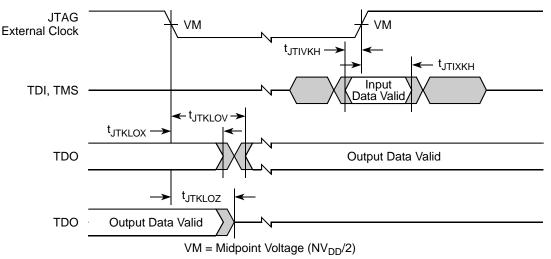

This section describes the AC electrical specifications for the IEEE Std 1149.1 (JTAG) interface. This table provides the JTAG AC timing specifications as defined in Figure 41 through Figure 45.

Table 47. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Note |

|------------------------------------------------------|--------------------------------------------|----------|----------|------|------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  |      |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | —        | ns   |      |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | —        | ns   |      |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   |      |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | —        | ns   | 3    |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | —        | ns   | 4    |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  |                                            | 10<br>10 | _        | ns   | 4    |

| Valid times:<br>Boundary-scan data<br>TDO            | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 2<br>2   | 11<br>11 | ns   | 5    |

| Output hold times:<br>Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns   | 5    |

This figure provides the boundary-scan timing diagram.

Figure 44. Boundary-Scan Timing Diagram

This figure provides the test access port timing diagram.

#### Figure 45. Test Access Port Timing Diagram

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 2.5-V supply.

| Parameters           | Symbol           | Con                       | ditions                | Min                   | Мах                    | Unit |

|----------------------|------------------|---------------------------|------------------------|-----------------------|------------------------|------|

| Supply voltage 2.5 V | NV <sub>DD</sub> |                           | —                      | 2.37                  | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA | NV <sub>DD</sub> = min | 2.00                  | NV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA  | NV <sub>DD</sub> = min | V <sub>SS</sub> – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                         | NV <sub>DD</sub> = min | 1.7                   | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                         | NV <sub>DD</sub> = min | -0.3                  | 0.70                   | V    |

| Input high current   | IIH              | V <sub>IN</sub>           | = NV <sub>DD</sub>     | —                     | 10                     | μΑ   |

| Input low current    | ۱ <sub>IL</sub>  | V <sub>IN</sub>           | I = V <sub>SS</sub>    | -15                   | —                      | μA   |

| Table 56. GPIO (When Operating at 2.5 V) DC Electrical Characteristics |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Note:

1. This specification only applies to GPIO pins that are operating from a 2.5-V supply. See Table 62 for the power supply listed for the individual GPIO signal

### 16.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLKIN. Timings are measured at the pin.

2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

This figure provides the AC test load for the GPIO.

Figure 52. GPIO AC Test Load

## 17 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins.

### **17.1 IPIC DC Electrical Characteristics**

This table provides the DC electrical characteristics for the external interrupt pins.

#### Table 58. IPIC DC Electrical Characteristics

| Characteristic     | Symbol          | Condition                | Min  | Мах                    | Unit |

|--------------------|-----------------|--------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                        | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | _                        | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> |                          | _    | ±5                     | μA   |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _    | 0.5                    | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _    | 0.4                    | V    |

### 17.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

Table 59. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

## 18 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8313E.

### **18.1 SPI DC Electrical Characteristics**

This table provides the DC electrical characteristics for the MPC8313E SPI.

Table 60. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                 | Min | Мах | Unit |

|---------------------|-----------------|---------------------------|-----|-----|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA | 2.4 | _   | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA  | _   | 0.5 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _   | 0.4 | V    |

| Characteristic     | Symbol          | Condition                      | Min  | Max                    | Unit |

|--------------------|-----------------|--------------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                              | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μΑ   |

### **18.2 SPI AC Timing Specifications**

This table and provide the SPI input and output AC timing specifications.

| Table 61 | SPI AC | Timina       | Specifications <sup>1</sup> |

|----------|--------|--------------|-----------------------------|

|          |        | ' i iiiiiiig | opecifications              |

| Characteristic                                           | Symbol <sup>2</sup> | Min | Мах | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs—master mode (internal clock) delay           | t <sub>NIKHOV</sub> | 0.5 | 6   | ns   |

| SPI outputs—slave mode (external clock) delay            | t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 6   | —   | ns   |

| SPI inputs—master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | —   | ns   |

| SPI inputs—slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Note:

1. Output specifications are measured from the 50% level of the rising edge of SYS\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

</sub>

This figure provides the AC test load for the SPI.

Figure 53. SPI AC Test Load

Figure 54 and Figure 55 represent the AC timing from Table 61. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

| Signal                                     | Package Pin Number | Pin Type | Power<br>Supply   | Note  |

|--------------------------------------------|--------------------|----------|-------------------|-------|

| TSEC1_TXD1/TSEC_1588_PP2                   | AD6                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TXD0/USBDR_STP/TSEC_1588_PP3         | AD5                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TX_EN/TSEC_1588_ALARM1               | AB7                | 0        | LV <sub>DDB</sub> | —     |

| TSEC1_TX_ER/TSEC_1588_ALARM2               | AB8                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_GTX_CLK125                           | AE1                | I        | LV <sub>DDB</sub> | _     |

| TSEC1_MDC/LB_POR_CFG_BOOT_ECC_DIS          | AF6                | 0        | NV <sub>DD</sub>  | 9, 11 |

| TSEC1_MDIO                                 | AB9                | I/O      | NV <sub>DD</sub>  | _     |

|                                            | ETSEC2             |          |                   |       |

| TSEC2_COL/GTM1_TIN4/GTM2_TIN3/GPIO15       | AB4                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_CRS/GTM1_TGATE4/GTM2_TGATE3/GPIO16   | AB3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_GTX_CLK/GTM1_TOUT4/GTM2_TOUT3/GPI017 | AC1                | I/O      | LV <sub>DDA</sub> | 12    |

| TSEC2_RX_CLK/GTM1_TIN2/GTM2_TIN1/GPIO18    | AC2                | I/O      | LV <sub>DDA</sub> | _     |

| TSCE2_RX_DV/GTM1_TGATE2/GTM2_TGATE1/GPIO19 | AA3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD3/GPIO20                          | Y5                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD2/GPIO21                          | AA4                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD1/GPIO22                          | AB2                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD0/GPIO23                          | AA5                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RX_ER/GTM1_TOUT2/GTM2_TOUT1/GPIO24   | AA2                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_CLK/GPIO25                        | AB1                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD3/CFG_RESET_SOURCE0               | W3                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD2/CFG_RESET_SOURCE1               | Y1                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD1/CFG_RESET_SOURCE2               | W5                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TXD0/CFG_RESET_SOURCE3               | Y3                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_EN/GPIO26                         | AA1                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_ER/GPI027                         | W1                 | I/O      | LV <sub>DDA</sub> | _     |

|                                            | SGMII PHY          |          |                   |       |

| ТХА                                        | U3                 | 0        |                   | —     |

| TXA                                        | V3                 | 0        |                   | —     |

| RXA                                        | U1                 | I        |                   | —     |

| RXA                                        | V1                 | I        |                   | —     |

| ТХВ                                        | P4                 | 0        |                   | —     |

| ТХВ                                        | N4                 | 0        |                   | _     |

#### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                                           | Package Pin Number                                                                                                     | Pin Type                                                      | Power<br>Supply  | Note |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------|

|                                                  | SPI                                                                                                                    |                                                               | 11               |      |

| SPIMOSI/GTM1_TIN3/GTM2_TIN4/GPIO28/LSRCID4       | H1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | —    |

| SPIMISO/GTM1_TGATE3/GTM2_TGATE4/GPIO29/<br>LDVAL | H3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | _    |

| SPICLK/GTM1_TOUT3/GPIO30                         | G1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> |      |

| SPISEL/GPIO31                                    | G3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | —    |

| Power                                            | and Ground Supplies                                                                                                    |                                                               | •                |      |

| AV <sub>DD1</sub>                                | F14                                                                                                                    | Power for e300 core<br>APLL<br>(1.0 V)                        | —                | _    |

| AV <sub>DD2</sub>                                | P21                                                                                                                    | Power for system<br>APLL (1.0 V)                              | —                | _    |

| GV <sub>DD</sub>                                 | A2,A3,A4,A24,A25,B3,<br>B4,B5,B12,B13,B20,B21,<br>B24,B25,B26,D1,D2,D8,<br>D9,D16,D17                                  | Power for DDR1<br>and DDR2 DRAM<br>I/O voltage<br>(1.8/2.5 V) | —                | _    |

| LV <sub>DD</sub>                                 | D24,D25,G23,H23,R23,<br>T23,W25,Y25,AA22,AC23                                                                          | Power for local bus<br>(3.3 V)                                | —                |      |

| LV <sub>DDA</sub>                                | W2,Y2                                                                                                                  | Power for eTSEC2<br>(2.5 V, 3.3 V)                            | —                | _    |

| LV <sub>DDB</sub>                                | AC8,AC9,AE4,AE5                                                                                                        | Power for eTSEC1/<br>USB DR<br>(2.5 V, 3.3 V)                 | —                | _    |

| MV <sub>REF</sub>                                | C14,D14                                                                                                                | Reference voltage signal for DDR                              | —                | —    |

| NV <sub>DD</sub>                                 | G4,H4,L2,M2,AC16,AC17,<br>AD25,AD26,AE12,AE13,<br>AE20,AE21,AE24,AE25,<br>AE26,AF24,AF25                               | Standard I/O<br>voltage (3.3 V)                               | —                | _    |

| V <sub>DD</sub>                                  | K11,K12,K13,K14,K15,<br>K16,L10,L17,M10,M17,<br>N10,N17,U12,U13,                                                       | Power for core (1.0<br>V)                                     | —                | _    |

| V <sub>DDC</sub>                                 | F6,F10,F19,K6,K10,K17,<br>K21,P6,P10,P17,R10,R17,<br>T10,T17,U10,U11,U14,<br>U15,U16,U17,W6,W21,<br>AA6,AA10,AA14,AA19 | Internal core logic<br>constant power (1.0<br>V)              | —                | _    |

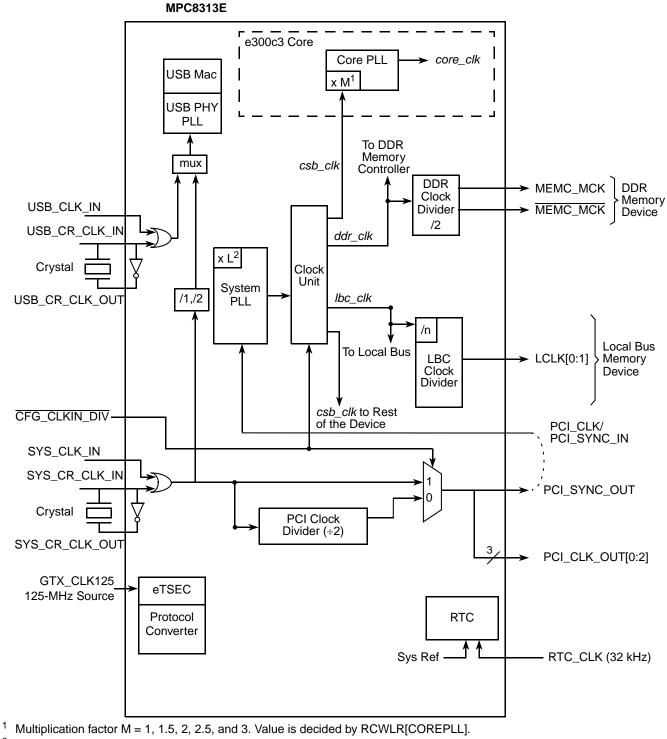

## 20 Clocking

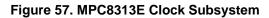

This figure shows the internal distribution of clocks within the MPC8313E.

<sup>2</sup> Multiplication factor L = 2, 3, 4, 5, and 6. Value is decided by RCWLR[SPMF].

### 20.3 Example Clock Frequency Combinations

This table shows several possible frequency combinations that can be selected based on the indicated input reference frequencies, with RCWLR[LBCM] = 0 and RCWLR[DDRCM] =1, such that the LBC operates with a frequency equal to the frequency of  $csb\_clk$  and the DDR controller operates at twice the frequency of  $csb\_clk$ .

|                            |                   |                   |                  |                                        |                  |      | LBC(lbc_clk) e300 Core(core |      |                         |       | e_clk) |            |       |            |

|----------------------------|-------------------|-------------------|------------------|----------------------------------------|------------------|------|-----------------------------|------|-------------------------|-------|--------|------------|-------|------------|

| SYS_<br>CLK_IN/<br>PCI_CLK | SPMF <sup>1</sup> | VCOD <sup>2</sup> | VCO <sup>3</sup> | CSB<br>( <i>csb_clk</i> ) <sup>4</sup> | DDR<br>(ddr_clk) | /2   | /4                          | /8   | USB<br>ref <sup>5</sup> | × 1   | × 1.5  | × <b>2</b> | × 2.5 | × <b>3</b> |

| 25.0                       | 6                 | 2                 | 600.0            | 150.0                                  | 300.0            |      | 37.5                        | 18.8 | Note <sup>6</sup>       | 150.0 | 225    | 300        | 375   | _          |

| 25.0                       | 5                 | 2                 | 500.0            | 125.0                                  | 250.0            | 62.5 | 31.25                       | 15.6 | Note 6                  | 125.0 | 188    | 250        | 313   | 375        |

| 33.3                       | 5                 | 2                 | 666.0            | 166.5                                  | 333.0            | _    | 41.63                       | 20.8 | Note 6                  | 166.5 | 250    | 333        | _     | _          |

| 33.3                       | 4                 | 2                 | 532.8            | 133.2                                  | 266.4            | 66.6 | 33.3                        | 16.7 | Note 6                  | 133.2 | 200    | 266        | 333   | 400        |

| 48.0                       | 3                 | 2                 | 576.0            | 144.0                                  | 288.0            | _    | 36                          | 18.0 | 48.0                    | 144.0 | 216    | 288        | 360   | —          |

| 66.7                       | 2                 | 2                 | 533.4            | 133.3                                  | 266.7            | 66.7 | 33.34                       | 16.7 | Note 6                  | 133.3 | 200    | 267        | 333   | 400        |

| Table 68. System Clock Frequencies | Table | 68. | System | Clock | Frequencies |

|------------------------------------|-------|-----|--------|-------|-------------|

|------------------------------------|-------|-----|--------|-------|-------------|

Note:

1. System PLL multiplication factor.

2. System PLL VCO divider.

3. When considering operating frequencies, the valid core VCO operating range of 400–800 MHz must not be violated.

4. Due to erratum eTSEC40, *csb\_clk* frequencies of less than 133 MHz do not support gigabit Ethernet data rates. The core frequency must be 333 MHz for gigabit Ethernet operation. This erratum will be fixed in revision 2 silicon.

5. Frequency of USB PLL input reference.

6. USB reference clock must be supplied from a separate source as it must be 24 or 48 MHz, the USB reference must be supplied from a separate external source using USB\_CLK\_IN.

## 21 Thermal

This section describes the thermal specifications of the MPC8313E.

### 21.1 Thermal Characteristics

This table provides the package thermal characteristics for the 516,  $27 \times 27$  mm TEPBGAII.

| Table 69. Package Th | ermal Characteristics for TEPBGAII |

|----------------------|------------------------------------|

|----------------------|------------------------------------|

| Characteristic                         | Board Type              | Symbol              | TEPBGA II | Unit | Note    |

|----------------------------------------|-------------------------|---------------------|-----------|------|---------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	ext{	heta}JA}$ | 25        | °C/W | 1, 2    |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$ | 18        | °C/W | 1, 2, 3 |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{	hetaJMA}$      | 20        | °C/W | 1, 3    |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	hetaJMA}$      | 15        | °C/W | 1, 3    |

| Junction-to-board                      | _                       | $R_{	heta JB}$      | 10        | °C/W | 4       |

### 21.3 Heat Sink Attachment

When attaching heat sinks to these devices, an interface material is required. The best method is to use thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces which would lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. Recommended maximum force on the top of the package is 10 lb (4.5 kg) force. If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

# 21.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction to case thermal resistance.

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package  $R_{\theta JC}$  = junction-to-case thermal resistance  $P_D$  = power dissipation

$T_I = T_C + (R_{\theta IC} x P_D)$

## 22 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8313E SYS\_CLK\_IN

### 22.1 System Clocking

The MPC8313E includes three PLLs.

- 1. The platform PLL (AV<sub>DD2</sub>) generates the platform clock from the externally supplied SYS\_CLK\_IN input in PCI host mode or SYS\_CLK\_IN/PCI\_SYNC\_IN in PCI agent mode. The frequency ratio between the platform and SYS\_CLK\_IN is selected using the platform PLL ratio configuration bits as described in Section 20.1, "System PLL Configuration."

- 2. The e300 core PLL (AV<sub>DD1</sub>) generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 20.2, "Core PLL Configuration."

- 3. There is a PLL for the SerDes block.

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>In Table 63, added LBC_PM_REF_10 &amp; LSRCID3 as muxed with USBDR_PCTL1</li> <li>In Table 63, added LSRCID2 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL2 VBUS</li> <li>In Table 63, moved 71, U2,&amp; V2 from V<sub>DD</sub> to XCOREVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; V4 from V<sub>SS</sub> to XCOREVDS.</li> <li>In Table 63, added impedance control requirements for SD_IMP_CAL_TX (100 ohms to GND) and SD_IMP_CAL_RX (200 ohms to GND).</li> <li>In Table 63, updated muxing in pinout to show new options for selecting IEEE 1588 functionality. Added footnote 8</li> <li>In Table 63, updated muxing in pinout to show new LBC ECC boot enable control muxed with eTSEC1_MDC</li> <li>Added pin type information for power supplies.</li> <li>Removed N1 and N3 from Vss section of Table 63. Added Therm0 and Therm1 (N1 and N3, respectively). Added note 7 to state: "Internal thermally sensitive resistor, resistor value varies linearly with temperature."</li> <li>In Table 65 corrected maximum frequency of Local Bus Frequency from "33–66" to 66 MHz</li> <li>In Table 65 corrected maximum frequency of PCI from "24–66" to 66 MHz</li> <li>Added "which is determined by RCWLR[COREPLL]" to the note in Section 20.2, "Core PLL Configuration" about the VCO divider.</li> <li>Added "Walues.</li> <li>In Table 69, notes were confusing. Added note 3 for VCO column, note 4 for CSB (<i>csb_c.lk</i>) column, note 5 for USB ref column, and note 6 to replace "Note 1". Clarified note 4 to explain errature are salid or certain <i>csb_c.lk</i> values.</li> <li>In Table 69, updated note 6 to specify USB reference clock frequencies limited to 24 and 48 for rev. 2 silicon.</li> <li>Replaced Table 71 "Thermal Resistance for TEPBGAII with Heat Sink in Open Flow".</li> <li>Removed last row of Table 19.</li> &lt;</ul> |

| 0              | 6/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |