# E·XFL

#### NXP USA Inc. - KMPC8313ZQAFFB Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 333MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | · .                                                                    |

| Package / Case                  | 516-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8313zqaffb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. Recommended Operating Conditions (continued)

| Characteristic Symbol Recommended Value <sup>1</sup> Unit | Current<br>Requirement |

|-----------------------------------------------------------|------------------------|

|-----------------------------------------------------------|------------------------|

Note:

- 1. GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. Some GPIO pins may operate from a 2.5-V supply when configured for other functions.

- 3. Min temperature is specified with  $T_A$ ; Max temperature is specified with  $T_J$

- 4. All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.

- 5. All I/O pins should be interfaced with peripherals operating at same voltage level.

- This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

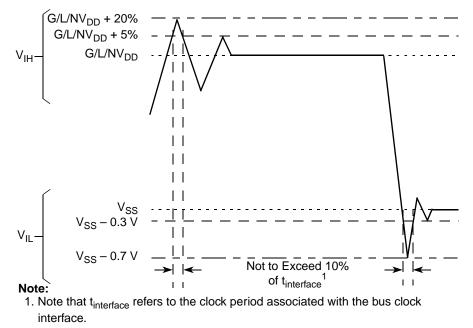

This figure shows the undershoot and overshoot voltages at the interfaces of the MPC8313E.

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/NV<sub>DD</sub>/LV<sub>DD</sub>

### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

| Driver Type                           | Output Impedance ( $\Omega$ ) | Supply Voltage           |

|---------------------------------------|-------------------------------|--------------------------|

| Local bus interface utilities signals | 42                            | NV <sub>DD</sub> = 3.3 V |

| PCI signals                           | 25                            |                          |

| DDR signal                            | 18                            | GV <sub>DD</sub> = 2.5 V |

### 5.2 **RESET AC Electrical Characteristics**

This table provides the reset initialization AC timing specifications.

| Parameter/Condition                                                                                                                                               | Min | Max | Unit                     | Note |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                        | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Required assertion time of PORESET with stable clock and power applied to SYS_CLK_IN when the device is in PCI host mode                                          | 32  | —   | t <sub>SYS_CLK_IN</sub>  | 2    |

| Required assertion time of PORESET with stable clock and power applied to PCI_SYNC_IN when the device is in PCI agent mode                                        | 32  | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| HRESET assertion (output)                                                                                                                                         | 512 |     | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3] and CFG_CLK_IN_DIV) with respect to negation of PORESET when the device is in PCI host mode | 4   | —   | <sup>t</sup> sys_clk_in  | 2    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input hold time for POR configuration signals with respect to negation of HRESET                                                                                  | 0   | —   | ns                       | —    |

| Time for the device to turn off POR configuration signal drivers with respect to the assertion of HRESET                                                          |     | 4   | ns                       | 3    |

| Time for the device to turn on POR configuration signal drivers with respect to the negation of $\overline{\text{HRESET}}$                                        | 1   |     | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

#### Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the

primary clock is applied to the SYS\_CLK\_IN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. 2. t<sub>SYS\_CLK\_IN</sub> is the clock period of the input clock applied to SYS\_CLK\_IN. It is only valid when the device is in PCI host mode.

POR configuration signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

This table provides the PLL lock times.

#### Table 11. PLL Lock Times

| Parameter/Condition | Min | Мах | Unit | Note |

|---------------------|-----|-----|------|------|

| PLL lock times      | _   | 100 | μs   | —    |

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface. Note that DDR SDRAM is  $GV_{DD}(typ) = 2.5 \text{ V}$  and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 \text{ V}$ .

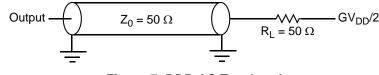

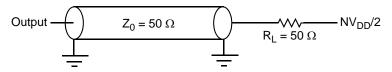

This figure provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

### 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

| Parameter                                                           | Symbol          | Min                    | Max                    | Unit |

|---------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                            | V <sub>IH</sub> | 2.0                    | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage NV <sub>DD</sub>                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$                  | V <sub>OH</sub> | NV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$                    | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ±5                     | μA   |

### 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          | _    | 2    |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all the media independent interface (MII), reduced gigabit media independent interface (RGMII), serial gigabit media independent interface (SGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the MII interface can be operated at 3.3 V. The RMII and SGMII interfaces can be operated at either 3.3 or 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for *Gigabit Ethernet Physical Layer Device Specification Version 1.2a* (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.5, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 **TSEC DC Electrical Characteristics**

All RGMII, RMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 24 and Table 25. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

### NOTE

eTSEC should be interfaced with peripheral operating at same voltage level.

| Parameter            | Symbol                               | Conditions                                   |                                    | Min             | Мах                                                      | Unit |

|----------------------|--------------------------------------|----------------------------------------------|------------------------------------|-----------------|----------------------------------------------------------|------|

| Supply voltage 3.3 V | LV <sub>DDA</sub> /LV <sub>DDB</sub> |                                              | _                                  | 2.97            | 3.63                                                     | V    |

| Output high voltage  | V <sub>OH</sub>                      | I <sub>OH</sub> = -4.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$     | 2.40            | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>                      | I <sub>OL</sub> = 4.0 mA                     | $LV_{DDA}$ or $LV_{DDB}$ = Min     | V <sub>SS</sub> | 0.50                                                     | V    |

| Input high voltage   | V <sub>IH</sub>                      | _                                            | _                                  | 2.0             | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>                      | _                                            | —                                  | -0.3            | 0.90                                                     | V    |

| Input high current   | Ι <sub>ΙΗ</sub>                      | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                    | —               | 40                                                       | μA   |

| Input low current    | ۱ <sub>IL</sub>                      | V                                            | / <sub>IN</sub> <sup>1</sup> = VSS | -600            | —                                                        | μΑ   |

### Table 24. MII DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

#### Table 25. RGMII/RTBI DC Electrical Characteristics

| Parameters           | Symbol              | Conditions | Min  | Max  | Unit |

|----------------------|---------------------|------------|------|------|------|

| Supply voltage 2.5 V | $LV_{DDA}/LV_{DDB}$ | _          | 2.37 | 2.63 | V    |

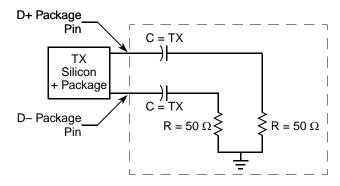

Figure 18. SGMII AC Test/Measurement Load

### 8.4 eTSEC IEEE 1588 AC Specifications

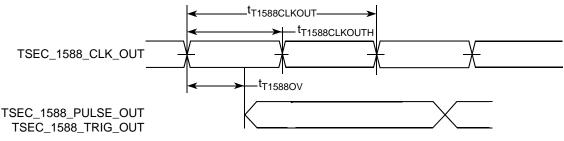

This figure provides the data and command output timing diagram.

**Note:** The output delay is count starting rising edge if t<sub>T1588CLKOUT</sub> is non-inverting. Otherwise, it is count starting falling edge.

Figure 19. eTSEC IEEE 1588 Output AC Timing

This figure provides the data and command input timing diagram.

Figure 20. eTSEC IEEE 1588 Input AC Timing

This table lists the IEEE 1588 AC timing specifications.

### Table 36. eTSEC IEEE 1588 AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition        | Symbol                                        | Min | Тур | Мах                    | Unit | Note |

|----------------------------|-----------------------------------------------|-----|-----|------------------------|------|------|

| TSEC_1588_CLK clock period | t <sub>T1588CLK</sub>                         | 3.8 | _   | $T_{RX\_CLK} \times 9$ | ns   | 1, 3 |

| TSEC_1588_CLK duty cycle   | t <sub>T1588CLKH</sub> /t <sub>T1588CLK</sub> | 40  | 50  | 60                     | %    |      |

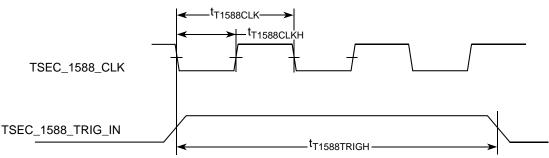

of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 9.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 24 shows the SerDes reference clock input requirement for the DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to  $XCOREV_{SS}$ . Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage ( $XCOREV_{SS}$ ). Figure 25 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 26 shows the SerDes reference clock input requirement for the single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC coupled externally. For the best noise performance, the reference of the clock could be DC or AC coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 24. Differential Reference Clock Input DC Requirements (External DC-Coupled)

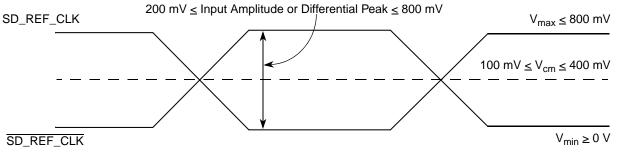

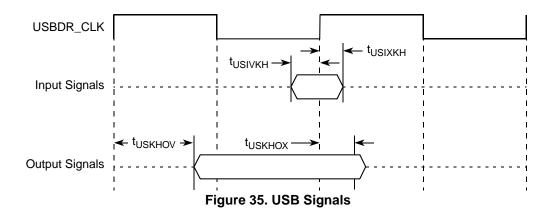

### 10.2 On-Chip USB PHY

This section describes the DC and AC electrical specifications for the on-chip USB PHY of the MPC8313E. See Chapter 7 in the USB Specifications Rev. 2, for more information.

This table provides the USB clock input (USB\_CLK\_IN) DC timing specifications.

| Parameter          | Symbol          | Min  | Мах                    | Unit |

|--------------------|-----------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | 2.7  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

This table provides the USB clock input (USB\_CLK\_IN) AC timing specifications.

| Table 43. USB | CLK_IN | AC Timing | Specifications |

|---------------|--------|-----------|----------------|

|---------------|--------|-----------|----------------|

| Parameter/Condition                       | Conditions                                                                            | Symbol                  | Min    | Тур | Max   | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------|-------------------------|--------|-----|-------|------|

| Frequency range                           | _                                                                                     | f <sub>USB_CLK_IN</sub> | —      | 24  | 48    | MHz  |

| Clock frequency tolerance                 | _                                                                                     | <sup>t</sup> CLK_TOL    | -0.005 | 0   | 0.005 | %    |

| Reference clock duty cycle                | Measured at 1.6 V                                                                     | t <sub>CLK_DUTY</sub>   | 40     | 50  | 60    | %    |

| Total input jitter/time interval<br>error | Peak-to-peak value measured with a second order high-pass filter of 500 kHz bandwidth | t <sub>CLK_PJ</sub>     | —      |     | 200   | ps   |

#### Table 45. Local Bus General Timing Parameters (continued)

|  | Parameter | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|--|-----------|---------------------|-----|-----|------|------|

|--|-----------|---------------------|-----|-----|------|------|

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1).

</sub>

- 2. All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from NV<sub>DD</sub>/2 of the rising/falling edge of LCLK0 to  $0.4 \times NV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> and t<sub>LALETOT1</sub> should be used when RCWH[LALE] is not set and the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 6. t<sub>LBOTOT2</sub> and t<sub>LALETOT2</sub> should be used when RCWH[LALE] is set and the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> and t<sub>LALETOT3</sub> should be used when RCWH[LALE] is set and the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

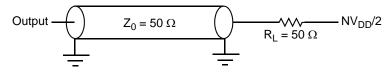

This figure provides the AC test load for the local bus.

Figure 36. Local Bus AC Test Load

### **15.2 Timers AC Timing Specifications**

This table provides the Timers input and output AC timing specifications.

Table 54. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

2. Timers inputs and outputs are asynchronous to any visible clock. Timers outputs should be synchronized before use by any external synchronous logic. Timers inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation

This figure provides the AC test load for the Timers.

Figure 51. Timers AC Test Load

### 16 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

### **16.1 GPIO DC Electrical Characteristics**

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 3.3-V supply.

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA       | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μΑ   |

Table 55. GPIO (When Operating at 3.3 V) DC Electrical Characteristics

Note:

1. This specification only applies to GPIO pins that are operating from a 3.3-V supply. See Table 62 for the power supply listed for the individual GPIO signal.

### **19.3 Pinout Listings**

This table provides the pin-out listing for the MPC8313E, TEPBGAII package.

| Signal                          | Package Pin Number | Pin Type | Power<br>Supply  | Note |  |  |  |  |  |

|---------------------------------|--------------------|----------|------------------|------|--|--|--|--|--|

| DDR Memory Controller Interface |                    |          |                  |      |  |  |  |  |  |

| MEMC_MDQ0                       | A8                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ1                       | A9                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ2                       | C10                | I/O      | GV <sub>DD</sub> |      |  |  |  |  |  |

| MEMC_MDQ3                       | C9                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ4                       | E9                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ5                       | E11                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ6                       | E10                | I/O      | GV <sub>DD</sub> |      |  |  |  |  |  |

| MEMC_MDQ7                       | C8                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ8                       | E8                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ9                       | A6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ10                      | B6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ11                      | C6                 | I/O      | GV <sub>DD</sub> |      |  |  |  |  |  |

| MEMC_MDQ12                      | C7                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ13                      | D7                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ14                      | D6                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ15                      | A5                 | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ16                      | A19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ17                      | D18                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ18                      | A17                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ19                      | E17                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ20                      | E16                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ21                      | C18                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ22                      | D19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ23                      | C19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ24                      | E19                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ25                      | A22                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ26                      | C21                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ27                      | C20                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

| MEMC_MDQ28                      | A21                | I/O      | GV <sub>DD</sub> | _    |  |  |  |  |  |

### Table 62. MPC8313E TEPBGAII Pinout Listing

| Signal     | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|------------|--------------------|----------|------------------|------|

| MEMC_MDQ29 | A20                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDQ30 | C22                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQ31 | B22                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDM0  | B7                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM1  | E6                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM2  | E18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM3  | E20                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDQS0 | A7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS1 | E7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS2 | B19                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS3 | A23                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MBA0  | D15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA1  | A18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA2  | A15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA0   | E12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA1   | D11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA2   | B11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA3   | A11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA4   | A12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA5   | E13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA6   | C12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA7   | E14                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA8   | B15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA9   | C17                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA10  | C13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA11  | A16                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA12  | C15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA13  | C16                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA14  | E15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MWE   | B18                | 0        | GV <sub>DD</sub> |      |

| MEMC_MRAS  | C11                | 0        | GV <sub>DD</sub> |      |

| MEMC_MCAS  | B10                | 0        | GV <sub>DD</sub> |      |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                                     | Package Pin Number | Pin Type | Power<br>Supply   | Note  |

|--------------------------------------------|--------------------|----------|-------------------|-------|

| TSEC1_TXD1/TSEC_1588_PP2                   | AD6                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TXD0/USBDR_STP/TSEC_1588_PP3         | AD5                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_TX_EN/TSEC_1588_ALARM1               | AB7                | 0        | LV <sub>DDB</sub> | —     |

| TSEC1_TX_ER/TSEC_1588_ALARM2               | AB8                | 0        | LV <sub>DDB</sub> | _     |

| TSEC1_GTX_CLK125                           | AE1                | I        | LV <sub>DDB</sub> | _     |

| TSEC1_MDC/LB_POR_CFG_BOOT_ECC_DIS          | AF6                | 0        | NV <sub>DD</sub>  | 9, 11 |

| TSEC1_MDIO                                 | AB9                | I/O      | NV <sub>DD</sub>  | _     |

|                                            | ETSEC2             |          |                   |       |

| TSEC2_COL/GTM1_TIN4/GTM2_TIN3/GPIO15       | AB4                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_CRS/GTM1_TGATE4/GTM2_TGATE3/GPIO16   | AB3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_GTX_CLK/GTM1_TOUT4/GTM2_TOUT3/GPI017 | AC1                | I/O      | LV <sub>DDA</sub> | 12    |

| TSEC2_RX_CLK/GTM1_TIN2/GTM2_TIN1/GPIO18    | AC2                | I/O      | LV <sub>DDA</sub> | _     |

| TSCE2_RX_DV/GTM1_TGATE2/GTM2_TGATE1/GPIO19 | AA3                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD3/GPIO20                          | Y5                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD2/GPIO21                          | AA4                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_RXD1/GPIO22                          | AB2                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_RXD0/GPIO23                          | AA5                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_RX_ER/GTM1_TOUT2/GTM2_TOUT1/GPIO24   | AA2                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_TX_CLK/GPIO25                        | AB1                | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_TXD3/CFG_RESET_SOURCE0               | W3                 | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_TXD2/CFG_RESET_SOURCE1               | Y1                 | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_TXD1/CFG_RESET_SOURCE2               | W5                 | I/O      | LV <sub>DDA</sub> | —     |

| TSEC2_TXD0/CFG_RESET_SOURCE3               | Y3                 | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_EN/GPIO26                         | AA1                | I/O      | LV <sub>DDA</sub> | _     |

| TSEC2_TX_ER/GPI027                         | W1                 | I/O      | LV <sub>DDA</sub> | _     |

|                                            | SGMII PHY          |          |                   |       |

| ТХА                                        | U3                 | 0        |                   | _     |

| TXA                                        | V3                 | 0        |                   | —     |

| RXA                                        | U1                 | I        |                   | —     |

| RXA                                        | V1                 | I        |                   | —     |

| ТХВ                                        | P4                 | 0        |                   | —     |

| ТХВ                                        | N4                 | 0        |                   | _     |

### 20.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in this table should be considered as reserved.

### NOTE

Core VCO frequency = core frequency  $\times$  VCO divider. The VCO divider, which is determined by RCWLR[COREPLL], must be set properly so that the core VCO frequency is in the range of 400–800 MHz.

| RCWL[COREPLL] |      | CWL[COREPLL] core_clk : csb_clk Ratio <sup>1</sup> |                                                                | VCO Divider (VCOD) <sup>3</sup>                                |

|---------------|------|----------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| 0–1           | 2–5  | 6                                                  | core_cik : csb_cik Ratio                                       |                                                                |

| nn            | 0000 | 0                                                  | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) |

| 11            | nnnn | n                                                  | n/a                                                            | n/a                                                            |

| 00            | 0001 | 0                                                  | 1:1                                                            | 2                                                              |

| 01            | 0001 | 0                                                  | 1:1                                                            | 4                                                              |

| 10            | 0001 | 0                                                  | 1:1                                                            | 8                                                              |

| 00            | 0001 | 1                                                  | 1.5:1                                                          | 2                                                              |

| 01            | 0001 | 1                                                  | 1.5:1                                                          | 4                                                              |

| 10            | 0001 | 1                                                  | 1.5:1                                                          | 8                                                              |

| 00            | 0010 | 0                                                  | 2:1                                                            | 2                                                              |

| 01            | 0010 | 0                                                  | 2:1                                                            | 4                                                              |

| 10            | 0010 | 0                                                  | 2:1                                                            | 8                                                              |

| 00            | 0010 | 1                                                  | 2.5:1                                                          | 2                                                              |

| 01            | 0010 | 1                                                  | 2.5:1                                                          | 4                                                              |

| 10            | 0010 | 1                                                  | 2.5:1                                                          | 8                                                              |

| 00            | 0011 | 0                                                  | 3:1                                                            | 2                                                              |

| 01            | 0011 | 0                                                  | 3:1                                                            | 4                                                              |

| 10            | 0011 | 0                                                  | 3:1                                                            | 8                                                              |

#### Table 67. e300 Core PLL Configuration

Note:

1. For core\_clk:csb\_clk ratios of 2.5:1 and 3:1, the core\_clk must not exceed its maximum operating frequency of 333 MHz.

2. Core VCO frequency = core frequency × VCO divider. Note that VCO divider has to be set properly so that the core VCO frequency is in the range of 400–800 MHz.

Table 69. Package Thermal Characteristics for TEPBGAII (continued)

| Characteristic          | Board Type         | Symbol              | TEPBGA II | Unit | Note |

|-------------------------|--------------------|---------------------|-----------|------|------|

| Junction-to-case        | _                  | $R_{	ext{	heta}JC}$ | 8         | °C/W | 5    |

| Junction-to-package top | Natural convection | $\Psi_{JT}$         | 7         | °C/W | 6    |

Note:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 21.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$ , where  $P_{I/O}$  is the power dissipation of the I/O drivers.

### 21.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. As a general statement, the value obtained on a single layer board is appropriate for a tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

# 21.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction-to-ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter

(edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_J = T_B + (R_{\theta JB} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_B$  = board temperature at the package perimeter (°C)  $R_{\theta JB}$  = junction-to-board thermal resistance (°C/W) per JESD51–8  $P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. The application board should be similar to the thermal test condition: the component is soldered to a board with internal planes.

### 21.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

where:

$T_I$  = junction temperature (°C)

$T_I = T_T + (\Psi_{IT} \times P_D)$

$T_T$  = thermocouple temperature on top of package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

### 21.2.4 Heat Sinks and Junction-to-Case Thermal Resistance

In some application environments, a heat sink is required to provide the necessary thermal management of the device. When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)  $R_{\theta CA}$  = case-to- ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

| Heat Sink Assuming Thermal Grease                | Airflow            | Thermal Resistance<br>(°C/W) |

|--------------------------------------------------|--------------------|------------------------------|

| Wakefield 53 $\times$ 53 $\times$ 2.5 mm pin fin | Natural convection | 13.0                         |

|                                                  | 0.5 m/s            | 10.6                         |

|                                                  | 1 m/s              | 9.7                          |

|                                                  | 2 m/s              | 9.2                          |

|                                                  | 4 m/s              | 8.9                          |

| Aavid 35 $\times~$ 31 $\times$ 23 mm pin fin     | Natural convection | 14.4                         |

|                                                  | 0.5 m/s            | 11.3                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.9                          |

|                                                  | 4 m/s              | 9.4                          |

| Aavid $30 \times 30 \times 9.4$ mm pin fin       | Natural convection | 16.5                         |

|                                                  | 0.5 m/s            | 13.5                         |

|                                                  | 1 m/s              | 12.1                         |

|                                                  | 2 m/s              | 10.9                         |

|                                                  | 4 m/s              | 10.0                         |

| Aavid $43 \times 41 \times 16.5$ mm pin fin      | Natural convection | 14.5                         |

|                                                  | 0.5 m/s            | 11.7                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.7                          |

|                                                  | 4 m/s              | 9.2                          |

Table 70. Thermal Resistance for TEPBGAII with Heat Sink in Open Flow

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in Table 70. More detailed thermal models can be made available on request.

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal NV<sub>DD</sub>, 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(Not Including PCI<br>Output Clocks) | PCI Output Clocks<br>(Including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | Ω    |

Table 71. Impedance Characteristics

Note: Nominal supply voltages. See Table 1,  $T_J$  = 105 °C.

### 22.7 Configuration Pin Muxing

The MPC8313E provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when PORESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

### 22.8 Pull-Up Resistor Requirements

The MPC8313E requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C, and IPIC (integrated programmable interrupt controller).

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 61. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions because most have asynchronous behavior and spurious assertion, which give unpredictable results.

Refer to the PCI 2.2 Specification, for all pull-ups required for PCI.

### 22.9 JTAG Configuration Signals

Boundary scan testing is enabled through the JTAG interface signals. The TRST signal is optional in IEEE 1149.1, but is provided on any Freescale devices that are built on Power Architecture technology. The device requires TRST to be asserted during reset conditions to ensure the JTAG boundary logic does not interfere with normal chip operation. While it is possible to force the TAP controller to the reset state using only the TCK and TMS signals, systems generally assert TRST during power-on reset. Because the JTAG interface is also used for accessing the common on-chip processor (COP) function, simply tying TRST to PORESET is not practical.

# 24 Revision History

This table summarizes a revision history for this document.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4              | 11/2011 | <ul> <li>In Table 2, added following notes: <ul> <li>Note 3: Min temperature is specified with T<sub>A</sub>; Max temperature is specified with T<sub>J</sub></li> <li>Note 4: All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.</li> <li>Note 5: All I/O pins should be interfaced with peripherals operating at same voltage level.</li> <li>Note 6: This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter</li> <li>Decoupled PCI_CLK and SYS_CLK_IN rise and fall times in Table 8. Relaxed maximum rise/fall time of SYS_CLK_IN to 4ns.</li> <li>Added a note in Table 27 stating "The frequency of RX_CLK should not exceed the TX_CLK by more than 300 ppm."</li> <li>In Table 30: <ul> <li>Changed max value of t<sub>skrg1</sub> in "Data to clock input skew (at receiver)" row from 2.8 to 2.6.</li> <li>Added note 7, stating that, "The frequency of RX_CLK should not exceed the GTX_CLK125 by more than 300 ppm."</li> </ul> </li> <li>In Table 30: <ul> <li>Changed max value of t<sub>skrg1</sub> in "Data to clock input skew (at receiver)" row from 2.8 to 2.6.</li> <li>Added note 7, stating that, "The frequency of RX_CLK should not exceed the GTX_CLK125 by more than 300 ppm."</li> </ul> </li> <li>In Table 30: <ul> <li>Changed max value of table 2 should be interfaced with peripheral operating at same voltage level" in Section 8.1.1, "TSEC DC Electrical Characteristics."</li> </ul> </li> <li>TSEC1_MDC and TSEC_MDIO are powered at 3.3V by NVDD. Replaced LVDDA/LVDDB with NVDD and removed instances of 2.5V at several places in Section 8.5, "Ethernet Management Interface Electrical Characteristics."</li> <li>In Table 43, changed min/max values of t<sub>CLK_TOL</sub> from 0.05 to 0.005.</li> <li>In Table 43, changed min/max values of the MPC8313E TEPBGAII," replaced "5.5 Sn/0.5 Cu/4 Ag" with "Sn/3.5 Ag."</li> <li>Added Note 12: "In MII mode, GTX_CLK should be pulled down by 300 Ω to V<sub>SS</sub>" to TSEC1_GTX_C</li></ul></li></ul> |  |

| 3              | 01/2009 | • Table 72, in column aa, changed to AG = 400 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 2.2            | 12/2008 | Made cross-references active for sections, figures, and tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2.1            | 12/2008 | Added Figure 2, after Table 2 and renumbered the following figures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

#### Table 73. Document Revision History

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>Replaced OVDD with NV<sub>DD</sub> everywhere</li> <li>Added XCOREVDD and XPADVDD to Table 1</li> <li>Moved VDD and VDDC to the top of the table before SerDes supplies in Table 2</li> <li>In Table 2 split DDR row into two from total current requirement of 425 mA. One for DDR1 (131 mA) and other for DDR2 (140 mA).</li> <li>In Table 2 corrected current requirement numbers for NV<sub>DD</sub> from 27 mA to 74 mA, LV<sub>DD</sub> from 60 mA to 16 mA, LV<sub>DD</sub> from 85 mA to 22 mA and LV<sub>DDB</sub> from 85 mA to 44 mA.</li> <li>In Table 2 corrected Vdd and Vddc current requirements from 560 mA and 454 mA to 469 and 377 mA, respectively. Corrected Avdd1 and Avdd2 current requirements from 10 mA to 2–3 mA, and XCOREVDD from 100 mA to 170 mA.</li> <li>In Table 2, added row stating junction temperature range of 0 to 105°C. Added footnote 2 stating GPIO pins may operate from 2.5-V supply as well when configured for different functionality.</li> <li>In Section 2.1.2, "Power Supply Voltage Specification," added a note describing the purpose of Table 2.</li> <li>In Section 2.1.2, "Power Sequencing," and added Figure 3.</li> <li>In Table 4, added "but do include core, USB PLL, and a portion of SerDes digital power" to Note 1.</li> <li>In Table 4 corrected "Typical power" to "Maximum power" in note 2 and added a note for Typical Power.</li> <li>In Table 5, moved Local bus typical power dissipation under LVdd.</li> <li>Added Table 6 to show the low power mode power dissipation for D3warm mode.</li> <li>In Table 4, added riminum value of USB input hold t<sub>USIXKH</sub> from 0 to 1ns</li> <li>Added Table 40 and fulle 44 showing USB clock in specifications"</li> <li>In Table 42, added now for rise time (t<sub>12CF</sub>). Removed minimum value of t<sub>12CF</sub> Added note 5 stating that the device does not follow the 12C-BUS Specifications version 2.1 regarding the t<sub>12CF</sub> AC parameter.</li> <li>In Table 46, added nows for tipse time (t<sub>12CR</sub>). Removed minimum value of t<sub>12CF</sub> Added note 5 stating that the device does not follow the 12C-BUS Specifications version 2.1 regardin</li></ul> |

### Table 73. Document Revision History (continued)

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|