# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 267MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 516-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8313czqaddb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. Recommended Operating Conditions (continued)

| Characteristic Symbol Recommended Value <sup>1</sup> Unit | Current<br>Requirement |

|-----------------------------------------------------------|------------------------|

|-----------------------------------------------------------|------------------------|

Note:

- 1. GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. Some GPIO pins may operate from a 2.5-V supply when configured for other functions.

- 3. Min temperature is specified with  $T_A$ ; Max temperature is specified with  $T_J$

- 4. All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.

- 5. All I/O pins should be interfaced with peripherals operating at same voltage level.

- This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

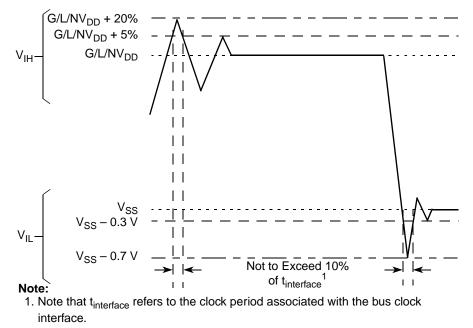

This figure shows the undershoot and overshoot voltages at the interfaces of the MPC8313E.

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/NV<sub>DD</sub>/LV<sub>DD</sub>

### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

| Driver Type                           | Output Impedance ( $\Omega$ ) | Supply Voltage           |

|---------------------------------------|-------------------------------|--------------------------|

| Local bus interface utilities signals | 42                            | NV <sub>DD</sub> = 3.3 V |

| PCI signals                           | 25                            |                          |

| DDR signal                            | 18                            | GV <sub>DD</sub> = 2.5 V |

## **3** Power Characteristics

The estimated typical power dissipation, not including I/O supply power, for this family of MPC8313E devices is shown in this table. Table 5 shows the estimated typical I/O power dissipation.

| Core Frequency<br>(MHz) | CSB Frequency<br>(MHz) | Typical <sup>2</sup> | Maximum for<br>Rev. 1.0 Silicon <sup>3</sup> | Maximum for<br>Rev. 2.x or Later Silicon <sup>3</sup> | Unit |

|-------------------------|------------------------|----------------------|----------------------------------------------|-------------------------------------------------------|------|

| 333                     | 167                    | 820                  | 1020                                         | 1200                                                  | mW   |

| 400                     | 133                    | 820                  | 1020                                         | 1200                                                  | mW   |

#### Table 4. MPC8313E Power Dissipation<sup>1</sup>

#### Note:

The values do not include I/O supply power or AV<sub>DD</sub>, but do include core, USB PLL, and a portion of SerDes digital power (not including XCOREV<sub>DD</sub>, XPADV<sub>DD</sub>, or SDAV<sub>DD</sub>, which all have dedicated power supplies for the SerDes PHY).

2. Typical power is based on a voltage of  $V_{DD}$  = 1.05 V and an artificial smoker test running at room temperature.

3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoker test.

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                                                                                                                                                                                                          | Parameter           | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|--------------------------|

| DDR 1, 60% utilization,<br>50% read/write                                                                                                                                                                                          | 333 MHz,<br>32 bits | _                           | 0.355                       | _                           | _                                                   | —                                                   | _                           | W    |                          |

| $\label{eq:Rs} \begin{array}{l} R_{s} = 22 \; \Omega \\ R_{t} = 50 \; \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data} = 8 \; pF, \\ \text{control address} = 8 \; pF, \\ \text{clock} = 8 \; pF \end{array}$ | 266 MHz,<br>32 bits | _                           | 0.323                       | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| DDR 2, 60% utilization,<br>50% read/write<br>$R_s = 22 \Omega$<br>$R_t = 75 \Omega$<br>single pair of clock<br>capacitive load: data = 8 pF,<br>control address = 8 pF,<br>clock = 8 pF                                            | 333 MHz,<br>32 bits | 0.266                       | —                           | _                           | _                                                   | —                                                   | _                           | W    | —                        |

|                                                                                                                                                                                                                                    | 266 MHz,<br>32 bits | 0.246                       | _                           | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| PCI I/O load = 50 pF                                                                                                                                                                                                               | 33 MHz              | —                           | —                           | 0.120                       |                                                     | _                                                   | —                           | W    | —                        |

|                                                                                                                                                                                                                                    | 66 MHz              |                             |                             | 0.249                       |                                                     | —                                                   | —                           | W    | —                        |

| Local bus I/O load = 20 pF                                                                                                                                                                                                         | 66 MHz              |                             |                             |                             |                                                     | —                                                   | 0.056                       | W    | —                        |

|                                                                                                                                                                                                                                    | 50 MHz              |                             |                             | _                           | _                                                   | —                                                   | 0.040                       | W    | _                        |

| TSEC I/O load = 20 pF                                                                                                                                                                                                              | MII,<br>25 MHz      | —                           | —                           | —                           | 0.008                                               | —                                                   | —                           | W    | Multiple by<br>number of |

|                                                                                                                                                                                                                                    | RGMII,<br>125 MHz   | —                           | —                           | —                           | 0.078                                               | 0.044                                               | —                           | W    | interface used           |

Table 5. MPC8313E Typical I/O Power Dissipation

This table provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

#### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —    |

This table provides the input AC timing specifications for the DDR2 SDRAM interface.

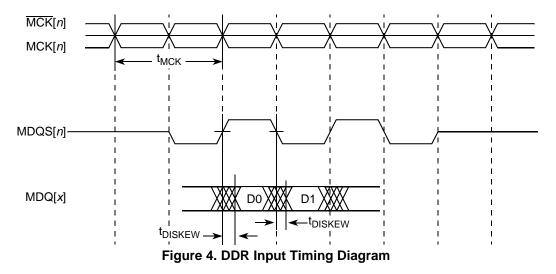

#### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $\text{GV}_{\text{DD}}$  of 2.5 ± 5%.

| Parameter                    | Symbol              | Min  | Мах | Unit | Note |

|------------------------------|---------------------|------|-----|------|------|

| Controller skew for MDQS—MDQ | t <sub>CISKEW</sub> | _    | _   | ps   | 1, 2 |

| 333 MHz                      |                     | -750 | 750 |      | —    |

| 266 MHz                      | _                   | -750 | 750 | _    | —    |

Notes:

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[*n*] and any corresponding bit that is captured with MDQS[*n*]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure illustrates the DDR input timing diagram showing the t<sub>DISKEW</sub> timing parameter.

#### 8.3.2 AC Requirements for SGMII SD REF CLK and SD REF CLK

This table lists the SGMII SerDes reference clock AC requirements. Note that SD\_REF\_CLK and SD REF CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 8   | —   | ns   |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _   | 100 | ps   |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _   | 50  | ps   |

#### Table 31. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

#### 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

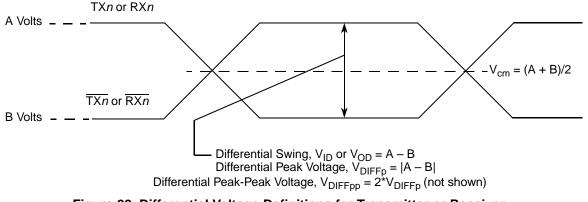

Table 32 and Table 33 describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD TX[n] and SD\_TX[*n*]) as depicted in Figure 16.

| Parameter                                   | Symbol                            | Min                                                                    | Тур | Max                                                                    | Unit | Note                       |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------|-----|------------------------------------------------------------------------|------|----------------------------|

| Supply voltage                              | XCOREV <sub>DD</sub>              | 0.95                                                                   | 1.0 | 1.05                                                                   | V    |                            |

| Output high voltage                         | V <sub>OH</sub>                   | _                                                                      | —   | XCOREV <sub>DD-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                          |

| Output low voltage                          | V <sub>OL</sub>                   | XCOREV <sub>DD-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                      | mV   | 1                          |

| Output ringing                              | V <sub>RING</sub>                 | _                                                                      | _   | 10                                                                     | %    |                            |

| Output differential voltage <sup>2, 3</sup> | V <sub>OD</sub>                   | 323                                                                    | 500 | 725                                                                    | mV   | Equalization setting: 1.0x |

| Output offset voltage                       | V <sub>OS</sub>                   | 425                                                                    | 500 | 575                                                                    | mV   | 1, 4                       |

| Output impedance<br>(single-ended)          | R <sub>O</sub>                    | 40                                                                     | _   | 60                                                                     | Ω    |                            |

| Mismatch in a pair                          | ΔR <sub>O</sub>                   | _                                                                      | _   | 10                                                                     | %    |                            |

| Change in V <sub>OD</sub> between 0 and 1   | $\Delta  V_{OD} $                 | _                                                                      | _   | 25                                                                     | mV   |                            |

| Change in V <sub>OS</sub> between 0 and 1   | $\Delta V_{OS}$                   | —                                                                      | —   | 25                                                                     | mV   |                            |

| Output current on short to GND              | I <sub>SA</sub> , I <sub>SB</sub> | _                                                                      | _   | 40                                                                     | mA   |                            |

Table 32. SGMII DC Transmitter Electrical Characteristics

#### Notes:

- 1. This will not align to DC-coupled SGMII. XCOREV<sub>DD-Typ</sub> = 1.0 V. 2.  $|V_{OD}| = |V_{TXn} V_{\overline{TXn}}|$ .  $|V_{OD}|$  is also referred as output differential peak voltage.  $V_{TX-DIFFp-p} = 2^*|V_{OD}|$ .

- 3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of XCOREV<sub>DD-Typ</sub> = 1.0 V, no common mode offset variation ( $V_{OS}$  = 500 mV), SerDes transmitter is terminated with 100- $\Omega$  differential load between TX[*n*] and TX[*n*].

- 4. V<sub>OS</sub> is also referred to as output common mode voltage.

Table 33. SGMII DC Receiver Electrical Characteristics (continued)

| Parameter                 | Symbol          | Min | Тур                   | Мах | Unit | Note |

|---------------------------|-----------------|-----|-----------------------|-----|------|------|

| Common mode input voltage | V <sub>CM</sub> | _   | V <sub>xcorevss</sub> | —   | V    | 4    |

Notes:

1. Input must be externally AC-coupled.

2.  $V_{RX\_DIFFp-p}$  is also referred to as peak to peak input differential voltage

3.  $V_{CM\_ACp-p}$  is also referred to as peak to peak AC common mode voltage.

4. On-chip termination to XCOREV<sub>SS</sub>.

### 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs  $(TX[n] \text{ and } \overline{TX}[n])$  or at the receiver inputs  $(RX[n] \text{ and } \overline{RX}[n])$  as depicted in Figure 18, respectively.

### 8.3.4.1 SGMII Transmit AC Timing Specifications

This table provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 34. SGMII Transmit AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                           | Symbol            | Min    | Тур | Мах    | Unit   | Note |

|-------------------------------------|-------------------|--------|-----|--------|--------|------|

| Deterministic jitter                | JD                | _      | _   | 0.17   | UI p-p |      |

| Total jitter                        | JT                | —      | _   | 0.35   | UI p-p |      |

| Unit interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1    |

| V <sub>OD</sub> fall time (80%–20%) | tfall             | 50     | _   | 120    | ps     |      |

| V <sub>OD</sub> rise time (20%–80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     |      |

Note:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

This table provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 17 shows the SGMII receiver input compliance mask eye diagram.

#### Table 35. SGMII Receive AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                                          | Symbol | Min  | Тур | Max | Unit   | Note |

|----------------------------------------------------|--------|------|-----|-----|--------|------|

| Deterministic jitter tolerance                     | JD     | 0.37 | —   | —   | UI p-p | 1    |

| Combined deterministic and random jitter tolerance | JDR    | 0.55 | —   | —   | UI p-p | 1    |

| Sinusoidal jitter tolerance                        | JSIN   | 0.1  | —   | —   | UI p-p | 1    |

The common mode voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm_out} = (V_{TXn} + V_{TXn})/2 = (A + B)/2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It's also referred as the DC offset in some occasion.

Figure 22. Differential Voltage Definitions for Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and TD, has a swing that goes between 2.5 and 2.0 V. Using these values, the peak-to-peak voltage swing of each signal (TD or TD) is 500 mV p-p, which is referred as the single-ended swing for each signal. In this example, since the differential signaling environment is fully symmetrical, the transmitter output's differential swing (V<sub>OD</sub>) has the same amplitude as each signal's single-ended swing. The differential output signal ranges between 500 and -500 mV, in other words, V<sub>OD</sub> is 500 mV in one phase and -500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp</sub>) is 1000 mV p-p.

### 9.2 SerDes Reference Clocks

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clocks input is SD\_REF\_CLK and SD\_REF\_CLK for SGMII interface.

The following sections describe the SerDes reference clock requirements and some application information.

### 9.2.1 SerDes Reference Clock Receiver Characteristics

Figure 23 shows a receiver reference diagram of the SerDes reference clocks.

- The supply voltage requirements for XCOREV<sub>DD</sub> are specified in Table 1 and Table 2.

- SerDes reference clock receiver reference circuit structure:

### 9.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low-phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

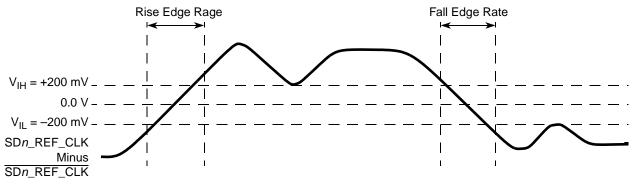

This table describes some AC parameters for SGMII protocol.

#### Table 39. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with  $XV_{DD\_SRDS1}$  or  $XV_{DD\_SRDS2}$  = 1.0 V ± 5%.

| Parameter                                                                  | Symbol             | Min  | Max  | Unit | Note |

|----------------------------------------------------------------------------|--------------------|------|------|------|------|

| Rising edge rate                                                           | Rise edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Falling edge rate                                                          | Fall edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Differential input high voltage                                            | V <sub>IH</sub>    | +200 | —    | mV   | 2    |

| Differential input low voltage                                             | V <sub>IL</sub>    | _    | -200 | mV   | 2    |

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-fall matching | _    | 20   | %    | 1, 4 |

#### Notes:

- 1. Measurement taken from single-ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from –200 to +200 mV on the differential waveform (derived from SD*n*\_REF\_CLK minus SD*n*\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 31.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point, where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The rise edge rate of SDn\_REF\_CLK should be compared to the fall edge rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 32.

Figure 31. Differential Measurement Points for Rise and Fall Time

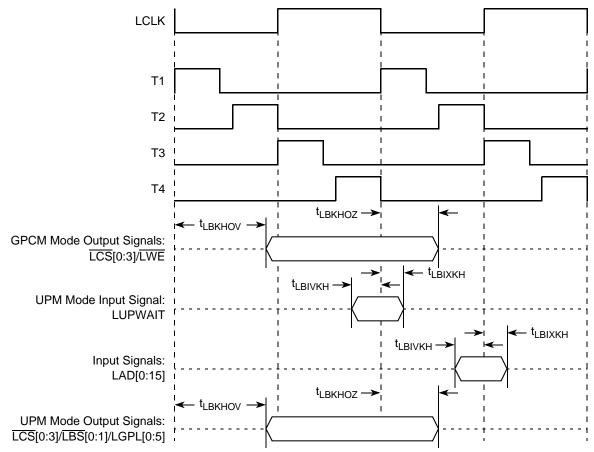

Figure 39. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4

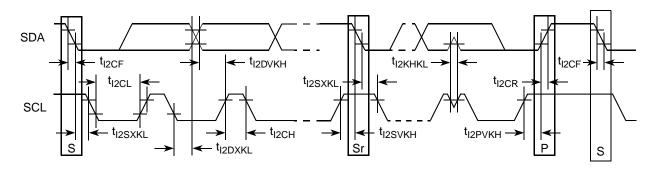

This figure shows the AC timing diagram for the  $I^2C$  bus.

Figure 47. I<sup>2</sup>C Bus AC Timing Diagram

## 14 PCI

This section describes the DC and AC electrical specifications for the PCI bus.

### 14.1 PCI DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI interface.

Table 50. PCI DC Electrical Characteristics<sup>1</sup>

| Parameter                 | Symbol          | Test Condition                          | Min                               | Max                    | Unit |

|---------------------------|-----------------|-----------------------------------------|-----------------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or           | $0.5\times \text{NV}_{\text{DD}}$ | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)              | -0.5                              | $0.3 	imes NV_{DD}$    | V    |

| High-level output voltage | V <sub>OH</sub> | $NV_{DD} = min, I_{OH} = -100 \ \mu A$  | $0.9 	imes NV_{DD}$               | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | $NV_{DD}$ = min, $I_{OL}$ = 100 $\mu$ A | _                                 | $0.1 	imes NV_{DD}$    | V    |

| Input current             | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$          | _                                 | ±5                     | μΑ   |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $NV_{IN}$  symbol referenced in Table 1 and Table 2.

### 14.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the MPC8313E is configured as a host or agent device.

This table shows the PCI AC timing specifications at 66 MHz.

Table 51. PCI AC Timing Specifications at 66 MHz

| Parameter              | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|------------------------|---------------------|-----|-----|------|------|

| Clock to output valid  | <sup>t</sup> PCKHOV | —   | 6.0 | ns   | 2    |

| Output hold from clock | t <sub>PCKHOX</sub> | 1   | —   | ns   | 2    |

### **15.2 Timers AC Timing Specifications**

This table provides the Timers input and output AC timing specifications.

Table 54. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

2. Timers inputs and outputs are asynchronous to any visible clock. Timers outputs should be synchronized before use by any external synchronous logic. Timers inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation

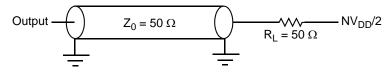

This figure provides the AC test load for the Timers.

Figure 51. Timers AC Test Load

### 16 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

### **16.1 GPIO DC Electrical Characteristics**

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 3.3-V supply.

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA       | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μA   |

Table 55. GPIO (When Operating at 3.3 V) DC Electrical Characteristics

Note:

1. This specification only applies to GPIO pins that are operating from a 3.3-V supply. See Table 62 for the power supply listed for the individual GPIO signal.

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 2.5-V supply.

| Parameters           | Symbol           | Conditions                         |                        | Min                   | Мах                    | Unit |

|----------------------|------------------|------------------------------------|------------------------|-----------------------|------------------------|------|

| Supply voltage 2.5 V | NV <sub>DD</sub> |                                    | —                      | 2.37                  | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA          | NV <sub>DD</sub> = min | 2.00                  | NV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA           | NV <sub>DD</sub> = min | V <sub>SS</sub> – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                                  | NV <sub>DD</sub> = min | 1.7                   | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                  | NV <sub>DD</sub> = min | -0.3                  | 0.70                   | V    |

| Input high current   | IIH              | V <sub>IN</sub> = NV <sub>DD</sub> |                        | —                     | 10                     | μΑ   |

| Input low current    | ۱ <sub>IL</sub>  | V <sub>IN</sub> = V <sub>SS</sub>  |                        | -15                   | —                      | μA   |

| Table 56. GPIO (When Operating at 2.5 V) DC Electrical Characteristics |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Note:

1. This specification only applies to GPIO pins that are operating from a 2.5-V supply. See Table 62 for the power supply listed for the individual GPIO signal

### 16.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLKIN. Timings are measured at the pin.

2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

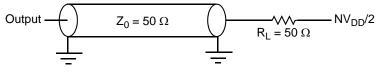

This figure provides the AC test load for the GPIO.

Figure 52. GPIO AC Test Load

| Characteristic     | Symbol          | Condition                      | Min  | Max                    | Unit |

|--------------------|-----------------|--------------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                              | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μΑ   |

### **18.2 SPI AC Timing Specifications**

This table and provide the SPI input and output AC timing specifications.

| Table 61 | SPI AC | Timina       | Specifications <sup>1</sup> |

|----------|--------|--------------|-----------------------------|

|          |        | ' i iiiiiiig | opecifications              |

| Characteristic                                           | Symbol <sup>2</sup> | Min | Мах | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs—master mode (internal clock) delay           | t <sub>NIKHOV</sub> | 0.5 | 6   | ns   |

| SPI outputs—slave mode (external clock) delay            | t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 6   | —   | ns   |

| SPI inputs—master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | —   | ns   |

| SPI inputs—slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Note:

1. Output specifications are measured from the 50% level of the rising edge of SYS\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

</sub>

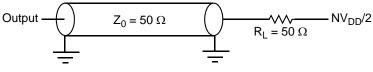

This figure provides the AC test load for the SPI.

Figure 53. SPI AC Test Load

Figure 54 and Figure 55 represent the AC timing from Table 61. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

#### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal         | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|----------------|--------------------|----------|------------------|------|

| TMS            | E4                 | I        | NV <sub>DD</sub> | 4    |

| TRST           | E5                 | I        | NV <sub>DD</sub> | 4    |

|                | TEST               |          | I I              |      |

| TEST_MODE      | F4                 | l        | $NV_{DD}$        | 6    |

|                | DEBUG              |          |                  |      |

| QUIESCE        | F5                 | 0        | $NV_{DD}$        | _    |

|                | System Control     |          |                  |      |

| HRESET         | F2                 | I/O      | $NV_{DD}$        | 1    |

| PORESET        | F3                 | I        | NV <sub>DD</sub> | _    |

| SRESET         | F1                 | I        | NV <sub>DD</sub> | _    |

|                | Clocks             |          |                  |      |

| SYS_CR_CLK_IN  | U26                | I        | NV <sub>DD</sub> | _    |

| SYS_CR_CLK_OUT | U25                | 0        | NV <sub>DD</sub> |      |

| SYS_CLK_IN     | U23                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_IN  | T26                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_OUT | R26                | 0        | NV <sub>DD</sub> | _    |

| USB_CLK_IN     | T22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_OUT   | U24                | 0        | NV <sub>DD</sub> | 3    |

| RTC_PIT_CLOCK  | R22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_IN    | T24                | I        | NV <sub>DD</sub> |      |

|                | MISC               |          | I I              |      |

| THERM0         | N1                 | Ι        | NV <sub>DD</sub> | 7    |

| THERM1         | N3                 | Ι        | NV <sub>DD</sub> | 7    |

|                | PCI                |          | 1                |      |

| PCI_INTA       | AF7                | 0        | NV <sub>DD</sub> | _    |

| PCI_RESET_OUT  | AB11               | 0        | NV <sub>DD</sub> | _    |

| PCI_AD0        | AB20               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD1        | AF23               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD2        | AF22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD3        | AB19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD4        | AE22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD5        | AF21               | I/O      | NV <sub>DD</sub> | _    |

| Signal    | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|-----------|--------------------|----------|------------------|------|

| PCI_AD6   | AD19               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD7   | AD20               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD8   | AC18               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD9   | AD18               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD10  | AB18               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD11  | AE19               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD12  | AB17               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD13  | AE18               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD14  | AD17               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD15  | AF19               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD16  | AB14               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD17  | AF15               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD18  | AD14               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD19  | AE14               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD20  | AF12               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD21  | AE11               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD22  | AD12               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD23  | AB13               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD24  | AF9                | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD25  | AD11               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD26  | AE10               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD27  | AB12               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD28  | AD10               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD29  | AC10               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD30  | AF10               | I/O      | NV <sub>DD</sub> | —    |

| PCI_AD31  | AF8                | I/O      | NV <sub>DD</sub> | —    |

| PCI_C/BE0 | AC19               | I/O      | NV <sub>DD</sub> | —    |

| PCI_C/BE1 | AB15               | I/O      | NV <sub>DD</sub> | —    |

| PCI_C/BE2 | AF14               | I/O      | NV <sub>DD</sub> | —    |

| PCI_C/BE3 | AF11               | I/O      | NV <sub>DD</sub> | —    |

| PCI_PAR   | AD16               | I/O      | NV <sub>DD</sub> | —    |

| PCI_FRAME | AF16               | I/O      | $NV_{DD}$        | 5    |

#### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

The primary clock source for the MPC8313E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the device is configured as a PCI host device, SYS\_CLK\_IN is its primary input clock. SYS\_CLK\_IN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether SYS\_CLK\_IN or SYS\_CLK\_IN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCICOEn] parameters select whether the PCI\_SYNC\_OUT is driven out on the PCI\_CLK\_OUTn signals.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the device to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock. When the device is configured as a PCI agent device the SYS\_CLK\_IN signal should be tied to VSS.

As shown in Figure 57, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create the coherent system bus clock ( $csb\_clk$ ), the internal clock for the DDR controller ( $ddr\_clk$ ), and the internal clock for the local bus interface unit ( $lbc\_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$$csb_clk = \{PCI_SYNC_IN \times (1 + \sim \overline{CFG_CLKIN_DIV})\} \times SPMF$$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 +  $\sim$ CFG\_CLKIN\_DIV) is the SYS\_CLK\_IN frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies up the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See Chapter 4, "Reset, Clocking, and Initialization," in the *MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual*, for more information on the clock subsystem.

The internal *ddr\_clk* frequency is determined by the following equation:

$ddr_clk = csb_clk \times (1 + RCWL[DDRCM])$

Note that  $ddr_clk$  is not the external memory bus frequency;  $ddr_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the same frequency as  $ddr_clk$ .

The internal *lbc\_clk* frequency is determined by the following equation:

$lbc\_clk = csb\_clk \times (1 + \text{RCWL[LBCM]})$

Note that *lbc\_clk* is not the external local bus frequency; *lbc\_clk* passes through the a LBC clock divider to create the external local bus clock outputs (LCLK[0:1]). The LBC clock divider ratio is controlled by LCRR[CLKDIV].

In addition, some of the internal units may be required to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. Table 63 specifies which units have a configurable clock frequency.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0100       | × 4                                 |

| 0101       | × 5                                 |

| 0110       | × 6                                 |

| 0111–1111  | Reserved                            |

#### Table 65. System PLL Multiplication Factors (continued)

#### Note:

1. If RCWL[DDRCM] and RCWL[LBCM] are both cleared, the system PLL VCO frequency = (CSB frequency) × (System PLL VCO Divider).

2. If either RCWL[DDRCM] or RCWL[LBCM] are set, the system PLL VCO frequency = 2 × (CSB frequency) × (System PLL VCO Divider).

3. The VCO divider needs to be set properly so that the System PLL VCO frequency is in the range of 450–750 MHz

As described in Section 20, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (SYS\_CLK\_IN or PCI\_SYNC\_IN) and the internal coherent system bus clock (*csb\_clk*). This table shows the expected frequency values for the CSB frequency for select *csb\_clk* to SYS\_CLK\_IN/PCI\_SYNC\_IN ratios.

|                                        |      |                                                   | Inp                     | out Clock Fre | equency (MF | lz) <sup>2</sup> |

|----------------------------------------|------|---------------------------------------------------|-------------------------|---------------|-------------|------------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :Input<br>Clock Ratio <sup>2</sup> | 24                      | 25            | 33.33       | 66.67            |

|                                        |      |                                                   | csb_clk Frequency (MHz) |               |             |                  |

| High                                   | 0010 | 2:1                                               |                         |               |             | 133              |

| High                                   | 0011 | 3:1                                               |                         |               | 100         |                  |

| High                                   | 0100 | 4:1                                               |                         | 100           | 133         |                  |

| High                                   | 0101 | 5:1                                               | 120                     | 125           | 167         |                  |

| High                                   | 0110 | 6:1                                               | 144                     | 150           |             |                  |

| Low                                    | 0010 | 2:1                                               |                         |               |             | 133              |

| Low                                    | 0011 | 3:1                                               |                         |               | 100         |                  |

| Low                                    | 0100 | 4:11                                              |                         | 100           | 133         |                  |

| Low                                    | 0101 | 5:1                                               | 120                     | 125           | 167         |                  |

| Low                                    | 0110 | 6:1                                               | 144                     | 150           |             |                  |

Table 66. CSB Frequency Options

<sup>1</sup> CFG\_CLKIN\_DIV select the ratio between SYS\_CLK\_IN and PCI\_SYNC\_OUT.

<sup>2</sup> SYS\_CLK\_IN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

### 20.3 Example Clock Frequency Combinations

This table shows several possible frequency combinations that can be selected based on the indicated input reference frequencies, with RCWLR[LBCM] = 0 and RCWLR[DDRCM] =1, such that the LBC operates with a frequency equal to the frequency of  $csb\_clk$  and the DDR controller operates at twice the frequency of  $csb\_clk$ .

|                            |                   |                   |                  |                                        |                  |      | LBC(  | lbc_cl | k)                      | e     | 300 Co | ore(cor    | e_clk) |            |

|----------------------------|-------------------|-------------------|------------------|----------------------------------------|------------------|------|-------|--------|-------------------------|-------|--------|------------|--------|------------|

| SYS_<br>CLK_IN/<br>PCI_CLK | SPMF <sup>1</sup> | VCOD <sup>2</sup> | VCO <sup>3</sup> | CSB<br>( <i>csb_clk</i> ) <sup>4</sup> | DDR<br>(ddr_clk) | /2   | /4    | /8     | USB<br>ref <sup>5</sup> | × 1   | × 1.5  | × <b>2</b> | × 2.5  | × <b>3</b> |

| 25.0                       | 6                 | 2                 | 600.0            | 150.0                                  | 300.0            |      | 37.5  | 18.8   | Note <sup>6</sup>       | 150.0 | 225    | 300        | 375    | _          |

| 25.0                       | 5                 | 2                 | 500.0            | 125.0                                  | 250.0            | 62.5 | 31.25 | 15.6   | Note 6                  | 125.0 | 188    | 250        | 313    | 375        |

| 33.3                       | 5                 | 2                 | 666.0            | 166.5                                  | 333.0            | _    | 41.63 | 20.8   | Note 6                  | 166.5 | 250    | 333        | _      | _          |

| 33.3                       | 4                 | 2                 | 532.8            | 133.2                                  | 266.4            | 66.6 | 33.3  | 16.7   | Note 6                  | 133.2 | 200    | 266        | 333    | 400        |

| 48.0                       | 3                 | 2                 | 576.0            | 144.0                                  | 288.0            | _    | 36    | 18.0   | 48.0                    | 144.0 | 216    | 288        | 360    | —          |

| 66.7                       | 2                 | 2                 | 533.4            | 133.3                                  | 266.7            | 66.7 | 33.34 | 16.7   | Note 6                  | 133.3 | 200    | 267        | 333    | 400        |

| Table 68. System Clock Frequencies | Table | 68. | System | Clock | Frequencies |

|------------------------------------|-------|-----|--------|-------|-------------|

|------------------------------------|-------|-----|--------|-------|-------------|

Note:

1. System PLL multiplication factor.

2. System PLL VCO divider.

3. When considering operating frequencies, the valid core VCO operating range of 400–800 MHz must not be violated.

4. Due to erratum eTSEC40, *csb\_clk* frequencies of less than 133 MHz do not support gigabit Ethernet data rates. The core frequency must be 333 MHz for gigabit Ethernet operation. This erratum will be fixed in revision 2 silicon.

5. Frequency of USB PLL input reference.

6. USB reference clock must be supplied from a separate source as it must be 24 or 48 MHz, the USB reference must be supplied from a separate external source using USB\_CLK\_IN.

## 21 Thermal

This section describes the thermal specifications of the MPC8313E.

### 21.1 Thermal Characteristics

This table provides the package thermal characteristics for the 516,  $27 \times 27$  mm TEPBGAII.

| Table 69. Package The | ermal Characteristics for | <sup>·</sup> TEPBGAII |

|-----------------------|---------------------------|-----------------------|

|-----------------------|---------------------------|-----------------------|

| Characteristic                         | Board Type              | Symbol              | TEPBGA II | Unit | Note    |

|----------------------------------------|-------------------------|---------------------|-----------|------|---------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	ext{	heta}JA}$ | 25        | °C/W | 1, 2    |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$ | 18        | °C/W | 1, 2, 3 |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{	hetaJMA}$      | 20        | °C/W | 1, 3    |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	hetaJMA}$      | 15        | °C/W | 1, 3    |

| Junction-to-board                      | _                       | $R_{	heta JB}$      | 10        | °C/W | 4       |

Table 69. Package Thermal Characteristics for TEPBGAII (continued)

| Characteristic          | Board Type         | Symbol              | TEPBGA II | Unit | Note |

|-------------------------|--------------------|---------------------|-----------|------|------|

| Junction-to-case        | _                  | $R_{	ext{	heta}JC}$ | 8         | °C/W | 5    |

| Junction-to-package top | Natural convection | $\Psi_{JT}$         | 7         | °C/W | 6    |

Note:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 21.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$ , where  $P_{I/O}$  is the power dissipation of the I/O drivers.

### 21.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. As a general statement, the value obtained on a single layer board is appropriate for a tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

# 21.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction-to-ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

| Heat Sink Assuming Thermal Grease                | Airflow            | Thermal Resistance<br>(°C/W) |

|--------------------------------------------------|--------------------|------------------------------|

| Wakefield 53 $\times$ 53 $\times$ 2.5 mm pin fin | Natural convection | 13.0                         |

|                                                  | 0.5 m/s            | 10.6                         |

|                                                  | 1 m/s              | 9.7                          |

|                                                  | 2 m/s              | 9.2                          |

|                                                  | 4 m/s              | 8.9                          |

| Aavid 35 $\times~$ 31 $\times$ 23 mm pin fin     | Natural convection | 14.4                         |

|                                                  | 0.5 m/s            | 11.3                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.9                          |

|                                                  | 4 m/s              | 9.4                          |

| Aavid $30 \times 30 \times 9.4$ mm pin fin       | Natural convection | 16.5                         |

|                                                  | 0.5 m/s            | 13.5                         |

|                                                  | 1 m/s              | 12.1                         |

|                                                  | 2 m/s              | 10.9                         |

|                                                  | 4 m/s              | 10.0                         |

| Aavid $43 \times 41 \times 16.5$ mm pin fin      | Natural convection | 14.5                         |

|                                                  | 0.5 m/s            | 11.7                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.7                          |

|                                                  | 4 m/s              | 9.2                          |

Table 70. Thermal Resistance for TEPBGAII with Heat Sink in Open Flow

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in Table 70. More detailed thermal models can be made available on request.

- Output signals on the SerDes interface are fed from the XPADV<sub>DD</sub> power plane. Input signals and sensitive transceiver analog circuits are on the XCOREV<sub>DD</sub> supply.

- Power: XPADV<sub>DD</sub> consumes less than 300 mW; XCOREV<sub>DD</sub> + SDAV<sub>DD</sub> consumes less than 750 mW.

### 22.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8313E system, and the MPC8313E itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ , and  $LV_{DDB}$  pin of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DDA}$ ,  $LV_{DDB}$ , and VSS power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ , and  $LV_{DDB}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100 to 330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values and types of bulk capacitors.

### 22.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power (XCOREV<sub>DD</sub> and XPADV<sub>DD</sub>) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only SMT capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there should be a 1-µF ceramic chip capacitor from each SerDes supply (XCOREV<sub>DD</sub> and XPADV<sub>DD</sub>) to the board ground plane on each side of the device. This should be done for all SerDes supplies.