#### Welcome to E-XFL.COM

### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

E·XF

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 267MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | ·                                                           |

| Ethernet                        | 10/100/1000Mbps (2)                                         |

| SATA                            |                                                             |

| USB                             | USB 2.0 + PHY (1)                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | -40°C ~ 105°C (TA)                                          |

| Security Features               | -                                                           |

| Package / Case                  | 516-BBGA Exposed Pad                                        |

| Supplier Device Package         | 516-TEPBGA (27x27)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8313czqaddc |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.10 Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) allows the MPC8313E to exchange data between other PowerQUICC family chips, Ethernet PHYs for configuration, and peripheral devices such as EEPROMs, real-time clocks, A/D converters, and ISDN devices.

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (receive, transmit, clock, and slave select). The SPI block consists of transmitter and receiver sections, an independent baud-rate generator, and a control unit.

# 1.11 DMA Controller, Dual I<sup>2</sup>C, DUART, Local Bus Controller, and Timers

The MPC8313E provides an integrated four-channel DMA controller with the following features:

- Allows chaining (both extended and direct) through local memory-mapped chain descriptors (accessible by local masters)

- Supports misaligned transfers

There are two I<sup>2</sup>C controllers. These synchronous, multi-master buses can be connected to additional devices for expansion and system development.

The DUART supports full-duplex operation and is compatible with the PC16450 and PC16550 programming models. The 16-byte FIFOs are supported for both the transmitter and the receiver.

The MPC8313E local bus controller (LBC) port allows connections with a wide variety of external DSPs and ASICs. Three separate state machines share the same external pins and can be programmed separately to access different types of devices. The general-purpose chip select machine (GPCM) controls accesses to asynchronous devices using a simple handshake protocol. The three user programmable machines (UPMs) can be programmed to interface to synchronous devices or custom ASIC interfaces. Each chip select can be configured so that the associated chip interface can be controlled by the GPCM or UPM controller. The FCM provides a glueless interface to parallel-bus NAND Flash E2PROM devices. The FCM contains three basic configuration register groups—BR*n*, OR*n*, and FMR. Both may exist in the same system. The local bus can operate at up to 66 MHz.

The MPC8313E system timers include the following features: periodic interrupt timer, real time clock, software watchdog timer, and two general-purpose timer blocks.

## 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8313E. The MPC8313E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

| Driver Type                                        | Output Impedance ( $\Omega$ ) | Supply Voltage                      |

|----------------------------------------------------|-------------------------------|-------------------------------------|

| DDR2 signal                                        | 18                            | GV <sub>DD</sub> = 1.8 V            |

| DUART, system control, I <sup>2</sup> C, JTAG, SPI | 42                            | NV <sub>DD</sub> = 3.3 V            |

| GPIO signals                                       | 42                            | NV <sub>DD</sub> = 3.3 V            |

| eTSEC signals                                      | 42                            | $LV_{DDA}$ , $LV_{DDB}$ = 2.5/3.3 V |

| USB signals                                        | 42                            | LV <sub>DDB</sub> = 2.5/3.3 V       |

Table 3. Output Drive Capability (continued)

## 2.2 Power Sequencing

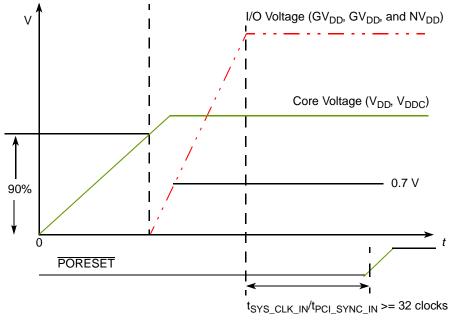

The MPC8313E does not require the core supply voltage ( $V_{DD}$  and  $V_{DDC}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) to be applied in any particular order. Note that during power ramp-up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$  and  $V_{DDC}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are stable, wait for a minimum of 32 clock cycles before negating PORESET.

Note that there is no specific power down sequence requirement for the MPC8313E. I/O voltage supplies  $(GV_{DD}, LV_{DD}, and NV_{DD})$  do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

## 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Max                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz,  $T_A$  = 25°C,  $V_{OUT}$  =  $GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.3                      | 2.7                      | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |      |

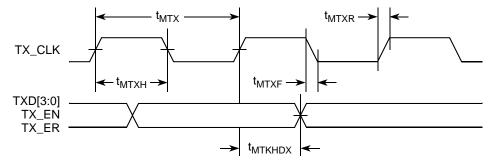

This figure shows the MII transmit AC timing diagram.

Figure 8. MII Transmit AC Timing Diagram

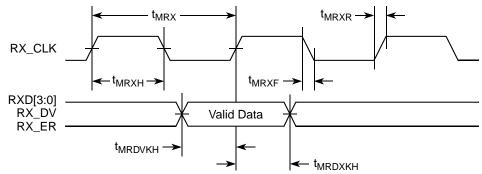

### 8.2.1.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

Table 27. MII Receive AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DDA}}/\text{LV}_{\text{DDB}}/\text{NV}_{\text{DD}}$  of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                              | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|------------------------------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                                      | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                                     | t <sub>MRX</sub>                    | —    | 40  | —   | ns   |

| RX_CLK duty cycle                                                | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                      | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                       | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MRXR</sub>                   | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>MRXF</sub>                   | 1.0  |     | 4.0 | ns   |

Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. The frequency of RX\_CLK should not exceed the TX\_CLK by more than 300 ppm

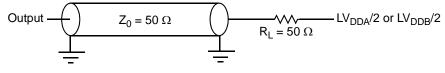

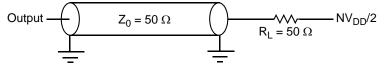

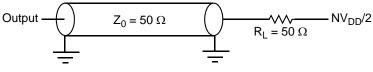

This figure provides the AC test load for TSEC.

Figure 9. TSEC AC Test Load

This figure shows the MII receive AC timing diagram.

Figure 10. MII Receive AC Timing Diagram RMII AC Timing Specifications

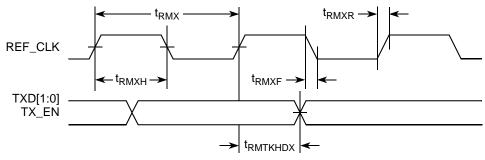

### 8.2.1.3 RMII Transmit AC Timing Specifications

This table provides the RMII transmit AC timing specifications.

### Table 28. RMII Transmit AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock                                          | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                     | t <sub>RMXH/</sub> t <sub>RMX</sub> | 35  | _   | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay             | t <sub>RMTKHDX</sub>                | 2   | _   | 10  | ns   |

| REF_CLK data clock rise $V_{IL}(min)$ to $V_{IH}(max)$ | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>RMXF</sub>                   | 1.0 | _   | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

This figure shows the RMII transmit AC timing diagram.

Figure 11. RMII Transmit AC Timing Diagram

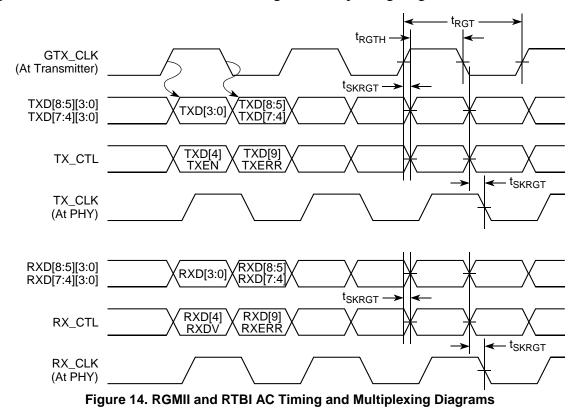

## 8.2.2 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

### Table 30. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DDA}/LV_{DDB}$  of 2.5 V ± 5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|---------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                    | -0.5 | —   | 0.5  | ns   |

| Data to clock input skew (at receiver) <sup>2</sup>    | tskrgt                                |      | _   | 2.6  | ns   |

| Clock cycle duration <sup>3</sup>                      | t <sub>RGT</sub>                      | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4, 5</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 5</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                     | —    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                     | _    | —   | 0.75 | ns   |

| GTX_CLK125 reference clock period                      | t <sub>G12</sub> <sup>6</sup>         | —    | 8.0 | —    | ns   |

| GTX_CLK125 reference clock duty cycle                  | t <sub>G125H</sub> /t <sub>G125</sub> | 47   | —   | 53   | %    |

Note:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the RTBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is  $LV_{DDA}/2$  or  $LV_{DDB}/2$ .

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. The frequency of RX\_CLK should not exceed the GTX\_CLK125 by more than 300 ppm

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

### 8.3 SGMII Interface Electrical Characteristics

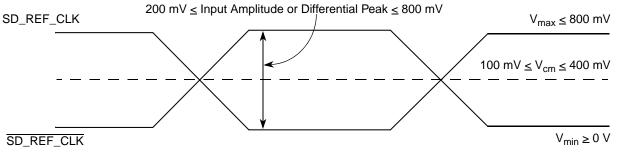

Each SGMII port features a 4-wire AC-coupled serial link from the dedicated SerDes interface of MPC8313E as shown in Figure 15, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features a 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XCOREVSS. The reference circuit of the SerDes transmitter and receiver is shown in Figure 33.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines described in Section 22.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the TSEC\_GTX\_CLK125 clock is not required for this port. Instead, the SerDes reference clock is required on SD\_REF\_CLK and SD\_REF\_CLK pins.

## 8.3.1 DC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 9, "High-Speed Serial Interfaces (HSSI)."

### 8.3.2 AC Requirements for SGMII SD REF CLK and SD REF CLK

This table lists the SGMII SerDes reference clock AC requirements. Note that SD\_REF\_CLK and SD REF CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 8   | —   | ns   |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _   | 100 | ps   |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _   | 50  | ps   |

### Table 31. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

#### 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 32 and Table 33 describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD TX[n] and SD\_TX[*n*]) as depicted in Figure 16.

| Parameter                                   | Symbol                            | Min                                                                    | Тур | Max                                                                    | Unit | Note                       |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------|-----|------------------------------------------------------------------------|------|----------------------------|

| Supply voltage                              | XCOREV <sub>DD</sub>              | 0.95                                                                   | 1.0 | 1.05                                                                   | V    |                            |

| Output high voltage                         | V <sub>OH</sub>                   | _                                                                      | —   | XCOREV <sub>DD-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                          |

| Output low voltage                          | V <sub>OL</sub>                   | XCOREV <sub>DD-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                      | mV   | 1                          |

| Output ringing                              | V <sub>RING</sub>                 | _                                                                      | _   | 10                                                                     | %    |                            |

| Output differential voltage <sup>2, 3</sup> | V <sub>OD</sub>                   | 323                                                                    | 500 | 725                                                                    | mV   | Equalization setting: 1.0x |

| Output offset voltage                       | V <sub>OS</sub>                   | 425                                                                    | 500 | 575                                                                    | mV   | 1, 4                       |

| Output impedance<br>(single-ended)          | R <sub>O</sub>                    | 40                                                                     | _   | 60                                                                     | Ω    |                            |

| Mismatch in a pair                          | ΔR <sub>O</sub>                   | _                                                                      | _   | 10                                                                     | %    |                            |

| Change in V <sub>OD</sub> between 0 and 1   | $\Delta  V_{OD} $                 | _                                                                      | _   | 25                                                                     | mV   |                            |

| Change in V <sub>OS</sub> between 0 and 1   | $\Delta V_{OS}$                   | —                                                                      | —   | 25                                                                     | mV   |                            |

| Output current on short to GND              | I <sub>SA</sub> , I <sub>SB</sub> | _                                                                      | _   | 40                                                                     | mA   |                            |

Table 32. SGMII DC Transmitter Electrical Characteristics

### Notes:

- 1. This will not align to DC-coupled SGMII. XCOREV<sub>DD-Typ</sub> = 1.0 V. 2.  $|V_{OD}| = |V_{TXn} V_{\overline{TXn}}|$ .  $|V_{OD}|$  is also referred as output differential peak voltage.  $V_{TX-DIFFp-p} = 2^*|V_{OD}|$ .

- 3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of XCOREV<sub>DD-Typ</sub> = 1.0 V, no common mode offset variation ( $V_{OS}$  = 500 mV), SerDes transmitter is terminated with 100- $\Omega$  differential load between TX[*n*] and TX[*n*].

- 4. V<sub>OS</sub> is also referred to as output common mode voltage.

of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 9.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 24 shows the SerDes reference clock input requirement for the DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to  $XCOREV_{SS}$ . Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage ( $XCOREV_{SS}$ ). Figure 25 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 26 shows the SerDes reference clock input requirement for the single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC coupled externally. For the best noise performance, the reference of the clock could be DC or AC coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 24. Differential Reference Clock Input DC Requirements (External DC-Coupled)

## 10 USB

## 10.1 USB Dual-Role Controllers

This section provides the AC and DC electrical specifications for the USB interface.

### **10.1.1 USB DC Electrical Characteristics**

This table provides the DC electrical characteristics for the USB interface.

| Table 40. USB DC Electrical Characte | eristics |

|--------------------------------------|----------|

|--------------------------------------|----------|

| Parameter                                          | Symbol          | Min                     | Мах                     | Unit |

|----------------------------------------------------|-----------------|-------------------------|-------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2.0                     | LV <sub>DDB</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                    | 0.8                     | V    |

| Input current                                      | I <sub>IN</sub> | —                       | ±5                      | μΑ   |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | LV <sub>DDB</sub> - 0.2 | _                       | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$   | V <sub>OL</sub> | —                       | 0.2                     | V    |

## 10.1.2 USB AC Electrical Specifications

This table describes the general timing parameters of the USB interface.

Table 41. USB General Timing Parameters (ULPI Mode Only)

| Parameter                              | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|----------------------------------------|---------------------|-----|-----|------|------|

| USB clock cycle time                   | t <sub>USCK</sub>   | 15  | —   | ns   |      |

| Input setup to USB clock—all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   |      |

| input hold to USB clock—all inputs     | t <sub>USIXKH</sub> | 1   | —   | ns   |      |

| USB clock to output valid—all outputs  | t <sub>USKHOV</sub> | _   | 7   | ns   |      |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   | —   | ns   |      |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (USB) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes us timing (USB) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

The following two figures provide the AC test load and signals for the USB, respectively.

Figure 34. USB AC Test Load

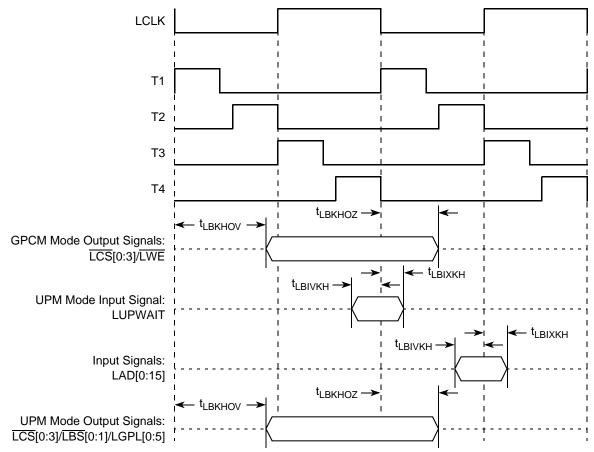

Figure 39. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4

| Characteristic     | Symbol          | Condition                      | Min  | Max                    | Unit |

|--------------------|-----------------|--------------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                              | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μΑ   |

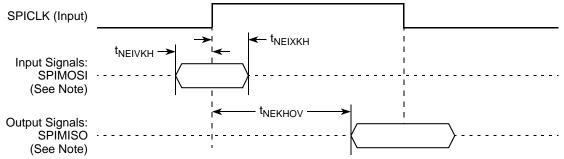

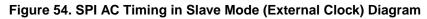

## **18.2 SPI AC Timing Specifications**

This table and provide the SPI input and output AC timing specifications.

| Table 61 | SPI AC | Timina       | Specifications <sup>1</sup> |

|----------|--------|--------------|-----------------------------|

|          |        | ' i iiiiiiig | opecifications              |

| Characteristic                                           | Symbol <sup>2</sup> | Min | Мах | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs—master mode (internal clock) delay           | t <sub>NIKHOV</sub> | 0.5 | 6   | ns   |

| SPI outputs—slave mode (external clock) delay            | t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 6   | —   | ns   |

| SPI inputs—master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | —   | ns   |

| SPI inputs—slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Note:

1. Output specifications are measured from the 50% level of the rising edge of SYS\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

</sub>

This figure provides the AC test load for the SPI.

Figure 53. SPI AC Test Load

Figure 54 and Figure 55 represent the AC timing from Table 61. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

This figure shows the SPI timing in master mode (internal clock).

Figure 55. SPI AC Timing in Master Mode (Internal Clock) Diagram

## 19 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8313E is available in a thermally enhanced plastic ball grid array (TEPBGAII), see Section 19.1, "Package Parameters for the MPC8313E TEPBGAII," and Section 19.2, "Mechanical Dimensions of the MPC8313E TEPBGAII," for information on the TEPBGAII.

## 19.1 Package Parameters for the MPC8313E TEPBGAII

The package parameters are as provided in the following list. The package type is 27 mm  $\times$  27 mm, 516 TEPBGAII.

| Package outline         | $27 \text{ mm} \times 27 \text{ mm}$                  |

|-------------------------|-------------------------------------------------------|

| Interconnects           | 516                                                   |

| Pitch                   | 1.00 mm                                               |

| Module height (typical) | 2.25 mm                                               |

| Solder Balls            | 96.5 Sn/3.5 Ag(VR package),                           |

|                         | 62 Sn/36 Pb/2 Ag (ZQ package) Ball diameter (typical) |

| 0.6 mm                  |                                                       |

| Signal     | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|------------|--------------------|----------|------------------|------|

| MEMC_MDQ29 | A20                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDQ30 | C22                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQ31 | B22                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDM0  | B7                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM1  | E6                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM2  | E18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM3  | E20                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDQS0 | A7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS1 | E7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS2 | B19                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS3 | A23                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MBA0  | D15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA1  | A18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA2  | A15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA0   | E12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA1   | D11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA2   | B11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA3   | A11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA4   | A12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA5   | E13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA6   | C12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA7   | E14                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA8   | B15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA9   | C17                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA10  | C13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA11  | A16                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA12  | C15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA13  | C16                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA14  | E15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MWE   | B18                | 0        | GV <sub>DD</sub> |      |

| MEMC_MRAS  | C11                | 0        | GV <sub>DD</sub> |      |

| MEMC_MCAS  | B10                | 0        | GV <sub>DD</sub> | _    |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal     | Package Pin Number             | Pin Type | Power<br>Supply  | Note |

|------------|--------------------------------|----------|------------------|------|

| MEMC_MCS0  | D10                            | 0        | GV <sub>DD</sub> | _    |

| MEMC_MCS1  | A10                            | 0        | GV <sub>DD</sub> | _    |

| MEMC_MCKE  | B14                            | 0        | GV <sub>DD</sub> | 3    |

| MEMC_MCK   | A13                            | 0        | GV <sub>DD</sub> | _    |

| MEMC_MCK   | A14                            | 0        | GV <sub>DD</sub> | —    |

| MEMC_MODT0 | B23                            | 0        | GV <sub>DD</sub> |      |

| MEMC_MODT1 | C23                            | 0        | GV <sub>DD</sub> | —    |

|            | Local Bus Controller Interface |          |                  |      |

| LAD0       | K25                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD1       | K24                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD2       | K23                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD3       | K22                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD4       | J25                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD5       | J24                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD6       | J23                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD7       | J22                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD8       | H24                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD9       | F26                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD10      | G24                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD11      | F25                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD12      | E25                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD13      | F24                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD14      | G22                            | I/O      | LV <sub>DD</sub> | 11   |

| LAD15      | F23                            | I/O      | LV <sub>DD</sub> | 11   |

| LA16       | AC25                           | 0        | LV <sub>DD</sub> | 11   |

| LA17       | AC26                           | 0        | LV <sub>DD</sub> | 11   |

| LA18       | AB22                           | 0        | LV <sub>DD</sub> | 11   |

| LA19       | AB23                           | 0        | LV <sub>DD</sub> | 11   |

| LA20       | AB24                           | 0        | LV <sub>DD</sub> | 11   |

| LA21       | AB25                           | 0        | LV <sub>DD</sub> | 11   |

| LA22       | AB26                           | 0        | LV <sub>DD</sub> | 11   |

| LA23       | E22                            | 0        | LV <sub>DD</sub> | 11   |

| Signal                                             | Package Pin Number | Pin Type | Power<br>Supply  | Note                     |

|----------------------------------------------------|--------------------|----------|------------------|--------------------------|

| RXB                                                | R1                 | I        |                  |                          |

| RXB                                                | P1                 | I        |                  | _                        |

| SD_IMP_CAL_RX                                      | V5                 | I        |                  | 200 Ω ±<br>10% to<br>GND |

| SD_REF_CLK                                         | T5                 | I        |                  | _                        |

| SD_REF_CLK                                         | T4                 | I        |                  |                          |

| SD_PLL_TPD                                         | T2                 | 0        |                  |                          |

| SD_IMP_CAL_TX                                      | N5                 | I        |                  | 100 Ω ±<br>10% to<br>GND |

| SDAVDD                                             | R5                 | I/O      |                  | —                        |

| SD_PLL_TPA_ANA                                     | R4                 | 0        |                  | —                        |

| SDAVSS                                             | R3                 | I/O      |                  | —                        |

|                                                    | USB PHY            |          |                  |                          |

| USB_DP                                             | P26                | I/O      |                  |                          |

| USB_DM                                             | N26                | I/O      |                  | _                        |

| USB_VBUS                                           | P24                | I/O      |                  | _                        |

| USB_TPA                                            | L26                | I/O      |                  | —                        |

| USB_RBIAS                                          | M24                | I/O      |                  | —                        |

| USB_PLL_PWR3                                       | M26                | I/O      |                  | —                        |

| USB_PLL_GND                                        | N24                | I/O      |                  | —                        |

| USB_PLL_PWR1                                       | N25                | I/O      |                  | —                        |

| USB_VSSA_BIAS                                      | M25                | I/O      |                  | —                        |

| USB_VDDA_BIAS                                      | M22                | I/O      |                  | —                        |

| USB_VSSA                                           | N22                | I/O      |                  | —                        |

| USB_VDDA                                           | P22                | I/O      |                  | —                        |

|                                                    | GTM/USB            | I        |                  |                          |

| USBDR_DRIVE_VBUS/GTM1_TIN1/GTM2_TIN2/LSRCID0       | AD23               | I/O      | NV <sub>DD</sub> | —                        |

| USBDR_PWRFAULT/GTM1_TGATE1/GTM2_TGATE2/<br>LSRCID1 | AE23               | I/O      | NV <sub>DD</sub> | —                        |

| USBDR_PCTL0/GTM1_TOUT1/LSRCID2                     | AC22               | 0        | NV <sub>DD</sub> | —                        |

| USBDR_PCTL1/LBC_PM_REF_10/LSRCID3                  | AB21               | 0        | $NV_{DD}$        | —                        |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

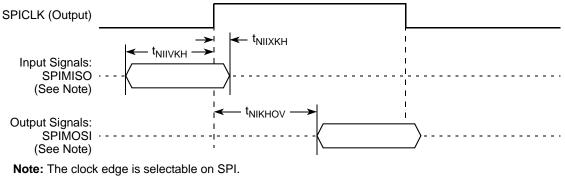

## 20 Clocking

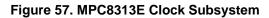

This figure shows the internal distribution of clocks within the MPC8313E.

<sup>2</sup> Multiplication factor L = 2, 3, 4, 5, and 6. Value is decided by RCWLR[SPMF].

The COP function of these processors allows a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert TRST without causing PORESET. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 61 allows the COP to independently assert HRESET or TRST, while ensuring that the target can drive HRESET as well. If the JTAG interface and COP header are not used, TRST should be tied to PORESET so that it is asserted when the system reset signal (PORESET) is asserted.

The COP header shown in Figure 61 adds many benefits—breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features are possible through this interface—and can be as inexpensive as an unpopulated footprint for a header to be added when needed.

The COP interface has a standard header for connection to the target system, based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header).

There is no standardized way to number the COP header shown in Figure 61; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 61 is common to all known emulators.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 10/2008 | <ul> <li>Added Note "The information in this document is accurate for revision 1.0, and 2.x and later. See Section 24.1, "Part Numbers Fully Addressed by this Document," before Section 1, "Overview."</li> <li>Added part numbering details for all the silicon revisions in Table 74.</li> <li>Changed V<sub>IH</sub> from 2.7 V to 2.4 V in Table 7.</li> <li>Added a column for maximum power dissipation in low power mode for Rev 2.x or later silicon in Table 6.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added Table 21 for DDR AC Specs on Rev 2.x or later silicon.</li> <li>Added EfWE, LFCLE, LFALE, LOE, LFRE, LFWP, LGTA, LUPWAIT, and LFRB in Table 63.</li> <li>In Table 39, added note 2: "This parameter is dependent on the csb_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC_MDC.)"</li> <li>Removed mentions of SGMII (SGMII has separate specs) from Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/STBI Electrical Characteristics."</li> <li>Corrected Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/SGMII/RTBI Electrical Characteristics," to state that RGMII/RTBI Interfaces only operate at 2.5 V, not 3.3 V.</li> <li>Added ZQ package to ordering information In Table 74 and Section 19.1, "Package Parameters for the MPC8313E TEPBGAII" (applicable to both silicon rev. 1.0 and 2.1)</li> <li>Removed footnotes 5 and 6 from Table 1 (left over when the PCI undershoot/overshoot voltages and maximum AC waveforms were removed from Section 2.1.2, "Power Supply Voltage Specification").</li> <li>Removed SD_PLL_TPD (T2) and SD_PLL_TPA_ANA (R4) from Table 63.</li> <li>Added Section 8.3, "SGMII Interface Electrical Characteristics." Removed Section 8.5.3 SGMII DC Electrical Characteristics.</li> <li>Removed "HRESET negation to S</li></ul> |

### Table 73. Document Revision History (continued)

-

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC8313EEC Rev. 4 11/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. QorlQ is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. RapidIO is a registered trademark of the RapidIO Trade Association. IEEE 1588 and 1149.1 are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

© 2007–2011 Freescale Semiconductor, Inc.