#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 400MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (2)                                         |

| SATA                            | -                                                           |

| USB                             | USB 2.0 + PHY (1)                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | -40°C ~ 105°C (TA)                                          |

| Security Features               | -                                                           |

| Package / Case                  | 516-BBGA Exposed Pad                                        |

| Supplier Device Package         | 516-TEPBGA (27x27)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8313czqagdc |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.6 USB Dual-Role Controller

The MPC8313E USB controller includes the following features:

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

- Compatible with Universal Serial Bus Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed/high-speed PHY

# 1.7 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313E eTSECs include the following features:

- Two RGMII/SGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status

- Three-speed support (10/100/1000 Mbps)

- On-chip high-speed serial interface to external SGMII PHY interface

- Support for IEEE Std 1588<sup>TM</sup>

- Support for two full-duplex FIFO interface modes

- Multiple PHY interface configuration

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>®</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Transmission from up to eight physical queues.

- Reception to up to eight physical queues

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 1. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

| Characteristic                       |                                                                                                        | Symbol                               | Max Value                                                                    | Unit | Note |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|------|

| Core supply voltage                  |                                                                                                        | V <sub>DD</sub>                      | -0.3 to 1.26                                                                 | V    | —    |

| PLL supply volta                     | ge                                                                                                     | AV <sub>DD</sub>                     | -0.3 to 1.26                                                                 | V    |      |

| Core power supp                      | bly for SerDes transceivers                                                                            | XCOREV <sub>DD</sub>                 | -0.3 to 1.26                                                                 | V    |      |

| Pad power suppl                      | y for SerDes transceivers                                                                              | XPADV <sub>DD</sub>                  | -0.3 to 1.26                                                                 | V    | —    |

| DDR and DDR2 DRAM I/O voltage        |                                                                                                        | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                                 | V    |      |

| PCI, local bus, D<br>and JTAG I/O vo | UART, system control and power management, I <sup>2</sup> C, Itage                                     | NV <sub>DD</sub> /LV <sub>DD</sub>   | -0.3 to 3.6                                                                  | V    |      |

| eTSEC, USB                           |                                                                                                        | LV <sub>DDA</sub> /LV <sub>DDB</sub> | -0.3 to 3.6                                                                  | V    | _    |

| Input voltage                        | DDR DRAM signals                                                                                       | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | DDR DRAM reference                                                                                     | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | Enhanced three-speed Ethernet signals                                                                  | LV <sub>IN</sub>                     | -0.3 to (LV <sub>DDA</sub> + 0.3)<br>or<br>-0.3 to (LV <sub>DDB</sub> + 0.3) | V    | 4, 5 |

|                                      | Local bus, DUART, SYS_CLK_IN, system control, and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 3, 5 |

|                                      | PCI                                                                                                    | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 6    |

| Storage tempera                      | ture range                                                                                             | T <sub>STG</sub>                     | -55 to 150                                                                   | °C   | —    |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** NV<sub>IN</sub> must not exceed NV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: LV<sub>IN</sub> must not exceed LV<sub>DDA</sub>/LV<sub>DDB</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

### 2.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for the MPC8313E. Note that the values in this table are the recommended and tested operating conditions. If a particular block is given a voltage falling within the range in the Recommended Value column, the MPC8313E is capable of delivering the amount of current listed in the Current Requirement column; this is the maximum current possible. Proper device operation outside of these conditions is not guaranteed.

| Driver Type                                        | Output Impedance ( $\Omega$ ) | Supply Voltage                      |

|----------------------------------------------------|-------------------------------|-------------------------------------|

| DDR2 signal                                        | 18                            | GV <sub>DD</sub> = 1.8 V            |

| DUART, system control, I <sup>2</sup> C, JTAG, SPI | 42                            | NV <sub>DD</sub> = 3.3 V            |

| GPIO signals                                       | 42                            | NV <sub>DD</sub> = 3.3 V            |

| eTSEC signals                                      | 42                            | $LV_{DDA}$ , $LV_{DDB}$ = 2.5/3.3 V |

| USB signals                                        | 42                            | LV <sub>DDB</sub> = 2.5/3.3 V       |

Table 3. Output Drive Capability (continued)

# 2.2 Power Sequencing

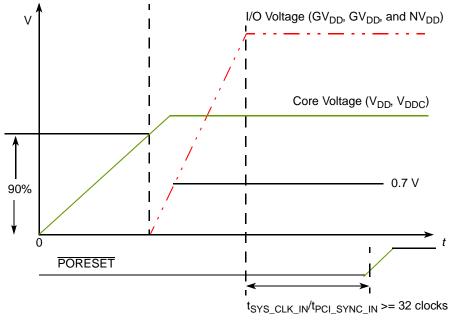

The MPC8313E does not require the core supply voltage ( $V_{DD}$  and  $V_{DDC}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) to be applied in any particular order. Note that during power ramp-up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$  and  $V_{DDC}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are stable, wait for a minimum of 32 clock cycles before negating PORESET.

Note that there is no specific power down sequence requirement for the MPC8313E. I/O voltage supplies  $(GV_{DD}, LV_{DD}, and NV_{DD})$  do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

# **3** Power Characteristics

The estimated typical power dissipation, not including I/O supply power, for this family of MPC8313E devices is shown in this table. Table 5 shows the estimated typical I/O power dissipation.

| Core Frequency<br>(MHz) | CSB Frequency<br>(MHz) | Typical <sup>2</sup> | Maximum for<br>Rev. 1.0 Silicon <sup>3</sup> | Maximum for<br>Rev. 2.x or Later Silicon <sup>3</sup> | Unit |

|-------------------------|------------------------|----------------------|----------------------------------------------|-------------------------------------------------------|------|

| 333                     | 167                    | 820                  | 1020                                         | 1200                                                  | mW   |

| 400                     | 133                    | 820                  | 1020                                         | 1200                                                  | mW   |

#### Table 4. MPC8313E Power Dissipation<sup>1</sup>

#### Note:

The values do not include I/O supply power or AV<sub>DD</sub>, but do include core, USB PLL, and a portion of SerDes digital power (not including XCOREV<sub>DD</sub>, XPADV<sub>DD</sub>, or SDAV<sub>DD</sub>, which all have dedicated power supplies for the SerDes PHY).

2. Typical power is based on a voltage of  $V_{DD}$  = 1.05 V and an artificial smoker test running at room temperature.

3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoker test.

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                                                                                                                                                                                       | Parameter           | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|--------------------------|

| DDR 1, 60% utilization,<br>50% read/write<br>$R_s = 22 \Omega$<br>$R_t = 50 \Omega$<br>single pair of clock<br>capacitive load: data = 8 pF,<br>control address = 8 pF,<br>clock = 8 pF                         | 333 MHz,<br>32 bits | _                           | 0.355                       | _                           | _                                                   | —                                                   | _                           | W    |                          |

|                                                                                                                                                                                                                 | 266 MHz,<br>32 bits | _                           | 0.323                       | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| DDR 2, 60% utilization,<br>50% read/write                                                                                                                                                                       | 333 MHz,<br>32 bits | 0.266                       | —                           | _                           | _                                                   | —                                                   | _                           | W    | —                        |

| $\begin{array}{l} R_{s} = 22 \ \Omega \\ R_{t} = 75 \ \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data} = 8 \ pF, \\ \text{control address} = 8 \ pF, \\ \text{clock} = 8 \ pF \end{array}$ | 266 MHz,<br>32 bits | 0.246                       | _                           | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| PCI I/O load = 50 pF                                                                                                                                                                                            | 33 MHz              | —                           | —                           | 0.120                       |                                                     | _                                                   | —                           | W    | —                        |

|                                                                                                                                                                                                                 | 66 MHz              |                             |                             | 0.249                       |                                                     | —                                                   | —                           | W    | —                        |

| Local bus I/O load = 20 pF                                                                                                                                                                                      | 66 MHz              |                             |                             |                             |                                                     | —                                                   | 0.056                       | W    | —                        |

|                                                                                                                                                                                                                 | 50 MHz              |                             |                             | _                           | _                                                   | —                                                   | 0.040                       | W    | _                        |

| TSEC I/O load = 20 pF                                                                                                                                                                                           | MII,<br>25 MHz      | —                           | —                           | —                           | 0.008                                               | —                                                   | —                           | W    | Multiple by<br>number of |

|                                                                                                                                                                                                                 | RGMII,<br>125 MHz   | _                           | _                           | —                           | 0.078                                               | 0.044                                               | —                           | W    | interface used           |

Table 5. MPC8313E Typical I/O Power Dissipation

# 5.2 **RESET AC Electrical Characteristics**

This table provides the reset initialization AC timing specifications.

| Parameter/Condition                                                                                                                                               | Min | Max | Unit                     | Note |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                        | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Required assertion time of PORESET with stable clock and power applied to SYS_CLK_IN when the device is in PCI host mode                                          | 32  | —   | t <sub>SYS_CLK_IN</sub>  | 2    |

| Required assertion time of PORESET with stable clock and power applied to PCI_SYNC_IN when the device is in PCI agent mode                                        | 32  | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| HRESET assertion (output)                                                                                                                                         | 512 |     | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3] and CFG_CLK_IN_DIV) with respect to negation of PORESET when the device is in PCI host mode | 4   | —   | <sup>t</sup> sys_clk_in  | 2    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input hold time for POR configuration signals with respect to negation of HRESET                                                                                  | 0   | —   | ns                       | —    |

| Time for the device to turn off POR configuration signal drivers with respect to the assertion of HRESET                                                          |     | 4   | ns                       | 3    |

| Time for the device to turn on POR configuration signal drivers with respect to the negation of $\overline{\text{HRESET}}$                                        | 1   |     | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

#### Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the

primary clock is applied to the SYS\_CLK\_IN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. 2. t<sub>SYS\_CLK\_IN</sub> is the clock period of the input clock applied to SYS\_CLK\_IN. It is only valid when the device is in PCI host mode.

POR configuration signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

This table provides the PLL lock times.

#### Table 11. PLL Lock Times

| Parameter/Condition | Min | Мах | Unit | Note |

|---------------------|-----|-----|------|------|

| PLL lock times      | _   | 100 | μs   | —    |

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface. Note that DDR SDRAM is  $GV_{DD}(typ) = 2.5 \text{ V}$  and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 \text{ V}$ .

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Max                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz,  $T_A$  = 25°C,  $V_{OUT}$  =  $GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.3                      | 2.7                      | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |      |

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

| Parameter/Condition                             | Symbol          | Min   | Мах  | Unit | Note |

|-------------------------------------------------|-----------------|-------|------|------|------|

| Output leakage current                          | I <sub>OZ</sub> | -9.9  | -9.9 | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub> | -16.2 | —    | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub> | 16.2  | _    | mA   | _    |

Note:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 15. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

#### Table 16. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Мах | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> | —   | 500 | μΑ   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

### 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM when  $GV_{DD}(typ) = 1.8 V$ .

#### Table 17. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —    |

This table provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

#### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —    |

This table provides the input AC timing specifications for the DDR2 SDRAM interface.

#### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $\text{GV}_{\text{DD}}$  of 2.5 ± 5%.

| Parameter                    | Symbol              | Min  | Мах | Unit | Note |

|------------------------------|---------------------|------|-----|------|------|

| Controller skew for MDQS—MDQ | t <sub>CISKEW</sub> | _    | —   | ps   | 1, 2 |

| 333 MHz                      |                     | -750 | 750 |      | —    |

| 266 MHz                      | _                   | -750 | 750 | _    | —    |

Notes:

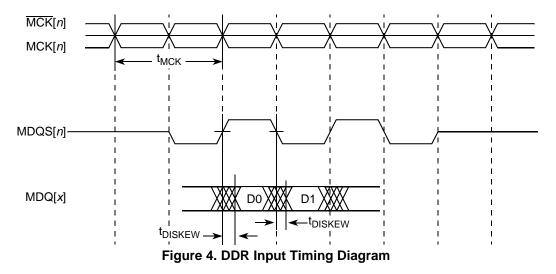

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[*n*] and any corresponding bit that is captured with MDQS[*n*]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

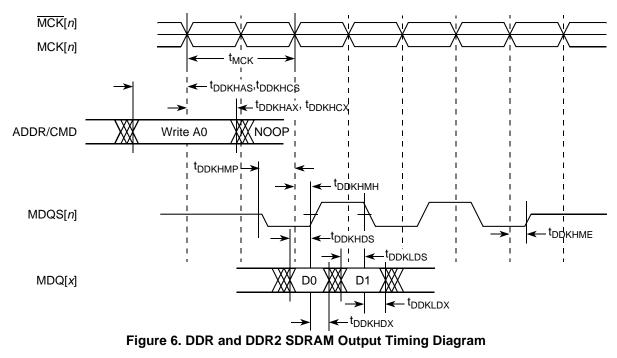

This figure illustrates the DDR input timing diagram showing the t<sub>DISKEW</sub> timing parameter.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

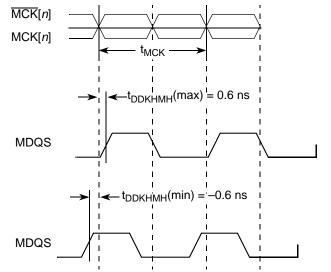

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

This figure shows the DDR and DDR2 SDRAM output timing diagram.

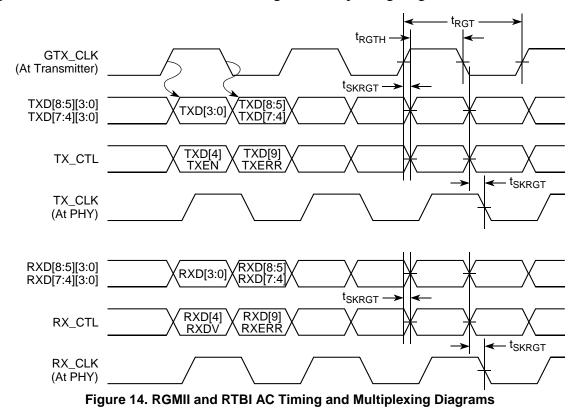

### 8.2.2 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

#### Table 30. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DDA}/LV_{DDB}$  of 2.5 V ± 5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|---------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                    | -0.5 | —   | 0.5  | ns   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                    | 1.0  | _   | 2.6  | ns   |

| Clock cycle duration <sup>3</sup>                      | t <sub>RGT</sub>                      | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4, 5</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 5</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                     | —    | _   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                     | _    | —   | 0.75 | ns   |

| GTX_CLK125 reference clock period                      | t <sub>G12</sub> <sup>6</sup>         | —    | 8.0 | —    | ns   |

| GTX_CLK125 reference clock duty cycle                  | t <sub>G125H</sub> /t <sub>G125</sub> | 47   | —   | 53   | %    |

Note:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the RTBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is  $LV_{DDA}/2$  or  $LV_{DDB}/2$ .

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. The frequency of RX\_CLK should not exceed the GTX\_CLK125 by more than 300 ppm

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

### 8.3 SGMII Interface Electrical Characteristics

Each SGMII port features a 4-wire AC-coupled serial link from the dedicated SerDes interface of MPC8313E as shown in Figure 15, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features a 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XCOREVSS. The reference circuit of the SerDes transmitter and receiver is shown in Figure 33.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines described in Section 22.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the TSEC\_GTX\_CLK125 clock is not required for this port. Instead, the SerDes reference clock is required on SD\_REF\_CLK and SD\_REF\_CLK pins.

### 8.3.1 DC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 9, "High-Speed Serial Interfaces (HSSI)."

#### 8.3.2 AC Requirements for SGMII SD REF CLK and SD REF CLK

This table lists the SGMII SerDes reference clock AC requirements. Note that SD\_REF\_CLK and SD REF CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    |     | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 8   | —   | ns   |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _   | 100 | ps   |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _   | 50  | ps   |

#### Table 31. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

#### 8.3.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 32 and Table 33 describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD TX[n] and SD\_TX[*n*]) as depicted in Figure 16.

| Parameter                                   | Symbol                            | Min                                                                    | Тур | Max                                                                    | Unit | Note                       |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------|-----|------------------------------------------------------------------------|------|----------------------------|

| Supply voltage                              | XCOREV <sub>DD</sub>              | 0.95                                                                   | 1.0 | 1.05                                                                   | V    |                            |

| Output high voltage                         | V <sub>OH</sub>                   | _                                                                      | —   | XCOREV <sub>DD-Typ</sub> /2<br>+  V <sub>OD</sub>   <sub>-max</sub> /2 | mV   | 1                          |

| Output low voltage                          | V <sub>OL</sub>                   | XCOREV <sub>DD-Typ</sub> /2<br>-  V <sub>OD</sub>   <sub>-max</sub> /2 | _   | _                                                                      | mV   | 1                          |

| Output ringing                              | V <sub>RING</sub>                 | _                                                                      | _   | 10                                                                     | %    |                            |

| Output differential voltage <sup>2, 3</sup> | V <sub>OD</sub>                   | 323                                                                    | 500 | 725                                                                    | mV   | Equalization setting: 1.0x |

| Output offset voltage                       | V <sub>OS</sub>                   | 425                                                                    | 500 | 575                                                                    | mV   | 1, 4                       |

| Output impedance<br>(single-ended)          | R <sub>O</sub>                    | 40                                                                     | _   | 60                                                                     | Ω    |                            |

| Mismatch in a pair                          | ΔR <sub>O</sub>                   | _                                                                      | _   | 10                                                                     | %    |                            |

| Change in V <sub>OD</sub> between 0 and 1   | $\Delta  V_{OD} $                 | _                                                                      | _   | 25                                                                     | mV   |                            |

| Change in V <sub>OS</sub> between 0 and 1   | $\Delta V_{OS}$                   | —                                                                      | —   | 25                                                                     | mV   |                            |

| Output current on short to GND              | I <sub>SA</sub> , I <sub>SB</sub> | _                                                                      | _   | 40                                                                     | mA   |                            |

Table 32. SGMII DC Transmitter Electrical Characteristics

#### Notes:

- 1. This will not align to DC-coupled SGMII. XCOREV<sub>DD-Typ</sub> = 1.0 V. 2.  $|V_{OD}| = |V_{TXn} V_{\overline{TXn}}|$ .  $|V_{OD}|$  is also referred as output differential peak voltage.  $V_{TX-DIFFp-p} = 2^*|V_{OD}|$ .

- 3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of XCOREV<sub>DD-Typ</sub> = 1.0 V, no common mode offset variation ( $V_{OS}$  = 500 mV), SerDes transmitter is terminated with 100- $\Omega$  differential load between TX[*n*] and TX[*n*].

- 4. V<sub>OS</sub> is also referred to as output common mode voltage.

Table 33. SGMII DC Receiver Electrical Characteristics (continued)

| Parameter                 | Symbol          | Min | Тур                   | Мах | Unit | Note |

|---------------------------|-----------------|-----|-----------------------|-----|------|------|

| Common mode input voltage | V <sub>CM</sub> | _   | V <sub>xcorevss</sub> | —   | V    | 4    |

Notes:

1. Input must be externally AC-coupled.

2.  $V_{RX\_DIFFp-p}$  is also referred to as peak to peak input differential voltage

3.  $V_{CM\_ACp-p}$  is also referred to as peak to peak AC common mode voltage.

4. On-chip termination to XCOREV<sub>SS</sub>.

### 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs  $(TX[n] \text{ and } \overline{TX}[n])$  or at the receiver inputs  $(RX[n] \text{ and } \overline{RX}[n])$  as depicted in Figure 18, respectively.

### 8.3.4.1 SGMII Transmit AC Timing Specifications

This table provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 34. SGMII Transmit AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                           | Symbol            | Min    | Тур | Мах    | Unit   | Note |

|-------------------------------------|-------------------|--------|-----|--------|--------|------|

| Deterministic jitter                | JD                | _      | _   | 0.17   | UI p-p |      |

| Total jitter                        | JT                | —      | _   | 0.35   | UI p-p |      |

| Unit interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1    |

| V <sub>OD</sub> fall time (80%–20%) | tfall             | 50     | _   | 120    | ps     |      |

| V <sub>OD</sub> rise time (20%–80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     |      |

Note:

1. Each UI is 800 ps  $\pm$  100 ppm.

### 8.3.4.2 SGMII Receive AC Timing Specifications

This table provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 17 shows the SGMII receiver input compliance mask eye diagram.

#### Table 35. SGMII Receive AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                                          | Symbol | Min  | Тур | Max | Unit   | Note |

|----------------------------------------------------|--------|------|-----|-----|--------|------|

| Deterministic jitter tolerance                     | JD     | 0.37 | —   | —   | UI p-p | 1    |

| Combined deterministic and random jitter tolerance | JDR    | 0.55 | —   | —   | UI p-p | 1    |

| Sinusoidal jitter tolerance                        | JSIN   | 0.1  | —   | —   | UI p-p | 1    |

#### Table 49. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 48).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                  | Max                  | Unit |

|---------------------------------------------------------------------------------|---------------------|----------------------|----------------------|------|

| Data hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices      | t <sub>i2DXKL</sub> | $\overline{0^2}$     | <br>0.9 <sup>3</sup> | μs   |

| Fall time of both SDA and SCL signals <sup>5</sup>                              | t <sub>I2CF</sub>   | —                    | 300                  | ns   |

| Setup time for STOP condition                                                   | t <sub>I2PVKH</sub> | 0.6                  | _                    | μs   |

| Bus free time between a STOP and START condition                                | t <sub>I2KHDX</sub> | 1.3                  | _                    | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)  | V <sub>NL</sub>     | $0.1 \times NV_{DD}$ | —                    | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times NV_{DD}$ | —                    | V    |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the bigh (H) state or hold time. Also, t<sub>12PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- The MPC8313E provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum  $t_{12DVKH}$  has only to be met if the device does not stretch the LOW period ( $t_{12CL}$ ) of the SCL signal.

- 4.  $C_B$  = capacitance of one bus line in pF.

- 5. The MPC8313E does not follow the  $l^2C$ -BUS Specifications, Version 2.1, regarding the t<sub>I2CF</sub> AC parameter.

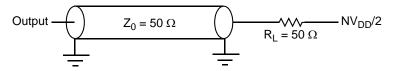

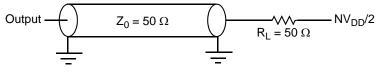

This figure provides the AC test load for the  $I^2C$ .

Figure 46. I<sup>2</sup>C AC Test Load

### **15.2 Timers AC Timing Specifications**

This table provides the Timers input and output AC timing specifications.

Table 54. Timers Input AC Timing Specifications<sup>1</sup>

| Characteristic                    | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLK\_IN. Timings are measured at the pin.

2. Timers inputs and outputs are asynchronous to any visible clock. Timers outputs should be synchronized before use by any external synchronous logic. Timers inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation

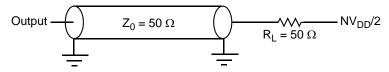

This figure provides the AC test load for the Timers.

Figure 51. Timers AC Test Load

# 16 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

### **16.1 GPIO DC Electrical Characteristics**

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 3.3-V supply.

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA       | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μΑ   |

Table 55. GPIO (When Operating at 3.3 V) DC Electrical Characteristics

Note:

1. This specification only applies to GPIO pins that are operating from a 3.3-V supply. See Table 62 for the power supply listed for the individual GPIO signal.

This table provides the DC electrical characteristics for the GPIO when the GPIO pins are operating from a 2.5-V supply.

| Parameters           | Symbol           | Conditions                         |                        | Min            | Мах                    | Unit |

|----------------------|------------------|------------------------------------|------------------------|----------------|------------------------|------|

| Supply voltage 2.5 V | NV <sub>DD</sub> | —                                  |                        | 2.37           | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA          | NV <sub>DD</sub> = min | 2.00           | NV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA           | NV <sub>DD</sub> = min | $V_{SS} - 0.3$ | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                                  | NV <sub>DD</sub> = min | 1.7            | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                  | NV <sub>DD</sub> = min | -0.3           | 0.70                   | V    |

| Input high current   | IIH              | V <sub>IN</sub> = NV <sub>DD</sub> |                        | —              | 10                     | μΑ   |

| Input low current    | ۱ <sub>IL</sub>  | $V_{IN} = V_{SS}$                  |                        | -15            | —                      | μA   |

| Table 56. GPIO (When Operating at 2.5 V) DC Electrical Characteristics |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Note:

1. This specification only applies to GPIO pins that are operating from a 2.5-V supply. See Table 62 for the power supply listed for the individual GPIO signal

# 16.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS\_CLKIN. Timings are measured at the pin.

2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

This figure provides the AC test load for the GPIO.

Figure 52. GPIO AC Test Load

#### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                                           | Package Pin Number                                                                                                     | Pin Type                                                      | Power<br>Supply  | Note |  |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------|--|--|--|--|

| SPI                                              |                                                                                                                        |                                                               |                  |      |  |  |  |  |

| SPIMOSI/GTM1_TIN3/GTM2_TIN4/GPIO28/LSRCID4       | H1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | —    |  |  |  |  |

| SPIMISO/GTM1_TGATE3/GTM2_TGATE4/GPIO29/<br>LDVAL | H3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | _    |  |  |  |  |

| SPICLK/GTM1_TOUT3/GPIO30                         | G1                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | _    |  |  |  |  |

| SPISEL/GPIO31                                    | G3                                                                                                                     | I/O                                                           | NV <sub>DD</sub> | _    |  |  |  |  |

| Power                                            | and Ground Supplies                                                                                                    |                                                               | 1 1              |      |  |  |  |  |

| AV <sub>DD1</sub>                                | F14                                                                                                                    | Power for e300 core<br>APLL<br>(1.0 V)                        | —                | _    |  |  |  |  |

| AV <sub>DD2</sub>                                | P21                                                                                                                    | Power for system<br>APLL (1.0 V)                              | —                | —    |  |  |  |  |

| GV <sub>DD</sub>                                 | A2,A3,A4,A24,A25,B3,<br>B4,B5,B12,B13,B20,B21,<br>B24,B25,B26,D1,D2,D8,<br>D9,D16,D17                                  | Power for DDR1<br>and DDR2 DRAM<br>I/O voltage<br>(1.8/2.5 V) | —                | _    |  |  |  |  |

| LV <sub>DD</sub>                                 | D24,D25,G23,H23,R23,<br>T23,W25,Y25,AA22,AC23                                                                          | Power for local bus<br>(3.3 V)                                | —                | —    |  |  |  |  |

| LV <sub>DDA</sub>                                | W2,Y2                                                                                                                  | Power for eTSEC2<br>(2.5 V, 3.3 V)                            | —                |      |  |  |  |  |

| LV <sub>DDB</sub>                                | AC8,AC9,AE4,AE5                                                                                                        | Power for eTSEC1/<br>USB DR<br>(2.5 V, 3.3 V)                 | —                |      |  |  |  |  |

| MV <sub>REF</sub>                                | C14,D14                                                                                                                | Reference voltage signal for DDR                              | —                | —    |  |  |  |  |

| NV <sub>DD</sub>                                 | G4,H4,L2,M2,AC16,AC17,<br>AD25,AD26,AE12,AE13,<br>AE20,AE21,AE24,AE25,<br>AE26,AF24,AF25                               | Standard I/O<br>voltage (3.3 V)                               | —                | _    |  |  |  |  |

| V <sub>DD</sub>                                  | K11,K12,K13,K14,K15,<br>K16,L10,L17,M10,M17,<br>N10,N17,U12,U13,                                                       | Power for core (1.0<br>V)                                     | —                | _    |  |  |  |  |

| V <sub>DDC</sub>                                 | F6,F10,F19,K6,K10,K17,<br>K21,P6,P10,P17,R10,R17,<br>T10,T17,U10,U11,U14,<br>U15,U16,U17,W6,W21,<br>AA6,AA10,AA14,AA19 | Internal core logic<br>constant power (1.0<br>V)              | —                | _    |  |  |  |  |

Table 69. Package Thermal Characteristics for TEPBGAII (continued)

| Characteristic          | Board Type         | Symbol              | TEPBGA II | Unit | Note |

|-------------------------|--------------------|---------------------|-----------|------|------|

| Junction-to-case        | _                  | $R_{	ext{	heta}JC}$ | 8         | °C/W | 5    |

| Junction-to-package top | Natural convection | $\Psi_{JT}$         | 7         | °C/W | 6    |

Note:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 21.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$ , where  $P_{I/O}$  is the power dissipation of the I/O drivers.

### 21.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. As a general statement, the value obtained on a single layer board is appropriate for a tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

# 21.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction-to-ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

| Heat Sink Assuming Thermal Grease                | Airflow            | Thermal Resistance<br>(°C/W) |

|--------------------------------------------------|--------------------|------------------------------|

| Wakefield 53 $\times$ 53 $\times$ 2.5 mm pin fin | Natural convection | 13.0                         |

|                                                  | 0.5 m/s            | 10.6                         |

|                                                  | 1 m/s              | 9.7                          |

|                                                  | 2 m/s              | 9.2                          |

|                                                  | 4 m/s              | 8.9                          |

| Aavid 35 $\times~$ 31 $\times$ 23 mm pin fin     | Natural convection | 14.4                         |

|                                                  | 0.5 m/s            | 11.3                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.9                          |

|                                                  | 4 m/s              | 9.4                          |

| Aavid $30 \times 30 \times 9.4$ mm pin fin       | Natural convection | 16.5                         |

|                                                  | 0.5 m/s            | 13.5                         |

|                                                  | 1 m/s              | 12.1                         |

|                                                  | 2 m/s              | 10.9                         |

|                                                  | 4 m/s              | 10.0                         |

| Aavid $43 \times 41 \times 16.5$ mm pin fin      | Natural convection | 14.5                         |

|                                                  | 0.5 m/s            | 11.7                         |

|                                                  | 1 m/s              | 10.5                         |

|                                                  | 2 m/s              | 9.7                          |

|                                                  | 4 m/s              | 9.2                          |

Table 70. Thermal Resistance for TEPBGAII with Heat Sink in Open Flow

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in Table 70. More detailed thermal models can be made available on request.

#### Notes:

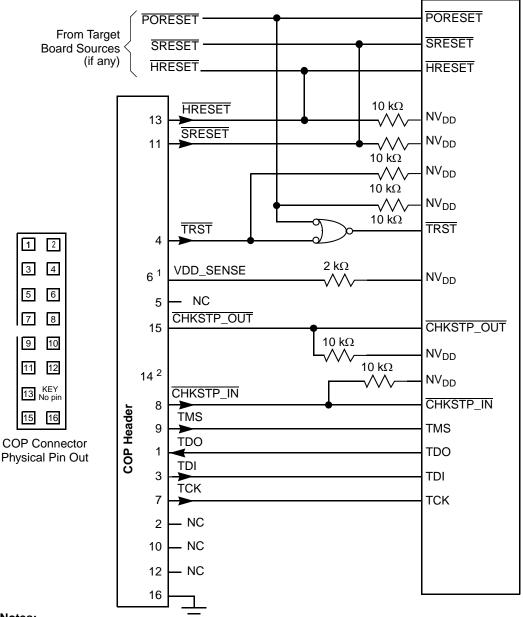

Some systems require power to be fed from the application board into the debugger repeater card via the COP header. In this case the resistor value for VDD\_SENSE should be around 20 Ω.

Key location; pin 14 is not physically present on the COP header.

Figure 61. JTAG Interface Connection

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."