# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 267MHz                                                                 |

| Co-Processors/DSP               | Security; SEC 2.2                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography                                                           |

| Package / Case                  | 516-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 516-TEPBGA (27x27)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8313ezqaddc |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.6 USB Dual-Role Controller

The MPC8313E USB controller includes the following features:

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

- Compatible with Universal Serial Bus Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed/high-speed PHY

# 1.7 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313E eTSECs include the following features:

- Two RGMII/SGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status

- Three-speed support (10/100/1000 Mbps)

- On-chip high-speed serial interface to external SGMII PHY interface

- Support for IEEE Std 1588<sup>TM</sup>

- Support for two full-duplex FIFO interface modes

- Multiple PHY interface configuration

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>®</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Transmission from up to eight physical queues.

- Reception to up to eight physical queues

- Full and half-duplex Ethernet support (1000 Mbps supports only full-duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE 802.1 virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound packets

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

# **1.8 Programmable Interrupt Controller (PIC)**

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model supports 5 external and 34 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

# 1.9 Power Management Controller (PMC)

The MPC8313E power management controller includes the following features:

- Provides power management when the device is used in both host and agent modes

- Supports PCI power management 1.2 D0, D1, D2, D3hot, and D3cold states

- On-chip split power supply controlled through external power switch for minimum standby power

- Support for PME generation in PCI agent mode, PME detection in PCI host mode

- Supports wake-up from Ethernet (Magic Packet), USB, GPIO, and PCI (PME input as host)

| Characteristic                                    | Symbol                                      | Recommended Value <sup>1</sup>                                                                                                               | Unit | Current<br>Requirement |

|---------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|

| Core supply voltage                               | V <sub>DD</sub>                             | 1.0 V ± 50 mV                                                                                                                                | V    | 469 mA                 |

| Internal core logic constant power                | V <sub>DDC</sub>                            | 1.0 V ± 50 mV                                                                                                                                | V    | 377 mA                 |

| SerDes internal digital power                     | XCOREV <sub>DD</sub>                        | 1.0                                                                                                                                          | V    | 170 mA                 |

| SerDes internal digital ground                    | XCOREV <sub>SS</sub>                        | 0.0                                                                                                                                          | V    | —                      |

| SerDes I/O digital power                          | XPADV <sub>DD</sub>                         | 1.0                                                                                                                                          | V    | 10 mA                  |

| SerDes I/O digital ground                         | XPADV <sub>SS</sub>                         | 0.0                                                                                                                                          | V    | —                      |

| SerDes analog power for PLL                       | SDAV <sub>DD</sub>                          | 1.0 V ± 50 mV                                                                                                                                | V    | 10 mA                  |

| SerDes analog ground for PLL                      | SDAV <sub>SS</sub>                          | 0.0                                                                                                                                          | V    | —                      |

| Dedicated 3.3 V analog power for USB PLL          | USB_PLL_PWR3                                | 3.3 V ± 300 mV                                                                                                                               | V    | 2–3 mA                 |

| Dedicated 1.0 V analog power for USB PLL          | USB_PLL_PWR1                                | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Dedicated analog ground for USB PLL               | USB_PLL_GND                                 | 0.0                                                                                                                                          | V    | —                      |

| Dedicated USB power for USB bias circuit          | USB_VDDA_BIAS                               | 3.3 V ± 300 mV                                                                                                                               | V    | 4–5 mA                 |

| Dedicated USB ground for USB bias circuit         | USB_VSSA_BIAS                               | 0.0                                                                                                                                          | V    | —                      |

| Dedicated power for USB transceiver               | USB_VDDA                                    | 3.3 V ± 300 mV                                                                                                                               | V    | 75 mA                  |

| Dedicated ground for USB transceiver              | USB_VSSA                                    | 0.0                                                                                                                                          | V    | —                      |

| Analog power for e300 core APLL                   | AV <sub>DD1</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Analog power for system APLL                      | AV <sub>DD2</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| DDR1 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 2.5 V ± 125 mV                                                                                                                               | V    | 131 mA                 |

| DDR2 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 1.8 V ± 80 mV                                                                                                                                | V    | 140 mA                 |

| Differential reference voltage for DDR controller | MV <sub>REF</sub>                           | $\begin{array}{c} 1/2 \text{ DDR supply} \\ (0.49 \times \text{GV}_{\text{DD}} \text{ to} \\ 0.51 \times \text{GV}_{\text{DD}}) \end{array}$ | V    | _                      |

| Standard I/O voltage                              | NV <sub>DD</sub>                            | $3.3 \text{ V} \pm 300 \text{ mV}^2$                                                                                                         | V    | 74 mA                  |

| eTSEC2 I/O supply                                 | LV <sub>DDA</sub>                           | 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                                            | V    | 22 mA                  |

| eTSEC1/USB DR I/O supply                          | LV <sub>DDB</sub>                           | LV <sub>DDB</sub> 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                          |      | 44 mA                  |

| Supply for eLBC IOs                               | LV <sub>DD</sub>                            | 3.3 V ± 300 mV V                                                                                                                             |      | 16 mA                  |

| Analog and digital ground                         | V <sub>SS</sub>                             | 0.0                                                                                                                                          | V    | —                      |

| Junction temperature range                        | T <sub>A</sub> /T <sub>J</sub> <sup>3</sup> | 0 to 105                                                                                                                                     | °C   |                        |

### Table 2. Recommended Operating Conditions

# 4.2 AC Electrical Characteristics

The primary clock source for the MPC8313E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the system clock input (SYS\_CLK\_IN/PCI\_CLK) AC timing specifications for the MPC8313E.

| Parameter/Condition           | Symbol                                    | Min | Тур | Max   | Unit | Note |

|-------------------------------|-------------------------------------------|-----|-----|-------|------|------|

| SYS_CLK_IN/PCI_CLK frequency  | f <sub>SYS_CLK_IN</sub>                   | 24  | _   | 66.67 | MHz  | 1    |

| SYS_CLK_IN/PCI_CLK cycle time | t <sub>SYS_CLK_IN</sub>                   | 15  | —   | _     | ns   | —    |

| SYS_CLK_IN rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>         | 0.6 | 0.8 | 4     | ns   | 2    |

| PCI_CLK rise and fall time    | t <sub>PCH</sub> , t <sub>PCL</sub>       | 0.6 | 0.8 | 1.2   | ns   | 2    |

| SYS_CLK_IN/PCI_CLK duty cycle | t <sub>KHK</sub> /t <sub>SYS_CLK_IN</sub> | 40  | —   | 60    | %    | 3    |

| SYS_CLK_IN/PCI_CLK jitter     | _                                         | _   | _   | ±150  | ps   | 4, 5 |

### Table 8. SYS\_CLK\_IN AC Timing Specifications

Notes:

1. Caution: The system, core, security block must not exceed their respective maximum or minimum operating frequencies.

2. Rise and fall times for SYS\_CLK\_IN/PCI\_CLK are measured at 0.4 and 2.4 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter-short term and long term-and is guaranteed by design.

5. The SYS\_CLK\_IN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYS\_CLK\_IN drivers with the specified jitter.

# 5 **RESET** Initialization

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8313E.

# 5.1 **RESET DC Electrical Characteristics**

This table provides the DC electrical characteristics for the RESET pins.

| Table 9. | RESET Pins | <b>DC Electrical</b> | Characteristics |

|----------|------------|----------------------|-----------------|

|----------|------------|----------------------|-----------------|

| Characteristic      | Symbol          | Condition                                            | Min  | Max                    | Unit |

|---------------------|-----------------|------------------------------------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                                                    | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                                    | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{IN} \leq \text{NV}_{DD}$ | —    | ±5                     | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA                            | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                             | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                             | —    | 0.4                    | V    |

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Max                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz,  $T_A$  = 25°C,  $V_{OUT}$  =  $GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.3                      | 2.7                      | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |      |

| Parameter                                                            | Symbol <sup>1</sup>                         | Min                             | Мах                         | Unit | Note |

|----------------------------------------------------------------------|---------------------------------------------|---------------------------------|-----------------------------|------|------|

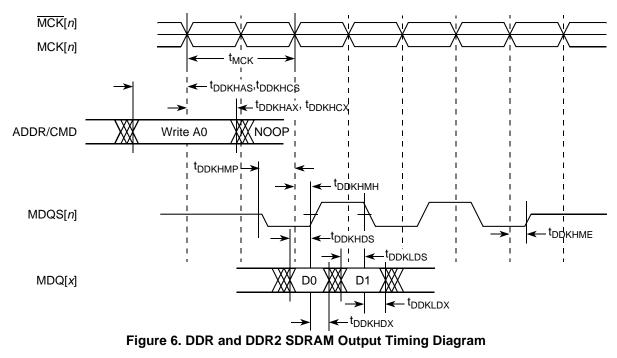

| MCK[ <i>n</i> ] cycle time, MCK[ <i>n</i> ]/MCK[ <i>n</i> ] crossing | t <sub>MCK</sub>                            | 6                               | 10                          | ns   | 2    |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz      | t <sub>DDKHAS</sub>                         | 2.1<br>2.5                      |                             | ns   | 3    |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz       | t <sub>DDKHAX</sub>                         | 2.0<br>2.7                      |                             | ns   | 3    |

| MCS[n] output setup with respect to MCK<br>333 MHz<br>266 MHz        | t <sub>DDKHCS</sub>                         | 2.1<br>3.15                     |                             | ns   | 3    |

| MCS[n] output hold with respect to MCK<br>333 MHz<br>266 MHz         | t <sub>DDKHCX</sub>                         | 2.0<br>2.7                      |                             | ns   | 3    |

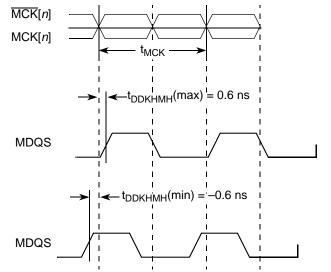

| MCK to MDQS Skew                                                     | t <sub>DDKHMH</sub>                         | -0.6                            | 0.6                         | ns   | 4    |

| MDQ//MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz  | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 800<br>900                      |                             | ps   | 5    |

| MDQ//MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz      | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> | 750<br>1000                     | _                           | ps   | 5    |

| MDQS preamble start                                                  | t <sub>DDKHMP</sub>                         | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 \times t_{MCK}$ + 0.6 | ns   | 6    |

| MDQS epilogue end                                                    | t <sub>DDKHME</sub>                         | -0.6                            | 0.6                         | ns   | 6    |

### Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Silicon Rev 2.x or Later

### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ//MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

This figure shows the DDR and DDR2 SDRAM output timing diagram.

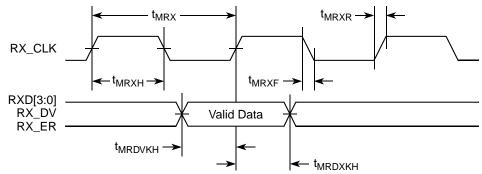

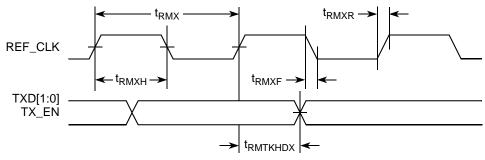

This figure shows the MII receive AC timing diagram.

Figure 10. MII Receive AC Timing Diagram RMII AC Timing Specifications

### 8.2.1.3 RMII Transmit AC Timing Specifications

This table provides the RMII transmit AC timing specifications.

### Table 28. RMII Transmit AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock                                          | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                     | t <sub>RMXH/</sub> t <sub>RMX</sub> | 35  | _   | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay             | t <sub>RMTKHDX</sub>                | 2   | _   | 10  | ns   |

| REF_CLK data clock rise $V_{IL}(min)$ to $V_{IH}(max)$ | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>RMXF</sub>                   | 1.0 | _   | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

This figure shows the RMII transmit AC timing diagram.

Figure 11. RMII Transmit AC Timing Diagram

### Table 37. MII Management DC Electrical Characteristics When Powered at 3.3 V (continued)

### Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the NV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

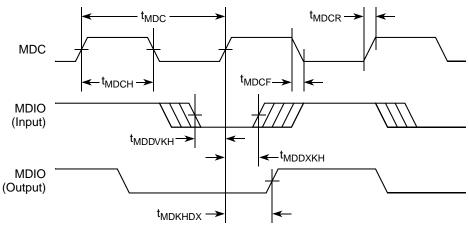

### 8.5.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

### Table 38. MII Management AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> is  $3.3 \text{ V} \pm 0.3 \text{V}$

| Parameter/Condition        | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Note |

|----------------------------|---------------------|-----|-----|-----|------|------|

| MDC frequency              | f <sub>MDC</sub>    | _   | 2.5 | _   | MHz  | 2    |

| MDC period                 | t <sub>MDC</sub>    | _   | 400 | —   | ns   |      |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32  | —   | —   | ns   |      |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10  | —   | 170 | ns   |      |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5   | —   | —   | ns   |      |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0   | —   | —   | ns   |      |

| MDC rise time              | t <sub>MDCR</sub>   | _   | —   | 10  | ns   |      |

| MDC fall time              | t <sub>MDHF</sub>   | _   | —   | 10  | ns   |      |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

2. This parameter is dependent on the csb\_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC\_MDC.)

This figure shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

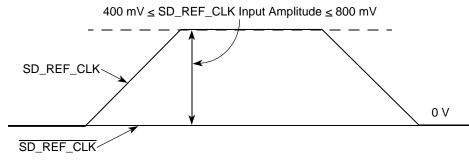

Figure 25. Differential Reference Clock Input DC Requirements (External AC-Coupled)

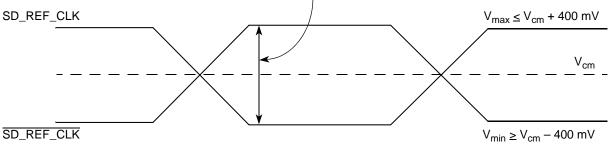

### 9.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to XCOREV<sub>SS</sub>, the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC coupled.

- Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce a signal with too large of an amplitude and may need to be DC-biased at the clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC coupling.

### NOTE

Figure 27 through Figure 30 are for conceptual reference only. Due to the fact that the clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is possible that the clock circuit reference designs provided by clock driver chip vendors are different from what is shown in the figures. They might also vary from one vendor to the other. Therefore, Freescale can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. It is recommended that the system designer contact the selected clock driver chip vendor for the optimal reference circuits for the MPC8313E SerDes reference clock receiver requirement provided in this document.

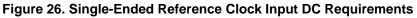

### 10.2 On-Chip USB PHY

This section describes the DC and AC electrical specifications for the on-chip USB PHY of the MPC8313E. See Chapter 7 in the USB Specifications Rev. 2, for more information.

This table provides the USB clock input (USB\_CLK\_IN) DC timing specifications.

| Parameter          | Symbol          | Min  | Мах                    | Unit |

|--------------------|-----------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | 2.7  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

This table provides the USB clock input (USB\_CLK\_IN) AC timing specifications.

| Table 43. USB | CLK_IN | I AC Timing | Specifications |

|---------------|--------|-------------|----------------|

|---------------|--------|-------------|----------------|

| Parameter/Condition                       | Conditions                                                                            | Symbol                  | Min    | Тур | Max   | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------|-------------------------|--------|-----|-------|------|

| Frequency range                           | _                                                                                     | f <sub>USB_CLK_IN</sub> | —      | 24  | 48    | MHz  |

| Clock frequency tolerance                 | _                                                                                     | <sup>t</sup> CLK_TOL    | -0.005 | 0   | 0.005 | %    |

| Reference clock duty cycle                | Measured at 1.6 V                                                                     | t <sub>CLK_DUTY</sub>   | 40     | 50  | 60    | %    |

| Total input jitter/time interval<br>error | Peak-to-peak value measured with a second order high-pass filter of 500 kHz bandwidth | t <sub>CLK_PJ</sub>     | —      | _   | 200   | ps   |

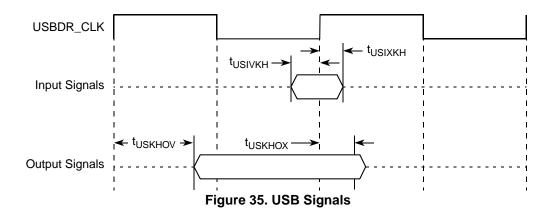

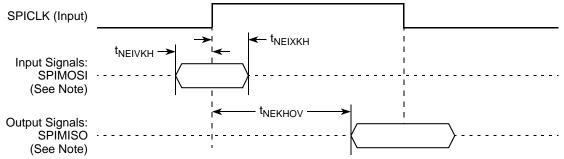

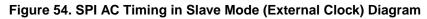

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

This figure shows the SPI timing in master mode (internal clock).

Figure 55. SPI AC Timing in Master Mode (Internal Clock) Diagram

# 19 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8313E is available in a thermally enhanced plastic ball grid array (TEPBGAII), see Section 19.1, "Package Parameters for the MPC8313E TEPBGAII," and Section 19.2, "Mechanical Dimensions of the MPC8313E TEPBGAII," for information on the TEPBGAII.

# 19.1 Package Parameters for the MPC8313E TEPBGAII

The package parameters are as provided in the following list. The package type is 27 mm  $\times$  27 mm, 516 TEPBGAII.

| Package outline         | $27 \text{ mm} \times 27 \text{ mm}$                  |

|-------------------------|-------------------------------------------------------|

| Interconnects           | 516                                                   |

| Pitch                   | 1.00 mm                                               |

| Module height (typical) | 2.25 mm                                               |

| Solder Balls            | 96.5 Sn/3.5 Ag(VR package),                           |

|                         | 62 Sn/36 Pb/2 Ag (ZQ package) Ball diameter (typical) |

| 0.6 mm                  |                                                       |

| Signal     | Package Pin Number             | Pin Type | Power<br>Supply  | Note |  |

|------------|--------------------------------|----------|------------------|------|--|

| MEMC_MCS0  | D10                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MCS1  | A10                            | 0        | GV <sub>DD</sub> | _    |  |

| MEMC_MCKE  | B14                            | 0        | GV <sub>DD</sub> | 3    |  |

| MEMC_MCK   | A13                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MCK   | A14                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MODT0 | B23                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MODT1 | C23                            | 0        | GV <sub>DD</sub> |      |  |

|            | Local Bus Controller Interface |          |                  |      |  |

| LAD0       | K25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD1       | K24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD2       | K23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD3       | K22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD4       | J25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD5       | J24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD6       | J23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD7       | J22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD8       | H24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD9       | F26                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD10      | G24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD11      | F25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD12      | E25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD13      | F24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD14      | G22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD15      | F23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LA16       | AC25                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA17       | AC26                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA18       | AB22                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA19       | AB23                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA20       | AB24                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA21       | AB25                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA22       | AB26                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA23       | E22                            | 0        | LV <sub>DD</sub> | 11   |  |

| Signal                                             | Package Pin Number | Pin Type | Power<br>Supply  | Note                     |  |

|----------------------------------------------------|--------------------|----------|------------------|--------------------------|--|

| RXB                                                | R1                 | I        |                  |                          |  |

| RXB                                                | P1                 | I        |                  | _                        |  |

| SD_IMP_CAL_RX                                      | V5                 | I        |                  | 200 Ω ±<br>10% to<br>GND |  |

| SD_REF_CLK                                         | T5                 | I        |                  | _                        |  |

| SD_REF_CLK                                         | T4                 | I        |                  |                          |  |

| SD_PLL_TPD                                         | T2                 | 0        |                  |                          |  |

| SD_IMP_CAL_TX                                      | N5                 | I        |                  | 100 Ω ±<br>10% to<br>GND |  |

| SDAVDD                                             | R5                 | I/O      |                  | —                        |  |

| SD_PLL_TPA_ANA                                     | R4                 | 0        |                  | —                        |  |

| SDAVSS                                             | R3                 | I/O      |                  | —                        |  |

|                                                    | USB PHY            |          |                  |                          |  |

| USB_DP                                             | P26                | I/O      |                  |                          |  |

| USB_DM                                             | N26                | I/O      |                  | _                        |  |

| USB_VBUS                                           | P24                | I/O      |                  | _                        |  |

| USB_TPA                                            | L26                | I/O      |                  | —                        |  |

| USB_RBIAS                                          | M24                | I/O      |                  | _                        |  |

| USB_PLL_PWR3                                       | M26                | I/O      |                  | —                        |  |

| USB_PLL_GND                                        | N24                | I/O      |                  | —                        |  |

| USB_PLL_PWR1                                       | N25                | I/O      |                  | —                        |  |

| USB_VSSA_BIAS                                      | M25                | I/O      |                  | —                        |  |

| USB_VDDA_BIAS                                      | M22                | I/O      |                  | _                        |  |

| USB_VSSA                                           | N22                | I/O      |                  | _                        |  |

| USB_VDDA                                           | P22                | I/O      |                  | —                        |  |

|                                                    | GTM/USB            | I        |                  |                          |  |

| USBDR_DRIVE_VBUS/GTM1_TIN1/GTM2_TIN2/LSRCID0       | AD23               | I/O      | NV <sub>DD</sub> |                          |  |

| USBDR_PWRFAULT/GTM1_TGATE1/GTM2_TGATE2/<br>LSRCID1 | AE23               | I/O      | NV <sub>DD</sub> | —                        |  |

| USBDR_PCTL0/GTM1_TOUT1/LSRCID2                     | AC22               | 0        | NV <sub>DD</sub> | —                        |  |

| USBDR_PCTL1/LBC_PM_REF_10/LSRCID3                  | AB21               | 0        | $NV_{DD}$        | —                        |  |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

The primary clock source for the MPC8313E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the device is configured as a PCI host device, SYS\_CLK\_IN is its primary input clock. SYS\_CLK\_IN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether SYS\_CLK\_IN or SYS\_CLK\_IN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCICOEn] parameters select whether the PCI\_SYNC\_OUT is driven out on the PCI\_CLK\_OUTn signals.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the device to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock. When the device is configured as a PCI agent device the SYS\_CLK\_IN signal should be tied to VSS.

As shown in Figure 57, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create the coherent system bus clock ( $csb\_clk$ ), the internal clock for the DDR controller ( $ddr\_clk$ ), and the internal clock for the local bus interface unit ( $lbc\_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$$csb_clk = \{PCI_SYNC_IN \times (1 + \sim \overline{CFG_CLKIN_DIV})\} \times SPMF$$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 +  $\sim$ CFG\_CLKIN\_DIV) is the SYS\_CLK\_IN frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies up the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See Chapter 4, "Reset, Clocking, and Initialization," in the *MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual*, for more information on the clock subsystem.

The internal *ddr\_clk* frequency is determined by the following equation:

$ddr_clk = csb_clk \times (1 + RCWL[DDRCM])$

Note that  $ddr_clk$  is not the external memory bus frequency;  $ddr_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the same frequency as  $ddr_clk$ .

The internal *lbc\_clk* frequency is determined by the following equation:

$lbc\_clk = csb\_clk \times (1 + \text{RCWL[LBCM]})$

Note that *lbc\_clk* is not the external local bus frequency; *lbc\_clk* passes through the a LBC clock divider to create the external local bus clock outputs (LCLK[0:1]). The LBC clock divider ratio is controlled by LCRR[CLKDIV].

In addition, some of the internal units may be required to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. Table 63 specifies which units have a configurable clock frequency.

• Third, between the device and any SerDes voltage regulator there should be a  $10-\mu$ F, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a  $100-\mu$ F, low ESR SMT tantalum chip capacitor. This should be done for all SerDes supplies.

# 22.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ , or  $LV_{DDB}$  as required. Unused active high inputs should be connected to  $V_{SS}$ . All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ ,  $LV_{DDB}$ , and  $V_{SS}$  pins of the device.

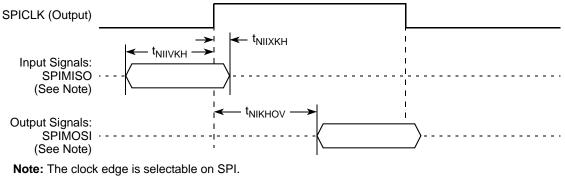

# 22.6 Output Buffer DC Impedance

The MPC8313E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $NV_{DD}$  or  $V_{SS}$ . Then, the value of each resistor is varied until the pad voltage is  $NV_{DD}/2$  (see Figure 60). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open), and  $R_p$  is trimmed until the voltage at the pad equals  $NV_{DD}/2$ .  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_p + R_N)/2$ .

Figure 60. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

### Notes:

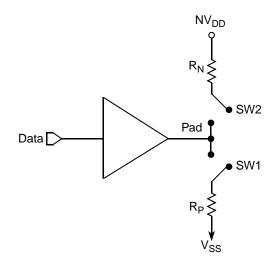

Some systems require power to be fed from the application board into the debugger repeater card via the COP header. In this case the resistor value for VDD\_SENSE should be around 20 Ω.

Key location; pin 14 is not physically present on the COP header.

Figure 61. JTAG Interface Connection

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

# 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8313E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | е                                       | t                                       | рр                                              | aa                                           | а                          | X                                            |

|-----------------|--------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------|----------------------------------------------|----------------------------|----------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range <sup>3</sup>       | Package <sup>1, 4</sup>                         | e300 core<br>Frequency <sup>2</sup>          | DDR<br>Frequency           | Revision<br>Level                            |

| MPC             | 8313               | Blank = Not<br>included<br>E = included | Blank = 0° to 105°C<br>C= -40° to 105°C | ZQ = PB<br>TEPBGAII<br>VR = PB free<br>TEPBGAII | AD = 266 MHz<br>AF = 333 MHz<br>AG = 400 MHz | D = 266 MHz<br>F = 333 MHz | Blank = 1.0<br>A = 2.0<br>B = 2.1<br>C = 2.2 |

### Table 72. Part Numbering Nomenclature

Note:

1. See Section 19, "Package and Pin Listings," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

- 3. Contact local Freescale office on availability of parts with °C temperature range.

- 4. ZQ package was available for Rev 1.0. For Rev 2.x, only VR package is available.

### 23.2 Part Marking

Parts are marked as shown in this figure.

Notes:

MPCnnnnetppaar is the orderable part number. ATWLYYWW is the standard assembly, test, year, and work week codes. CCCCC is the country code. MMMMM is the mask number.

Figure 62. Part Marking for TEPBGAII Device

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>In Table 63, added LBC_PM_REF_10 &amp; LSRCID3 as muxed with USBDR_PCTL1</li> <li>In Table 63, added LSRCID2 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL2 VBUS</li> <li>In Table 63, moved 71, U2,&amp; V2 from V<sub>DD</sub> to XCOREVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; V4 from V<sub>SS</sub> to XCOREVDS.</li> <li>In Table 63, added impedance control requirements for SD_IMP_CAL_TX (100 ohms to GND) and SD_IMP_CAL_RX (200 ohms to GND).</li> <li>In Table 63, updated muxing in pinout to show new options for selecting IEEE 1588 functionality. Added footnote 8</li> <li>In Table 63, updated muxing in pinout to show new LBC ECC boot enable control muxed with eTSEC1_MDC</li> <li>Added pin type information for power supplies.</li> <li>Removed N1 and N3 from Vss section of Table 63. Added Therm0 and Therm1 (N1 and N3, respectively). Added note 7 to state: "Internal thermally sensitive resistor, resistor value varies linearly with temperature."</li> <li>In Table 65 corrected maximum frequency of Local Bus Frequency from "33–66" to 66 MHz</li> <li>In Table 65 corrected maximum frequency of PCI from "24–66" to 66 MHz</li> <li>Added "which is determined by RCWLR[COREPLL]" to the note in Section 20.2, "Core PLL Configuration" about the VCO divider.</li> <li>Added "Walues.</li> <li>In Table 69, notes were confusing. Added note 3 for VCO column, note 4 for CSB (<i>csb_c.clk</i>) column, note 5 for USB ref column, and note 6 to replace "Note 1". Clarified note 4 to explain errature are salid for certain <i>csb_c.clk</i> values.</li> <li>In Table 69, updated note 6 to specify USB reference clock frequencies limited to 24 and 48 for rev. 2 silicon.</li> <li>Replaced Table 71 "Thermal Resistance for TEPBGAII with Heat Sink in Open Flow".</li> <li>Removed last row of Table 19.</li></ul> |

| 0              | 6/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC8313EEC Rev. 4 11/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. QorlQ is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. RapidIO is a registered trademark of the RapidIO Trade Association. IEEE 1588 and 1149.1 are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

© 2007–2011 Freescale Semiconductor, Inc.