#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 333MHz                                                     |

| Co-Processors/DSP               | Security; SEC 2.2                                          |

| RAM Controllers                 | DDR, DDR2                                                  |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100/1000Mbps (2)                                        |

| SATA                            | -                                                          |

| USB                             | USB 2.0 + PHY (1)                                          |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography                                               |

| Package / Case                  | 516-BBGA Exposed Pad                                       |

| Supplier Device Package         | 516-TEPBGA (27x27)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8313ezqaff |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

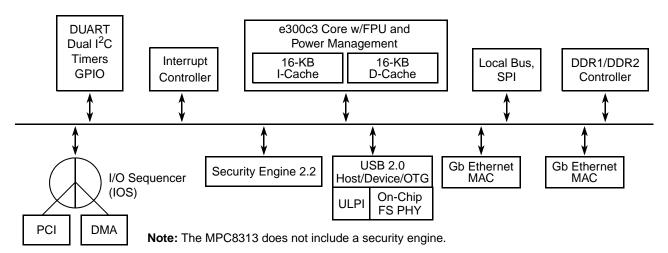

# 1 Overview

The MPC8313E incorporates the e300c3 core, which includes 16 Kbytes of L1 instruction and data caches and on-chip memory management units (MMUs). The MPC8313E has interfaces to dual enhanced three-speed 10/100/1000 Mbps Ethernet controllers, a DDR1/DDR2 SDRAM memory controller, an enhanced local bus controller, a 32-bit PCI controller, a dedicated security engine, a USB 2.0 dual-role controller and an on-chip high-speed PHY, a programmable interrupt controller, dual I<sup>2</sup>C controllers, a 4-channel DMA controller, and a general-purpose I/O port. This figure shows a block diagram of the MPC8313E.

### Figure 1. MPC8313E Block Diagram

The MPC8313E security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES, 3DES, AES, SHA-1, and MD-5 algorithms.

### 1.1 MPC8313E Features

The following features are supported in the MPC8313E:

- Embedded PowerPC<sup>TM</sup> e300 processor core built on Power Architecture<sup>TM</sup> technology; operates at up to 333 MHz.

- High-performance, low-power, and cost-effective host processor

- DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both DDR1 and DDR2

- 16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

- Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced local bus interface with up to 66-MHz operation, and USB 2.0 (high speed) with an on-chip PHY.

- Security engine provides acceleration for control and data plane security protocols

- Power management controller for low-power consumption

- High degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration

### 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

### 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

## 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

# 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

## 1.6 USB Dual-Role Controller

The MPC8313E USB controller includes the following features:

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

- Compatible with Universal Serial Bus Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed/high-speed PHY

## 1.7 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313E eTSECs include the following features:

- Two RGMII/SGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status

- Three-speed support (10/100/1000 Mbps)

- On-chip high-speed serial interface to external SGMII PHY interface

- Support for IEEE Std 1588<sup>TM</sup>

- Support for two full-duplex FIFO interface modes

- Multiple PHY interface configuration

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>®</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Transmission from up to eight physical queues.

- Reception to up to eight physical queues

- Full and half-duplex Ethernet support (1000 Mbps supports only full-duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE 802.1 virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound packets

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

# **1.8 Programmable Interrupt Controller (PIC)**

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model supports 5 external and 34 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

## 1.9 Power Management Controller (PMC)

The MPC8313E power management controller includes the following features:

- Provides power management when the device is used in both host and agent modes

- Supports PCI power management 1.2 D0, D1, D2, D3hot, and D3cold states

- On-chip split power supply controlled through external power switch for minimum standby power

- Support for PME generation in PCI agent mode, PME detection in PCI host mode

- Supports wake-up from Ethernet (Magic Packet), USB, GPIO, and PCI (PME input as host)

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 1. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

| Characteristic                       |                                                                                                        | Symbol                               | Max Value                                                                    | Unit | Note |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|------|

| Core supply voltage                  |                                                                                                        | V <sub>DD</sub>                      | -0.3 to 1.26                                                                 | V    | —    |

| PLL supply volta                     | ge                                                                                                     | AV <sub>DD</sub>                     | -0.3 to 1.26                                                                 | V    |      |

| Core power supp                      | bly for SerDes transceivers                                                                            | XCOREV <sub>DD</sub>                 | -0.3 to 1.26                                                                 | V    |      |

| Pad power suppl                      | y for SerDes transceivers                                                                              | XPADV <sub>DD</sub>                  | -0.3 to 1.26                                                                 | V    | —    |

| DDR and DDR2                         | DRAM I/O voltage                                                                                       | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                                 | V    |      |

| PCI, local bus, D<br>and JTAG I/O vo | UART, system control and power management, I <sup>2</sup> C, Itage                                     | NV <sub>DD</sub> /LV <sub>DD</sub>   | -0.3 to 3.6                                                                  | V    |      |

| eTSEC, USB                           |                                                                                                        | LV <sub>DDA</sub> /LV <sub>DDB</sub> | -0.3 to 3.6                                                                  | V    | _    |

| Input voltage                        | DDR DRAM signals                                                                                       | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | DDR DRAM reference                                                                                     | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                      | Enhanced three-speed Ethernet signals                                                                  | LV <sub>IN</sub>                     | -0.3 to (LV <sub>DDA</sub> + 0.3)<br>or<br>-0.3 to (LV <sub>DDB</sub> + 0.3) | V    | 4, 5 |

|                                      | Local bus, DUART, SYS_CLK_IN, system control, and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 3, 5 |

|                                      | PCI                                                                                                    | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 6    |

| Storage temperature range            |                                                                                                        | T <sub>STG</sub>                     | -55 to 150                                                                   | °C   | —    |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** NV<sub>IN</sub> must not exceed NV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: LV<sub>IN</sub> must not exceed LV<sub>DDA</sub>/LV<sub>DDB</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

### 2.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for the MPC8313E. Note that the values in this table are the recommended and tested operating conditions. If a particular block is given a voltage falling within the range in the Recommended Value column, the MPC8313E is capable of delivering the amount of current listed in the Current Requirement column; this is the maximum current possible. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                    | Symbol                                      | Recommended Value <sup>1</sup>                                                                                                               | Unit | Current<br>Requirement |

|---------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|

| Core supply voltage                               | V <sub>DD</sub>                             | 1.0 V ± 50 mV                                                                                                                                | V    | 469 mA                 |

| Internal core logic constant power                | V <sub>DDC</sub>                            | 1.0 V ± 50 mV                                                                                                                                | V    | 377 mA                 |

| SerDes internal digital power                     | XCOREV <sub>DD</sub>                        | 1.0                                                                                                                                          | V    | 170 mA                 |

| SerDes internal digital ground                    | XCOREV <sub>SS</sub>                        | 0.0                                                                                                                                          | V    | —                      |

| SerDes I/O digital power                          | XPADV <sub>DD</sub>                         | 1.0                                                                                                                                          | V    | 10 mA                  |

| SerDes I/O digital ground                         | XPADV <sub>SS</sub>                         | 0.0                                                                                                                                          | V    | —                      |

| SerDes analog power for PLL                       | SDAV <sub>DD</sub>                          | 1.0 V ± 50 mV                                                                                                                                | V    | 10 mA                  |

| SerDes analog ground for PLL                      | SDAV <sub>SS</sub>                          | 0.0                                                                                                                                          | V    | —                      |

| Dedicated 3.3 V analog power for USB PLL          | USB_PLL_PWR3                                | 3.3 V ± 300 mV                                                                                                                               | V    | 2–3 mA                 |

| Dedicated 1.0 V analog power for USB PLL          | USB_PLL_PWR1                                | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Dedicated analog ground for USB PLL               | USB_PLL_GND                                 | 0.0                                                                                                                                          | V    | —                      |

| Dedicated USB power for USB bias circuit          | USB_VDDA_BIAS                               | 3.3 V ± 300 mV                                                                                                                               | V    | 4–5 mA                 |

| Dedicated USB ground for USB bias circuit         | USB_VSSA_BIAS                               | 0.0                                                                                                                                          | V    | —                      |

| Dedicated power for USB transceiver               | USB_VDDA                                    | 3.3 V ± 300 mV                                                                                                                               | V    | 75 mA                  |

| Dedicated ground for USB transceiver              | USB_VSSA                                    | 0.0                                                                                                                                          | V    | —                      |

| Analog power for e300 core APLL                   | AV <sub>DD1</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Analog power for system APLL                      | AV <sub>DD2</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| DDR1 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 2.5 V ± 125 mV                                                                                                                               | V    | 131 mA                 |

| DDR2 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 1.8 V ± 80 mV                                                                                                                                | V    | 140 mA                 |

| Differential reference voltage for DDR controller | MV <sub>REF</sub>                           | $\begin{array}{c} 1/2 \text{ DDR supply} \\ (0.49 \times \text{GV}_{\text{DD}} \text{ to} \\ 0.51 \times \text{GV}_{\text{DD}}) \end{array}$ | V    | _                      |

| Standard I/O voltage                              | NV <sub>DD</sub>                            | $3.3 \text{ V} \pm 300 \text{ mV}^2$                                                                                                         | V    | 74 mA                  |

| eTSEC2 I/O supply                                 | LV <sub>DDA</sub>                           | 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                                            | V    | 22 mA                  |

| eTSEC1/USB DR I/O supply                          | LV <sub>DDB</sub>                           | 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                                            | V    | 44 mA                  |

| Supply for eLBC IOs                               | LV <sub>DD</sub>                            | 3.3 V ± 300 mV                                                                                                                               | V    | 16 mA                  |

| Analog and digital ground                         | V <sub>SS</sub>                             | 0.0                                                                                                                                          | V    | —                      |

| Junction temperature range                        | T <sub>A</sub> /T <sub>J</sub> <sup>3</sup> | 0 to 105                                                                                                                                     | °C   |                        |

### Table 2. Recommended Operating Conditions

| Driver Type                                        | Output Impedance ( $\Omega$ ) | Supply Voltage                      |

|----------------------------------------------------|-------------------------------|-------------------------------------|

| DDR2 signal                                        | 18                            | GV <sub>DD</sub> = 1.8 V            |

| DUART, system control, I <sup>2</sup> C, JTAG, SPI | 42                            | NV <sub>DD</sub> = 3.3 V            |

| GPIO signals                                       | 42                            | NV <sub>DD</sub> = 3.3 V            |

| eTSEC signals                                      | 42                            | $LV_{DDA}$ , $LV_{DDB}$ = 2.5/3.3 V |

| USB signals                                        | 42                            | LV <sub>DDB</sub> = 2.5/3.3 V       |

Table 3. Output Drive Capability (continued)

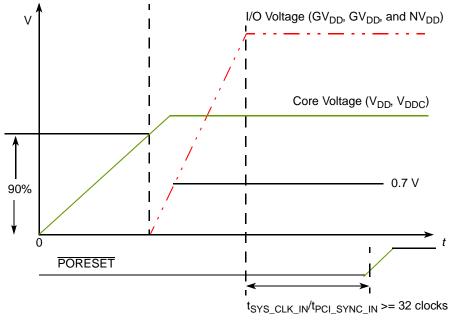

## 2.2 Power Sequencing

The MPC8313E does not require the core supply voltage ( $V_{DD}$  and  $V_{DDC}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) to be applied in any particular order. Note that during power ramp-up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$  and  $V_{DDC}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are stable, wait for a minimum of 32 clock cycles before negating PORESET.

Note that there is no specific power down sequence requirement for the MPC8313E. I/O voltage supplies  $(GV_{DD}, LV_{DD}, and NV_{DD})$  do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

This table provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

#### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —    |

This table provides the input AC timing specifications for the DDR2 SDRAM interface.

#### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $\text{GV}_{\text{DD}}$  of 2.5 ± 5%.

| Parameter                    | Symbol              | Min  | Мах | Unit | Note |

|------------------------------|---------------------|------|-----|------|------|

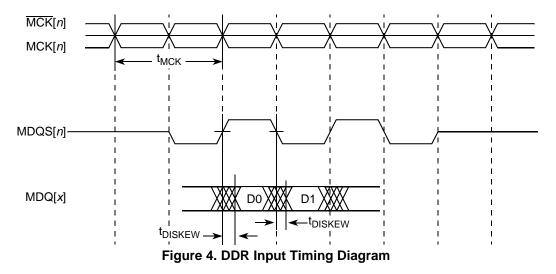

| Controller skew for MDQS—MDQ | t <sub>CISKEW</sub> | _    | _   | ps   | 1, 2 |

| 333 MHz                      |                     | -750 | 750 |      | —    |

| 266 MHz                      | _                   | -750 | 750 | _    | —    |

Notes:

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[*n*] and any corresponding bit that is captured with MDQS[*n*]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure illustrates the DDR input timing diagram showing the t<sub>DISKEW</sub> timing parameter.

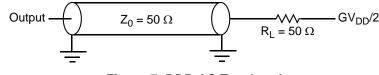

This figure provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

## 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

| Parameter                                                           | Symbol          | Min                    | Max                    | Unit |

|---------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                            | V <sub>IH</sub> | 2.0                    | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage NV <sub>DD</sub>                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$                  | V <sub>OH</sub> | NV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$                    | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ±5                     | μA   |

## 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          | _    | 2    |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all the media independent interface (MII), reduced gigabit media independent interface (RGMII), serial gigabit media independent interface (SGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the MII interface can be operated at 3.3 V. The RMII and SGMII interfaces can be operated at either 3.3 or 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for *Gigabit Ethernet Physical Layer Device Specification Version 1.2a* (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.5, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 **TSEC DC Electrical Characteristics**

All RGMII, RMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 24 and Table 25. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

### NOTE

eTSEC should be interfaced with peripheral operating at same voltage level.

| Parameter            | Symbol                               | Conditions                                   |                                    | Min             | Max                                                      | Unit |

|----------------------|--------------------------------------|----------------------------------------------|------------------------------------|-----------------|----------------------------------------------------------|------|

| Supply voltage 3.3 V | LV <sub>DDA</sub> /LV <sub>DDB</sub> |                                              | _                                  | 2.97            | 3.63                                                     | V    |

| Output high voltage  | V <sub>OH</sub>                      | I <sub>OH</sub> = -4.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$     | 2.40            | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>                      | I <sub>OL</sub> = 4.0 mA                     | $LV_{DDA}$ or $LV_{DDB}$ = Min     | V <sub>SS</sub> | 0.50                                                     | V    |

| Input high voltage   | V <sub>IH</sub>                      | _                                            | _                                  | 2.0             | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>                      | _                                            | —                                  | -0.3            | 0.90                                                     | V    |

| Input high current   | Ι <sub>ΙΗ</sub>                      | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                    | —               | 40                                                       | μA   |

| Input low current    | ۱ <sub>IL</sub>                      | V                                            | / <sub>IN</sub> <sup>1</sup> = VSS | -600            | —                                                        | μΑ   |

### Table 24. MII DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

#### Table 25. RGMII/RTBI DC Electrical Characteristics

| Parameters           | Symbol              | Conditions | Min  | Max  | Unit |

|----------------------|---------------------|------------|------|------|------|

| Supply voltage 2.5 V | $LV_{DDA}/LV_{DDB}$ | _          | 2.37 | 2.63 | V    |

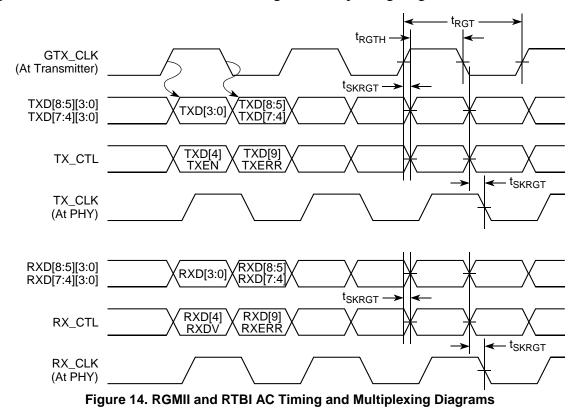

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

### 8.3 SGMII Interface Electrical Characteristics

Each SGMII port features a 4-wire AC-coupled serial link from the dedicated SerDes interface of MPC8313E as shown in Figure 15, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features a 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XCOREVSS. The reference circuit of the SerDes transmitter and receiver is shown in Figure 33.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines described in Section 22.5, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the TSEC\_GTX\_CLK125 clock is not required for this port. Instead, the SerDes reference clock is required on SD\_REF\_CLK and SD\_REF\_CLK pins.

### 8.3.1 DC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 9, "High-Speed Serial Interfaces (HSSI)."

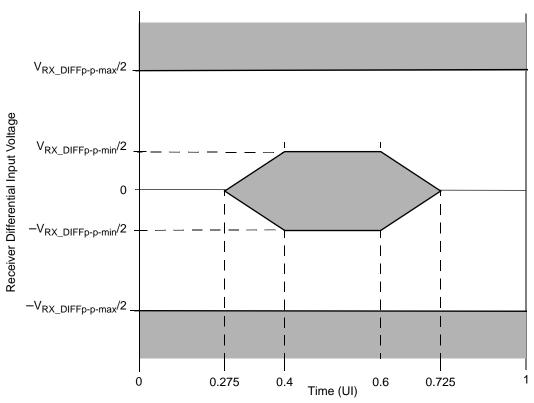

#### Table 35. SGMII Receive AC Timing Specifications (continued)

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter              | Symbol          | Min    | Тур | Max               | Unit   | Note |

|------------------------|-----------------|--------|-----|-------------------|--------|------|

| Total jitter tolerance | JT              | 0.65   | _   | _                 | UI p-p | 1    |

| Bit error ratio        | BER             | _      | _   | 10 <sup>-12</sup> |        |      |

| Unit interval          | UI              | 799.92 | 800 | 800.08            | ps     | 2    |

| AC coupling capacitor  | C <sub>TX</sub> | 5      | _   | 200               | nF     | 3    |

#### Notes:

1. Measured at receiver.

2. Each UI is 800 ps ± 100 ppm.

3. The external AC coupling capacitor is required. It is recommended to be placed near the device transmitter outputs.

Figure 17. SGMII Receiver Input Compliance Mask

# 9 High-Speed Serial Interfaces (HSSI)

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 9.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 22 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (TXn and  $\overline{TXn}$ ) or a receiver input (RXn and  $\overline{RXn}$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

1. Single-ended swing

The transmitter output signals and the receiver input signals TXn,  $\overline{TXn}$ , RXn, and  $\overline{RXn}$  each have a peak-to-peak swing of A – B volts. This is also referred as each signal wire's single-ended swing.

2. Differential output voltage, V<sub>OD</sub> (or differential output swing):

The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{TXn} - V_{\overline{TXn}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential input voltage, V<sub>ID</sub> (or differential input swing):

The differential input voltage (or swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{RXn} - V_{\overline{RXn}}$ . The  $V_{ID}$  value can be either positive or negative.

- 4. Differential peak voltage,  $V_{DIFFp}$ The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- 5. Differential peak-to-peak, V<sub>DIFFp-p</sub>

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

6. Differential waveform

The differential waveform is constructed by subtracting the inverting signal (TX*n*, for example) from the non-inverting signal (TX*n*, for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 22 as an example for differential waveform.

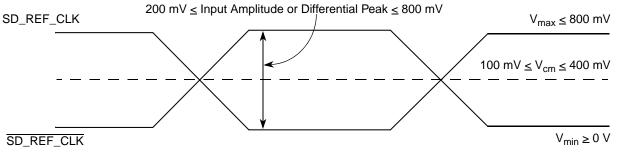

7. Common mode voltage,  $V_{cm}$

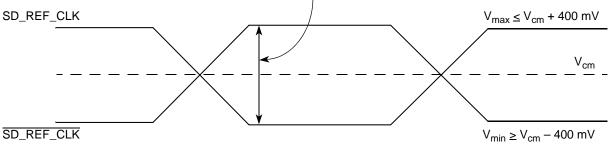

of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 9.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 24 shows the SerDes reference clock input requirement for the DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to  $XCOREV_{SS}$ . Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage ( $XCOREV_{SS}$ ). Figure 25 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

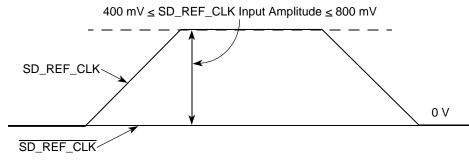

- Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 26 shows the SerDes reference clock input requirement for the single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC coupled externally. For the best noise performance, the reference of the clock could be DC or AC coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 24. Differential Reference Clock Input DC Requirements (External DC-Coupled)

Figure 25. Differential Reference Clock Input DC Requirements (External AC-Coupled)

### 9.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to XCOREV<sub>SS</sub>, the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC coupled.

- Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce a signal with too large of an amplitude and may need to be DC-biased at the clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC coupling.

### NOTE

Figure 27 through Figure 30 are for conceptual reference only. Due to the fact that the clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is possible that the clock circuit reference designs provided by clock driver chip vendors are different from what is shown in the figures. They might also vary from one vendor to the other. Therefore, Freescale can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. It is recommended that the system designer contact the selected clock driver chip vendor for the optimal reference circuits for the MPC8313E SerDes reference clock receiver requirement provided in this document.

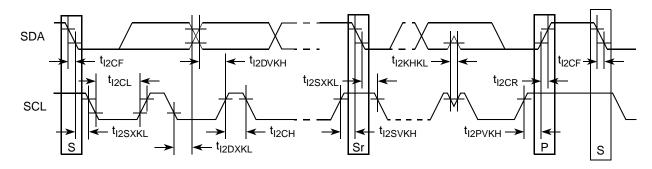

This figure shows the AC timing diagram for the  $I^2C$  bus.

Figure 47. I<sup>2</sup>C Bus AC Timing Diagram

# 14 PCI

This section describes the DC and AC electrical specifications for the PCI bus.

# 14.1 PCI DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI interface.

Table 50. PCI DC Electrical Characteristics<sup>1</sup>

| Parameter                 | Symbol          | Test Condition                          | Min                               | Max                    | Unit |

|---------------------------|-----------------|-----------------------------------------|-----------------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or           | $0.5\times \text{NV}_{\text{DD}}$ | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)              | -0.5                              | $0.3 	imes NV_{DD}$    | V    |

| High-level output voltage | V <sub>OH</sub> | $NV_{DD} = min, I_{OH} = -100 \ \mu A$  | $0.9 	imes NV_{DD}$               | —                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | $NV_{DD}$ = min, $I_{OL}$ = 100 $\mu$ A | _                                 | $0.1 \times NV_{DD}$   | V    |

| Input current             | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$          | _                                 | ±5                     | μA   |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $NV_{IN}$  symbol referenced in Table 1 and Table 2.

## 14.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the MPC8313E is configured as a host or agent device.

This table shows the PCI AC timing specifications at 66 MHz.

Table 51. PCI AC Timing Specifications at 66 MHz

| Parameter              | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|------------------------|---------------------|-----|-----|------|------|

| Clock to output valid  | <sup>t</sup> PCKHOV | _   | 6.0 | ns   | 2    |

| Output hold from clock | t <sub>PCKHOX</sub> | 1   | —   | ns   | 2    |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal         | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|----------------|--------------------|----------|------------------|------|

| TMS            | E4                 | I        | NV <sub>DD</sub> | 4    |

| TRST           | E5                 | I        | NV <sub>DD</sub> | 4    |

|                | TEST               |          | I                |      |

| TEST_MODE      | F4                 | l        | $NV_{DD}$        | 6    |

|                | DEBUG              |          |                  |      |

| QUIESCE        | F5                 | 0        | $NV_{DD}$        | _    |

|                | System Control     |          |                  |      |

| HRESET         | F2                 | I/O      | $NV_{DD}$        | 1    |

| PORESET        | F3                 | I        | NV <sub>DD</sub> | _    |

| SRESET         | F1                 | I        | NV <sub>DD</sub> | _    |

|                | Clocks             |          |                  |      |

| SYS_CR_CLK_IN  | U26                | I        | NV <sub>DD</sub> | _    |

| SYS_CR_CLK_OUT | U25                | 0        | NV <sub>DD</sub> | _    |

| SYS_CLK_IN     | U23                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_IN  | T26                | I        | NV <sub>DD</sub> | _    |

| USB_CR_CLK_OUT | R26                | 0        | NV <sub>DD</sub> | _    |

| USB_CLK_IN     | T22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_OUT   | U24                | 0        | NV <sub>DD</sub> | 3    |

| RTC_PIT_CLOCK  | R22                | I        | NV <sub>DD</sub> | _    |

| PCI_SYNC_IN    | T24                | I        | NV <sub>DD</sub> | _    |

|                | MISC               |          | I                |      |

| THERM0         | N1                 | Ι        | NV <sub>DD</sub> | 7    |

| THERM1         | N3                 | Ι        | NV <sub>DD</sub> | 7    |

|                | PCI                |          | I                |      |

| PCI_INTA       | AF7                | 0        | NV <sub>DD</sub> | _    |

| PCI_RESET_OUT  | AB11               | 0        | NV <sub>DD</sub> | _    |

| PCI_AD0        | AB20               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD1        | AF23               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD2        | AF22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD3        | AB19               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD4        | AE22               | I/O      | NV <sub>DD</sub> | _    |

| PCI_AD5        | AF21               | I/O      | NV <sub>DD</sub> | _    |

| Signal                                             | Package Pin Number | Pin Type | Power<br>Supply  | Note                     |

|----------------------------------------------------|--------------------|----------|------------------|--------------------------|

| RXB                                                | R1                 | I        |                  | —                        |

| RXB                                                | P1                 | I        |                  | —                        |

| SD_IMP_CAL_RX                                      | V5                 | I        |                  | 200 Ω ±<br>10% to<br>GND |

| SD_REF_CLK                                         | T5                 | I        |                  | —                        |

| SD_REF_CLK                                         | T4                 | I        |                  | —                        |

| SD_PLL_TPD                                         | T2                 | 0        |                  | —                        |

| SD_IMP_CAL_TX                                      | N5                 | I        |                  | 100 Ω ±<br>10% to<br>GND |

| SDAVDD                                             | R5                 | I/O      |                  | —                        |

| SD_PLL_TPA_ANA                                     | R4                 | 0        |                  | —                        |

| SDAVSS                                             | R3                 | I/O      |                  | —                        |

|                                                    | USB PHY            | L.       |                  | 1                        |

| USB_DP                                             | P26                | I/O      |                  | _                        |

| USB_DM                                             | N26                | 26 I/O   |                  | —                        |

| USB_VBUS                                           | P24                | I/O      |                  | —                        |

| USB_TPA                                            | L26                | I/O      |                  | —                        |

| USB_RBIAS                                          | M24                | I/O      |                  | —                        |

| USB_PLL_PWR3                                       | M26                | I/O      |                  | —                        |

| USB_PLL_GND                                        | N24                | I/O      |                  | —                        |

| USB_PLL_PWR1                                       | N25                | I/O      |                  | —                        |

| USB_VSSA_BIAS                                      | M25                | I/O      |                  | —                        |

| USB_VDDA_BIAS                                      | M22                | I/O      |                  | —                        |

| USB_VSSA                                           | N22                | I/O      |                  | —                        |

| USB_VDDA                                           | P22                | I/O      |                  | —                        |

|                                                    | GTM/USB            | I        |                  | 1                        |

| USBDR_DRIVE_VBUS/GTM1_TIN1/GTM2_TIN2/LSRCID0       | AD23               | I/O      | NV <sub>DD</sub> | —                        |

| USBDR_PWRFAULT/GTM1_TGATE1/GTM2_TGATE2/<br>LSRCID1 | AE23               | I/O      | NV <sub>DD</sub> | -                        |

| USBDR_PCTL0/GTM1_TOUT1/LSRCID2                     | AC22               | 0        | NV <sub>DD</sub> | —                        |

| USBDR_PCTL1/LBC_PM_REF_10/LSRCID3                  | AB21               | 0        | NV <sub>DD</sub> | —                        |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

# 24 Revision History

This table summarizes a revision history for this document.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 11/2011 | <ul> <li>In Table 2, added following notes: <ul> <li>Note 3: Min temperature is specified with T<sub>A</sub>; Max temperature is specified with T<sub>J</sub></li> <li>Note 4: All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.</li> <li>Note 5: All I/O pins should be interfaced with peripherals operating at same voltage level.</li> <li>Note 6: This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter</li> <li>Decoupled PCI_CLK and SYS_CLK_IN rise and fall times in Table 8. Relaxed maximum rise/fall time of SYS_CLK_IN to 4ns.</li> <li>Added a note in Table 27 stating "The frequency of RX_CLK should not exceed the TX_CLK by more than 300 ppm."</li> <li>In Table 30: <ul> <li>Changed max value of t<sub>skrg1</sub> in "Data to clock input skew (at receiver)" row from 2.8 to 2.6.</li> <li>Added note 7, stating that, "The frequency of RX_CLK should not exceed the GTX_CLK125 by more than 300 ppm."</li> </ul> </li> <li>In Table 30: <ul> <li>Changed max value of t<sub>skrg1</sub> in "Data to clock input skew (at receiver)" row from 2.8 to 2.6.</li> <li>Added note 7, stating that, "The frequency of RX_CLK should not exceed the GTX_CLK125 by more than 300 ppm."</li> </ul> </li> <li>In Table 30: <ul> <li>Changed max value of table 2 should be interfaced with peripheral operating at same voltage level" in Section 8.1.1, "TSEC DC Electrical Characteristics."</li> </ul> </li> <li>TSEC1_MDC and TSEC_MDIO are powered at 3.3V by NVDD. Replaced LVDDA/LVDDB with NVDD and removed instances of 2.5V at several places in Section 8.5, "Ethernet Management Interface Electrical Characteristics."</li> <li>In Table 43, changed min/max values of t<sub>CLK_TOL</sub> from 0.05 to 0.005.</li> <li>In Table 43, changed min/max values of the MPC8313E TEPBGAII," replaced "5.5 Sn/0.5 Cu/4 Ag" with "Sn/3.5 Ag."</li> <li>Added Note 12: "In MII mode, GTX_CLK should be pulled down by 300 Ω to V<sub>SS</sub>" to TSEC1_GTX_C</li></ul></li></ul> |

| 3              | 01/2009 | • Table 72, in column aa, changed to AG = 400 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2            | 12/2008 | Made cross-references active for sections, figures, and tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1            | 12/2008 | Added Figure 2, after Table 2 and renumbered the following figures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 73. Document Revision History

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 10/2008 | <ul> <li>Added Note "The information in this document is accurate for revision 1.0, and 2.x and later. See Section 24.1, "Part Numbers Fully Addressed by this Document," before Section 1, "Overview."</li> <li>Added part Numbering details for all the silicon revisions in Table 74.</li> <li>Changed V<sub>IH</sub> from 2.7 V to 2.4 V in Table 7.</li> <li>Added a column for maximum power dissipation in low power mode for Rev 2.x or later silicon in Table 6.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added Table 21 for DDR AC Specs on Rev 2.x or later silicon.</li> <li>Added EfWE, LFCLE, LFALE, LOE, LFRE, LFWP, LGTA, LUPWAIT, and LFRB in Table 63.</li> <li>In Table 39, added note 2: "This parameter is dependent on the csb_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC_MDC.)"</li> <li>Removed mentions of SGMII (SGMII has separate specs) from Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics."</li> <li>Corrected Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/SGMII/RTBI Electrical Characteristics," to state that RGMII/RTBI Interfaces only operate at 2.5 V, not 3.3 V.</li> <li>Added ZQ package to ordering information In Table 74 and Section 19.1, "Package Parameters for the MPC8313E TEPBGAII" (applicable to both silicon rev. 1.0 and 2.1)</li> <li>Removed footnotes 5 and 6 from Table 1 (left over when the PCI undershoot/overshoot voltages and maximum AC waveforms were removed from Section 2.1.2, "Power Supply Voltage Specification").</li> <li>Removed SD_PLL_TPD (T2) and SD_PLL_TPA_ANA (R4) from Table 63.</li> <li>Added Section 8.3, "SGMII Interface Electrical Characteristics." Removed Section 8.5.3 SGMII DC Electrical Characteristics.</li> <li>Removed "HRESET negation to S</li></ul> |

### Table 73. Document Revision History (continued)

-