#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| 2 0 0 0 0 0                     |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Core Processor                  | PowerPC e300c3                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 333MHz                                                      |

| Co-Processors/DSP               | Security; SEC 2.2                                           |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (2)                                         |

| SATA                            | -                                                           |

| USB                             | USB 2.0 + PHY (1)                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography                                                |

| Package / Case                  | 516-BBGA Exposed Pad                                        |

| Supplier Device Package         | 516-TEPBGA (27x27)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8313ezqaffb |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

## 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

## 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

## 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

| Interface                     | Parameter | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments |

|-------------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|----------|

| USBDR controller load = 20 pF | 60 MHz    |                             | _                           |                             | 0.078                                               |                                                     | —                           | W    |          |

| Other I/O                     | _         | —                           |                             | 0.015                       | _                                                   |                                                     | —                           | W    | _        |

Table 5. MPC8313E Typical I/O Power Dissipation (continued)

This table shows the estimated core power dissipation of the MPC8313E while transitioning into the D3 warm low-power state.

| Table 6. MPC8313E Low-Power Modes Power | Dissipation <sup>1</sup> |

|-----------------------------------------|--------------------------|

|-----------------------------------------|--------------------------|

| 333-MHz Core, 167-MHz CSB <sup>2</sup> | Rev. 1.0 <sup>3</sup> | Rev. 2.x or Later <sup>3</sup> | Unit |

|----------------------------------------|-----------------------|--------------------------------|------|

| D3 warm                                | 400                   | 425                            | mW   |

Note:

- 1. All interfaces are enabled. For further power savings, disable the clocks to unused blocks.

- The interfaces are run at the following frequencies: DDR: 333 MHz, eLBC 83 MHz, PCI 33 MHz, eTSEC1 and TSEC2: 167 MHz, SEC: 167 MHz, USB: 167 MHz. See the SCCR register for more information.

- 3. This is maximum power in D3 Warm based on a voltage of 1.05 V and a junction temperature of 105°C.

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8313E.

## 4.1 DC Electrical Characteristics

This table provides the system clock input (SYS\_CLK\_IN/PCI\_SYNC\_IN) DC timing specifications for the MPC8313E.

| Parameter                 | Condition                                                                                                         | Symbol          | Min  | Мах                    | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | _                                                                                                                 | V <sub>IH</sub> | 2.4  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | _                                                                                                                 | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current  | $0 \ V \ \leq V_{IN} \leq NV_{DD}$                                                                                | I <sub>IN</sub> | —    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \\ or \\ NV_{DD} - 0.5 \ V \leq V_{IN} \leq NV_{DD} \end{array}$ | I <sub>IN</sub> | _    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $0.5~\text{V} \leq \text{V}_{\text{IN}} \leq \text{NV}_{\text{DD}} - 0.5~\text{V}$                                | I <sub>IN</sub> | —    | ±50                    | μΑ   |

Table 7. SYS\_CLK\_IN DC Electrical Characteristics

### NOTE

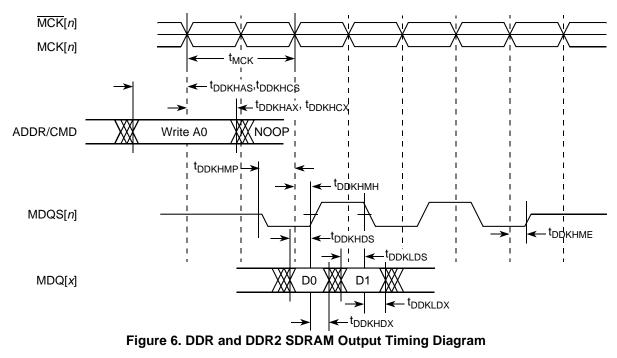

For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

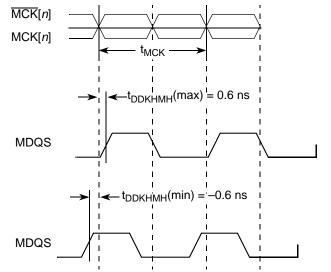

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

This figure shows the DDR and DDR2 SDRAM output timing diagram.

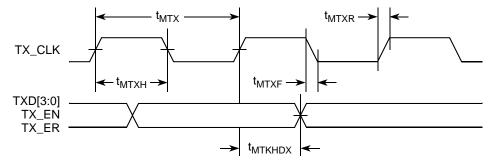

This figure shows the MII transmit AC timing diagram.

Figure 8. MII Transmit AC Timing Diagram

### 8.2.1.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

Table 27. MII Receive AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DDA}}/\text{LV}_{\text{DDB}}/\text{NV}_{\text{DD}}$  of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                              | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|------------------------------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                                      | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                                     | t <sub>MRX</sub>                    | —    | 40  | —   | ns   |

| RX_CLK duty cycle                                                | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                      | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                       | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MRXR</sub>                   | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>MRXF</sub>                   | 1.0  |     | 4.0 | ns   |

Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. The frequency of RX\_CLK should not exceed the TX\_CLK by more than 300 ppm

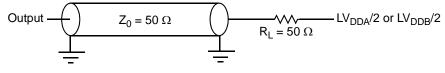

This figure provides the AC test load for TSEC.

Figure 9. TSEC AC Test Load

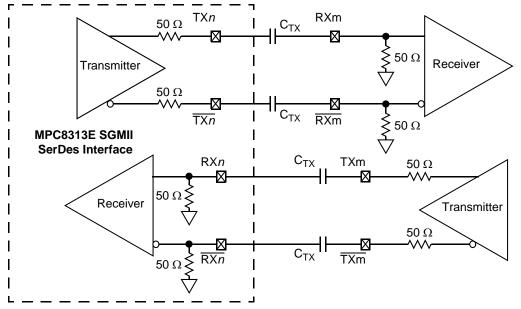

Figure 15. 4-Wire AC-Coupled SGMII Serial Link Connection Example

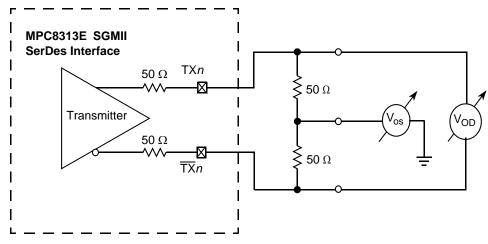

Figure 16. SGMII Transmitter DC Measurement Circuit

| Table 33. SGMII DC Receive | r Electrical Characteristics |

|----------------------------|------------------------------|

|----------------------------|------------------------------|

| Parameter                             | Symbol                  | Min  | Тур | Max  | Unit | Note |

|---------------------------------------|-------------------------|------|-----|------|------|------|

| Supply voltage                        | XCOREV <sub>DD</sub>    | 0.95 | 1.0 | 1.05 | V    |      |

| DC Input voltage range                |                         |      | N/A |      |      | 1    |

| Input differential voltage            | V <sub>RX_DIFFp-p</sub> | 100  | —   | 1200 | mV   | 2    |

| Loss of signal threshold              | VL <sub>OS</sub>        | 30   | —   | 100  | mV   |      |

| Input AC common mode voltage          | V <sub>CM_ACp-p</sub>   | —    | _   | 100  | mV   | 3    |

| Receiver differential input impedance | Z <sub>RX_DIFF</sub>    | 80   | 100 | 120  | Ω    |      |

| Receiver common mode input impedance  | Z <sub>RX_CM</sub>      | 20   | —   | 35   | Ω    |      |

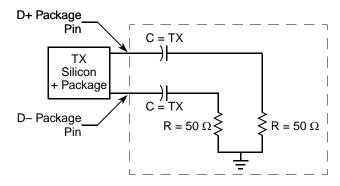

Figure 18. SGMII AC Test/Measurement Load

## 8.4 eTSEC IEEE 1588 AC Specifications

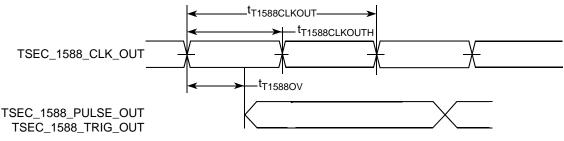

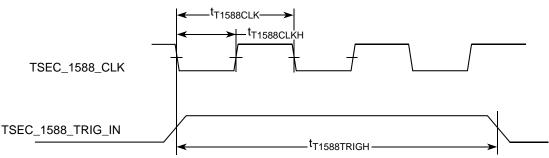

This figure provides the data and command output timing diagram.

**Note:** The output delay is count starting rising edge if t<sub>T1588CLKOUT</sub> is non-inverting. Otherwise, it is count starting falling edge.

Figure 19. eTSEC IEEE 1588 Output AC Timing

This figure provides the data and command input timing diagram.

Figure 20. eTSEC IEEE 1588 Input AC Timing

This table lists the IEEE 1588 AC timing specifications.

### Table 36. eTSEC IEEE 1588 AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition        | Symbol                                        | Min | Тур | Мах                    | Unit | Note |

|----------------------------|-----------------------------------------------|-----|-----|------------------------|------|------|

| TSEC_1588_CLK clock period | t <sub>T1588CLK</sub>                         | 3.8 | _   | $T_{RX\_CLK} \times 9$ | ns   | 1, 3 |

| TSEC_1588_CLK duty cycle   | t <sub>T1588CLKH</sub> /t <sub>T1588CLK</sub> | 40  | 50  | 60                     | %    |      |

### Table 36. eTSEC IEEE 1588 AC Timing Specifications (continued)

At recommended operating conditions with L/TV\_{DD} of 3.3 V  $\pm$  5%.

| Parameter/Condition                   | Symbol                                                  | Min                         | Тур | Мах | Unit | Note |

|---------------------------------------|---------------------------------------------------------|-----------------------------|-----|-----|------|------|

| TSEC_1588_CLK peak-to-peak jitter     | t <sub>T1588CLKINJ</sub>                                | —                           |     | 250 | ps   |      |

| Rise time eTSEC_1588_CLK<br>(20%-80%) | t <sub>T1588CLKINR</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| Fall time eTSEC_1588_CLK<br>(80%–20%) | t <sub>T1588CLKINF</sub>                                | 1.0                         | _   | 2.0 | ns   |      |

| TSEC_1588_CLK_OUT clock period        | t <sub>T1588</sub> CLKOUT                               | 2 × t <sub>T1588CLK</sub>   | _   | _   | ns   |      |

| TSEC_1588_CLK_OUT duty cycle          | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70  | %    |      |

| TSEC_1588_PULSE_OUT                   | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0 | ns   |      |

| TSEC_1588_TRIG_IN pulse width         | t <sub>T1588</sub> trigh                                | $2 \times t_{T1588CLK_MAX}$ |     | —   | ns   | 2    |

Notes:

1. T<sub>RX\_CLK</sub> is the max clock period of eTSEC receiving clock selected by TMR\_CTRL[CKSEL]. See the *MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual,* for a description of TMR\_CTRL registers.

2. It need to be at least two times of clock period of clock selected by TMR\_CTRL[CKSEL]. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description of TMR\_CTRL registers.

The maximum value of t<sub>T1588CLK</sub> is not only defined by the value of T<sub>RX\_CLK</sub>, but also defined by the recovered clock. For example, for 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 3600, 280, and 56 ns, respectively.

## 8.5 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for MII, RMII, RGMII, SGMII, and RTBI are specified in Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics."

### 8.5.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. Table 37 provide the DC electrical characteristics for MDIO and MDC.

| Parameter              | Symbol          | Condi                     | Min                     | Max             | Unit                   |    |

|------------------------|-----------------|---------------------------|-------------------------|-----------------|------------------------|----|

| Supply voltage (3.3 V) | $NV_{DD}$       | _                         |                         | 2.97            | 3.63                   | V  |

| Output high voltage    | V <sub>OH</sub> | I <sub>OH</sub> = -1.0 mA | NV <sub>DD</sub> = Min  | 2.10            | NV <sub>DD</sub> + 0.3 | V  |

| Output low voltage     | V <sub>OL</sub> | I <sub>OL</sub> = 1.0 mA  | NV <sub>DD</sub> = Min  | V <sub>SS</sub> | 0.50                   | V  |

| Input high voltage     | V <sub>IH</sub> | -                         | -                       | 2.0             | _                      | V  |

| Input low voltage      | V <sub>IL</sub> | -                         | -                       | —               | 0.80                   | V  |

| Input high current     | I <sub>IH</sub> | NV <sub>DD</sub> = Max    | $V_{IN}^{1} = 2.1 V$    | —               | 40                     | μA |

| Input low current      | ۱ <sub>IL</sub> | NV <sub>DD</sub> = Max    | V <sub>IN</sub> = 0.5 V | -600            | —                      | μΑ |

Table 37. MII Management DC Electrical Characteristics When Powered at 3.3 V

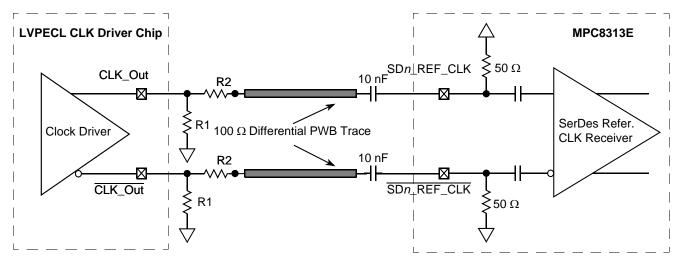

assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8313E SerDes3 reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult with the clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 29. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

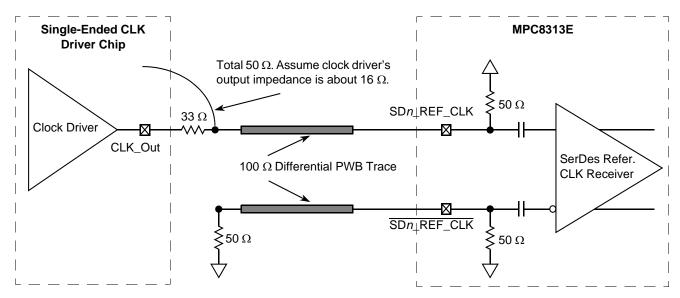

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the MPC8313E SerDes reference clock input's DC requirement.

Figure 30. Single-Ended Connection (Reference Only)

### 9.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low-phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters for SGMII protocol.

### Table 39. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with  $XV_{DD\_SRDS1}$  or  $XV_{DD\_SRDS2}$  = 1.0 V ± 5%.

| Parameter                                                                  | Symbol             | Min  | Max  | Unit | Note |

|----------------------------------------------------------------------------|--------------------|------|------|------|------|

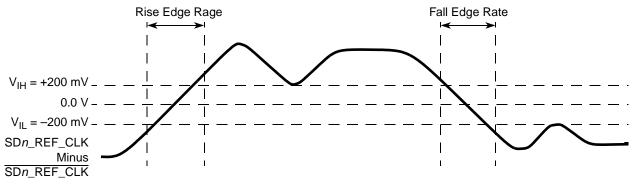

| Rising edge rate                                                           | Rise edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Falling edge rate                                                          | Fall edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Differential input high voltage                                            | V <sub>IH</sub>    | +200 | —    | mV   | 2    |

| Differential input low voltage                                             | V <sub>IL</sub>    | _    | -200 | mV   | 2    |

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-fall matching | _    | 20   | %    | 1, 4 |

#### Notes:

- 1. Measurement taken from single-ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from –200 to +200 mV on the differential waveform (derived from SD*n*\_REF\_CLK minus SD*n*\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 31.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point, where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The rise edge rate of SDn\_REF\_CLK should be compared to the fall edge rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 32.

Figure 31. Differential Measurement Points for Rise and Fall Time

Figure 32. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following section for detailed information:

• Section 8.3.2, "AC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK"

### 9.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

## 9.3 SerDes Transmitter and Receiver Reference Circuits

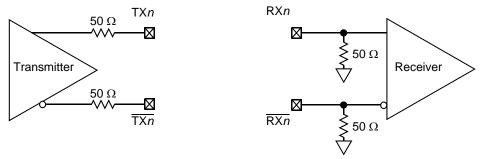

This figure shows the reference circuits for the SerDes data lane's transmitter and receiver.

Figure 33. SerDes Transmitter and Receiver Reference Circuits

The SerDes data lane's DC and AC specifications are defined in the interface protocol section listed below (SGMII) based on the application usage:

• Section 8.3, "SGMII Interface Electrical Characteristics"

Please note that a external AC-coupling capacitor is required for the above serial transmission protocol with the capacitor value defined in the specifications of the protocol section.

| Signal     | Package Pin Number             | Pin Type | Power<br>Supply  | Note |  |

|------------|--------------------------------|----------|------------------|------|--|

| MEMC_MCS0  | D10                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MCS1  | A10                            | 0        | GV <sub>DD</sub> | _    |  |

| MEMC_MCKE  | B14                            | 0        | GV <sub>DD</sub> | 3    |  |

| MEMC_MCK   | A13                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MCK   | A14                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MODT0 | B23                            | 0        | GV <sub>DD</sub> |      |  |

| MEMC_MODT1 | C23                            | 0        | GV <sub>DD</sub> |      |  |

|            | Local Bus Controller Interface |          |                  |      |  |

| LAD0       | K25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD1       | K24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD2       | K23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD3       | K22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD4       | J25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD5       | J24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD6       | J23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD7       | J22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD8       | H24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD9       | F26                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD10      | G24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD11      | F25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD12      | E25                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD13      | F24                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD14      | G22                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LAD15      | F23                            | I/O      | LV <sub>DD</sub> | 11   |  |

| LA16       | AC25                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA17       | AC26                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA18       | AB22                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA19       | AB23                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA20       | AB24                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA21       | AB25                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA22       | AB26                           | 0        | LV <sub>DD</sub> | 11   |  |

| LA23       | E22                            | 0        | LV <sub>DD</sub> | 11   |  |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                              | Package Pin Number         | Pin Type           | Power<br>Supply     | Note |  |

|-------------------------------------|----------------------------|--------------------|---------------------|------|--|

| LA14/TSEC_1588_TRIG1                | L24                        | 0                  | LV <sub>DD</sub>    | 8    |  |

| LA15/TSEC_1588_ALARM2               | K26                        | 0                  | LV <sub>DD</sub>    | 8    |  |

|                                     | DUART                      |                    |                     |      |  |

| UART_SOUT1/MSRCID0                  | N2                         | 0                  | $NV_{DD}$           | —    |  |

| UART_SIN1/MSRCID1                   | M5                         | I/O                | NV <sub>DD</sub>    | _    |  |

| UART_CTS1/GPIO8/MSRCID2             | M1                         | I/O                | NV <sub>DD</sub>    | _    |  |

| UART_RTS1/GPIO9/MSRCID3             | K1                         | I/O                | NV <sub>DD</sub>    | _    |  |

| UART_SOUT2/MSRCID4/TSEC_1588_CLK    | M3                         | 0                  | NV <sub>DD</sub>    | 8    |  |

| UART_SIN2/MDVAL/TSEC_1588_GCLK      | L1                         | I/O                | NV <sub>DD</sub>    | 8    |  |

| UART_CTS2/TSEC_1588_PP1             | L5                         | I/O                | NV <sub>DD</sub>    | 8    |  |

| UART_RTS2/TSEC_1588_PP2             | L3                         | I/O                | NV <sub>DD</sub>    | 8    |  |

|                                     | I <sup>2</sup> C interface |                    |                     |      |  |

| IIC1_SDA/CKSTOP_OUT/TSEC_1588_TRIG1 | J4                         | I/O                | NV <sub>DD</sub>    | 2, 8 |  |

| IIC1_SCL/CKSTOP_IN/TSEC_1588_ALARM2 | J2                         | I/O                | NV <sub>DD</sub> 2, |      |  |

| IIC2_SDA/PMC_PWR_OK/GPIO10          | J3                         | I/O                | NV <sub>DD</sub> 2  |      |  |

| IIC2_SCL/GPIO11                     | H5                         | I/O                | NV <sub>DD</sub>    | 2    |  |

|                                     | Interrupts                 |                    |                     |      |  |

| MCP_OUT                             | G5                         | 0                  | $NV_{DD}$           | 2    |  |

| IRQ0/MCP_IN                         | K5                         | I                  | NV <sub>DD</sub>    | _    |  |

| ĪRQ1                                | K4                         | I                  | NV <sub>DD</sub>    | _    |  |

| ĪRQ2                                | K2                         | I                  | NV <sub>DD</sub>    | _    |  |

| IRQ3/CKSTOP_OUT                     | К3                         | I/O                | NV <sub>DD</sub>    | _    |  |

| IRQ4/CKSTOP_IN/GPIO12               | J1                         | I/O                | NV <sub>DD</sub>    | _    |  |

|                                     | Configuration              |                    |                     |      |  |

| CFG_CLKIN_DIV                       | D5                         | I                  | $NV_{DD}$           | _    |  |

| EXT_PWR_CTRL                        | J5                         | O NV <sub>DD</sub> |                     | _    |  |

| CFG_LBIU_MUX_EN                     | R24                        | Ι                  | NV <sub>DD</sub>    | _    |  |

|                                     | JTAG                       |                    |                     |      |  |

| тск                                 | E1                         | Ι                  | $NV_{DD}$           | _    |  |

| TDI                                 | E2                         | Ι                  | NV <sub>DD</sub>    | 4    |  |

| TDO                                 | E3                         | 0                  | NV <sub>DD</sub>    | 3    |  |

| Signal               | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                         | Power<br>Supply | Note |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------|--|

| V <sub>SS</sub>      | B1,B2,B8,B9,B16,B17,C1,<br>C2,C3,C4,C5,C24,C25,<br>C26,D3,D4,D12,D13,D20,<br>D21,F8,F11,F13,F16,F17,<br>F21,G2,G25,H2,H6,H21,<br>H25,L4,L6,L11,L12,L13,<br>L14,L15,L16,L21,L23,M4,<br>M11,M12,M13,M14,M15,<br>M16,M23,N6,N11,N12,<br>N13,N14,N15,N16,<br>N21,N23,P11,P12,P13,<br>P14,P15,P16,P23,P25,<br>R11,R12,R13,R14,R15,<br>R16,R25,T6,T11,T12,T13,<br>T14,T15,T16,T21,T25,U5,<br>U6,U21,W4,W23,Y4,Y23,<br>AA8,AA11,AA13,AA16,<br>AA17,AA21,AC4,AC5,<br>AC12,AC13,AC20,AC21,<br>AD1,AE2,AE8,AE9,AE16,<br>AE17,AF2 |                                                  |                 |      |  |

| XCOREV <sub>DD</sub> | T1,U2,V2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Core power for<br>SerDes<br>transceivers (1.0 V) | _               | _    |  |

| XCOREV <sub>SS</sub> | P2,R2,T3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                                                |                 | —    |  |

| XPADV <sub>DD</sub>  | P5,U4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pad power for<br>SerDes<br>transceivers (1.0 V)  |                 | _    |  |

| XPADV <sub>SS</sub>  | P3,V4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                | _               | —    |  |

### Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

Notes:

- 1. This pin is an open drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to NV<sub>DD</sub>.

- 2. This pin is an open drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to  $NV_{DD}$ .

- 3. This output is actively driven during reset rather than being three-stated during reset.

- 4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 5. This pin should have a weak pull up if the chip is in PCI host mode. Follow PCI specifications recommendation.

- 6. This pin must always be tied to V<sub>SS</sub>.

- 7. Internal thermally sensitive resistor, resistor value varies linearly with temperature. Useful for determining the junction temperature.

- 8. 1588 signals are available on these pins only in MPC8313 Rev 2.x or later.

- 9. LB\_POR\_CFG\_BOOT\_ECC\_DIS is available only in MPC8313 Rev 2.x or later.

- 10. This pin has an internal pull-up.

- 11. This pin has an internal pull-down.

- 12. In MII mode, GTX\_CLK should be pulled down by  $300\Omega$  to V<sub>SS</sub>.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0100       | × 4                                 |

| 0101       | × 5                                 |

| 0110       | × 6                                 |

| 0111–1111  | Reserved                            |

### Table 65. System PLL Multiplication Factors (continued)

#### Note:

1. If RCWL[DDRCM] and RCWL[LBCM] are both cleared, the system PLL VCO frequency = (CSB frequency) × (System PLL VCO Divider).

2. If either RCWL[DDRCM] or RCWL[LBCM] are set, the system PLL VCO frequency = 2 × (CSB frequency) × (System PLL VCO Divider).

3. The VCO divider needs to be set properly so that the System PLL VCO frequency is in the range of 450–750 MHz

As described in Section 20, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (SYS\_CLK\_IN or PCI\_SYNC\_IN) and the internal coherent system bus clock (*csb\_clk*). This table shows the expected frequency values for the CSB frequency for select *csb\_clk* to SYS\_CLK\_IN/PCI\_SYNC\_IN ratios.

|                                        |      |                                                   | Input Clock Frequency (MHz) <sup>2</sup> |     |               |       |

|----------------------------------------|------|---------------------------------------------------|------------------------------------------|-----|---------------|-------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :Input<br>Clock Ratio <sup>2</sup> | 24                                       | 25  | 33.33         | 66.67 |

|                                        |      |                                                   | csb_clk F                                |     | equency (MHz) |       |

| High                                   | 0010 | 2:1                                               |                                          |     |               | 133   |

| High                                   | 0011 | 3:1                                               |                                          | 100 |               |       |

| High                                   | 0100 | 4:1                                               |                                          | 100 | 133           |       |

| High                                   | 0101 | 5:1                                               | 120                                      | 125 | 167           |       |

| High                                   | 0110 | 6:1                                               | 144                                      | 150 |               |       |

| Low                                    | 0010 | 2:1                                               |                                          |     | 133           |       |

| Low                                    | 0011 | 3:1                                               |                                          |     | 100           |       |

| Low                                    | 0100 | 4:11                                              |                                          | 100 | 133           |       |

| Low                                    | 0101 | 5:1                                               | 120                                      | 125 | 167           |       |

| Low                                    | 0110 | 6:1                                               | 144                                      | 150 |               |       |

Table 66. CSB Frequency Options

<sup>1</sup> CFG\_CLKIN\_DIV select the ratio between SYS\_CLK\_IN and PCI\_SYNC\_OUT.

<sup>2</sup> SYS\_CLK\_IN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

| Heat sink Vendors include the following list:                                                                                |              |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                              | 603-224-9988 |

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-thermal.com  | 408-436-8770 |

| Tyco Electronics<br>Chip Coolers <sup>TM</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105<br>Internet: www.chipcoolers.com     | 800-522-6752 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                    | 603-635-2800 |

| Interface material vendors include the following:                                                                            |              |

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801<br>Internet: www.chomerics.com                                          | 781-935-4850 |

| Dow-Corning Corporation<br>Corporate Center<br>PO BOX 994                                                                    | 800-248-2481 |

| Midland, MI 48686-0994<br>Internet: www.dowcorning.com                                                                       |              |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                               | 888-642-7674 |

| The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                   | 800-347-4572 |

- Output signals on the SerDes interface are fed from the XPADV<sub>DD</sub> power plane. Input signals and sensitive transceiver analog circuits are on the XCOREV<sub>DD</sub> supply.

- Power: XPADV<sub>DD</sub> consumes less than 300 mW; XCOREV<sub>DD</sub> + SDAV<sub>DD</sub> consumes less than 750 mW.

## 22.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8313E system, and the MPC8313E itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ , and  $LV_{DDB}$  pin of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DDA}$ ,  $LV_{DDB}$ , and VSS power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $LV_{DDA}$ , and  $LV_{DDB}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100 to 330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values and types of bulk capacitors.

## 22.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power (XCOREV<sub>DD</sub> and XPADV<sub>DD</sub>) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only SMT capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there should be a 1-µF ceramic chip capacitor from each SerDes supply (XCOREV<sub>DD</sub> and XPADV<sub>DD</sub>) to the board ground plane on each side of the device. This should be done for all SerDes supplies.

The COP function of these processors allows a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert TRST without causing PORESET. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 61 allows the COP to independently assert HRESET or TRST, while ensuring that the target can drive HRESET as well. If the JTAG interface and COP header are not used, TRST should be tied to PORESET so that it is asserted when the system reset signal (PORESET) is asserted.

The COP header shown in Figure 61 adds many benefits—breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features are possible through this interface—and can be as inexpensive as an unpopulated footprint for a header to be added when needed.

The COP interface has a standard header for connection to the target system, based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header).

There is no standardized way to number the COP header shown in Figure 61; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 61 is common to all known emulators.

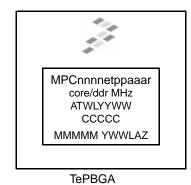

## 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8313E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | е                                       | t                                       | рр                                              | aa                                           | а                          | X                                            |

|-----------------|--------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------|----------------------------------------------|----------------------------|----------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range <sup>3</sup>       | Package <sup>1, 4</sup>                         | e300 core<br>Frequency <sup>2</sup>          | DDR<br>Frequency           | Revision<br>Level                            |

| MPC             | 8313               | Blank = Not<br>included<br>E = included | Blank = 0° to 105°C<br>C= -40° to 105°C | ZQ = PB<br>TEPBGAII<br>VR = PB free<br>TEPBGAII | AD = 266 MHz<br>AF = 333 MHz<br>AG = 400 MHz | D = 266 MHz<br>F = 333 MHz | Blank = 1.0<br>A = 2.0<br>B = 2.1<br>C = 2.2 |

### Table 72. Part Numbering Nomenclature

Note:

1. See Section 19, "Package and Pin Listings," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

- 3. Contact local Freescale office on availability of parts with °C temperature range.

- 4. ZQ package was available for Rev 1.0. For Rev 2.x, only VR package is available.

### 23.2 Part Marking

Parts are marked as shown in this figure.

Notes:

MPCnnnnetppaar is the orderable part number. ATWLYYWW is the standard assembly, test, year, and work week codes. CCCCC is the country code. MMMMM is the mask number.

Figure 62. Part Marking for TEPBGAII Device

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 10/2008 | <ul> <li>Added Note "The information in this document is accurate for revision 1.0, and 2.x and later. See Section 24.1, "Part Numbers Fully Addressed by this Document," before Section 1, "Overview."</li> <li>Added part Numbering details for all the silicon revisions in Table 74.</li> <li>Changed V<sub>IH</sub> from 2.7 V to 2.4 V in Table 7.</li> <li>Added a column for maximum power dissipation in low power mode for Rev 2.x or later silicon in Table 6.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added a column for Power Nos for Rev 2.x or later silicon and added a row for 400 MHz in Table 4.</li> <li>Added Table 21 for DDR AC Specs on Rev 2.x or later silicon.</li> <li>Added EfWE, LFCLE, LFALE, LOE, LFRE, LFWP, LGTA, LUPWAIT, and LFRB in Table 63.</li> <li>In Table 39, added note 2: "This parameter is dependent on the csb_clk speed. (The MIIMCFG[Mgmt Clock Select] field determines the clock frequency of the Mgmt Clock EC_MDC.)"</li> <li>Removed mentions of SGMII (SGMII has separate specs) from Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics."</li> <li>Corrected Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/SGMII/RTBI Electrical Characteristics," to state that RGMII/RTBI Interfaces only operate at 2.5 V, not 3.3 V.</li> <li>Added ZQ package to ordering information In Table 74 and Section 19.1, "Package Parameters for the MPC8313E TEPBGAII" (applicable to both silicon rev. 1.0 and 2.1)</li> <li>Removed footnotes 5 and 6 from Table 1 (left over when the PCI undershoot/overshoot voltages and maximum AC waveforms were removed from Section 2.1.2, "Power Supply Voltage Specification").</li> <li>Removed SD_PLL_TPD (T2) and SD_PLL_TPA_ANA (R4) from Table 63.</li> <li>Added Section 8.3, "SGMII Interface Electrical Characteristics." Removed Section 8.5.3 SGMII DC Electrical Characteristics.</li> <li>Removed "HRESET negation to S</li></ul> |

### Table 73. Document Revision History (continued)

-

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 3/2008 | <ul> <li>In Table 63, added LBC_PM_REF_10 &amp; LSRCID3 as muxed with USBDR_PCTL1</li> <li>In Table 63, added LSRCID2 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL2 VBUS</li> <li>In Table 63, moved 71, U2,&amp; V2 from V<sub>DD</sub> to XCOREVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; V4 from V<sub>SS</sub> to XCOREVDS.</li> <li>In Table 63, added impedance control requirements for SD_IMP_CAL_TX (100 ohms to GND) and SD_IMP_CAL_RX (200 ohms to GND).</li> <li>In Table 63, updated muxing in pinout to show new options for selecting IEEE 1588 functionality. Added footnote 8</li> <li>In Table 63, updated muxing in pinout to show new LBC ECC boot enable control muxed with eTSEC1_MDC</li> <li>Added pin type information for power supplies.</li> <li>Removed N1 and N3 from Vss section of Table 63. Added Therm0 and Therm1 (N1 and N3, respectively). Added note 7 to state: "Internal thermally sensitive resistor, resistor value varies linearly with temperature."</li> <li>In Table 65 corrected maximum frequency of Local Bus Frequency from "33–66" to 66 MHz</li> <li>In Table 65 corrected maximum frequency of PCI from "24–66" to 66 MHz</li> <li>Added "which is determined by RCWLR[COREPLL]" to the note in Section 20.2, "Core PLL Configuration" about the VCO divider.</li> <li>Added "Walues.</li> <li>In Table 69, notes were confusing. Added note 3 for VCO column, note 4 for CSB (<i>csb_c.lk</i>) column, note 5 for USB ref column, and note 6 to replace "Note 1". Clarified note 4 to explain errature of Section 20.2, "Core PLL Configuration" about the VCO divider column in Table 68. Added footnote stating that core_clk frequency must not exceed its maximum, so 2.5:1 and 3:1 <i>core_clk:csb_c.lk</i> ratios are invalid for certain <i>csb_c.lk</i> values.</li> <li>In Table 69, updated note 6 to specify U</li></ul> |

| 0              | 6/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |