#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 267MHz                                                     |

| Co-Processors/DSP               |                                                            |

| RAM Controllers                 | DDR, DDR2                                                  |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers |                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                        |

| SATA                            | -                                                          |

| USB                             | USB 2.0 + PHY (1)                                          |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | -                                                          |

| Package / Case                  | 516-BBGA Exposed Pad                                       |

| Supplier Device Package         | 516-TEPBGA (27x27)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8313vraddb |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

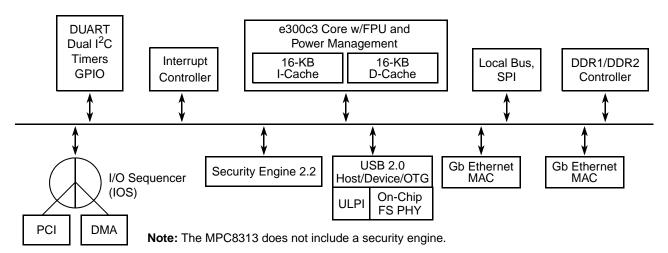

# 1 Overview

The MPC8313E incorporates the e300c3 core, which includes 16 Kbytes of L1 instruction and data caches and on-chip memory management units (MMUs). The MPC8313E has interfaces to dual enhanced three-speed 10/100/1000 Mbps Ethernet controllers, a DDR1/DDR2 SDRAM memory controller, an enhanced local bus controller, a 32-bit PCI controller, a dedicated security engine, a USB 2.0 dual-role controller and an on-chip high-speed PHY, a programmable interrupt controller, dual I<sup>2</sup>C controllers, a 4-channel DMA controller, and a general-purpose I/O port. This figure shows a block diagram of the MPC8313E.

## Figure 1. MPC8313E Block Diagram

The MPC8313E security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES, 3DES, AES, SHA-1, and MD-5 algorithms.

# 1.1 MPC8313E Features

The following features are supported in the MPC8313E:

- Embedded PowerPC<sup>TM</sup> e300 processor core built on Power Architecture<sup>TM</sup> technology; operates at up to 333 MHz.

- High-performance, low-power, and cost-effective host processor

- DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both DDR1 and DDR2

- 16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

- Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced local bus interface with up to 66-MHz operation, and USB 2.0 (high speed) with an on-chip PHY.

- Security engine provides acceleration for control and data plane security protocols

- Power management controller for low-power consumption

- High degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration

# 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

# 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

# 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

# 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

# **3** Power Characteristics

The estimated typical power dissipation, not including I/O supply power, for this family of MPC8313E devices is shown in this table. Table 5 shows the estimated typical I/O power dissipation.

| Core Frequency<br>(MHz) | CSB Frequency<br>(MHz) | Typical <sup>2</sup> | Maximum for<br>Rev. 1.0 Silicon <sup>3</sup> | Maximum for<br>Rev. 2.x or Later Silicon <sup>3</sup> | Unit |

|-------------------------|------------------------|----------------------|----------------------------------------------|-------------------------------------------------------|------|

| 333                     | 167                    | 820                  | 1020                                         | 1200                                                  | mW   |

| 400                     | 133                    | 820                  | 1020                                         | 1200                                                  | mW   |

## Table 4. MPC8313E Power Dissipation<sup>1</sup>

## Note:

The values do not include I/O supply power or AV<sub>DD</sub>, but do include core, USB PLL, and a portion of SerDes digital power (not including XCOREV<sub>DD</sub>, XPADV<sub>DD</sub>, or SDAV<sub>DD</sub>, which all have dedicated power supplies for the SerDes PHY).

2. Typical power is based on a voltage of  $V_{DD}$  = 1.05 V and an artificial smoker test running at room temperature.

3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoker test.

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                                                                                                                                                                                                          | Parameter           | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|--------------------------|

| DDR 1, 60% utilization,<br>50% read/write                                                                                                                                                                                          | 333 MHz,<br>32 bits | _                           | 0.355                       | _                           | _                                                   | —                                                   | _                           | W    |                          |

| $\label{eq:Rs} \begin{array}{l} R_{s} = 22 \; \Omega \\ R_{t} = 50 \; \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data} = 8 \; pF, \\ \text{control address} = 8 \; pF, \\ \text{clock} = 8 \; pF \end{array}$ | 266 MHz,<br>32 bits | _                           | 0.323                       | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| DDR 2, 60% utilization,<br>50% read/write                                                                                                                                                                                          | 333 MHz,<br>32 bits | 0.266                       | —                           | _                           | _                                                   | —                                                   | _                           | W    | —                        |

| $\begin{array}{l} R_{s} = 22 \; \Omega \\ R_{t} = 75 \; \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data = 8 pF,} \\ \text{control address = 8 pF,} \\ \text{clock = 8 pF} \end{array}$                        | 266 MHz,<br>32 bits | 0.246                       | _                           | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| PCI I/O load = 50 pF                                                                                                                                                                                                               | 33 MHz              | —                           | —                           | 0.120                       |                                                     | _                                                   | —                           | W    | —                        |

|                                                                                                                                                                                                                                    | 66 MHz              |                             |                             | 0.249                       |                                                     | —                                                   | —                           | W    | —                        |

| Local bus I/O load = 20 pF                                                                                                                                                                                                         | 66 MHz              |                             |                             |                             |                                                     | —                                                   | 0.056                       | W    | —                        |

|                                                                                                                                                                                                                                    | 50 MHz              |                             |                             | _                           | _                                                   | —                                                   | 0.040                       | W    | _                        |

| TSEC I/O load = 20 pF                                                                                                                                                                                                              | MII,<br>25 MHz      | —                           | —                           | —                           | 0.008                                               | —                                                   | —                           | W    | Multiple by<br>number of |

|                                                                                                                                                                                                                                    | RGMII,<br>125 MHz   | —                           | _                           | —                           | 0.078                                               | 0.044                                               | —                           | W    | interface used           |

Table 5. MPC8313E Typical I/O Power Dissipation

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Max                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz,  $T_A$  = 25°C,  $V_{OUT}$  =  $GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.3                      | 2.7                      | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |      |

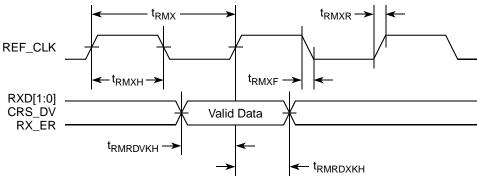

# 8.2.1.4 RMII Receive AC Timing Specifications

This table provides the RMII receive AC timing specifications.

### Table 29. RMII Receive AC Timing Specifications

At recommended operating conditions with NV<sub>DD</sub> of 3.3 V  $\pm$  0.3 V.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock period                                                   | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _   | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                          | t <sub>RMRDVKH</sub>                | 4.0 | _   | —   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                           | t <sub>RMRDXKH</sub>                | 2.0 | -   | —   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>                   | 1.0 | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

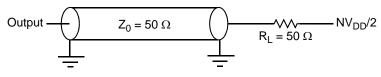

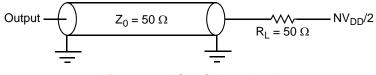

This table provides the AC test load.

Figure 12. AC Test Load

This table shows the RMII receive AC timing diagram.

Figure 13. RMII Receive AC Timing Diagram

Table 33. SGMII DC Receiver Electrical Characteristics (continued)

| Parameter                 | Symbol          | Min | Тур                   | Мах | Unit | Note |

|---------------------------|-----------------|-----|-----------------------|-----|------|------|

| Common mode input voltage | V <sub>CM</sub> | _   | V <sub>xcorevss</sub> | —   | V    | 4    |

Notes:

1. Input must be externally AC-coupled.

2.  $V_{RX\_DIFFp-p}$  is also referred to as peak to peak input differential voltage

3.  $V_{CM\_ACp-p}$  is also referred to as peak to peak AC common mode voltage.

4. On-chip termination to XCOREV<sub>SS</sub>.

# 8.3.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs  $(TX[n] \text{ and } \overline{TX}[n])$  or at the receiver inputs  $(RX[n] \text{ and } \overline{RX}[n])$  as depicted in Figure 18, respectively.

## 8.3.4.1 SGMII Transmit AC Timing Specifications

This table provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### Table 34. SGMII Transmit AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                           | Symbol            | Min    | Тур | Мах    | Unit   | Note |

|-------------------------------------|-------------------|--------|-----|--------|--------|------|

| Deterministic jitter                | JD                | _      | _   | 0.17   | UI p-p |      |

| Total jitter                        | JT                | —      | _   | 0.35   | UI p-p |      |

| Unit interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 1    |

| V <sub>OD</sub> fall time (80%–20%) | tfall             | 50     | _   | 120    | ps     |      |

| V <sub>OD</sub> rise time (20%–80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     |      |

Note:

1. Each UI is 800 ps  $\pm$  100 ppm.

## 8.3.4.2 SGMII Receive AC Timing Specifications

This table provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 17 shows the SGMII receiver input compliance mask eye diagram.

## Table 35. SGMII Receive AC Timing Specifications

At recommended operating conditions with XCOREV<sub>DD</sub> = 1.0 V  $\pm$  5%.

| Parameter                                          | Symbol | Min  | Тур | Max | Unit   | Note |

|----------------------------------------------------|--------|------|-----|-----|--------|------|

| Deterministic jitter tolerance                     | JD     | 0.37 | —   | —   | UI p-p | 1    |

| Combined deterministic and random jitter tolerance | JDR    | 0.55 | —   | —   | UI p-p | 1    |

| Sinusoidal jitter tolerance                        | JSIN   | 0.1  | —   | —   | UI p-p | 1    |

of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

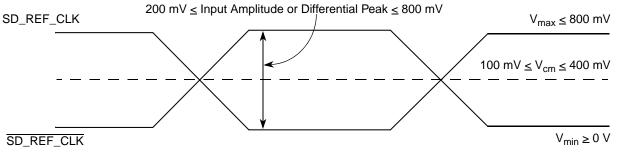

- For external DC-coupled connection, as described in Section 9.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 24 shows the SerDes reference clock input requirement for the DC-coupled connection scheme.

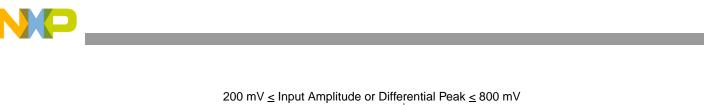

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to  $XCOREV_{SS}$ . Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage ( $XCOREV_{SS}$ ). Figure 25 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

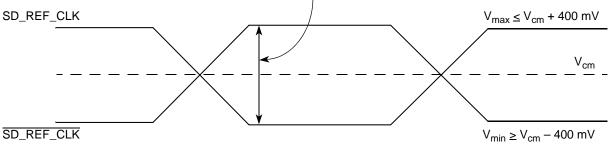

- Single-ended mode

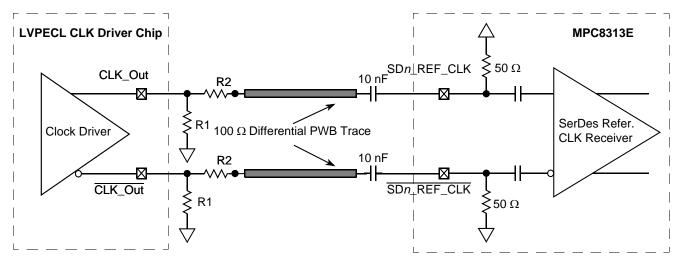

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 26 shows the SerDes reference clock input requirement for the single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC coupled externally. For the best noise performance, the reference of the clock could be DC or AC coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 24. Differential Reference Clock Input DC Requirements (External DC-Coupled)

Figure 25. Differential Reference Clock Input DC Requirements (External AC-Coupled)

# 9.2.3 Interfacing With Other Differential Signaling Levels

- With on-chip termination to XCOREV<sub>SS</sub>, the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC coupled.

- Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

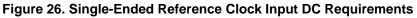

- LVPECL outputs can produce a signal with too large of an amplitude and may need to be DC-biased at the clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC coupling.

## NOTE

Figure 27 through Figure 30 are for conceptual reference only. Due to the fact that the clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is possible that the clock circuit reference designs provided by clock driver chip vendors are different from what is shown in the figures. They might also vary from one vendor to the other. Therefore, Freescale can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. It is recommended that the system designer contact the selected clock driver chip vendor for the optimal reference circuits for the MPC8313E SerDes reference clock receiver requirement provided in this document.

assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8313E SerDes3 reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult with the clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 29. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the MPC8313E SerDes reference clock input's DC requirement.

Figure 30. Single-Ended Connection (Reference Only)

# 9.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low-phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

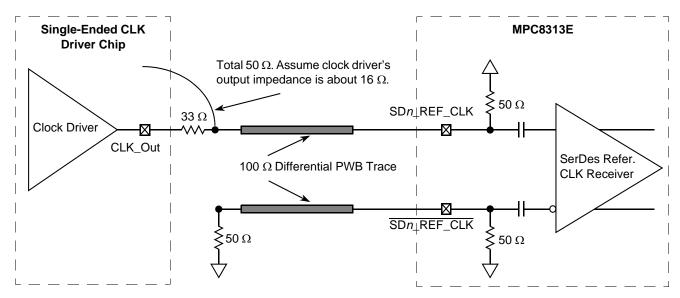

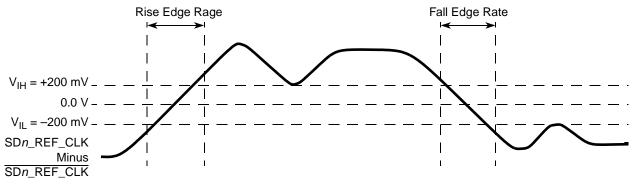

This table describes some AC parameters for SGMII protocol.

## Table 39. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with  $XV_{DD\_SRDS1}$  or  $XV_{DD\_SRDS2}$  = 1.0 V ± 5%.

| Parameter                                                                  | Symbol             | Min  | Max  | Unit | Note |

|----------------------------------------------------------------------------|--------------------|------|------|------|------|

| Rising edge rate                                                           | Rise edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Falling edge rate                                                          | Fall edge rate     | 1.0  | 4.0  | V/ns | 2, 3 |

| Differential input high voltage                                            | V <sub>IH</sub>    | +200 | —    | mV   | 2    |

| Differential input low voltage                                             | V <sub>IL</sub>    | _    | -200 | mV   | 2    |

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-fall matching | _    | 20   | %    | 1, 4 |

#### Notes:

- 1. Measurement taken from single-ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from –200 to +200 mV on the differential waveform (derived from SD*n*\_REF\_CLK minus SD*n*\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 31.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point, where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The rise edge rate of SDn\_REF\_CLK should be compared to the fall edge rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 32.

Figure 31. Differential Measurement Points for Rise and Fall Time

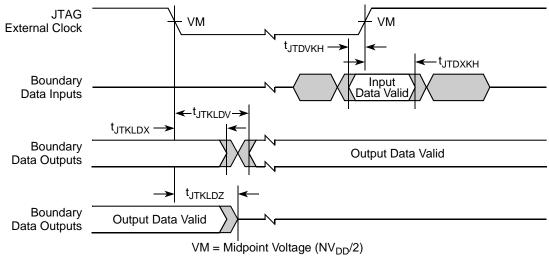

This figure provides the boundary-scan timing diagram.

Figure 44. Boundary-Scan Timing Diagram

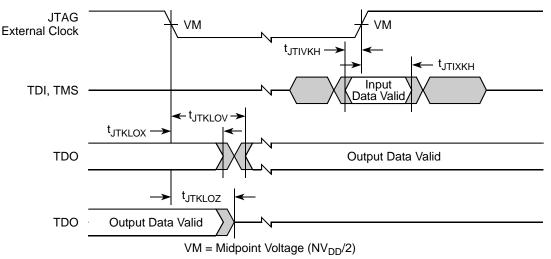

This figure provides the test access port timing diagram.

## Figure 45. Test Access Port Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface.

# **13.1** I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interface.

## Table 48. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with NV\_{DD} of 3.3 V  $\pm$  0.3 V.

| Parameter                                                                                     | Symbol              | Min                       | Мах                                    | Unit | Note |

|-----------------------------------------------------------------------------------------------|---------------------|---------------------------|----------------------------------------|------|------|

| Input high voltage level                                                                      | V <sub>IH</sub>     | $0.7 	imes NV_{DD}$       | NV <sub>DD</sub> + 0.3                 | V    |      |

| Input low voltage level                                                                       | V <sub>IL</sub>     | -0.3                      | $0.3 	imes NV_{DD}$                    | V    |      |

| Low level output voltage                                                                      | V <sub>OL</sub>     | 0                         | $0.2 \times \mathrm{NV}_{\mathrm{DD}}$ | V    | 1    |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF | <sup>t</sup> I2KLKV | 20 + 0.1 × C <sub>B</sub> | 250                                    | ns   | 2    |

| Pulse width of spikes which must be suppressed by the input filter                            | t <sub>i2KHKL</sub> | 0                         | 50                                     | ns   | 3    |

| Capacitance for each I/O pin                                                                  | CI                  | —                         | 10                                     | pF   |      |

| Input current, (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> )                          | I <sub>IN</sub>     | —                         | ± 5                                    | μΑ   | 4    |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2.  $C_B$  = capacitance of one bus line in pF.

- 3. Refer to the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for information on the digital filter used.

- 4. I/O pins obstruct the SDA and SCL lines if  $\mathsf{NV}_{\mathsf{DD}}$  is switched off.

# 13.2 I<sup>2</sup>C AC Electrical Specifications

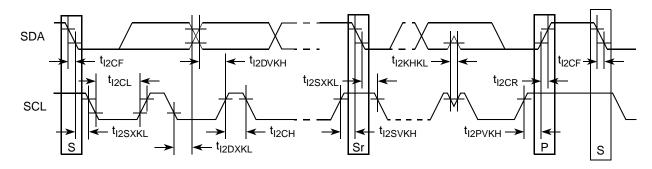

This table provides the AC timing parameters for the  $I^2C$  interface.

## Table 49. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 48).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Мах | Unit |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400 | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —   | μS   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | _   | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | —   | μS   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | —   | μS   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 |     | ns   |

This figure shows the AC timing diagram for the  $I^2C$  bus.

Figure 47. I<sup>2</sup>C Bus AC Timing Diagram

# 14 PCI

This section describes the DC and AC electrical specifications for the PCI bus.

# 14.1 PCI DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI interface.

Table 50. PCI DC Electrical Characteristics<sup>1</sup>

| Parameter                 | Symbol          | Test Condition                          | Min                               | Max                    | Unit |

|---------------------------|-----------------|-----------------------------------------|-----------------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or           | $0.5\times \text{NV}_{\text{DD}}$ | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)              | -0.5                              | $0.3 	imes NV_{DD}$    | V    |

| High-level output voltage | V <sub>OH</sub> | $NV_{DD} = min, I_{OH} = -100 \ \mu A$  | $0.9 	imes NV_{DD}$               | —                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | $NV_{DD}$ = min, $I_{OL}$ = 100 $\mu$ A | _                                 | $0.1 \times NV_{DD}$   | V    |

| Input current             | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$          | _                                 | ±5                     | μA   |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $NV_{IN}$  symbol referenced in Table 1 and Table 2.

# 14.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the MPC8313E is configured as a host or agent device.

This table shows the PCI AC timing specifications at 66 MHz.

Table 51. PCI AC Timing Specifications at 66 MHz

| Parameter              | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|------------------------|---------------------|-----|-----|------|------|

| Clock to output valid  | <sup>t</sup> PCKHOV | —   | 6.0 | ns   | 2    |

| Output hold from clock | t <sub>PCKHOX</sub> | 1   | —   | ns   | 2    |

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|--------------------------------|---------------------|-----|-----|------|------|

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3 |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 2, 4 |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | —   | ns   | 2, 4 |

## Table 51. PCI AC Timing Specifications at 66 MHz (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

## This table shows the PCI AC timing specifications at 33 MHz.

## Table 52. PCI AC Timing Specifications at 33 MHz

| Parameter                      | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|--------------------------------|---------------------|-----|-----|------|------|

| Clock to output valid          | <sup>t</sup> PCKHOV | —   | 11  | ns   | 2    |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | _   | ns   | 2    |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3 |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 |     | ns   | 2, 4 |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns   | 2, 4 |

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

This figure provides the AC test load for PCI.

Figure 48. PCI AC Test Load

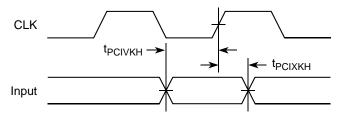

This figure shows the PCI input AC timing conditions.

Figure 49. PCI Input AC Timing Measurement Conditions

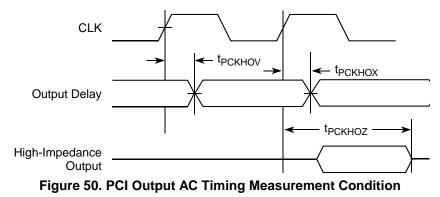

This figure shows the PCI output AC timing conditions.

# 15 Timers

This section describes the DC and AC electrical specifications for the timers.

# **15.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the MPC8313E timers pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Characteristic      | Symbol          | Condition                        | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA        | 2.4  |                        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA         | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA         | —    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \leq V_{IN} \leq NV_{DD}$ | _    | ±5                     | μA   |

**Table 53. Timers DC Electrical Characteristics**

| Signal     | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|------------|--------------------|----------|------------------|------|

| MEMC_MDQ29 | A20                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDQ30 | C22                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQ31 | B22                | I/O      | GV <sub>DD</sub> |      |

| MEMC_MDM0  | B7                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM1  | E6                 | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM2  | E18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDM3  | E20                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MDQS0 | A7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS1 | E7                 | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS2 | B19                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MDQS3 | A23                | I/O      | GV <sub>DD</sub> | _    |

| MEMC_MBA0  | D15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA1  | A18                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MBA2  | A15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA0   | E12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA1   | D11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA2   | B11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA3   | A11                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA4   | A12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA5   | E13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA6   | C12                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA7   | E14                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA8   | B15                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA9   | C17                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA10  | C13                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA11  | A16                | 0        | GV <sub>DD</sub> | _    |

| MEMC_MA12  | C15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA13  | C16                | 0        | GV <sub>DD</sub> |      |

| MEMC_MA14  | E15                | 0        | GV <sub>DD</sub> |      |

| MEMC_MWE   | B18                | 0        | GV <sub>DD</sub> |      |

| MEMC_MRAS  | C11                | 0        | GV <sub>DD</sub> |      |

| MEMC_MCAS  | B10                | 0        | GV <sub>DD</sub> |      |

## Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Signal                      | Package Pin Number | Pin Type | Power<br>Supply  | Note |

|-----------------------------|--------------------|----------|------------------|------|

| LA24                        | E23                | 0        | LV <sub>DD</sub> | 11   |

| LA25                        | D22                | 0        | LV <sub>DD</sub> | 11   |

| LCS0                        | D23                | 0        | LV <sub>DD</sub> | 10   |

| LCS1                        | J26                | 0        | LV <sub>DD</sub> | 10   |

| LCS2                        | F22                | 0        | LV <sub>DD</sub> | 10   |

| LCS3                        | D26                | 0        | LV <sub>DD</sub> | 10   |

| LWE0/LFWE                   | E24                | 0        | LV <sub>DD</sub> | 10   |

| LWE1                        | H26                | 0        | LV <sub>DD</sub> | 10   |

| LBCTL                       | L22                | 0        | LV <sub>DD</sub> | 10   |

| LALE/M1LALE/M2LALE          | E26                | 0        | LV <sub>DD</sub> | 11   |

| LGPL0/LFCLE                 | AA23               | 0        | LV <sub>DD</sub> |      |

| LGPL1/LFALE                 | AA24               | 0        | LV <sub>DD</sub> |      |

| LGPL2/LOE/LFRE              | AA25               | 0        | LV <sub>DD</sub> | 10   |

| LGPL3/LFWP                  | AA26               | 0        | LV <sub>DD</sub> |      |

| LGPL4/LGTA/LUPWAIT/LFRB     | Y22                | I/O      | LV <sub>DD</sub> | 2    |

| LGPL5                       | E21                | 0        | LV <sub>DD</sub> | 10   |

| LCLK0                       | H22                | 0        | LV <sub>DD</sub> | 11   |

| LCLK1                       | G26                | 0        | LV <sub>DD</sub> | 11   |

| LA0/GPIO0/MSRCID0           | AC24               | I/O      | LV <sub>DD</sub> |      |

| LA1/GPIO1//MSRCID1          | Y24                | I/O      | LV <sub>DD</sub> |      |

| LA2/GPIO2//MSRCID2          | Y26                | I/O      | LV <sub>DD</sub> |      |

| LA3/GPIO3//MSRCID3          | W22                | I/O      | LV <sub>DD</sub> |      |

| LA4/GPIO4//MSRCID4          | W24                | I/O      | LV <sub>DD</sub> |      |

| LA5/GPIO5/MDVAL             | W26                | I/O      | LV <sub>DD</sub> |      |

| LA6/GPIO6                   | V22                | I/O      | LV <sub>DD</sub> |      |

| LA7/GPIO7/TSEC_1588_TRIG2   | V23                | I/O      | LV <sub>DD</sub> | 8    |

| LA8/GPIO13/TSEC_1588_ALARM1 | V24                | I/O      | LV <sub>DD</sub> | 8    |

| LA9/GPIO14/TSEC_1588_PP3    | V25                | I/O      | LV <sub>DD</sub> | 8    |

| LA10/TSEC_1588_CLK          | V26                | 0        | LV <sub>DD</sub> | 8    |

| LA11/TSEC_1588_GCLK         | U22                | 0        | LV <sub>DD</sub> | 8    |

| LA12/TSEC_1588_PP1          | AD24               | 0        | LV <sub>DD</sub> | 8    |

| LA13/TSEC_1588_PP2          | L25                | 0        | LV <sub>DD</sub> | 8    |

## Table 62. MPC8313E TEPBGAII Pinout Listing (continued)

| Unit                                      | Default<br>Frequency | Options                            |

|-------------------------------------------|----------------------|------------------------------------|

| TSEC1                                     | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| TSEC2                                     | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| Security Core, I <sup>2</sup> C, SAP, TPR | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| USB DR                                    | csb_clk              | Off, csb_clk, csb_clk/2, csb_clk/3 |

| PCI and DMA complex                       | csb_clk              | Off, csb_clk                       |

## Table 63. Configurable Clock Units

This table provides the operating frequencies for the MPC8313E TEPBGAII under recommended operating conditions (see Table 2).

| Characteristic <sup>1</sup>                      | Maximum Operating<br>Frequency | Unit |

|--------------------------------------------------|--------------------------------|------|

| e300 core frequency (core_clk)                   | 333                            | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> ) | 167                            | MHz  |

| DDR1/2 memory bus frequency (MCK) <sup>2</sup>   | 167                            | MHz  |

| Local bus frequency (LCLKn) <sup>3</sup>         | 66                             | MHz  |

| PCI input frequency (SYS_CLK_IN or PCI_CLK)      | 66                             | MHz  |

## Table 64. Operating Frequencies for TEPBGAII

#### Note:

- The SYS\_CLK\_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK[0:1], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM] and SCCR[USBDRCM] must be programmed such that the maximum internal operating frequency of the security core and USB modules do not exceed their respective value listed in this table.

- 2. The DDR data rate is 2x the DDR memory bus frequency.

- 3. The local bus frequency is 1/2, 1/4, or 1/8 of the *lbc\_clk* frequency (depending on LCRR[CLKDIV]), which is in turn, 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

# 20.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. This table shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0000       | Reserved                            |

| 0001       | Reserved                            |

| 0010       | × 2                                 |

| 0011       | × 3                                 |

#### Table 65. System PLL Multiplication Factors

# 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8313E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | е                                       | t                                       | рр                                              | aa                                           | а                          | X                                            |

|-----------------|--------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------|----------------------------------------------|----------------------------|----------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range <sup>3</sup>       | Package <sup>1, 4</sup>                         | e300 core<br>Frequency <sup>2</sup>          | DDR<br>Frequency           | Revision<br>Level                            |

| MPC             | 8313               | Blank = Not<br>included<br>E = included | Blank = 0° to 105°C<br>C= -40° to 105°C | ZQ = PB<br>TEPBGAII<br>VR = PB free<br>TEPBGAII | AD = 266 MHz<br>AF = 333 MHz<br>AG = 400 MHz | D = 266 MHz<br>F = 333 MHz | Blank = 1.0<br>A = 2.0<br>B = 2.1<br>C = 2.2 |

## Table 72. Part Numbering Nomenclature

Note:

1. See Section 19, "Package and Pin Listings," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

- 3. Contact local Freescale office on availability of parts with °C temperature range.

- 4. ZQ package was available for Rev 1.0. For Rev 2.x, only VR package is available.

# 23.2 Part Marking

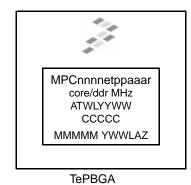

Parts are marked as shown in this figure.

Notes:

MPCnnnnetppaar is the orderable part number. ATWLYYWW is the standard assembly, test, year, and work week codes. CCCCC is the country code. MMMMM is the mask number.

Figure 62. Part Marking for TEPBGAII Device

\_\_\_\_\_

| Rev.<br>Number | Date   | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1              | 3/2008 | <ul> <li>In Table 63, added LBC_PM_REF_10 &amp; LSRCID3 as muxed with USBDR_PCTL1</li> <li>In Table 63, added LSRCID2 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL0</li> <li>In Table 63, added LSRCID0 as muxed with USBDR_PCTL2 VBUS</li> <li>In Table 63, moved 71, U2,&amp; V2 from V<sub>DD</sub> to XCOREVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; U4 from V<sub>DD</sub> to XPADVDD.</li> <li>In Table 63, moved P5, &amp; V4 from V<sub>SS</sub> to XCOREVDS.</li> <li>In Table 63, added impedance control requirements for SD_IMP_CAL_TX (100 ohms to GND) and SD_IMP_CAL_RX (200 ohms to GND).</li> <li>In Table 63, updated muxing in pinout to show new options for selecting IEEE 1588 functionality. Added footnote 8</li> <li>In Table 63, updated muxing in pinout to show new LBC ECC boot enable control muxed with eTSEC1_MDC</li> <li>Added pin type information for power supplies.</li> <li>Removed N1 and N3 from Vss section of Table 63. Added Therm0 and Therm1 (N1 and N3, respectively). Added note 7 to state: "Internal thermally sensitive resistor, resistor value varies linearly with temperature."</li> <li>In Table 65 corrected maximum frequency of Local Bus Frequency from "33–66" to 66 MHz</li> <li>In Table 65 corrected maximum frequency of PCI from "24–66" to 66 MHz</li> <li>Added "which is determined by RCWLR[COREPLL]" to the note in Section 20.2, "Core PLL Configuration" about the VCO divider.</li> <li>Added "Walues.</li> <li>In Table 69, notes were confusing. Added note 3 for VCO column, note 4 for CSB (<i>csb_c.lk</i>) column, note 5 for USB ref column, and note 6 to replace "Note 1". Clarified note 4 to explain errature of Section 20.2, "Core PLL Configuration" about the VCO divider column in Table 68. Added footnote stating that core_clk frequency must not exceed its maximum, so 2.5:1 and 3:1 <i>core_clk:csb_c.lk</i> ratios are invalid for certain <i>csb_c.lk</i> values.</li> <li>In Table 69, updated note 6 to specify U</li></ul> |  |  |  |  |

| 0              | 6/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |