Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 72MHz                                                                                    |

| Connectivity               | I²C, IrDA, SPI, UART/USART, USB                                                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                   |

| Number of I/O              | 20                                                                                       |

| Program Memory Size        | 68KB (68K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 20K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 32-WFQFN Exposed Pad                                                                     |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc123zd4an0 |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# NUC123

| 6.15  | I <sup>2</sup> S Controller (I <sup>2</sup> S)63 |

|-------|--------------------------------------------------|

| 6.15. | 1 Overview                                       |

| 6.15. | 2 Features                                       |

| 6.16  | USB Device Controller (USB)64                    |

| 6.16. | 1 Overview                                       |

| 6.16. | 2 Features                                       |

| 6.17  | Analog-to-Digital Converter (ADC)65              |

| 6.17. | 1 Overview                                       |

| 6.17. | 2 Features                                       |

| 7 EL  | ECTRICAL CHARACTERISTICS (NUC123xxxANx)          |

| 7.1   | Absolute Maximum Ratings66                       |

| 7.2   | DC Electrical Characteristics67                  |

| 7.3   | AC Electrical Characteristics71                  |

| 7.3.1 | External 4~24 MHz High Speed Oscillator71        |

| 7.3.2 | External 4~24 MHz High Speed Crystal71           |

| 7.3.3 | Internal 22.1184 MHz High Speed Oscillator72     |

| 7.3.4 | Internal 10 kHz Low Speed Oscillator72           |

| 7.4   | Analog Characteristics73                         |

| 7.4.1 | 10-bit SARADC Specifications73                   |

| 7.4.2 | LDO and Power Management Specifications74        |

| 7.4.3 | Low Voltage Reset Specifications74               |

| 7.4.4 | Brown-out Detector Specifications75              |

| 7.4.5 | Power-On Reset (5V) Specifications75             |

| 7.4.6 | USB PHY Specifications                           |

| 7.5   | Flash DC Electrical Characteristics77            |

| 7.6   | SPI Dynamic Characteristics78                    |

| 8 EL  | ECTRICAL CHARACTERISTICS (NUC123xxxAEx)          |

| 8.1   | Absolute Maximum Ratings80                       |

| 8.2   | DC Electrical Characteristics81                  |

| 8.3   | AC Electrical Characteristics                    |

| 8.3.1 | External 4~24 MHz High Speed Oscillator85        |

| 8.3.2 | External 4~24 MHz High Speed Crystal85           |

| 8.3.3 | Internal 22.1184 MHz High Speed Oscillator86     |

| 8.3.4 | Internal 10 kHz Low Speed Oscillator86           |

| 8.4   | Analog Characteristics                           |

|       |                                                  |

### **1 GENERAL DESCRIPTION**

The NuMicro<sup>®</sup> NUC123 series is a new 32-bit Cortex<sup>®</sup>-M0 microcontroller with USB 2.0 Full-speed devices and a 10-bit ADC. The NUC123 series provides the high 72 MHz operating speed, large 20 Kbytes SRAM, 8 USB endpoints and three sets of SPI controllers, which make it powerful in USB communication and data processing. The NUC123 series is ideal for industrial control, consumer electronics, and communication system applications such as printers, touch panel, gaming keyboard, gaming joystick, USB audio, PC peripherals, and alarm systems.

The NUC123 series runs up to 72 MHz and supports 32-bit multiplier, structure NVIC (Nested Vector Interrupt Control), dual-channel APB and PDMA (Peripheral Direct Memory Access) with CRC function. Besides, the NUC123 series is equipped with 36/68 Kbytes Flash memory, 12/20 Kbytes SRAM, and 4 Kbytes loader ROM for the ISP. It operates at a wide voltage range of 2.5V ~ 5.5V and temperature range of  $-40^{\circ}$ C ~  $+105^{\circ}$ C and  $-40^{\circ}$ C ~  $+85^{\circ}$ C. It is also equipped with plenty of peripheral devices, such as 8-channel 10-bit ADC, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, USB 2.0 FS devices, and offers low-voltage reset and Brown-out detection, PWM (Pulse-width Modulation), capture and compare features, four sets of 32-bit timers, Watchdog Timer, and internal RC oscillator. All these peripherals have been incorporated into the NUC123 series to reduce component count, board space and system cost.

Additionally, the NUC123 series is equipped with ISP (In-System Programming), IAP (In-Application-Programming) and ICP (In-Circuit Programming) functions, which allows the user to update the program under software control through the on-chip connectivity interface, such as SWD, UART and USB.

| Product Line | UART | SPI | l <sup>2</sup> C | USB | PS/2 | l²S | PWM | ADC |

|--------------|------|-----|------------------|-----|------|-----|-----|-----|

| NUC123       | 2    | 3   | 2                | 1   | 1    | 1   | 4   | 8   |

Table 1-1 Key Features Support Table

## 2 FEATURES

### 2.1 NuMicro<sup>®</sup> NUC123 Series Features

- Core

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core runs up to 72 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Supports Serial Wire Debug with 2 watchpoints/4 breakpoints

- Built-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 36/68 KB Flash for program code

- 4 KB flash for ISP loader

- Supports In-System Program (ISP) application code update

- 512 byte page erase for flash

- Configurable Data Flash address and size for both 36KB and 68KB system

- Supports 2-wire ICP update through SWD/ICE interface

- Supports fast parallel programming mode by external programmer

- SRAM Memory

- 12/20 KB embedded SRAM

- Supports PDMA mode

- PDMA (Peripheral DMA)

- Supports 6 channels PDMA for automatic data transfer between SRAM and peripherals such as SPI, UART, I<sup>2</sup>S, USB 2.0 FS device, PWM and ADC

- Supports CRC calculation with four common polynomials, CRC-CCITT, CRC-8, CRC-16 and CRC-32

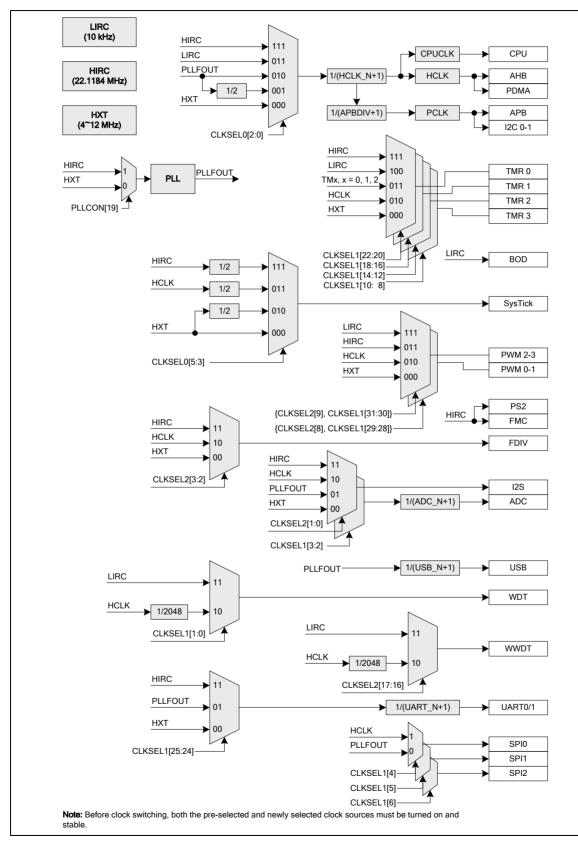

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed oscillator (Trimmed to 1%) for system operation, and low power 10 kHz low speed oscillator for watchdog and wake-up operation

- Supports one PLL, up to 144 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for precise timing operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin configured as interrupt source with edge/level setting

- Supports High Driver and High Sink I/O mode

- Timer

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function

- Watchdog/Windowed-Watchdog Timer

- Multiple clock sources

**NUC123**

- 8 selectable time-out period from 1.6ms ~ 26.0sec (depending on clock source)

- Wake-up from Power-down or Idle mode

- Interrupt or reset selectable on watchdog timer time-out

- Interrupt on windowed-watchdog timer time-out

- Reset on windowed-watchdog timer time-out or reload in an unexpected time window

- PWM/Capture

- Up to two built-in 16-bit PWM generators provided with four PWM outputs or two complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one 8-bit prescaler and one Dead-zone generator for complementary paired PWM

- Up to four 16-bit digital Capture timers (shared with PWM timers) provided with four rising/falling capture inputs

- Supports Capture interrupt

- UART

- Up to two UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0/1 with 16-byte FIFO for standard device

- Support IrDA (SIR) function

- Supports RS-485 9-bit mode and direction control.

- Programmable baud-rate generator up to 1/16 system clock

- Supports PDMA mode

- SPI

- Up to three sets of SPI controllers

- Supports SPI master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Up to two slave/device select lines in Master mode

- Supports Byte Suspend mode in 16/24/32-bit transmission

- Supports PDMA transfer

- I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C devices

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allowing versatile rate control

- Supports multiple address recognition (four slave address with mask option)

- Supports wake-up by address recognition (for 1st slave address only)

- I<sup>2</sup>S

- Interface with external audio CODEC

- Operated as either master or Slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports Mono and stereo audio data

- Supports I<sup>2</sup>S and MSB justified data format

- Two 8 word FIFO data buffers are provided, one for transmitting and the other for receiving

# **3 ABBREVIATIONS**

| Acronym | Description                                     |

|---------|-------------------------------------------------|

| ACMP    | Analog Comparator Controller                    |

| ADC     | Analog-to-Digital Converter                     |

| AES     | Advanced Encryption Standard                    |

| APB     | Advanced Peripheral Bus                         |

| АНВ     | Advanced High-Performance Bus                   |

| BOD     | Brown-out Detection                             |

| CAN     | Controller Area Network                         |

| DAP     | Debug Access Port                               |

| DES     | Data Encryption Standard                        |

| EBI     | External Bus Interface                          |

| EPWM    | Enhanced Pulse Width Modulation                 |

| FIFO    | First In, First Out                             |

| FMC     | Flash Memory Controller                         |

| FPU     | Floating-point Unit                             |

| GPIO    | General-Purpose Input/Output                    |

| HCLK    | The Clock of Advanced High-Performance Bus      |

| HIRC    | 22.1184 MHz Internal High Speed RC Oscillator   |

| НХТ     | 4~20 MHz External High Speed Crystal Oscillator |

| IAP     | In Application Programming                      |

| ICP     | In Circuit Programming                          |

| ISP     | In System Programming                           |

| LDO     | Low Dropout Regulator                           |

| LIN     | Local Interconnect Network                      |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)  |

| MPU     | Memory Protection Unit                          |

| NVIC    | Nested Vectored Interrupt Controller            |

| PCLK    | The Clock of Advanced Peripheral Bus            |

| PDMA    | Peripheral Direct Memory Access                 |

| PLL     | Phase-Locked Loop                               |

| PWM     | Pulse Width Modulation                          |

| QEI     | Quadrature Encoder Interface                    |

| SD      | Secure Digital                                  |

| SPI     | Serial Peripheral Interface                     |

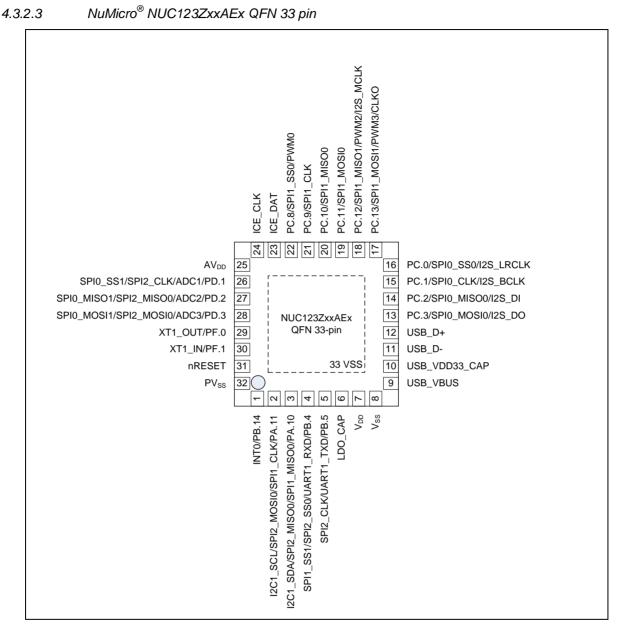

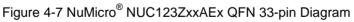

### 5 BLOCK DIAGRAM

# 5.1 NuMicro<sup>®</sup> NUC123 Block Diagram

Figure 5-1 NuMicro<sup>®</sup> NUC123 Block Diagram

#### 6.2.5 System Memory Map

The NuMicro<sup>®</sup> NUC123 series provides 4G-byte addressing space. The memory locations assigned to each on-chip controllers are shown in the Table 6-5. The detailed register definition, memory space, and programming detailed will be described in the following sections for each on-chip peripherals. The NuMicro<sup>®</sup> NUC123 Series only supports little-endian data format.

| Address Space                     | Token            | Controllers                                       |

|-----------------------------------|------------------|---------------------------------------------------|

| Flash and SRAM Memory Space       |                  |                                                   |

| 0x0000_0000 – 0x0000_FFFF         | FLASH_BA         | FLASH Memory Space (64KB)                         |

| 0x2000_0000 – 0x2000_4FFF         | SRAM_BA          | SRAM Memory Space (20KB)                          |

| AHB Controllers Space (0x5000_00  | 00 – 0x501F_FFFF | F)                                                |

| 0x5000_0000 – 0x5000_01FF         | GCR_BA           | System Global Control Registers                   |

| 0x5000_0200 – 0x5000_02FF         | CLK_BA           | Clock Control Registers                           |

| 0x5000_0300 – 0x5000_03FF         | INT_BA           | Interrupt Multiplexer Control Registers           |

| 0x5000_4000 – 0x5000_7FFF         | GPIO_BA          | GPIO Control Registers                            |

| 0x5000_8000 – 0x5000_BFFF         | PDMA_BA          | Peripheral DMA Control Registers                  |

| 0x5000_C000 – 0x5000_FFFF         | FMC_BA           | Flash Memory Control Registers                    |

| APB1 Controllers Space (0x4000_0  | 000 ~ 0x400F_FFF | F)                                                |

| 0x4000_4000 – 0x4000_7FFF         | WDT_BA           | Watchdog/Window Watchdog Timer Control Registers  |

| 0x4001_0000 – 0x4001_3FFF         | TMR01_BA         | Timer0/Timer1 Control Registers                   |

| 0x4002_0000 – 0x4002_3FFF         | I2C0_BA          | I <sup>2</sup> C0 Interface Control Registers     |

| 0x4003_0000 – 0x4003_3FFF         | SPI0_BA          | SPI0 with master/slave function Control Registers |

| 0x4003_4000 – 0x4003_7FFF         | SPI1_BA          | SPI1 with master/slave function Control Registers |

| 0x4004_0000 – 0x4004_3FFF         | PWMA_BA          | PWM0/1/2/3 Control Registers                      |

| 0x4005_0000 – 0x4005_3FFF         | UART0_BA         | UART0 Control Registers                           |

| 0x4006_0000 – 0x4006_3FFF         | USBD_BA          | USB 2.0 FS device Controller Registers            |

| 0x400E_0000 - 0x400E_FFFF         | ADC_BA           | Analog-Digital-Converter (ADC) Control Registers  |

| APB2 Controllers Space (0x4010_0  | 000 ~ 0x401F_FFF | F)                                                |

| 0x4010_0000 – 0x4010_3FFF         | PS2_BA           | PS/2 Interface Control Registers                  |

| 0x4011_0000 – 0x4011_3FFF         | TMR23_BA         | Timer2/Timer3 Control Registers                   |

| 0x4012_0000 – 0x4012_3FFF         | I2C1_BA          | I <sup>2</sup> C1 Interface Control Registers     |

| 0x4013_0000 – 0x4013_3FFF         | SPI2_BA          | SPI2 with master/slave function Control Registers |

| 0x4015_0000 – 0x4015_3FFF         | UART1_BA         | UART1 Control Registers                           |

| 0x401A_0000 – 0x401A_3FFF         | I2S_BA           | I <sup>2</sup> S Interface Control Registers      |

| System Controllers Space (0xE000_ | _E000 ~ 0xE000_E | :FFF)                                             |

| 0xE000_E010 - 0xE000_E0FF         | SCS_BA           | System Timer Control Registers                    |

# NUC123

#### 6.8 PWM Generator and Capture Timer (PWM)

#### 6.8.1 Overview

The NuMicro<sup>®</sup> NUC123 series has 1 set of PWM group supporting 1 set of PWM generators which can be configured as 4 independent PWM outputs, PWM0~PWM3, or as 2 complementary PWM pairs, (PWM0, PWM1), (PWM2, PWM3) with two programmable dead-zone generators. PWM output function can be alternated to capture function.

Each PWM generator has one 8-bit prescaler, one clock divider with 5 divided frequencies (1, 1/2, 1/4, 1/8, 1/16), two PWM Timers including two clock selectors, two 16-bit PWM down-counters for PWM period control, two 16-bit comparators for PWM duty control and one dead-zone generator. The PWM generators provide four independent PWM interrupt flags which are set by hardware when the corresponding PWM period down counter reaches zero.

Each PWM interrupt source with its corresponding enable bit can cause CPU to request PWM interrupt. The PWM generators can be configured as one-shot mode to produce only one PWM cycle signal or auto-reload mode to output PWM waveform continuously. PWM can be used to trigger ADC when operation in center-aligned mode.

#### 6.8.2 Features

PWM function:

- Up to 1 PWM group (PWMA) to support 4 PWM channels or 2 PWM paired channels

- Supports 8-bit prescaler from 1 to 255

- Up to 16-bit resolution PWM timer

- PWM timer supports down and up-down operation type

- One-shot or Auto-reload mode PWM

- PWM Interrupt request synchronized with PWM period or duty

- Supports dead-zone generator with 8-bit resolution for 2 PWM paired channels

- Supports trigger ADC on center point in center-aligned mode

#### Capture function:

- Supports 4 Capture input channels shared with 4 PWM output channels

- Supports rising or falling capture condition

- Supports rising or falling capture interrupt

- Supports PDMA transfer function for each channel

### 6.12 PS/2 Device Controller (PS2D)

#### 6.12.1 Overview

PS/2 device controller provides basic timing control for PS/2 communication. All communication between the device and the host is managed through the CLK and DATA pins. Unlike PS/2 keyboard or mouse device controller, the received/transmit code needs to be translated as meaningful code by firmware. The device controller generates the CLK signal after receiving a request to send, but host has ultimate control over communication. DATA sent from the host to the device is read on the rising edge and DATA sent from device to the host is change after rising edge. A 16 bytes FIFO is used to reduce CPU intervention. Software can select 1 to 16 bytes for a continuous transmission.

#### 6.12.2 Features

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

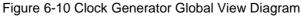

### 7.3 AC Electrical Characteristics

#### 7.3.1 External 4~24 MHz High Speed Oscillator

Note: Duty cycle is 50%.

| SYMBOL            | PARAMETER       | CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|-----------------|------------|-----|-----|-----|------|

| t <sub>CHCX</sub> | Clock High Time |            | 10  | -   | -   | nS   |

| t <sub>CLCX</sub> | Clock Low Time  |            | 10  | -   | -   | nS   |

| t <sub>CLCH</sub> | Clock Rise Time |            | 2   | -   | 15  | nS   |

| t <sub>CHCL</sub> | Clock Fall Time |            | 2   | -   | 15  | nS   |

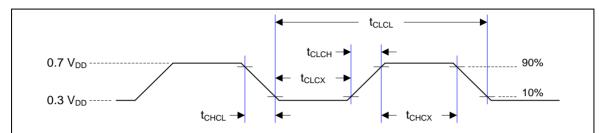

# 7.3.2 External 4~24 MHz High Speed Crystal

| PARAMETER             | CONDITIONS       | MIN | ТҮР | МАХ | UNIT |

|-----------------------|------------------|-----|-----|-----|------|

| Input clock frequency | External crystal | 4   | 12  | 24  | MHz  |

| Temperature           | -                | -40 | -   | 85  | °C   |

| V <sub>DD</sub>       | -                | 2.5 | 5   | 5.5 | V    |

7.3.2.1 Typical Crystal Application Circuits

| CRYSTAL        | C1      | C2      | R       |

|----------------|---------|---------|---------|

| 4 MHz ~ 24 MHz | without | without | without |

Figure 7-1 Typical Crystal Application Circuit

### 7.3.3 Internal 22.1184 MHz High Speed Oscillator

| PARAMETER                                | CONDITIONS                                     | MIN | TYP     | МАХ | UNIT |

|------------------------------------------|------------------------------------------------|-----|---------|-----|------|

| Supply voltage <sup>[1]</sup>            | -                                              | 2.5 | -       | 5.5 | V    |

| Center Frequency                         | -                                              | -   | 22.1184 | -   | MHz  |

|                                          | +25℃; V <sub>DD</sub> =5 V                     | -1  | -       | +1  | %    |

| Calibrated Internal Oscillator Frequency | -40°C ~+85°C ;<br>V <sub>DD</sub> =2.5 V~5.5 V | -3  | -       | +3  | %    |

| Operation Current                        | V <sub>DD</sub> =5 V                           | -   | 500     | -   | uA   |

### 7.3.4 Internal 10 kHz Low Speed Oscillator

| PARAMETER                                | CONDITIONS                                    | MIN | TYP | MAX | UNIT |

|------------------------------------------|-----------------------------------------------|-----|-----|-----|------|

| Supply voltage <sup>[1]</sup>            | -                                             | 2.5 | -   | 5.5 | V    |

| Center Frequency                         | -                                             | -   | 10  | -   | kHz  |

|                                          | +25℃; V <sub>DD</sub> =5 V                    | -30 | -   | +30 | %    |

| Calibrated Internal Oscillator Frequency | -40°C ~+85°C;<br>V <sub>DD</sub> =2.5 V~5.5 V | -50 | -   | +50 | %    |

Note: Internal operation voltage comes from LDO.

#### 7.4.2 LDO and Power Management Specifications

| PARAMETER      | MIN  | ТҮР | МАХ  | UNIT | NOTE                          |

|----------------|------|-----|------|------|-------------------------------|

| Input Voltage  | 2.5  | 5   | 5.5  | V    | $V_{\text{DD}}$ input voltage |

| Output Voltage | 1.62 | 1.8 | 1.98 | V    | $V_{DD} > 2.5V$               |

| Temperature    | -40  | 25  | 85   | °C   |                               |

| Сbр            | -    | 1   | -    | uF   | Resr = 1Ω                     |

Notes:

1. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between  $V_{\mbox{\scriptsize DD}}$  and the closest  $V_{\mbox{\scriptsize SS}}$  pin of the device.

2. To ensure power stability, a 1uF (Cbp) or higher capacitor must be connected between LDO pin and the closest VSS pin of the device.

#### 7.4.3 Low Voltage Reset Specifications

| PARAMETER         | CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------|-----|-----|-----|------|

| Operation voltage | -                            | 1.7 | -   | 5.5 | V    |

| Quiescent current | $V_{DD} = 5.5 V$             | -   | -   | 5   | uA   |

| Temperature       | -                            | -40 | 25  | 85  | °C   |

|                   | Temperature = $25^{\circ}$ C | 1.7 | 2.0 | 2.3 | V    |

| Threshold voltage | Temperature = $-40^{\circ}C$ | -   | 2.4 | -   | V    |

|                   | Temperature = $85^{\circ}$ C | -   | 1.6 | -   | V    |

| Hysteresis        | -                            | 0   | 0   | 0   | V    |

| C <sub>bp</sub> | External Bypass Capacitor |  | 1.0 | - | uF |

|-----------------|---------------------------|--|-----|---|----|

## 7.5 Flash DC Electrical Characteristics

| SYMBOL             | PARAMETER             | CONDITIONS       | MIN. | TYP. | MAX. | UNIT             |

|--------------------|-----------------------|------------------|------|------|------|------------------|

| V <sub>DD</sub>    | Supply voltage        |                  | 1.62 | 1.8  | 1.98 | V <sup>[1]</sup> |

| T <sub>RET</sub>   | Data Retention        | <b>Temp=85</b> ℃ | 10   |      |      | year             |

| T <sub>ERASE</sub> | Page Erase Time       |                  |      | 20   |      | ms               |

| T <sub>MER</sub>   | Mass Erase Time       |                  |      | 40   |      | ms               |

| T <sub>PROG</sub>  | Program Time          |                  |      | 40   |      | us               |

| I <sub>DD1</sub>   | Read Current          |                  |      |      | 0.25 | mA               |

| I <sub>DD2</sub>   | Program/Erase Current |                  |      |      | 7    | mA               |

| I <sub>PD</sub>    | Power Down Current    |                  |      | 1    | 20   | uA               |

**Note:** V<sub>DD</sub> is source from chip LDO output voltage.

# 8 ELECTRICAL CHARACTERISTICS (NUC123XXXAEX)

## 8.1 Absolute Maximum Ratings

| Symbol                        | Parameter                                              | Min                   | Мах                   | Unit |

|-------------------------------|--------------------------------------------------------|-----------------------|-----------------------|------|

| $V_{\text{DD}}-V_{\text{SS}}$ | DC Power Supply                                        | -0.3                  | +7.0                  | V    |

| V <sub>IN</sub>               | Input Voltage                                          | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| 1/t <sub>CLCL</sub>           | Oscillator Frequency                                   | 4                     | 24                    | MHz  |

| T <sub>A</sub>                | Operating Temperature                                  | -40                   | +105                  | °C   |

| T <sub>ST</sub>               | Storage Temperature                                    | -55                   | +150                  | °C   |

| I <sub>DD</sub>               | Maximum Current into V <sub>DD</sub>                   | -                     | 120                   | mA   |

| I <sub>SS</sub>               | Maximum Current out of $V_{SS}$                        |                       | 120                   | mA   |

|                               | Maximum Current sunk by a I/O pin                      |                       | 35                    | mA   |

|                               | Maximum Current sourced by a I/O pin                   |                       | 35                    | mA   |

| 10                            | I <sub>IO</sub> Maximum Current sunk by total I/O pins |                       | 100                   | mA   |

|                               | Maximum Current sourced by total I/O pins              |                       | 100                   | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affect the lift and reliability of the device.

| PARAMETER              | SYM                 | SPECIFICATIONS |     |     |      |                                                                                 |

|------------------------|---------------------|----------------|-----|-----|------|---------------------------------------------------------------------------------|

| PARAMETER              | SYM                 | MIN            | ТҮР | MAX | UNIT | TEST CONDITIONS                                                                 |

| at 4 MHz               | I <sub>DD10</sub>   |                | 5   |     | mA   | V <sub>DD</sub> = 5V at 4 MHz,<br>All IP and PLL Disabled,<br>XTAL = 4 MHz      |

|                        | I <sub>DD11</sub>   |                | 4   |     | mA   | $V_{DD}$ = 3V at 4 MHz,<br>All IP Enabled and PLL Disabled, XTAL =<br>4 MHz     |

|                        | I <sub>DD12</sub>   |                | 3   |     | mA   | $V_{DD}$ = 3V at 4 MHz,<br>All IP and PLL Disabled,<br>XTAL = 4 MHz             |

|                        | I <sub>IDLE1</sub>  |                | 28  |     | mA   | $V_{DD}$ = 5.5V at 72 MHz,<br>All IP and PLL Enabled,<br>XTAL = 12 MHz          |

| Operating current      | I <sub>IDLE2</sub>  |                | 12  |     | mA   | $V_{DD}$ = 5.5V at 72 MHz,<br>All IP Disabled and PLL Enabled, XTAL =<br>12 MHz |

| at 72 MHz              | I <sub>IDLE3</sub>  |                | 25  |     | mA   | $V_{DD}$ = 3V at 72 MHz,<br>All IP and PLL Enabled,<br>XTAL = 12 MHz            |

|                        | I <sub>IDLE4</sub>  |                | 10  |     | mA   | $V_{DD} = 3V$ at 72 MHz,<br>All IP Disabled and PLL Enabled,<br>XTAL=12 MHz     |

|                        | I <sub>IDLE5</sub>  |                | 6   |     | mA   | $V_{DD}$ = 5.5V at 12 MHz,<br>All IP Enabled and PLL Disabled, XTAL =<br>12 MHz |

| Operating current      | I <sub>IDLE6</sub>  |                | 3   |     | mA   | $V_{DD}$ = 5.5V at 12 MHz,<br>All IP and PLL Disabled,<br>XTAL = 12 MHz         |

| Idle mode<br>at 12 MHz | I <sub>IDLE7</sub>  |                | 5   |     | mA   | $V_{DD}$ = 3V at 12 MHz,<br>All IP Enabled and PLL Disabled, XTAL =<br>12 MHz   |

|                        | I <sub>IDLE8</sub>  |                | 2   |     | mA   | $V_{DD} = 3 V$ at 12 MHz,<br>All IP and PLL Disabled,<br>XTAL = 12 MHz          |

|                        | I <sub>IDLE9</sub>  |                | 5   |     | mA   | $V_{DD}$ = 5V at 4 MHz,<br>All IP Enabled and PLL Disabled, XTAL =<br>4 MHz     |

| Operating current      | I <sub>IDLE10</sub> |                | 4   |     | mA   | $V_{DD}$ = 5V at 4 MHz,<br>All IP and PLL Disabled,<br>XTAL = 4 MHz             |

| Idle mode<br>at 4 MHz  | I <sub>IDLE11</sub> |                | 3   |     | mA   | $V_{DD}$ = 3V at 4 MHz,<br>All IP Enabled and PLL Disabled, XTAL =<br>4 MHz     |

|                        | I <sub>IDLE12</sub> |                | 2   |     | mA   | V <sub>DD</sub> = 3V at 4 MHz,<br>All IP and PLL Disabled,<br>XTAL = 4 MHz      |

#### 8.4.2 LDO and Power Management Specifications

| PARAMETER      | MIN  | TYP | МАХ  | UNIT | NOTE                          |

|----------------|------|-----|------|------|-------------------------------|

| Input Voltage  | 2.5  | 5   | 5.5  | V    | $V_{\text{DD}}$ input voltage |

| Output Voltage | 1.62 | 1.8 | 1.98 | V    | $V_{DD} > 2.5V$               |

| Temperature    | -40  | 25  | 105  | °C   |                               |

| Сbр            | -    | 1   | -    | uF   | Resr = 1Ω                     |

Notes:

1. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between  $V_{DD}$  and the closest  $V_{SS}$  pin of the device.

2. To ensure power stability, a 1uF (Cbp) or higher capacitor must be connected between LDO pin and the closest  $V_{SS}$  pin of the device.

#### 8.4.3 Low Voltage Reset Specifications

| PARAMETER         | CONDITIONS                  | MIN | TYP   | MAX | UNIT |

|-------------------|-----------------------------|-----|-------|-----|------|

| Operation voltage | -                           | 1.7 | -     | 5.5 | V    |

| Quiescent current | $V_{DD} = 5.5 V$            | -   | -     | 5   | uA   |

| Temperature       | -                           | -40 | 25    | 105 | °C   |

|                   | Temperature = $25^{\circ}C$ | 1.7 | 2.0   | 2.3 | V    |

| Threshold voltage | Temperature = -40°C         | -   | - 1.8 | -   | V    |

|                   | Temperature = $85^{\circ}C$ | -   | 2.2   | -   | V    |

| Hysteresis        | -                           | 0   | 0     | 0   | V    |

## 8.6 SPI Dynamic Characteristics

| SYMBOL          | PARAMETER                                                               | MIN      | ТҮР       | MAX       | UNIT |  |  |  |

|-----------------|-------------------------------------------------------------------------|----------|-----------|-----------|------|--|--|--|

| SPI Master mode | SPI Master mode (V <sub>DD</sub> = 4.5V ~ 5.5V, 30pF loading Capacitor) |          |           |           |      |  |  |  |

| t <sub>DS</sub> | Data setup time                                                         | 4        | 2         | -         | ns   |  |  |  |

| t <sub>DH</sub> | Data hold time                                                          | 0        | -         | -         | ns   |  |  |  |

| t <sub>v</sub>  | Data output valid time                                                  | -        | 7         | 11        | ns   |  |  |  |

| SPI Master mode | $e (V_{DD} = 3.0V \sim 3.6V, 30pF loading Capac$                        | itor)    |           |           |      |  |  |  |

| t <sub>DS</sub> | Data setup time                                                         | 5        | 3         | -         | ns   |  |  |  |

| t <sub>DH</sub> | Data hold time                                                          | 0        | -         | -         | ns   |  |  |  |

| t <sub>v</sub>  | Data output valid time                                                  | -        | 13        | 18        | ns   |  |  |  |

| SPI Slave mode  | SPI Slave mode (V <sub>DD</sub> = 4.5V ~ 5.5V, 30pF loading Capacitor)  |          |           |           |      |  |  |  |

| t <sub>DS</sub> | Data setup time                                                         | 0        | -         | -         | ns   |  |  |  |

| t <sub>DH</sub> | Data hold time                                                          | 2*PCLK+4 | -         | -         | ns   |  |  |  |

| t <sub>V</sub>  | Data output valid time                                                  | -        | 2*PCLK+11 | 2*PCLK+19 | ns   |  |  |  |

| SPI Slave mode  | SPI Slave mode (V <sub>DD</sub> = 3.0V ~ 3.6V, 30pF loading Capacitor)  |          |           |           |      |  |  |  |

| t <sub>DS</sub> | Data setup time                                                         | 0        | -         | -         | ns   |  |  |  |

| t <sub>DH</sub> | Data hold time                                                          | 2*PCLK+6 | -         | -         | ns   |  |  |  |

| t <sub>v</sub>  | Data output valid time                                                  | -        | 2*PCLK+19 | 2*PCLK+25 | ns   |  |  |  |

Figure 8-2 SPI Master Dynamic Characteristics timing

# **10 REVISION HISTORY**

| Date       | Revision | Description                                                                                      |

|------------|----------|--------------------------------------------------------------------------------------------------|

| 2012.04.01 | 1.00     | Preliminary version.                                                                             |

| 2015.05.29 | 2.00     | 1. Merged NUC123xxxANx & NUC123xxxAEx into this document.                                        |

| 2015.11.04 | 2.01     | 1. Removed ADC function pins of NUC123 QFN33 package type in section 4.3.1.3, 4.3.2.3 and 4.4.1. |

| 2016.01.12 | 2.02     | 1. Revised section 8.2 Source Current PA, PB, PC, PD, PE, PF (Push-pull Mode).                   |

| 2016.07.06 | 2.03     | 1. Updated ADC function pins of NUC123 QFN33 package type in section 4.3.1.3, 4.3.2.3 and 4.4.1. |