Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

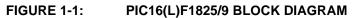

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-UQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1825-e-jq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                                           |  |

|------|---------------------------------------------------------------------------|--|

| 2.0  | Enhanced Mid-range CPU                                                    |  |

| 3.0  | Memory Organization                                                       |  |

| 4.0  | Device Configuration                                                      |  |

| 5.0  | Oscillator Module (With Fail-Safe Clock Monitor)                          |  |

| 6.0  | Reference Clock Module                                                    |  |

| 7.0  | Resets                                                                    |  |

| 8.0  | Interrupts                                                                |  |

| 9.0  | Power-Down Mode (Sleep)                                                   |  |

| 10.0 |                                                                           |  |

| 11.0 |                                                                           |  |

| 12.0 |                                                                           |  |

| 13.0 |                                                                           |  |

| 14.0 |                                                                           |  |

| 15.0 |                                                                           |  |

| 16.0 |                                                                           |  |

| 17.0 | - 3                                                                       |  |

|      | SR Latch                                                                  |  |

|      | Comparator Module                                                         |  |

|      | Timer0 Module                                                             |  |

|      | Timer1 Module with Gate Control                                           |  |

|      | Timer2/4/6 Modules                                                        |  |

| 23.0 |                                                                           |  |

| 24.0 |                                                                           |  |

| 25.0 |                                                                           |  |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |  |

|      | Capacitive Sensing (CPS) Module                                           |  |

|      | In-Circuit Serial Programming™ (ICSP™)                                    |  |

|      | Instruction Set Summary                                                   |  |

| 30.0 |                                                                           |  |

| 31.0 |                                                                           |  |

| 32.0 |                                                                           |  |

|      | Packaging Information                                                     |  |

|      | endix A: Data Sheet Revision History                                      |  |

|      | endix B: Migrating From Other PIC® Devices                                |  |

|      | Microchip Web Site                                                        |  |

|      | omer Change Notification Service                                          |  |

|      | omer Support                                                              |  |

| Prod | uct Identification System                                                 |  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 3-6:PIC16(L)F1825/9 MEMORY MAP, BANKS 24-31

| IADE |               | 0.0(1 | -)1 1023/3 Wit |      |               |      |               |      |               |      |               |      |               |      |                                       |

|------|---------------|-------|----------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------------------------------|

|      | BANK 24       |       | BANK 25        |      | BANK 26       |      | BANK 27       |      | BANK 28       |      | BANK 29       |      | BANK 30       |      | BANK 31                               |

| C00h | INDF0         | C80h  | INDF0          | D00h | INDF0         | D80h | INDF0         | E00h | INDF0         | E80h | INDF0         | F00h | INDF0         | F80h | INDF0                                 |

| C01h | INDF1         | C81h  | INDF1          | D01h | INDF1         | D81h | INDF1         | E01h | INDF1         | E81h | INDF1         | F01h | INDF1         | F81h | INDF1                                 |

| C02h | PCL           | C82h  | PCL            | D02h | PCL           | D82h | PCL           | E02h | PCL           | E82h | PCL           | F02h | PCL           | F82h | PCL                                   |

| C03h | STATUS        | C83h  | STATUS         | D03h | STATUS        | D83h | STATUS        | E03h | STATUS        | E83h | STATUS        | F03h | STATUS        | F83h | STATUS                                |

| C04h | FSR0L         | C84h  | FSR0L          | D04h | FSR0L         | D84h | FSR0L         | E04h | FSR0L         | E84h | FSR0L         | F04h | FSR0L         | F84h | FSR0L                                 |

| C05h | FSR0H         | C85h  | FSR0H          | D05h | FSR0H         | D85h | FSR0H         | E05h | FSR0H         | E85h | FSR0H         | F05h | FSR0H         | F85h | FSR0H                                 |

| C06h | FSR1L         | C86h  | FSR1L          | D06h | FSR1L         | D86h | FSR1L         | E06h | FSR1L         | E86h | FSR1L         | F06h | FSR1L         | F86h | FSR1L                                 |

| C07h | FSR1H         | C87h  | FSR1H          | D07h | FSR1H         | D87h | FSR1H         | E07h | FSR1H         | E87h | FSR1H         | F07h | FSR1H         | F87h | FSR1H                                 |

| C08h | BSR           | C88h  | BSR            | D08h | BSR           | D88h | BSR           | E08h | BSR           | E88h | BSR           | F08h | BSR           | F88h | BSR                                   |

| C09h | WREG          | C89h  | WREG           | D09h | WREG          | D89h | WREG          | E09h | WREG          | E89h | WREG          | F09h | WREG          | F89h | WREG                                  |

| C0Ah | PCLATH        | C8Ah  | PCLATH         | D0Ah | PCLATH        | D8Ah | PCLATH        | E0Ah | PCLATH        | E8Ah | PCLATH        | F0Ah | PCLATH        | F8Ah | PCLATH                                |

| C0Bh | INTCON        | C8Bh  | INTCON         | D0Bh | INTCON        | D8Bh | INTCON        | E0Bh | INTCON        | E8Bh | INTCON        | F0Bh | INTCON        | F8Bh | INTCON                                |

| C0Ch | —             | C8Ch  |                | D0Ch |               | D8Ch |               | E0Ch |               | E8Ch | _             | F0Ch |               | F8Ch |                                       |

| C0Dh | —             | C8Dh  |                | D0Dh |               | D8Dh |               | E0Dh |               | E8Dh | _             | F0Dh |               | F8Dh |                                       |

| C0Eh | -             | C8Eh  | _              | D0Eh | _             | D8Eh | _             | E0Eh | _             | E8Eh | -             | F0Eh | _             | F8Eh |                                       |

| C0Fh | —             | C8Fh  | —              | D0Fh | —             | D8Fh | —             | E0Fh | —             | E8Fh | —             | F0Fh | —             | F8Fh |                                       |

| C10h | —             | C90h  | —              | D10h | —             | D90h | —             | E10h | —             | E90h | —             | F10h | —             | F90h |                                       |

| C11h | —             | C91h  | —              | D11h | —             | D91h | —             | E11h | —             | E91h | —             | F11h | —             | F91h |                                       |

| C12h | _             | C92h  | —              | D12h | —             | D92h | —             | E12h | —             | E92h | _             | F12h | —             | F92h |                                       |

| C13h | _             | C93h  | —              | D13h | —             | D93h | —             | E13h | —             | E93h | _             | F13h | _             | F93h |                                       |

| C14h | —             | C94h  | _              | D14h | _             | D94h | _             | E14h | _             | E94h | —             | F14h | _             | F94h |                                       |

| C15h | _             | C95h  | —              | D15h | —             | D95h | —             | E15h | —             | E95h | _             | F15h | _             | F95h |                                       |

| C16h | —             | C96h  | —              | D16h | —             | D96h | —             | E16h | —             | E96h | —             | F16h | —             | F96h |                                       |

| C17h | —             | C97h  | —              | D17h | —             | D97h | —             | E17h | —             | E97h | —             | F17h | —             | F97h | One Table 0 7 fee                     |

| C18h | —             | C98h  | —              | D18h | —             | D98h | —             | E18h | —             | E98h | —             | F18h | —             | F98h | See Table 3-7 for<br>register mapping |

| C19h | _             | C99h  | —              | D19h | —             | D99h | —             | E19h | —             | E99h | _             | F19h | —             | F99h | details                               |

| C1Ah | —             | C9Ah  | —              | D1Ah | —             | D9Ah | —             | E1Ah | —             | E9Ah | _             | F1Ah | —             | F9Ah |                                       |

| C1Bh | _             | C9Bh  | —              | D1Bh | —             | D9Bh | —             | E1Bh | —             | E9Bh | _             | F1Bh | _             | F9Bh |                                       |

| C1Ch | _             | C9Ch  | —              | D1Ch | —             | D9Ch | —             | E1Ch | —             | E9Ch | _             | F1Ch | _             | F9Ch |                                       |

| C1Dh | —             | C9Dh  | —              | D1Dh | —             | D9Dh | —             | E1Dh | —             | E9Dh | —             | F1Dh | —             | F9Dh |                                       |

| C1Eh | —             | C9Eh  | —              | D1Eh | —             | D9Eh | —             | E1Eh | —             | E9Eh | —             | F1Eh | —             | F9Eh |                                       |

| C1Fh | —             | C9Fh  | —              | D1Fh | —             | D9Fh | —             | E1Fh | —             | E9Fh | —             | F1Fh | —             | F9Fh |                                       |

| C20h |               | CA0h  |                | D20h |               | DA0h |               | E20h |               | EA0h |               | F20h |               | FA0h |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

|      | Unimplemented |       | Unimplemented  |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      |                                       |

|      | Read as '0'   |       | Read as '0'    |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

| C6Fh |               | CEFh  |                | D6Fh |               | DEFh |               | E6Fh |               | EEFh |               | F6Fh |               | FEFh |                                       |

| C70h |               | CF0h  |                | D70h |               | DF0h |               | E70h |               | EF0h |               | F70h |               | FF0h |                                       |

|      | Accesses      |       | Accesses       |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses                              |

|      | 70h – 7Fh     |       | 70h – 7Fh      |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh                             |

| CFFh |               | CFFh  |                | D7Fh |               | DFFh |               | E7Fh |               | EFFh |               | F7Fh |               | FFFh |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

**Legend:** = Unimplemented data memory locations, read as '0'.

# 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.3** "Write **Protection**" for more information.

# 4.2.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

# 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

# 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16F/LF182X/PIC12F/LF1822 Memory Programming Specification*" (DS41390).

# 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained internally within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

# 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Word 1 to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 Oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

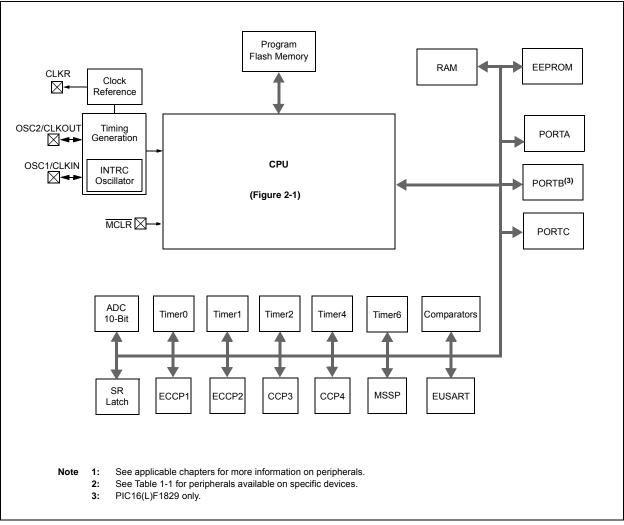

# 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Word 1:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 5-2:

#### EXTERNAL CLOCK (EC) MODE OPERATION

# 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce Interrupts. Refer to the corresponding chapters for details.

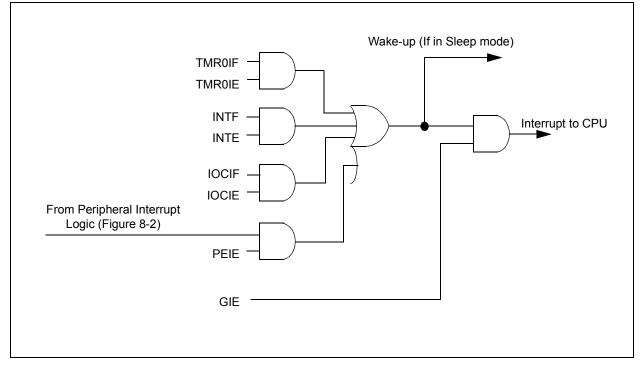

A block diagram of the interrupt logic is shown in Figure 8-1.

## FIGURE 8-1: INTERRUPT LOGIC

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

#### REGISTER 8-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|---------|---------|-----|-----|---------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | —   | CCP2IE  |

| bit 7   |         |         |         |         |     |     | bit 0   |

| Legend:                                                                                                                 |           |                                                                                       |                                                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable bit                                                                                                        |           | W = Writable bit                                                                      | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is ur                                                                                                           | nchanged  | x = Bit is unknown                                                                    | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is s                                                                                                          | et        | '0' = Bit is cleared                                                                  |                                                       |  |  |  |

| bit 7                                                                                                                   | OSFIE: Os | scillator Fail Interrupt Enable                                                       | bit                                                   |  |  |  |

|                                                                                                                         |           | es the Oscillator Fail interrup<br>les the Oscillator Fail interrup                   |                                                       |  |  |  |

| bit 6                                                                                                                   | C2IE: Con | nparator C2 Interrupt Enable                                                          | bit                                                   |  |  |  |

|                                                                                                                         |           | es the Comparator C2 interrules the Comparator C2 interrules the Comparator C2 interr | •                                                     |  |  |  |

| bit 5                                                                                                                   | C1IE: Con | nparator C1 Interrupt Enable                                                          | bit                                                   |  |  |  |

|                                                                                                                         |           | es the Comparator C1 interrules the Comparator C1 interrules the Comparator C1 interr |                                                       |  |  |  |

| bit 4                                                                                                                   | EEIE: EEF | ROM Write Completion Inter                                                            | rrupt Enable bit                                      |  |  |  |

|                                                                                                                         |           | es the EEPROM write compl<br>les the EEPROM write comp                                | •                                                     |  |  |  |

| bit 3                                                                                                                   | BCL1IE: N | ISSP Bus Collision Interrupt                                                          | Enable bit                                            |  |  |  |

| <ul> <li>1 = Enables the MSSP bus collision interrupt</li> <li>0 = Disables the MSSP bus collision interrupt</li> </ul> |           |                                                                                       |                                                       |  |  |  |

| bit 2-1 Unimplemented: Read as '0'                                                                                      |           |                                                                                       |                                                       |  |  |  |

| bit 0                                                                                                                   | CCP2IE: ( | CCP2 Interrupt Enable bit                                                             |                                                       |  |  |  |

|                                                                                                                         | 1 = Enabl | es the CCP2 interrupt                                                                 |                                                       |  |  |  |

|                                                                                                                         | 0 = Disab | les the CCP2 interrupt                                                                |                                                       |  |  |  |

| — — LATA5 LATA4 — LATA2 LATA1 LATA0                 | I a manual. |     |         |         |     |         |         |         |

|-----------------------------------------------------|-------------|-----|---------|---------|-----|---------|---------|---------|

| — — LATA5 LATA4 — LATA2 LATA1 LATA0                 |             |     |         |         |     |         |         |         |

|                                                     | bit 7       |     |         |         |     |         |         | bit 0   |

| U-0 U-0 R/W-x/u R/W-x/u U-0 R/W-x/u R/W-x/u R/W-x/u | —           | —   | LATA5   | LATA4   | —   | LATA2   | LATA1   | LATA0   |

|                                                     | U-0         | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

#### REGISTER 12-5: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0'                                |

bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-6: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | —   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                                         |

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|

| ANSELB | —       | -       | ANSB5   | ANSB4   | _     | —     | _     | —     | 129                 |

| INLVLB | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | _     | —     | _     | —     | 129                 |

| LATB   | LATB7   | LATB6   | LATB5   | LATB4   | —     | —     | _     | —     | 128                 |

| PORTB  | RB7     | RB6     | RB5     | RB4     | —     | —     | _     | —     | 128                 |

| TRISB  | TRISB7  | TRISB6  | TRISB5  | TRISB4  | —     | _     | _     | —     | 128                 |

| WPUB   | WPUB7   | WPUB6   | WPUB5   | WPUB4   | _     | _     |       | _     | 129                 |

# TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup>

Legend:x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.Note1:PIC16(L)F1829 only.

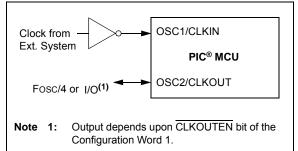

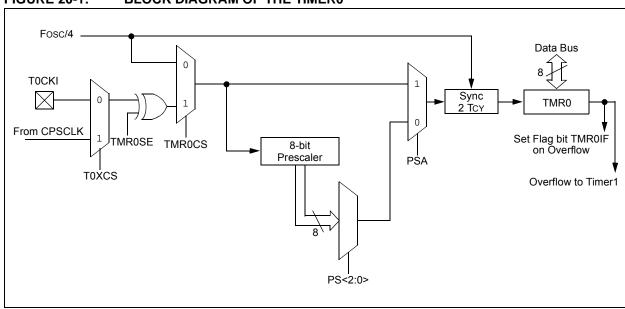

# 20.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

# 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

## 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

# FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

# 21.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 21-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 21-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                           | R/W-0/u                                                                                                              | R/W-0/u                                                                                 | R/W-0/u                                                  | R/W-0/u          | U-0      | R/W-0/u |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|----------|---------|--|

| TMR1             | CS<1:0>                                                                                                                                                                                                           | T1CKF                                                                                                                | 'S<1:0>                                                                                 | T1OSCEN                                                  | T1SYNC           | _        | TMR10N  |  |

| bit 7            |                                                                                                                                                                                                                   |                                                                                                                      |                                                                                         |                                                          |                  |          | bit 0   |  |

| Legend:          |                                                                                                                                                                                                                   |                                                                                                                      |                                                                                         |                                                          |                  |          |         |  |

| R = Readable     | e bit                                                                                                                                                                                                             | W = Writable                                                                                                         | bit                                                                                     | U = Unimpler                                             | nented bit. read | l as '0' |         |  |

| u = Bit is unc   | hanged                                                                                                                                                                                                            | W = Writable bitU = Unimplemented bit, read as '0'x = Bit is unknown-n/n = Value at POR and BOR/Value at all other F |                                                                                         |                                                          |                  |          |         |  |

| '1' = Bit is set |                                                                                                                                                                                                                   | '0' = Bit is clea                                                                                                    | ared                                                                                    |                                                          |                  |          |         |  |

| bit 7-6          | 11 = Timer1 c<br>10 = Timer1 c<br><u>If T10SC</u><br>External<br><u>If T10SC</u><br>Crystal c<br>01 = Timer1 c                                                                                                    | clock source is<br><u>CEN = 0</u> :<br>clock from T10                                                                | Capacitive Ser<br>pin or oscillato<br>CKI pin (on the<br>OSI/T1OSO pi<br>system clock ( | nsing Oscillator<br>r:<br>e rising edge)<br>ins<br>Fosc) | - (CAPOSC)       |          |         |  |

| bit 5-4          | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres                                                                                                                                                                   | scale value<br>scale value                                                                                           | t Clock Presca                                                                          | ale Select bits                                          |                  |          |         |  |

| bit 3            | <ul> <li>00 = 1:1 Prescale value</li> <li>T1OSCEN: LP Oscillator Enable Control bit</li> <li>1 = Dedicated Timer1 oscillator circuit enabled</li> <li>0 = Dedicated Timer1 oscillator circuit disabled</li> </ul> |                                                                                                                      |                                                                                         |                                                          |                  |          |         |  |

| bit 2            | <u>TMR1CS&lt;1:0</u><br>1 = Do not sy<br>0 = Synchror                                                                                                                                                             | ) <u>&gt; = 1x:</u><br>ynchronize exte<br>nize external cl                                                           | ernal clock inp                                                                         | nchronization C<br>ut<br>system clock (F                 |                  |          |         |  |

|                  | TMR1CS<1:0<br>This bit is ign                                                                                                                                                                                     |                                                                                                                      |                                                                                         |                                                          |                  |          |         |  |

| bit 1            | Unimplemen                                                                                                                                                                                                        | ted: Read as '                                                                                                       | 0'                                                                                      |                                                          |                  |          |         |  |

| bit 0            | TMR1ON: Tir<br>1 = Enables<br>0 = Stops Tir<br>Clears Ti                                                                                                                                                          | Timer1                                                                                                               | ilop                                                                                    |                                                          |                  |          |         |  |

# 22.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 modules is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 22.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMRx register

- · a write to the TxCON register

- · Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- · Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMRx is not cleared when TxCON is written.

# 22.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIRx register. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIEx register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

#### 22.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode. Additional information is provided in Section 25.0 "Master Synchronous Serial Port (MSSP1 and MSSP2) Module".

# 22.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

| R/W-x/u                 | R/W-x/u                                                                                  | R/W-x/u             | U-0             | R/W-x/u            | R/W-x/u           | R/W-x/u          | R/W-x/u             |  |  |

|-------------------------|------------------------------------------------------------------------------------------|---------------------|-----------------|--------------------|-------------------|------------------|---------------------|--|--|

| MDCHODIS                | MDCHPOL                                                                                  | MDCHSYNC            | _               |                    | MDCH              | 1<3:0>           |                     |  |  |

| bit 7                   | •                                                                                        |                     |                 |                    |                   |                  | bit 0               |  |  |

| Logondy                 |                                                                                          |                     |                 |                    |                   |                  |                     |  |  |

| Legend:<br>R = Readable | hit                                                                                      | W = Writable b      | i+              | LI – Unimplor      | nented bit, read  | L ac. 'O'        |                     |  |  |

|                         |                                                                                          |                     |                 | •                  | at POR and BO     |                  | thar Deceta         |  |  |

| u = Bit is uncha        | angeu                                                                                    | x = Bit is unknown  |                 |                    | al FOR and BO     | R/Value at all t | Siner Reseis        |  |  |

| '1' = Bit is set        |                                                                                          | '0' = Bit is clear  | rea             |                    |                   |                  |                     |  |  |

| bit 7                   | MDCHODIS:                                                                                | : Modulator High    | Carrier Ou      | tout Disable bit   |                   |                  |                     |  |  |

|                         |                                                                                          | signal driving the  |                 | •                  | ted by MDCH<      | 3:0>) is disable | ed                  |  |  |

|                         | 0 = Output s                                                                             | signal driving the  | ,<br>peripheral | output pin (seled  | ted by MDCH<      | 3:0>) is enable  | ed                  |  |  |

| bit 6                   | MDCHPOL: Modulator High Carrier Polarity Select bit                                      |                     |                 |                    |                   |                  |                     |  |  |

|                         | 1 = Selected                                                                             | d high carrier sigr | nal is invert   | ed                 |                   |                  |                     |  |  |

|                         | 0 = Selected                                                                             | d high carrier sigr | nal is not in   | verted             |                   |                  |                     |  |  |

| bit 5                   | MDCHSYNC                                                                                 | : Modulator High    | Carrier Sy      | nchronization E    | nable bit         |                  |                     |  |  |

|                         |                                                                                          | or waits for a fall | ing edge o      | n the high time o  | carrier signal be | efore allowing   | a switch to the     |  |  |

|                         | low time                                                                                 |                     | voobroniza      | d to the high tim  |                   | (1)              |                     |  |  |

|                         |                                                                                          | or Output is not s  |                 | ed to the high th  | le carrier signal | (')              |                     |  |  |

| bit 4                   | -                                                                                        | nted: Read as '0'   |                 |                    | (1)               |                  |                     |  |  |

| bit 3-0                 |                                                                                          | Modulator Data      | -               |                    | (')               |                  |                     |  |  |

|                         | 1111 = Res                                                                               | served. No chanr    | nel connect     | ted.               |                   |                  |                     |  |  |

|                         | •                                                                                        |                     |                 |                    |                   |                  |                     |  |  |

|                         | •                                                                                        |                     |                 |                    |                   |                  |                     |  |  |

|                         |                                                                                          | served. No chann    |                 |                    |                   |                  |                     |  |  |

|                         |                                                                                          | P4 output (PWM      |                 |                    |                   |                  |                     |  |  |

|                         | 0110 = CCP3 output (PWM Output mode only)                                                |                     |                 |                    |                   |                  |                     |  |  |

|                         | 0101 = CCP2 output (PWM Output mode only)                                                |                     |                 |                    |                   |                  |                     |  |  |

|                         | 0100 = CCP1 output (PWM Output mode only)<br>0011 = Reference Clock module signal (CLKR) |                     |                 |                    |                   |                  |                     |  |  |

|                         |                                                                                          | CIN2 port pin       | aalo olgilai    |                    |                   |                  |                     |  |  |

|                         |                                                                                          | CIN1 port pin       |                 |                    |                   |                  |                     |  |  |

|                         | 0000 = Vss                                                                               | 5                   |                 |                    |                   |                  |                     |  |  |

| Note 1. Nar             | manual comics                                                                            |                     |                 | occur in the signs | l atraam if the   | annian ia matau  | un a la ra a im a d |  |  |

# REGISTER 23-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| R/W-x/u          | R/W-x/u                                                                                                                                                                         | R/W-x/u                                                                                 | U-0                      | R/W-x/u            | R/W-x/u                       | R/W-x/u         | R/W-x/u          |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|--------------------|-------------------------------|-----------------|------------------|--|--|

| MDCLODIS         | MDCLPOL                                                                                                                                                                         | MDCLSYNC                                                                                |                          |                    | MDCL                          | _<3:0>          |                  |  |  |

| bit 7            |                                                                                                                                                                                 | ·                                                                                       |                          |                    |                               |                 | bit 0            |  |  |

| Legend:          |                                                                                                                                                                                 |                                                                                         |                          |                    |                               |                 |                  |  |  |

| R = Readable     | bit                                                                                                                                                                             | W = Writable bi                                                                         | t                        | U = Unimplen       | nented bit, read              | l as '0'        |                  |  |  |

| u = Bit is uncha | anged                                                                                                                                                                           | x = Bit is unkno                                                                        | wn                       | •                  | t POR and BO                  |                 | other Resets     |  |  |

| '1' = Bit is set | •                                                                                                                                                                               | '0' = Bit is clear                                                                      | ed                       |                    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 |                                                                                         |                          |                    |                               |                 |                  |  |  |

| bit 7            | MDCLODIS:                                                                                                                                                                       | Modulator Low C                                                                         | arrier Out               | out Disable bit    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 | signal driving the peripheral output pin (selected by MDCL<3:0> of the MDCARL register) |                          |                    |                               |                 |                  |  |  |

|                  | is disabl                                                                                                                                                                       | ea<br>signal driving the p                                                              | erinheral (              | outout nin (select | ted by MDCI <3                | 3.0> of the MD( | CARL register    |  |  |

|                  | is enable                                                                                                                                                                       | • • •                                                                                   | , on photon (            |                    |                               |                 |                  |  |  |

| bit 6            | MDCLPOL:                                                                                                                                                                        | Modulator Low Ca                                                                        | arrier Polar             | ity Select bit     |                               |                 |                  |  |  |

|                  | <ul> <li>1 = Selected low carrier signal is inverted</li> <li>0 = Selected low carrier signal is not inverted</li> </ul>                                                        |                                                                                         |                          |                    |                               |                 |                  |  |  |

| 5.4 <i>C</i>     |                                                                                                                                                                                 | •                                                                                       |                          |                    | abla bit                      |                 |                  |  |  |

| bit 5            | <b>MDCLSYNC:</b> Modulator Low Carrier Synchronization Enable bit<br>1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high |                                                                                         |                          |                    |                               |                 |                  |  |  |

|                  | time car                                                                                                                                                                        | rier                                                                                    |                          |                    | •                             |                 | iterite the high |  |  |

|                  |                                                                                                                                                                                 | or Output is not s                                                                      | ynchronize               | d to the low time  | e carrier signal <sup>(</sup> | 1)              |                  |  |  |

| bit 4            | -                                                                                                                                                                               | nted: Read as '0'                                                                       |                          |                    | ~                             |                 |                  |  |  |

| bit 3-0          | <b>MDCL&lt;3:0&gt;</b> Modulator Data High Carrier Selection bits <sup>(1)</sup><br>1111 = Reserved. No channel connected.                                                      |                                                                                         |                          |                    |                               |                 |                  |  |  |

|                  | 1111 = Res                                                                                                                                                                      | served. No chann                                                                        | el connect               | ed.                |                               |                 |                  |  |  |

|                  | •                                                                                                                                                                               |                                                                                         |                          |                    |                               |                 |                  |  |  |

|                  | •                                                                                                                                                                               |                                                                                         |                          |                    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 | erved. No chann<br>P4 output (PWM (                                                     |                          |                    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 | P3 output (PWM (                                                                        |                          |                    |                               |                 |                  |  |  |

|                  | 0101 = CCP2 output (PWM Output mode only)                                                                                                                                       |                                                                                         |                          |                    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 | P1 output (PWM (<br>erence Clock mod                                                    |                          |                    |                               |                 |                  |  |  |

|                  |                                                                                                                                                                                 | CIN2 port pin                                                                           | ଯା <del>ତ</del> ରାହା ାଣା |                    |                               |                 |                  |  |  |

|                  | 0001 = MD                                                                                                                                                                       | CIN1 port pin                                                                           |                          |                    |                               |                 |                  |  |  |

|                  | 0000 = Vss                                                                                                                                                                      | 5                                                                                       |                          |                    |                               |                 |                  |  |  |

# REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3     | Bit 2 | Bit 1  | Bit 0 | Register<br>on Page |

|--------|----------|---------|----------|--------|-----------|-------|--------|-------|---------------------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | —      |           | MDCF  | <3:0>  |       | 199                 |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      | MDCL<3:0> |       |        |       | 200                 |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT     | _     | —      | MDBIT | 197                 |

| MDSRC  | MDMSODIS |         | —        | _      |           | MDMS  | 6<3:0> |       | 198                 |

Legend: — Unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

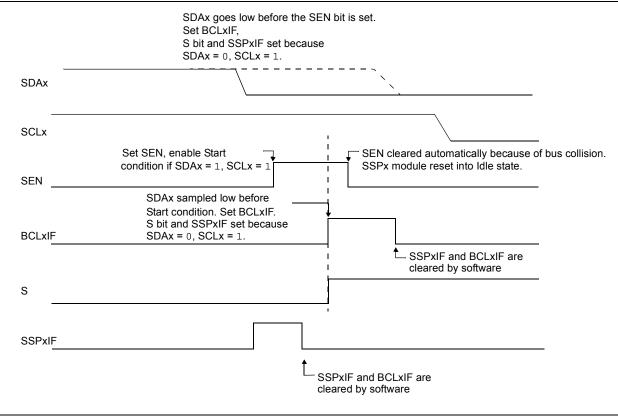

#### 25.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx are sampled low at the beginning of the Start condition (Figure 25-33).

- b) SCLx is sampled low before SDAx is asserted low (Figure 25-34).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLxIF flag is set and

- the MSSPx module is reset to its Idle state (Figure 25-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 25-35). If, however, a '1' is sampled on the

SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

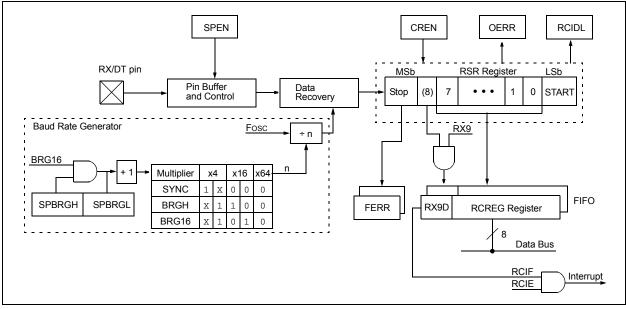

# FIGURE 26-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 26-1, Register 26-2 and Register 26-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

# FIGURE 26-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

# FIGURE 26-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

97 The SUS-ABT revealed is the white he will be a set.

# 29.0 INSTRUCTION SET SUMMARY

Each PIC16 instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of four oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

#### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |  |  |

|-------|-----------------|--|--|--|--|

| PC    | Program Counter |  |  |  |  |

| TO    | Time-out bit    |  |  |  |  |

| С     | Carry bit       |  |  |  |  |

| DC    | Digit carry bit |  |  |  |  |

| Z     | Zero bit        |  |  |  |  |

| PD    | Power-down bit  |  |  |  |  |

#### 30.4 DC Characteristics: PIC16(L)F1825/9-I/E

|              | DC CI    | HARACTERISTICS                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |          |       |                                                                         |  |  |  |