### Microchip Technology - PIC16F1825-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1825-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-3:** PIC16(L)F1829 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                         | Function | Input | Output | Description                         |

|------------------------------------------------------------------------------|----------|-------|--------|-------------------------------------|

| name                                                                         | Function | Туре  | Туре   | Description                         |

| RC2/AN6/CPS6/C12IN2-/                                                        | RC2      | TTL   | CMOS   | General purpose I/O.                |

| P1D <sup>(1,2)</sup> /P2B <sup>(1,2)</sup> /MDCIN1                           | AN6      | AN    | —      | A/D Channel 6 input.                |

|                                                                              | CPS6     | AN    | —      | Capacitive sensing input 6.         |

|                                                                              | C12IN2-  | AN    | —      | Comparator C1 or C2 negative input. |

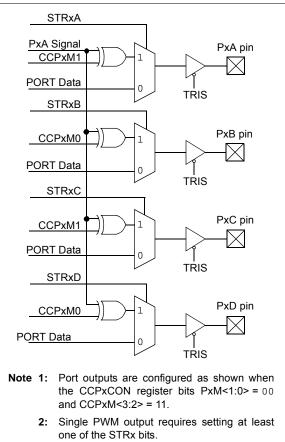

|                                                                              | P1D      | —     | CMOS   | PWM output.                         |

|                                                                              | P2B      | _     | CMOS   | PWM output.                         |

|                                                                              | MDCIN1   | ST    | —      | Modulator Carrier Input 1.          |

| RC3/AN7/CPS7/C12IN3-/                                                        | RC3      | TTL   | CMOS   | General purpose I/O.                |

| P2A <sup>(1,2)</sup> /CCP2 <sup>(1,2)</sup> /P1C <sup>(1,2)</sup> /<br>MDMIN | AN7      | AN    |        | A/D Channel 7 input.                |

|                                                                              | CPS7     | AN    | _      | Capacitive sensing input 7.         |

|                                                                              | C12IN3-  | AN    | —      | Comparator C1 or C2 negative input. |

|                                                                              | P2A      |       | CMOS   | PWM output.                         |

|                                                                              | CCP2     | AN    | _      | Capture/Compare/PWM2.               |

|                                                                              | P1C      | _     | CMOS   | PWM output.                         |

|                                                                              | MDMIN    | ST    | —      | Modulator source input.             |

| RC4/C2OUT/SRNQ/P1B/TX <sup>(1)</sup> /                                       | RC4      | TTL   | CMOS   | General purpose I/O.                |

| CK <sup>(1)</sup> /MDOUT                                                     | C2OUT    | _     | CMOS   | Comparator C2 output.               |

|                                                                              | SRNQ     | _     | CMOS   | SR Latch inverting output.          |

|                                                                              | P1B      | _     | CMOS   | PWM output.                         |

|                                                                              | TX       | _     | CMOS   | USART asynchronous transmit.        |

|                                                                              | СК       | ST    | CMOS   | USART synchronous clock.            |

|                                                                              | MDOUT    | _     | CMOS   | Modulator output.                   |

| RC5/P1A/CCP1/DT <sup>(1)</sup> /RX <sup>(1)</sup> /                          | RC5      | TTL   | CMOS   | General purpose I/O.                |

| MDCIN2                                                                       | P1A      | _     | CMOS   | PWM output.                         |

|                                                                              | CCP1     | ST    | CMOS   | Capture/Compare/PWM1.               |

|                                                                              | RX       | ST    |        | USART asynchronous input.           |

|                                                                              | DT       | ST    | CMOS   | USART synchronous data.             |

|                                                                              | MDCIN2   | ST    |        | Modulator Carrier Input 2.          |

| RC6/AN8/CPS8/CCP4/SS1                                                        | RC6      | TTL   | CMOS   | General purpose I/O.                |

|                                                                              | AN8      | AN    |        | A/D Channel 8 input.                |

|                                                                              | CPS8     | AN    | _      | Capacitive sensing input 8.         |

|                                                                              | CCP4     | AN    | _      | Capture/Compare/PWM4.               |

|                                                                              | SS1      | ST    | —      | Slave Select input.                 |

| RC7/AN9/CPS9/SDO1                                                            | RC7      | TTL   | CMOS   | General purpose I/O.                |

|                                                                              | AN9      | AN    | —      | A/D Channel 9 input.                |

|                                                                              | CPS9     | AN    | —      | Capacitive sensing input 9.         |

|                                                                              | SDO1     | _     | CMOS   | SPI data output.                    |

| VDD                                                                          | Vdd      | Power | —      | Positive supply.                    |

| Vss                                                                          | Vss      | Power | —      | Ground reference.                   |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Default function location.

# PIC16(L)F1825/9

| System Chook     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GURE 5-7:                | INTERNAL OSCILLATOR SWITCH TIMING                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------|

| HEINTOSC/<br>MEDITOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                                                      |

| HFINTOSC/<br>MENTOSC       Orderstor Delay <sup>10</sup> Orderia dyna       Austria         LFINTOSC       #0       =0         IRCF <3:0>       #0       =0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          | LPINTOSC (PSCM and WOT distabled)                    |

| AMPRIPOSC       Contents Only ***       Restause         LFINTOSC       #************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                                                      |

| LFINTOSC       ≠0       =0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Cardinator Onlay <sup>63</sup> Science Synce Running |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LFINTOSC                 |                                                      |

| ARTINITOSC/ LETINITOSC (EIRHer PSCM or WDY enabled)<br>MEINITOSC<br>HFINTOSC<br>LETINTOSC<br>LETINTOSC<br>URCF <3:0> = 0 = 0<br>System Clock<br>URTRITOSC HEIRITOSC/MEINITOSC<br>URTRITOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IRCF <3:0>               | $\neq 0$ $= 0$                                       |

| NEFINITOSC/       2-cycles System         LFINTOSC       2-cycles System         IRCF <3.0>       ≠ 0         y= 0       = 0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System Clock             |                                                      |

| HFINTOSC/<br>LFINTOSC<br>LFINTOSC<br>IRCF <3:0> = 0 = 0<br>System Clock = 0 = 0<br>System Clock = 0 = 0<br>LFINTOSC == NFINTOSCARFINTOSC<br>LFINTOSC == NFINTOSCARFINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NENETOSO/                | LFINTOSC (ERDer POCM of WOT spabled)                 |

| LFINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HFINTOSC/                |                                                      |

| IRCF <3:0>       ≠ 0       = 0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | terran rana.             | l <u>iji 2-ovota konta</u> liji <u>Posasino</u>      |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LFINTOSC                 |                                                      |

| LEPHYTOSC HEINTOSC/MEINTOSC<br>LEPHYTOSC LIPHYTOSC turns off unterse WOY or Picose is enabled<br>Originator (newy <sup>Th</sup> ) provide Sync (<br>MEINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IRCF <3:0>               | $\neq 0$ $\chi = 0$                                  |

| LEINTOSC HEINTOSCIMETINTOSC<br>LEINTOSC LIPITOSC Linne off untere WOY or PLONE is enabled<br>URINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                                                      |

| LFIRTOSC turns off unless WS7 or FS098 is anabied<br>UFIRTOSC Coddition Geory <sup>(1)</sup> (cryste Sanc )<br>MFIRTOSC Reprod<br>MFIRTOSC F<br>System Grook Codd Codd Codd Codd Codd Codd Codd C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System Clock             |                                                      |

| LFIRCHOSC turns off univers VCF or FSOM is anabied<br>LFIRCHOSC Lines off univers VCF or FSOM is anabied<br>Coldition Group <sup>(1)</sup> (-cycle Sanc )<br>Aurenting<br>MFENTOSC<br>MFENTOSC<br>IPCF <3:02 7 0<br>System Crock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |                                                      |

| LFIRTOSC turns off unless WS7 or FS098 is anabied<br>UFIRTOSC Coddition Geory <sup>(1)</sup> (cryste Sanc )<br>MFIRTOSC Reprod<br>MFIRTOSC F<br>System Grook Codd Codd Codd Codd Codd Codd Codd C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n ann na h-ann an an she |                                                      |

| Childhin Gook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 1922 I 1997            |                                                      |

| HEINTOBC/<br>MENTOSC<br>BECE <3:52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LEBITOSC                 |                                                      |

| MENTOSC         Image: Second sec |                          | California California Computer Sona 🕴 🦷 🥵 🥵 🥵        |

| System G>>>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                                                      |

| yuuuuuuun yuunuu yuuni yuuni yuuni yuuni yuuni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$2CE <3:0>              |                                                      |

| aamaamaamaamaamaamaamaamaamaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | System Crock             |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                                      |

| Nexa 1: Sen Table 5-1, "Capilizion Switching Dalays" for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                                                      |

# PIC16(L)F1825/9

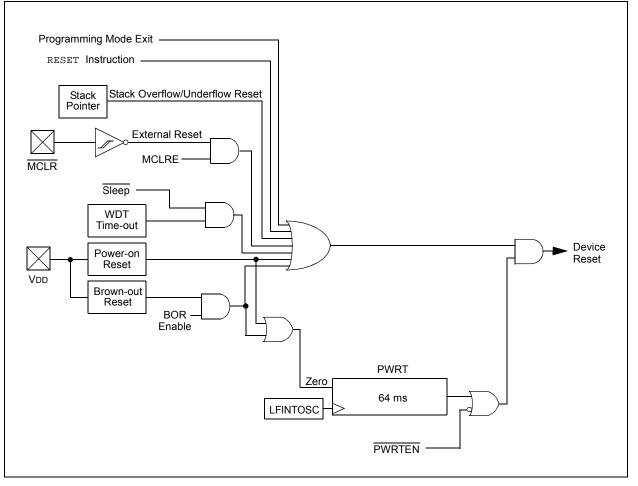

# 7.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 7-1.

### FIGURE 7-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

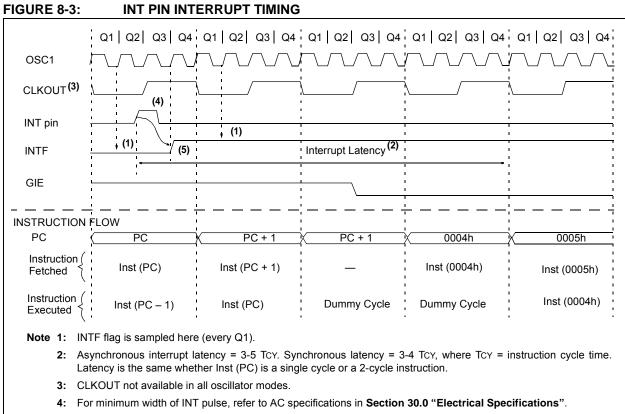

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### EXAMPLE 11-2: DATA EEPROM WRITE

|                      | BANKSEL<br>MOVLW<br>MOVWF<br>MOVWF<br>BCF<br>BCF<br>BSF              | EEADRL<br>DATA_EE_<br>EEDATL<br>EECON1,<br>EECON1,    | DATA<br>CFGS<br>EEPGD | ;Data Memory Address to write<br>;<br>;Data Memory Value to write |

|----------------------|----------------------------------------------------------------------|-------------------------------------------------------|-----------------------|-------------------------------------------------------------------|

| Required<br>Sequence | BCF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>BSF<br>BCF<br>BTFSC<br>GOTO | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,<br>INTCON, | WR<br>GIE<br>WREN     | ;Disable writes                                                   |

|                              | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash ADDR                   | I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I |

| Flash Data                   | INSTR (PC) INSTR (PC + 1) EEDATH,EEDATL INSTR (PC + 3) INSTR (PC + 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                              | INSTR(PC - 1)       BSF EECON1,RD       INSTR(PC + 1)       Forced NOP       INSTR(PC + 3)       INSTR(PC + 4)         executed here       executed here       executed here       executed here       executed here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RD bit                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EEDATH<br>EEDATL<br>Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EERHLT                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### 14.3 FVR Control Registers

### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0          | R-q/q                                                                                                                          | R/W-0/0                                              | R/W-0/0                                         | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                              | R/W-0/0                                                 | R/W-0/0      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|--|