Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

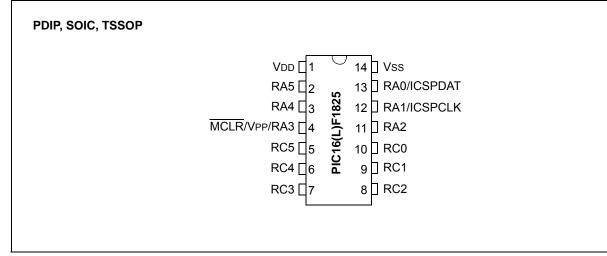

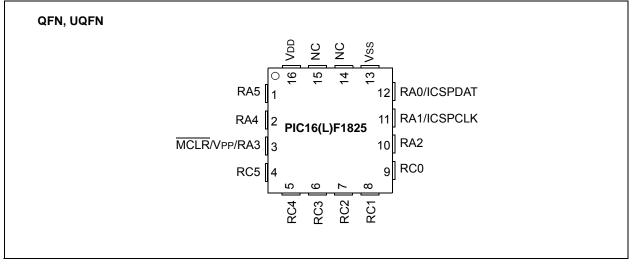

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed32MHzConnectivityPC, LINbus, SPI, UART/USARTNumber of I/O11Program Memory Size14KB (8K × 14)Program Memory TypeFLASHEEPROM Size256 × 8RAM Size1.8V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPrackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOICPurchase URLhttps://www.e-xfl.com/product-detail/microchip-technology/pic16f1825t-i-sl | Details                    |                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Core Size8-BitSpeed32MHzConnectivityPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size14KB (8K x 14)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                 | Product Status             | Active                                                                     |

| Speed32MHzConnectivityI²C, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size14KB (8K x 14)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)                                                                 | Core Processor             | PIC                                                                        |

| ConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size14KB (8K × 14)Program Memory TypeFLASHEEPROM Size256 × 8RAM Size1K × 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)                                                                           | Core Size                  | 8-Bit                                                                      |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size14KB (8K x 14)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Surface Machine Line Line Line Line Line Line Line L                                                               | Speed                      | 32MHz                                                                      |

| Number of I/O11Program Memory Size14KB (8K × 14)Program Memory TypeFLASHEEPROM Size256 × 8RAM Size1K × 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)                                                                                                                                                                   | Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Program Memory Size14KB (8K x 14)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                    | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Program Memory TypeFLASHEEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                     | Number of I/O              | 11                                                                         |

| EEPROM Size256 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                             | Program Memory Size        | 14KB (8K x 14)                                                             |

| RAM SizeIK x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                               | Program Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                                             | EEPROM Size                | 256 x 8                                                                    |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                                                                                  | RAM Size                   | 1K x 8                                                                     |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                                                                                                                                 | Data Converters            | A/D 8x10b                                                                  |

| Mounting TypeSurface MountPackage / Case14-SOIC (0.154", 3.90mm Width)Supplier Device Package14-SOIC                                                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                                   |

| Package / Case     14-SOIC (0.154", 3.90mm Width)       Supplier Device Package     14-SOIC                                                                                                                                                                                                                                                                                                                                                                                | Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Supplier Device Package 14-SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mounting Type              | Surface Mount                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16f1825t-i-sl                                                                                                                                                                                                                                                                                                                                                                                    | Supplier Device Package    | 14-SOIC                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1825t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Peripheral Highlights (Continued)**

- · Data Signal Modulator Module:

- Selectable modulator and carrier sources

- SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

#### ECCP (Full-Bridge) ECCP (Half-Bridge) MSSP (I<sup>2</sup>C<sup>TM</sup>/SPI) Sheet Index Program Memory 10-bit ADC (ch) Data EEPROM CapSense (ch) Flash (words) Comparators Data SRAM (8/16-bit) EUSART SR Latch Timers I/O's<sup>(2)</sup> Debug<sup>(1)</sup> (bytes) (bytes) СC ХГР Device Data PIC12(L)F1822 (1) 2K 256 128 6 4 4 1 2/1 1 1 0/1/0 Y I/H Υ PIC12(L)F1840 4K 256 256 6 4 4 1 2/1 0/1/0 Y I/H Y (2)1 1 PIC16(L)F1823 (1) 2K 256 128 12 8 8 2 2/1 1 1 1/0/0 Y I/H Y PIC16(L)F1824 (3) 4K 256 256 12 8 8 2 4/1 1 1 1/1/2 Y I/H Υ PIC16(L)F1825 (4)8K 256 1024 12 8 8 2 4/1 1 1 1/1/2 Υ I/H Υ 12 2 1/0/0 I/H Υ PIC16(L)F1826 (5)2K 256 256 16 12 2/1 1 1 Υ PIC16(L)F1827 (5) 4K 256 384 16 12 12 2 4/1 1 2 1/1/2 Y I/H Y Y Y PIC16(L)F1828 (3)4K 256 256 18 12 12 2 4/1 1 1 1/1/2I/H PIC16(L)F1829 (4)8K 256 1024 18 12 12 2 4/1 1 2 1/1/2 Υ I/H Υ PIC16(L)F1847 8K 256 16 12 12 2 4/1 2 1/1/2 Y I/H Y (6)1024 1

# PIC12(L)F1822/1840/PIC16(L)F182x/1847 Family Types

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

3: DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

# 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.4** "**Stack**" for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.5 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0** "Instruction Set Summary" for more details.

# TABLE 3-3: PIC16(L)F1825/9 MEMORY MAP, BANKS 0-7

|              | BANK 0               | 010(         | BANK 1                |               | BANK 2                |              | BANK 3                |               | BANK 4                  |              | BANK 5                |              | BANK 6                |              | BANK 7                |

|--------------|----------------------|--------------|-----------------------|---------------|-----------------------|--------------|-----------------------|---------------|-------------------------|--------------|-----------------------|--------------|-----------------------|--------------|-----------------------|

| 000h         | INDF0                | 080h         | INDF0                 | 100h          | INDF0                 | 180h         | INDF0                 | 200h          | INDF0                   | 280h         | INDF0                 | 300h         | INDF0                 | 380h         | INDF0                 |

| 001h         | INDF1                | 081h         | INDF1                 | 101h          | INDF1                 | ] 181h [     | INDF1                 | 201h          | INDF1                   | 281h         | INDF1                 | 301h         | INDF1                 | 381h         | INDF1                 |

| 002h         | PCL                  | 082h         | PCL                   | 102h          | PCL                   | 182h         | PCL                   | 202h          | PCL                     | 282h         | PCL                   | 302h         | PCL                   | 382h         | PCL                   |

| 003h         | STATUS               | 083h         | STATUS                | 103h          | STATUS                | 183h         | STATUS                | 203h          | STATUS                  | 283h         | STATUS                | 303h         | STATUS                | 383h         | STATUS                |

| 004h         | FSR0L                | 084h         | FSR0L                 | 104h          | FSR0L                 | 184h         | FSR0L                 | 204h          | FSR0L                   | 284h         | FSR0L                 | 304h         | FSR0L                 | 384h         | FSR0L                 |

| 005h         | FSR0H                | 085h<br>086h | FSR0H<br>FSR1L        | 105h          | FSR0H<br>FSR1L        | 185h         | FSR0H<br>FSR1L        | 205h          | FSR0H<br>FSR1L          | 285h<br>286h | FSR0H<br>FSR1L        | 305h         | FSR0H<br>FSR1L        | 385h         | FSR0H<br>FSR1L        |

| 006h<br>007h | FSR1L<br>FSR1H       | 086h<br>087h | FSR1L<br>FSR1H        | 106h<br>107h  | FSR1L<br>FSR1H        | 186h<br>187h | FSR1L<br>FSR1H        | 206h<br>207h  | FSR1L<br>FSR1H          | 286n<br>287h | FSR1L<br>FSR1H        | 306h<br>307h | FSR1L<br>FSR1H        | 386h<br>387h | FSR1L<br>FSR1H        |

| 007h<br>008h | BSR                  | 088h         | BSR                   | 10711<br>108h | BSR                   | 188h         | BSR                   | 20711<br>208h | BSR                     | 288h         | BSR                   | 308h         | BSR                   | 388h         | BSR                   |

| 009h         | WREG                 | 089h         | WREG                  | 109h          | WREG                  | 189h         | WREG                  | 209h          | WREG                    | 289h         | WREG                  | 309h         | WREG                  | 389h         | WREG                  |

| 00Ah         | PCLATH               | 08Ah         | PCLATH                | 10Ah          | PCLATH                | 18Ah         | PCLATH                | 20Ah          | PCLATH                  | 28Ah         | PCLATH                | 30Ah         | PCLATH                | 38Ah         | PCLATH                |

| 00Bh         | INTCON               | 08Bh         | INTCON                | 10Bh          | INTCON                | 18Bh         | INTCON                | 20Bh          | INTCON                  | 28Bh         | INTCON                | 30Bh         | INTCON                | 38Bh         | INTCON                |

| 00Ch         | PORTA                | 08Ch         | TRISA                 | 10Ch          | LATA                  | 18Ch         | ANSELA                | 20Ch          | WPUA                    | 28Ch         | _                     | 30Ch         | _                     | 38Ch         | INLVLA                |

| 00Dh         | PORTB <sup>(1)</sup> | 08Dh         | TRISB <sup>(1)</sup>  | 10Dh          | LATB <sup>(1)</sup>   | 18Dh         | ANSELB <sup>(1)</sup> | 20Dh          | WPUB <sup>(1)</sup>     | 28Dh         |                       | 30Dh         | —                     | 38Dh         | INLVLB <sup>(1)</sup> |

| 00Eh         | PORTC                | 08Eh         | TRISC                 | 10Eh          | LATC                  | 18Eh         | ANSELC                | 20Eh          | WPUC                    | 28Eh         | -                     | 30Eh         | —                     | 38Eh         | INLVLC                |

| 00Fh         | —                    | 08Fh         | —                     | 10Fh          | _                     | 18Fh         | _                     | 20Fh          | _                       | 28Fh         | _                     | 30Fh         | _                     | 38Fh         | _                     |

| 010h         | _                    | 090h         | —                     | 110h          | _                     | 190h         | _                     | 210h          | _                       | 290h         | —                     | 310h         |                       | 390h         | _                     |

| 011h         | PIR1                 | 091h         | PIE1                  | 111h          | CM1CON0               | 191h         | EEADRL                | 211h          | SSP1BUF                 | 291h         | CCPR1L                | 311h         | CCPR3L                | 391h         | IOCAP                 |

| 012h         | PIR2                 | 092h         | PIE2                  | 112h          | CM1CON1               | 192h         | EEADRH                | 212h          | SSP1ADD                 | 292h         | CCPR1H                | 312h         | CCPR3H                | 392h         | IOCAN                 |

| 013h         | PIR3                 | 093h         | PIE3                  | 113h          | CM2CON0               | 193h         | EEDATL                | 213h          | SSP1MSK                 | 293h         | CCP1CON               | 313h         | CCP3CON               | 393h         | IOCAF                 |

| 014h         | PIR4 <sup>(1)</sup>  | 094h         | PIE4 <sup>(1)</sup>   | 114h          | CM2CON1               | 194h         | EEDATH                | 214h          | SSP1STAT                | 294h         | PWM1CON               | 314h         | _                     | 394h         | IOCBP <sup>(1)</sup>  |

| 015h         | TMR0                 | 095h         | OPTION_REG            | 115h          | CMOUT                 | 195h         | EECON1                | 215h          | SSP1CON1                | 295h         | CCP1AS                | 315h         | _                     | 395h         | IOCBN <sup>(1)</sup>  |

| 016h         | TMR1L                | 096h         | PCON                  | 116h          | BORCON                | 196h         | EECON2                | 216h          | SSP1CON2                | 296h         | PSTR1CON              | 316h         | _                     | 396h         | IOCBF <sup>(1)</sup>  |

| 017h         | TMR1H                | 097h         | WDTCON                | 117h          | FVRCON                | 197h         | _                     | 217h          | SSP1CON3                | 297h         | —                     | 317h         | —                     | 397h         | _                     |

| 018h         | T1CON                | 098h         | OSCTUNE               | 118h          | DACCON0               | 198h         | —                     | 218h          | _                       | 298h         | CCPR2L                | 318h         | CCPR4L                | 398h         | _                     |

| 019h         | T1GCON               | 099h         | OSCCON                | 119h          | DACCON1               | 199h         | RCREG                 | 219h          | SSP2BUF <sup>(1)</sup>  | 299h         | CCPR2H                | 319h         | CCPR4H                | 399h         | —                     |

| 01Ah         | TMR2                 | 09Ah         | OSCSTAT               | 11Ah          | SRCON0                | 19Ah         | TXREG                 | 21Ah          | SSP2ADD <sup>(1)</sup>  | 29Ah         | CCP2CON               | 31Ah         | CCP4CON               | 39Ah         | CLKRCON               |

| 01Bh         | PR2                  | 09Bh         | ADRESL                | 11Bh          | SRCON1                | 19Bh         | SPBRGL                | 21Bh          | SSP2MSK <sup>(1)</sup>  | 29Bh         | PWM2CON               | 31Bh         | _                     | 39Bh         | _                     |

| 01Ch         | T2CON                | 09Ch         | ADRESH                | 11Ch          | —                     | 19Ch         | SPBRGH                | 21Ch          | SSP2STAT <sup>(1)</sup> | 29Ch         | CCP2AS                | 31Ch         | —                     | 39Ch         | MDCON                 |

| 01Dh         | _                    | 09Dh         | ADCON0                | 11Dh          | APFCON0               | 19Dh         | RCSTA                 | 21Dh          | SSP2CON1 <sup>(1)</sup> | 29Dh         | PSTR2CON              | 31Dh         | —                     | 39Dh         | MDSRC                 |

| 01Eh         | CPSCON0              | 09Eh         | ADCON1                | 11Eh          | APFCON1               | 19Eh         | TXSTA                 | 21Eh          | SSP2CON2 <sup>(1)</sup> | 29Eh         | CCPTMRS               | 31Eh         | —                     | 39Eh         | MDCARL                |

| 01Fh         | CPSCON1              | 09Fh         | —                     | 11Fh          | _                     | 19Fh         | BAUDCON               | 21Fh          | SSP2CON3 <sup>(1)</sup> | 29Fh         | _                     | 31Fh         | _                     | 39Fh         | MDCARH                |

| 020h         |                      | 0A0h         |                       | 120h          |                       | 1A0h         |                       | 220h          |                         | 2A0h         |                       | 320h         |                       | 3A0h         |                       |

|              | General              |              | General               |               | General               |              | General               |               | General                 |              | General               |              | General               |              | General               |

|              | Purpose              |              | Purpose               |               | Purpose               |              | Purpose               |               | Purpose                 |              | Purpose               |              | Purpose               |              | Purpose               |

|              | Register             |              | Register              |               | Register              |              | Register              |               | Register                |              | Register              |              | Register              |              | Register              |

|              | 96 Bytes             |              | 80 Bytes              |               | 80 Bytes              |              | 80 Bytes              |               | 80 Bytes                |              | 80 Bytes              |              | 80 Bytes              |              | 80 Bytes              |

| 06Fh         |                      | 0EFh         |                       | 16Fh          |                       | 1EFh         |                       | 26Fh          |                         | 2EFh         |                       | 36Fh         |                       | 3EFh         |                       |

| 070h         |                      | 0F0h         |                       | 170h          |                       | 1F0h         |                       | 270h          |                         | 2F0h         |                       | 370h         |                       | 3F0h         |                       |

|              | Common RAM           |              | Accesses<br>70h – 7Fh |               | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |               | Accesses<br>70h – 7Fh   |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |

| 07Fh         |                      | 0FFh         | /011 – /FII           | 17Fh          | / UII – / FII         | 1FFh         | /011 - / FII          | 27Fh          | /011 – / FII            | 2FFh         | -                     | 37Fh         | /011 – / F11          | 3FFh         | /011-/F11             |

| 07FN         |                      | UFFN         |                       | l ı⁄⊢u l      |                       | liteu        |                       | _ ∠/⊦n [      |                         | ZEEN         |                       | 37FN         |                       | 3FFN         |                       |

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Available only on PIC16(L)F1829.

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1               | Bit 0 | Register<br>on Page |

|---------|--------|--------|---------|-------|---------|-------|---------------------|-------|---------------------|

| CLKRCON | CLKREN | CLKROE | CLKRSLR | CLKRI | DC<1:0> | C     | LKRDIV<2:0          | >     | 72                  |

| 1       |        |        | 1 (-1   |       |         |       | al a al cara coma a |       |                     |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   |          | FOSC<2:0> |         | 48                  |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

| Name   | Bit 7  | Bit 6 | Bit 5     | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|-------|-----------|-------|------------|-------|-------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0> |       |            | —     | SCS   | <1:0>  | 68                  |

| STATUS | —      | —     | —         | TO    | PD         | Z     | DC    | С      | 22                  |

| WDTCON | _      | _     |           |       | WDTPS<4:0> | >     |       | SWDTEN | 100                 |

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   |          | FOSC<2:0> |         | 48                  |

Legend: — Unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0                                     | U-0             | R/W-1/1            | R/W-1/1           | U-0                                                                             | U-0                | U-0                 | U-0    |

|-----------------------------------------|-----------------|--------------------|-------------------|---------------------------------------------------------------------------------|--------------------|---------------------|--------|

| _                                       | —               | ANSB5              | ANSB4             | —                                                                               | _                  | —                   | —      |

| bit 7                                   |                 |                    |                   |                                                                                 |                    |                     | bit C  |

|                                         |                 |                    |                   |                                                                                 |                    |                     |        |

| Legend:                                 |                 |                    |                   |                                                                                 |                    |                     |        |

| R = Readable                            | bit             | W = Writable bi    | t                 | U = Unimpleme                                                                   | ented bit, read as | '0'                 |        |

| u = Bit is unchanged x = Bit is unknown |                 |                    |                   | -n/n = Value at                                                                 | POR and BOR/V      | alue at all other F | Resets |

| '1' = Bit is set                        |                 | '0' = Bit is clear | ed                |                                                                                 |                    |                     |        |

|                                         |                 |                    |                   |                                                                                 |                    |                     |        |

| bit 7-6                                 | Unimplement     | ed: Read as '0'    |                   |                                                                                 |                    |                     |        |

| bit 5-4                                 | 0 = Digital I/C | ). Pin is assigned | to port or digita | r Digital Function<br>al special function<br>nput <sup>(1)</sup> . Digital inpu |                    | . ,                 |        |

| bit 3-0                                 | Unimplement     | ed: Read as '0'    |                   |                                                                                 |                    |                     |        |

|                                         |                 |                    |                   |                                                                                 |                    |                     |        |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | —   | —   | _   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits<sup>(1,2)</sup> 1 = Pull-up enabled

0 =Pull-up disabled

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-14: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —   | _   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | INLVLB<7:4>: PORTB Input Level Select bits                |

|---------|-----------------------------------------------------------|

|         | For RB<7:4> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

| bit 7-6 | Unimplemented: Read as '0'                                |

# PIC16(L)F1825/9

| REGISTER 12-18: | ANSELC: PORTC ANALOG SELECT REGISTER |  |

|-----------------|--------------------------------------|--|

|                 |                                      |  |

| R/W-1/1              | R/W-1/1                                                                                                                                                                                                                                                                                                           | U-0                                                   | U-0              | R/W-1/1            | R/W-1/1          | R/W-1/1        | R/W-1/1                 |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|--------------------|------------------|----------------|-------------------------|--|--|--|

| ANSC7 <sup>(2)</sup> | ANSC6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                              | _                                                     |                  | ANSC3              | ANSC2            | ANSC1          | ANSC0                   |  |  |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                    |                  |                |                         |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                    |                  |                |                         |  |  |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                    |                  |                |                         |  |  |  |

| R = Readable         | bit                                                                                                                                                                                                                                                                                                               | W = Writable                                          | bit              | U = Unimpler       | nented bit, read | d as '0'       |                         |  |  |  |

| u = Bit is unch      | nanged                                                                                                                                                                                                                                                                                                            | x = Bit is unkr                                       | nown             | -n/n = Value a     | at POR and BO    | R/Value at all | other Resets            |  |  |  |

| '1' = Bit is set     |                                                                                                                                                                                                                                                                                                                   | '0' = Bit is cle                                      | ared             |                    |                  |                |                         |  |  |  |

| bit 7-6              | 0 = Digital I/                                                                                                                                                                                                                                                                                                    | Analog Select<br>O. Pin is assigr<br>nput. Pin is ass | ned to port or d | ligital special fu | inction.         |                | ectively <sup>(2)</sup> |  |  |  |

| bit 5-4              | Unimplemen                                                                                                                                                                                                                                                                                                        | nted: Read as '                                       | 0'               |                    |                  |                |                         |  |  |  |

| bit 3-0              | <ul> <li>ANSC&lt;3:0&gt;: Analog Select between Analog or Digital Function on pins RC&lt;3:0&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |                                                       |                  |                    |                  |                |                         |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                    |                  |                |                         |  |  |  |

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

# REGISTER 12-19: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                | •                    |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

- 3: WPUC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

# PIC16(L)F1825/9

| Name                  | Bit 7                  | Bit 6                  | Bit 5     | Bit 4    | Bit 3      | Bit 2       | Bit 1   | Bit 0        | Register on<br>Page |

|-----------------------|------------------------|------------------------|-----------|----------|------------|-------------|---------|--------------|---------------------|

| ADCON0                | _                      |                        |           | CHS<4:0> |            |             | GO/DONE | GO/DONE ADON |                     |

| ADCON1                | ADFM                   |                        | ADCS<2:0> |          | —          | ADNREF      | ADPR    | EF<1:0       | 151                 |

| ADRESH                | A/D Result Re          | egister High           |           |          |            |             |         |              | 152, 153            |

| ADRESL                | A/D Result Re          | egister Low            |           |          |            |             |         |              | 152, 153            |

| ANSELA                | —                      | _                      | _         | ANSA4    | —          | ANSA2       | ANSA1   | ANSA0        | 123                 |

| ANSELB <sup>(1)</sup> | —                      | —                      | ANSB5     | ANSB4    | _          | —           | —       | —            | 129                 |

| ANSELC                | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _         | _        | ANSC3      | ANSC2       | ANSC1   | ANSC0        | 134                 |

| CCP4CON               | P4M                    | <1:0>                  | DC4E      | <1:0>    | CCP4M<3:0> |             |         |              | 224                 |

| INLVLA                | —                      | —                      | INLVLA5   | INLVLA4  | INLVLA3    | INLVLA2     | INLVLA1 | INLVLA0      | 124                 |

| INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6                | INLVLB5   | INLVLB4  | _          | _           | —       | _            | 129                 |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5   | INLVLC4  | INLVLC3    | INLVLC2     | INLVLC1 | INLVLC0      | 135                 |

| INTCON                | GIE                    | PEIE                   | TMR0IE    | INTE     | IOCIE      | TMR0IF      | INTF    | IOCIF        | 87                  |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE      | TXIE     | SSP1IE     | CCP1IE      | TMR2IE  | TMR1IE       | 88                  |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF      | TXIF     | SSP1IF     | CCP1IF      | TMR2IF  | TMR1IF       | 92                  |

| TRISA                 | —                      | —                      | TRISA5    | TRISA4   | TRISA3     | TRISA2      | TRISA1  | TRISA0       | 122                 |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5    | TRISB4   | _          | —           | —       | —            | 128                 |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5    | TRISC4   | TRISC3     | TRISC2      | TRISC1  | TRISC0       | 133                 |

| FVRCON                | FVREN                  | FVRRDY                 | TSEN      | TSRNG    | CDAFV      | /R<1:0>     | ADEVE   | २<1:0>       | 142                 |

| DACCON0               | DACEN                  | DACLPS                 | DACOE     | _        | DACPS      | SS<1:0> — [ |         | DACNSS       | 160                 |

| DACCON1               | —                      | —                      | —         |          |            | DACR<4:0>   |         |              | 160                 |

#### **TABLE 16-3:** SUMMARY OF REGISTERS ASSOCIATED WITH ADC

x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC Legend: module. PIC16(L)F1829 only.

Note 1:

# 19.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 19-1) contain Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- · Speed/Power selection

- · Hysteresis enable

- · Output synchronization

The CMxCON1 registers (see Register 19-2) contain Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

### 19.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 19.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 19.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 19-1 shows the output state versus input conditions, including polarity control.

#### TABLE 19-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

# 19.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

# 19.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

# 19.9 Interaction with ECCP Logic

In some devices, a comparator output signal can be used to trigger the auto-shutdown feature found within the ECCP module. When the ECCP auto-shutdown feature is enabled and a comparator output signal is selected as the source, the comparator can be used simultaneously as a general purpose comparator and as the ECCP auto-shutdown source. In addition, the comparator output signal can also be routed to the designated I/O pin. If the ECCP Auto-Restart mode is also enabled, the comparators can be used as a closed loop analog feedback circuit to the ECCP, thereby creating an analog controlled PWM.

Please see section

#### for more information.

**Note:** When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

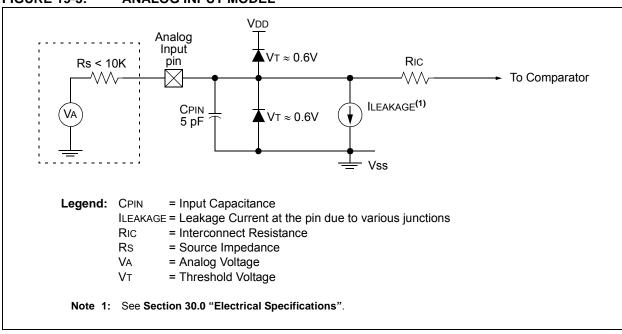

### FIGURE 19-3: ANALOG INPUT MODEL

# 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD.

If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 20.2 Option and Timer0 Control Register

# REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1          | R/W-1/1         | R/W-1/1                                 | R/W-1/1        | R/W-1/1           | R/W-1/1          | R/W-1/1          | R/W-1/1   |  |  |  |

|------------------|-----------------|-----------------------------------------|----------------|-------------------|------------------|------------------|-----------|--|--|--|

| WPUEN            | INTEDG          | TMR0CS                                  | TMR0SE         | PSA               |                  | PS<2:0>          |           |  |  |  |

| bit 7            | ÷               | ÷                                       |                | ÷                 |                  |                  | bit (     |  |  |  |

|                  |                 |                                         |                |                   |                  |                  |           |  |  |  |

| Legend:          |                 |                                         |                |                   |                  |                  |           |  |  |  |

| R = Readable     | bit             | W = Writable I                          | oit            | U = Unimplem      | nented bit, read | as '0'           |           |  |  |  |

| u = Bit is unch  | nanged          | x = Bit is unkn                         | own            | -n/n = Value a    | t POR and BOR    | Value at all oth | er Resets |  |  |  |

| '1' = Bit is set |                 | '0' = Bit is clea                       | ared           |                   |                  |                  |           |  |  |  |

| bit 7            |                 | ak Pull-up Enabl                        | o hit          |                   |                  |                  |           |  |  |  |

|                  |                 | pull-ups are disa                       |                | ICLR if it is ena | bled)            |                  |           |  |  |  |

|                  |                 | ll-ups are enable                       | · ·            |                   | ,                |                  |           |  |  |  |

| bit 6            | INTEDG: Inte    | errupt Edge Sele                        | ct bit         |                   |                  |                  |           |  |  |  |

|                  |                 | on rising edge of                       |                |                   |                  |                  |           |  |  |  |

|                  | 0 = Interrupt   | on falling edge o                       | f INT pin      |                   |                  |                  |           |  |  |  |

| bit 5            | TMR0CS: Tir     | mer0 Clock Sour                         | ce Select bit  |                   |                  |                  |           |  |  |  |

|                  |                 | on on TOCKI pin                         |                |                   |                  |                  |           |  |  |  |

|                  | 0 = Internal ir | nstruction cycle of                     | clock (Fosc/4) |                   |                  |                  |           |  |  |  |

| bit 4            |                 | Timer0 Source Edge Select bit           |                |                   |                  |                  |           |  |  |  |

|                  |                 | t on high-to-low                        |                | •                 |                  |                  |           |  |  |  |

|                  |                 | t on low-to-high                        |                |                   |                  |                  |           |  |  |  |

| bit 3            |                 | ler Assignment b                        |                |                   |                  |                  |           |  |  |  |

|                  |                 | r is not assigned<br>r is assigned to t |                |                   |                  |                  |           |  |  |  |

| bit 2-0          |                 | escaler Rate Sel                        |                |                   |                  |                  |           |  |  |  |

|                  | Bit             | Value Timer0                            | Rate           |                   |                  |                  |           |  |  |  |

|                  |                 | 000 1:2                                 |                |                   |                  |                  |           |  |  |  |

|                  |                 | 001 1:4                                 |                |                   |                  |                  |           |  |  |  |

|                  |                 | 010 1:8                                 |                |                   |                  |                  |           |  |  |  |

|                  |                 | 011 1:1<br>100 1:3                      |                |                   |                  |                  |           |  |  |  |

|                  |                 | 100 1:3<br>101 1:6                      |                |                   |                  |                  |           |  |  |  |

|                  |                 | 110 <b>1</b> :1                         |                |                   |                  |                  |           |  |  |  |

|                  |                 | 111 1:2                                 |                |                   |                  |                  |           |  |  |  |

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7      | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2          | Bit 1   | Bit 0   | Register<br>on Page |  |

|------------|------------|------------------------|---------|---------|---------|----------------|---------|---------|---------------------|--|

| CPSCON0    | CPSON      | CPSRM                  | _       | _       | CPSRN   | G<1:0>         | CPSOUT  | T0xCS   | 315                 |  |

| FVRCON     | FVREN      | FVRRDY                 | TSEN    | TSRNG   | CDAFV   | DAFVR<1:0> ADF |         | २<1:0>  | 142                 |  |

| INLVLA     | _          |                        | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2        | INLVLA1 | INLVLA0 | 124                 |  |

| INTCON     | GIE        | PEIE                   | TMR0IE  | INTE    | IOCIE   | TMR0IF         | INTF    | IOCIF   | 87                  |  |

| OPTION_REG | WPUEN      | INTEDG                 | TMR0CS  | TMR0SE  | PSA     |                | 176     |         |                     |  |

| TMR0       | Timer0 Mod | Timer0 Module Register |         |         |         |                |         |         |                     |  |

| TRISA      | _          |                        | TRISA5  | TRISA4  | TRISA3  | TRISA2         | TRISA1  | TRISA0  | 122                 |  |

Legend: — Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

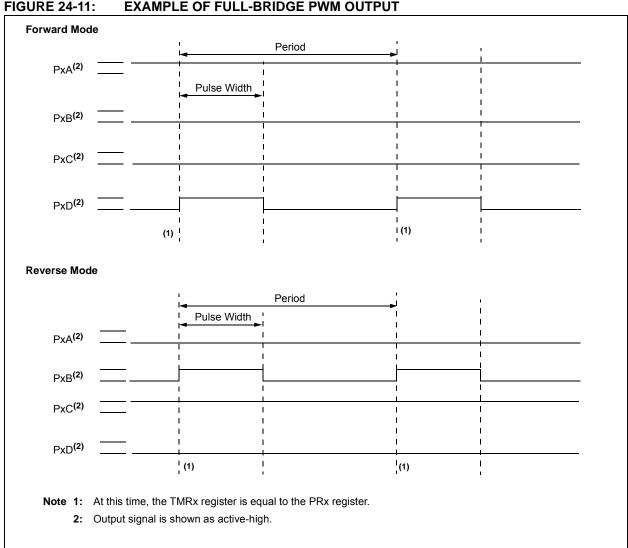

FIGURE 24-11: **EXAMPLE OF FULL-BRIDGE PWM OUTPUT**

# PIC16(L)F1825/9

### 25.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 25-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 25.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

# 25.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

# 25.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

25.6.6.4 Typical Transmit Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all eight bits are transmitted.

- 11. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

# 26.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 26.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 26.4.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE, Global Interrupt Enable, bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

### 26.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for synchronous slave transmission (see Section 26.4.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# 26.5.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| PIC16LF       | 1825/9                         | Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended         Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for extended |            |       |            |        |                                                                 |  |

|---------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------------|--------|-----------------------------------------------------------------|--|

| PIC16F1       | 825/9                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |       |            |        |                                                                 |  |

| Param.<br>No. | Sym.                           | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min.       | Тур†  | Max.       | Units  | Conditions                                                      |  |

| D001          | Vdd                            | Supply Voltage (VDDMIN, VDDMAX)                                                                                                                                                                                                                                                                                                                                                                                                                                |            |       |            |        |                                                                 |  |

|               |                                | PIC16LF1825/9                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.8<br>2.5 | _     | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )               |  |

| D001          |                                | PIC16F1825/9                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.8<br>2.5 | _     | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )               |  |

| D002*         | Vdr                            | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                      |            |       |            | •      |                                                                 |  |

|               |                                | PIC16LF1825/9                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.5        | -     | _          | V      | Device in Sleep mode                                            |  |

| D002*         |                                | PIC16F1825/9                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.7        | -     | _          | V      | Device in Sleep mode                                            |  |