# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The High directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |             |        |       |      |  |

|-----------|-------------|--------|-------|------|--|

| RETLW     | DATA0       | ;Ir    | ndex0 | data |  |

| RETLW     | DATA1       | ;Ir    | ndex1 | data |  |

| RETLW     | DATA2       |        |       |      |  |

| RETLW     | DATA3       |        |       |      |  |

| my_functi | on          |        |       |      |  |

| ; LO      | IS OF CODE. |        |       |      |  |

| MOVLW     | LOW cons    | tants  |       |      |  |

| MOVWF     | FSR1L       |        |       |      |  |

| MOVLW     | HIGH con    | stants | 5     |      |  |

| MOVWF     | FSR1H       |        |       |      |  |

| MOVIW     | 0[FSR1]     |        |       |      |  |

| ;THE PROG | RAM MEMORY  | IS IN  | W     |      |  |

|           |             |        |       |      |  |

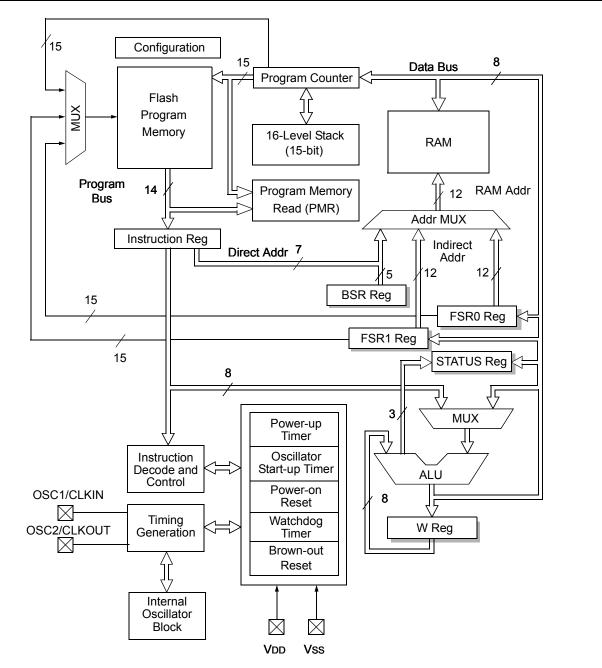

## 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- · 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "**Indirect Addressing**" for more information.

Data Memory uses a 12-bit address. The upper seven bits of the address define the Bank address and the lower five bits select the registers/RAM in that bank.

#### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC16(L)F1825/9. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

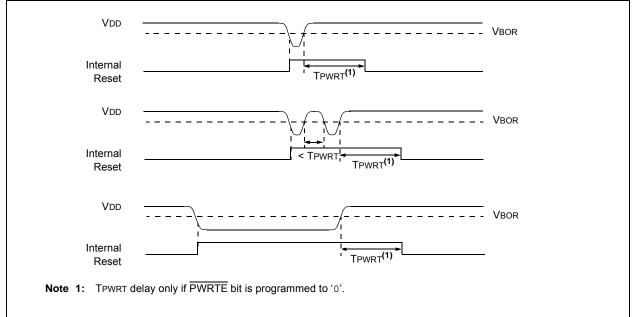

### REGISTER 7-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u                                                                                                                                            | U-0                                                                                          | U-0                        | U-0                                                      | U-0                                      | U-0                | U-0               | R-q/u      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|------------------------------------------|--------------------|-------------------|------------|--|

| SBOREN                                                                                                                                             | —                                                                                            | —                          | —                                                        | —                                        | —                  | —                 | BORRDY     |  |

| bit 7                                                                                                                                              |                                                                                              |                            |                                                          |                                          | -                  |                   | bit 0      |  |

|                                                                                                                                                    |                                                                                              |                            |                                                          |                                          |                    |                   |            |  |

| Legend:                                                                                                                                            |                                                                                              |                            |                                                          |                                          |                    |                   |            |  |

| R = Readable b                                                                                                                                     | oit                                                                                          | W = Writable b             | oit                                                      | U = Unimplen                             | nented bit, read a | as '0'            |            |  |

| u = Bit is uncha                                                                                                                                   | anged                                                                                        | x = Bit is unkn            | own                                                      | -n/n = Value a                           | at POR and BOR     | /Value at all oth | ner Resets |  |

| '1' = Bit is set                                                                                                                                   |                                                                                              | '0' = Bit is clea          | ared                                                     | q = Value dep                            | ends on conditio   | on                |            |  |

| bit 7<br>bit 6-1                                                                                                                                   | If BOREN <1:0<br>SBOREN is re<br>If BOREN <1:0<br>1 = BOR Ena<br>0 = BOR Disa<br>Unimplement | abled<br>abled: Read as '0 | tion Word $1 \neq$<br>as no effect on<br>tion Word $1 =$ | 0 <u>1</u> :<br>the BOR.<br>0 <u>1</u> : |                    |                   |            |  |

| bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive |                                                                                              |                            |                                                          |                                          |                    |                   |            |  |

| TADLE /- | ABLE 7-5. SUMMART OF REGISTERS ASSOCIATED WITH RESETS |        |       |       |       |        |       |        |                     |  |  |

|----------|-------------------------------------------------------|--------|-------|-------|-------|--------|-------|--------|---------------------|--|--|

| Name     | Bit 7                                                 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |  |  |

| BORCON   | SBOREN                                                | _      |       |       | _     |        |       | BORRDY | 76                  |  |  |

| PCON     | STKOVF                                                | STKUNF | _     | _     | RMCLR | RI     | POR   | BOR    | 80                  |  |  |

| STATUS   | _                                                     | _      | _     | TO    | С     | 22     |       |        |                     |  |  |

| WDTCON   |                                                       |        |       | V     |       | SWDTEN | 100   |        |                     |  |  |

TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — Unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

#### REGISTER 8-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|---------|---------|-----|-----|---------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | —   | CCP2IE  |

| bit 7   |         |         |         |         |     |     | bit 0   |

| Legend:              |           |                                                                                       |                                                       |

|----------------------|-----------|---------------------------------------------------------------------------------------|-------------------------------------------------------|

| R = Readal           | ole bit   | W = Writable bit                                                                      | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged |           | x = Bit is unknown                                                                    | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is s       | et        | '0' = Bit is cleared                                                                  |                                                       |

| bit 7                | OSFIE: Os | scillator Fail Interrupt Enable                                                       | bit                                                   |

|                      |           | es the Oscillator Fail interrup<br>les the Oscillator Fail interrup                   |                                                       |

| bit 6                | C2IE: Con | nparator C2 Interrupt Enable                                                          | bit                                                   |

|                      |           | es the Comparator C2 interrules the Comparator C2 interr                              | •                                                     |

| bit 5                | C1IE: Con | nparator C1 Interrupt Enable                                                          | bit                                                   |

|                      |           | es the Comparator C1 interrules the Comparator C1 interrules the Comparator C1 interr |                                                       |

| bit 4                | EEIE: EEF | ROM Write Completion Inter                                                            | rrupt Enable bit                                      |

|                      |           | es the EEPROM write compl<br>les the EEPROM write comp                                | •                                                     |

| bit 3                | BCL1IE: N | ISSP Bus Collision Interrupt                                                          | Enable bit                                            |

|                      |           | es the MSSP bus collision in<br>les the MSSP bus collision ir                         | I                                                     |

| bit 2-1              | Unimplem  | nented: Read as '0'                                                                   |                                                       |

| bit 0                | CCP2IE: ( | CCP2 Interrupt Enable bit                                                             |                                                       |

|                      | 1 = Enabl | es the CCP2 interrupt                                                                 |                                                       |

|                      | 0 = Disab | les the CCP2 interrupt                                                                |                                                       |

# 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EED-ATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

## 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

## 12.2 PORTA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-4). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-2 shows how to initialize a port.

Reading the PORTA register (Register 12-3) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLA register (Register 12-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1825/9-I/E" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 12.2.1 ANSELA REGISTER

The ANSELA register (Register 12-6) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### EXAMPLE 12-2: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

| Name       | Bit 7   | Bit 6                  | Bit 5                  | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|------------------------|------------------------|-----------------------|---------|---------|---------|---------|---------------------|

| ANSELA     | _       | —                      | -                      | ANSA4                 | _       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| APFCON0    | RXDTSEL | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup>  | _                     | T1GSEL  | TXCKSEL | _       | _       | 118                 |

| APFCON1    | —       | —                      | SDO2SEL <sup>(1)</sup> | SS2SEL <sup>(1)</sup> | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL | 119                 |

| INLVLA     | _       | —                      | INLVLA5                | INLVLA4               | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| LATA       | _       | —                      | LATA5                  | LATA4                 | _       | LATA2   | LATA1   | LATA0   | 123                 |

| OPTION_REG | WPUEN   | INTEDG                 | TMR0CS                 | TMR0SE                | PSA     |         | PS<2:0> |         | 176                 |

| PORTA      | _       | —                      | RA5                    | RA4                   | RA3     | RA2     | RA1     | RA0     | 122                 |

| TRISA      | _       | —                      | TRISA5                 | TRISA4                | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| WPUA       | —       | —                      | WPUA5                  | WPUA4                 | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 124                 |

x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA. PIC16(L)F1829 only. PIC16(L)F1825 only. Legend:

Note 1:

2:

#### **TABLE 12-4:** SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|-----------|---------|---------|---------------------|

| 0015104 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREI     | N<1:0>  | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | FOSC<2:0> |         |         | 48                  |

Legend: - Unimplemented location, read as '0'. Shaded cells are not used by PORTA.

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA                | —       | _       | _       | ANSA4   | —       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| ANSELB <sup>(1)</sup> | —       | _       | ANSB5   | ANSB4   | —       | —       | _       | —       | 129                 |

| INLVLA                | _       | _       | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| INLVLB <sup>(1)</sup> | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 |         |         | -       |         | 129                 |

| INTCON                | GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF   | 87                  |

| IOCAF                 | _       | _       | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 138                 |

| IOCAN                 | —       | _       | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 138                 |

| IOCAP                 | _       |         | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 137                 |

| IOCBF <sup>(1)</sup>  | IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | —       | _       | _       | —       | 139                 |

| IOCBN <sup>(1)</sup>  | IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | _       |         | _       | _       | 139                 |

| IOCBP <sup>(1)</sup>  | IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | —       | —       | _       | —       | 138                 |

| TRISA                 | _       | _       | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISB <sup>(1)</sup>  | TRISB7  | TRISB6  | TRISB5  | TRISB4  | —       | —       | —       | —       | 128                 |

### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — Unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

**Note 1:** PIC16(L)F1829 only.

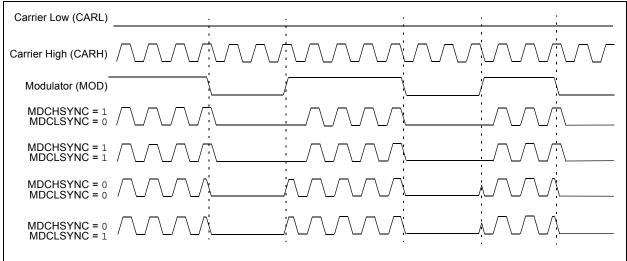

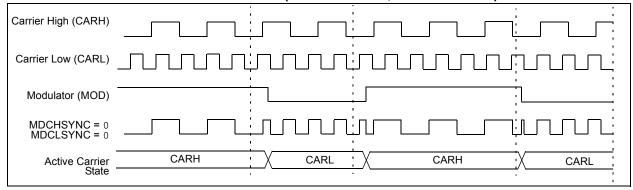

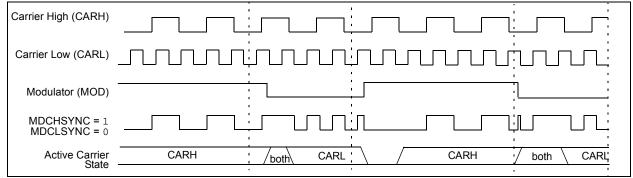

### FIGURE 23-2: ON OFF KEYING (OOK) SYNCHRONIZATION

### EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

### FIGURE 23-3: CARRIER HIGH SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 0)

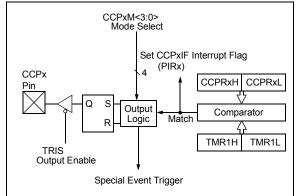

## 24.2 Compare Mode

The Compare mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- · Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 24-2 shows a simplified diagram of the Compare operation.

#### FIGURE 24-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 24.2.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON0 or APFCON1 register. Refer to **Section 12.1** "Alternate Pin Function" for more details.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 24.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

### 24.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

### 24.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- · Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Special Event Trigger output starts an A/D conversion (if the A/D module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

#### TABLE 24-3: SPECIAL EVENT TRIGGER

| Device          | CCPx/ECCPx |

|-----------------|------------|

| PIC16(L)F1825/9 | CCP4       |

Refer to **Section 16.2.5 "Special Event Trigger**" for more information.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 25.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

| Name                  | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4                  | Bit 3   | Bit 2   | Bit 1                  | Bit 0                  | Register on<br>Page |

|-----------------------|------------------------|------------------------|------------------------|------------------------|---------|---------|------------------------|------------------------|---------------------|

| ANSELA                | —                      | _                      | _                      | ANSA4                  | _       | ANSA2   | ANSA1                  | ANSA0                  | 122                 |

| ANSELB <sup>(1)</sup> | —                      | _                      | ANSB5                  | ANSB4                  | _       | _       | _                      | _                      | 129                 |

| ANSELC                | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _                      | _                      | ANSC3   | ANSC2   | ANSC1                  | ANSC0                  | 134                 |

| APFCON0               | RXDTSEL                | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup>  | _                      | T1GSEL  | TXCKSEL | _                      | —                      | 118                 |

| APFCON1               | —                      | -                      | SDO2SEL <sup>(1)</sup> | SS2SEL <sup>(1)</sup>  | P1DSEL  | P1CSEL  | P2BSEL                 | CCP2SEL                | 119                 |

| INLVLA                | —                      | -                      | INLVLA5 <sup>(1)</sup> | INLVLA4 <sup>(1)</sup> | INLVLA3 | INLVLA2 | INLVLA1                | INLVLA0                | 124                 |

| INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6                | INLVLB5                | INLVLB4                | _       | _       | _                      | _                      | 129                 |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5                | INLVLC4                | INLVLC3 | INLVLC2 | INLVLC1 <sup>(1)</sup> | INLVLC0 <sup>(1)</sup> | 135                 |

| INTCON                | GIE                    | PEIE                   | TMR0IE                 | INTE                   | IOCIE   | TMR0IF  | INTF                   | IOCIF                  | 87                  |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE                   | TXIE                   | SSP1IE  | CCP1IE  | TMR2IE                 | TMR1IE                 | 88                  |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF                   | TXIF                   | SSP1IF  | CCP1IF  | TMR2IF                 | TMR1IF                 | 92                  |

| SSP1BUF               | Synchronous            | Serial Port Rece       | eive Buffer/Tran       | smit Register          |         |         |                        |                        | 233*                |

| SSP1CON1              | WCOL                   | SSPOV                  | SSPEN                  | CKP                    |         | SSPM    | <3:0>                  |                        | 277                 |

| SSP1CON3              | ACKTIM                 | PCIE                   | SCIE                   | BOEN                   | SDAHT   | SBCDE   | AHEN                   | DHEN                   | 279                 |

| SSP1STAT              | SMP                    | CKE                    | D/A                    | Р                      | S       | R/W     | UA                     | BF                     | 276                 |

| TRISA                 | _                      | _                      | TRISA5 <sup>(1)</sup>  | TRISA4 <sup>(1)</sup>  | TRISA3  | TRISA2  | TRISA1                 | TRISA0                 | 122                 |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5                 | TRISB4                 | _       | _       | _                      | —                      | 128                 |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5                 | TRISC4                 | TRISC3  | TRISC2  | TRISC1 <sup>(1)</sup>  | TRISC0 <sup>(1)</sup>  | 133                 |

#### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — Unimplemented location, read as '0'. Shaded cells are not used by the MSSP1 in SPI mode.

\* Page provides register information.

Note 1: PIC16(L)F1829 only.

2: PIC16(L)F1825 only.

# 25.6 I<sup>2</sup>C MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDAx and SCKx pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDAx and SCLx lines.

The following events will cause the SSPx Interrupt Flag bit, SSPxIF, to be set (SSPx interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- · Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

# 25.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCLx. See **Section 25.7 "Baud Rate Generator"** for more detail.

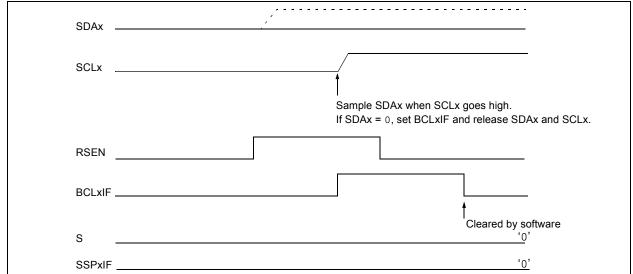

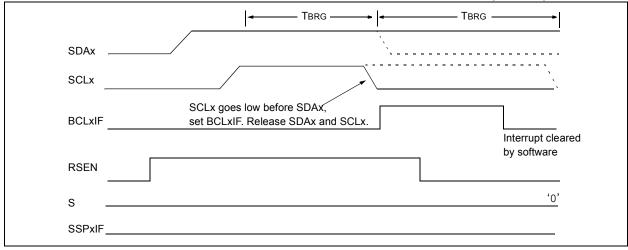

# 25.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from low level to high level. (CASE 1)

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'. (CASE 2)

When the user releases SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled. If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0' (Figure 25-36). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 25-37).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

#### FIGURE 25-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 25-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### REGISTER 25-5: SSPMSK: SSPx MASK REGISTER

| R/W-1/1                             | R/W-1/1                                                 | R/W-1/1                                                                                  | R/W-1/1                                          | R/W-1/1                                                         | R/W-1/1        | R/W-1/1                     | R/W-1/1 |  |  |  |

|-------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|----------------|-----------------------------|---------|--|--|--|

|                                     |                                                         |                                                                                          | MSK                                              | <7:0>                                                           |                |                             |         |  |  |  |

| bit 7                               |                                                         |                                                                                          |                                                  |                                                                 |                |                             | bit 0   |  |  |  |

|                                     |                                                         |                                                                                          |                                                  |                                                                 |                |                             |         |  |  |  |

| Legend:                             |                                                         |                                                                                          |                                                  |                                                                 |                |                             |         |  |  |  |

| R = Readable bit                    |                                                         | W = Writable bit                                                                         |                                                  | U = Unimplemented bit, read as '0'                              |                |                             |         |  |  |  |

| u = Bit is uncl                     | hanged                                                  | x = Bit is unknown                                                                       |                                                  | -n/n = Value at POR and BOR/Value at all other Resets           |                |                             |         |  |  |  |

| '1' = Bit is set '0' = Bit is clear |                                                         |                                                                                          | ared                                             |                                                                 |                |                             |         |  |  |  |

| bit 7-1                             | MSK<7:1>:                                               | Mack bite                                                                                |                                                  |                                                                 |                |                             |         |  |  |  |

|                                     | 1 = The rec                                             | eived address b<br>eived address b                                                       |                                                  |                                                                 |                | I <sup>2</sup> C address ma | atch    |  |  |  |

| bit 0                               | I <sup>2</sup> C Slave me<br>1 = The rec<br>0 = The rec | ask bit for I <sup>2</sup> C S<br>ode, 10-bit addr<br>eived address b<br>eived address b | ess (SSPM<3<br>it 0 is compar<br>it 0 is not use | 3:0> = 0111 or<br>ed to SSPxADI<br>d to detect I <sup>2</sup> C | D<0> to detect | l <sup>2</sup> C address m  | atch    |  |  |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

## REGISTER 25-6: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0          | R/W-0/0                                                                                       | R/W-0/0        | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|------------------|-----------------------------------------------------------------------------------------------|----------------|---------|--------------|------------------|----------|---------|--|

|                  |                                                                                               |                | ADD     | <7:0>        |                  |          |         |  |

| bit 7            |                                                                                               |                |         |              |                  |          | bit 0   |  |

|                  |                                                                                               |                |         |              |                  |          |         |  |

| Legend:          |                                                                                               |                |         |              |                  |          |         |  |

| R = Readable     | bit                                                                                           | W = Writable b | oit     | U = Unimpler | nented bit, read | d as '0' |         |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                |         |              |                  |          |         |  |

#### Master mode:

1' = Bit is set

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 26.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 26-9 for the timing of the Break character sequence.

#### 26.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- Load the TXREG with a dummy character to 3. initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character 4 into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is 5. reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### SEND BREAK CHARACTER SEQUENCE Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

#### 26.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in Section 26.3.3 "Auto-Wake-up on Break". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### **FIGURE 26-9:**

#### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 27.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

#### TABLE 26-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6                  | Bit 5                 | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register on<br>Page |

|---------|-------------------------------|------------------------|-----------------------|-------|--------|---------|--------|--------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL <sup>(1)</sup> | SS1SEL <sup>(1)</sup> | _     | T1GSEL | TXCKSEL | -      | —      | 118                 |

| BAUDCON | ABDOVF                        | RCIDL                  | _                     | SCKP  | BRG16  | _       | WUE    | ABDEN  | 292                 |

| INTCON  | GIE                           | PEIE                   | TMR0IE                | INTE  | IOCIE  | TMR0IF  | INTF   | IOCIF  | 87                  |

| PIE1    | TMR1GIE                       | ADIE                   | RCIE                  | TXIE  | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 88                  |

| PIR1    | TMR1GIF                       | ADIF                   | RCIF                  | TXIF  | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 92                  |

| RCSTA   | SPEN                          | RX9                    | SREN                  | CREN  | ADDEN  | FERR    | OERR   | RX9D   | 291                 |

| TXREG   | EUSART Transmit Data Register |                        |                       |       |        |         |        |        |                     |

| TXSTA   | CSRC                          | TX9                    | TXEN                  | SYNC  | SENDB  | BRGH    | TRMT   | TX9D   | 290                 |

Legend: — Unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

Note 1: PIC16(L)F1825 only.

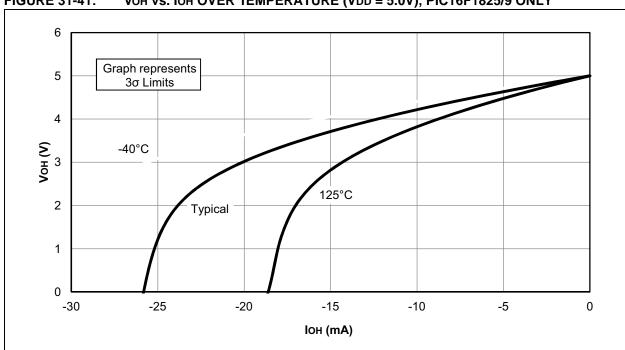

FIGURE 31-41: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V), PIC16F1825/9 ONLY

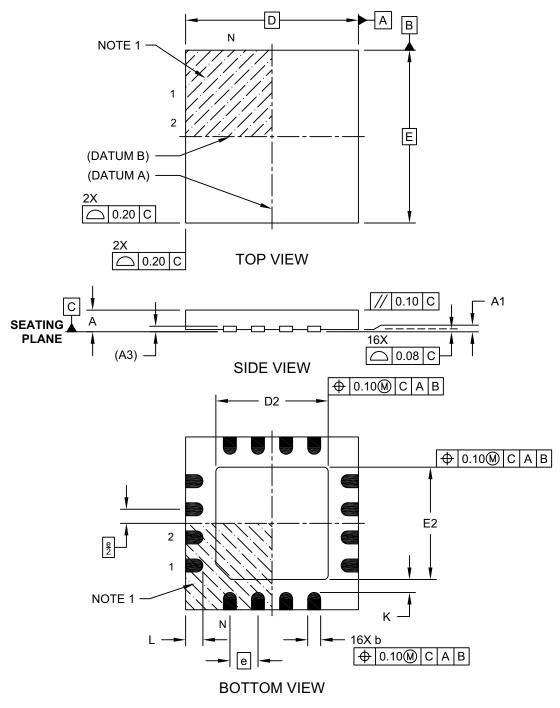

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support