Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829-i-gz |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Highlights (Continued)**

- · Data Signal Modulator Module:

- Selectable modulator and carrier sources

- SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

#### ECCP (Full-Bridge) ECCP (Half-Bridge) MSSP (I<sup>2</sup>C<sup>TM</sup>/SPI) Sheet Index Program Memory 10-bit ADC (ch) Data EEPROM CapSense (ch) Flash (words) Comparators Data SRAM (8/16-bit) EUSART SR Latch Timers I/O's<sup>(2)</sup> Debug<sup>(1)</sup> (bytes) (bytes) СC ХГР Device Data PIC12(L)F1822 (1) 2K 256 128 6 4 4 1 2/1 1 1 0/1/0 Y I/H Υ PIC12(L)F1840 4K 256 256 6 4 4 1 2/1 0/1/0 Y I/H Y (2)1 1 PIC16(L)F1823 (1) 2K 256 128 12 8 8 2 2/1 1 1 1/0/0 Y I/H Y PIC16(L)F1824 (3) 4K 256 256 12 8 8 2 4/1 1 1 1/1/2 Y I/H Υ PIC16(L)F1825 (4)8K 256 1024 12 8 8 2 4/1 1 1 1/1/2 Υ I/H Υ 12 2 1/0/0 I/H Υ PIC16(L)F1826 (5)2K 256 256 16 12 2/1 1 1 Υ PIC16(L)F1827 (5) 4K 256 384 16 12 12 2 4/1 1 2 1/1/2 Y I/H Y Y Y PIC16(L)F1828 (3)4K 256 256 18 12 12 2 4/1 1 1 1/1/2I/H PIC16(L)F1829 (4)8K 256 1024 18 12 12 2 4/1 1 2 1/1/2 Υ I/H Υ PIC16(L)F1847 8K 256 16 12 12 2 4/1 2 1/1/2 Y I/H Y (6)1024 1

## PIC12(L)F1822/1840/PIC16(L)F182x/1847 Family Types

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

3: DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

## TABLE 3-4: PIC16(L)F1825/9 MEMORY MAP, BANKS 8-15

| IADL |           |      | •         |      | NI WIAF, DA |      |           |       |                 |      |               |      |               |               |               |

|------|-----------|------|-----------|------|-------------|------|-----------|-------|-----------------|------|---------------|------|---------------|---------------|---------------|

|      | BANK 8    |      | BANK 9    |      | BANK 10     |      | BANK 11   |       | BANK 12         |      | BANK 13       |      | BANK 14       |               | BANK 15       |

| 400h | INDF0     | 480h | INDF0     | 500h | INDF0       | 580h | INDF0     | 600h  | INDF0           | 680h | INDF0         | 700h | INDF0         | 780h          | INDF0         |

| 401h | INDF1     | 481h | INDF1     | 501h | INDF1       | 581h | INDF1     | 601h  | INDF1           | 681h | INDF1         | 701h | INDF1         | 781h          | INDF1         |

| 402h | PCL       | 482h | PCL       | 502h | PCL         | 582h | PCL       | 602h  | PCL             | 682h | PCL           | 702h | PCL           | 782h          | PCL           |

| 403h | STATUS    | 483h | STATUS    | 503h | STATUS      | 583h | STATUS    | 603h  | STATUS          | 683h | STATUS        | 703h | STATUS        | 783h          | STATUS        |

| 404h | FSR0L     | 484h | FSR0L     | 504h | FSR0L       | 584h | FSR0L     | 604h  | FSR0L           | 684h | FSR0L         | 704h | FSR0L         | 784h          | FSR0L         |

| 405h | FSR0H     | 485h | FSR0H     | 505h | FSR0H       | 585h | FSR0H     | 605h  | FSR0H           | 685h | FSR0H         | 705h | FSR0H         | 785h          | FSR0H         |

| 406h | FSR1L     | 486h | FSR1L     | 506h | FSR1L       | 586h | FSR1L     | 606h  | FSR1L           | 686h | FSR1L         | 706h | FSR1L         | 786h          | FSR1L         |

| 407h | FSR1H     | 487h | FSR1H     | 507h | FSR1H       | 587h | FSR1H     | 607h  | FSR1H           | 687h | FSR1H         | 707h | FSR1H         | 787h          | FSR1H         |

| 408h | BSR       | 488h | BSR       | 508h | BSR         | 588h | BSR       | 608h  | BSR             | 688h | BSR           | 708h | BSR           | 788h          | BSR           |

| 409h | WREG      | 489h | WREG      | 509h | WREG        | 589h | WREG      | 609h  | WREG            | 689h | WREG          | 709h | WREG          | 789h          | WREG          |

| 40Ah | PCLATH    | 48Ah | PCLATH    | 50Ah | PCLATH      | 58Ah | PCLATH    | 60Ah  | PCLATH          | 68Ah | PCLATH        | 70Ah | PCLATH        | 78Ah          | PCLATH        |

| 40Bh | INTCON    | 48Bh | INTCON    | 50Bh | INTCON      | 58Bh | INTCON    | 60Bh  | INTCON          | 68Bh | INTCON        | 70Bh | INTCON        | 78Bh          | INTCON        |

| 40Ch | —         | 48Ch | —         | 50Ch | —           | 58Ch | —         | 60Ch  |                 | 68Ch | —             | 70Ch | —             | 78Ch          | —             |

| 40Dh | _         | 48Dh | _         | 50Dh | _           | 58Dh | _         | 60Dh  |                 | 68Dh | _             | 70Dh | —             | 78Dh          | _             |

| 40Eh | _         | 48Eh | _         | 50Eh | _           | 58Eh | _         | 60Eh  |                 | 68Eh | _             | 70Eh | —             | 78Eh          | _             |

| 40Fh | _         | 48Fh | _         | 50Fh | _           | 58Fh | _         | 60Fh  |                 | 68Fh | _             | 70Fh | —             | 78Fh          | _             |

| 410h | _         | 490h | _         | 510h | _           | 590h | _         | 610h  |                 | 690h | _             | 710h | —             | 790h          | _             |

| 411h | —         | 491h | —         | 511h | _           | 591h | _         | 611h  |                 | 691h | —             | 711h | —             | 791h          | —             |

| 412h | —         | 492h | —         | 512h | —           | 592h | —         | 612h  |                 | 692h | —             | 712h | —             | 792h          | —             |

| 413h | —         | 493h | —         | 513h | _           | 593h | _         | 613h  |                 | 693h | —             | 713h | —             | 793h          | —             |

| 414h | _         | 494h | _         | 514h | _           | 594h | _         | 614h  | _               | 694h | _             | 714h | —             | 794h          | —             |

| 415h | TMR4      | 495h | —         | 515h | _           | 595h | _         | 615h  |                 | 695h | —             | 715h | —             | 795h          | —             |

| 416h | PR4       | 496h | _         | 516h | _           | 596h | _         | 616h  | _               | 696h | _             | 716h | —             | 796h          | —             |

| 417h | T4CON     | 497h | —         | 517h | _           | 597h | _         | 617h  |                 | 697h | —             | 717h | —             | 797h          | —             |

| 418h | _         | 498h | _         | 518h | _           | 598h | _         | 618h  |                 | 698h | _             | 718h | —             | 798h          | _             |

| 419h | —         | 499h | —         | 519h | _           | 599h | _         | 619h  | —               | 699h | —             | 719h | —             | 799h          | —             |

| 41Ah | _         | 49Ah | _         | 51Ah | _           | 59Ah | _         | 61Ah  |                 | 69Ah | _             | 71Ah | —             | 79Ah          | _             |

| 41Bh | —         | 49Bh | —         | 51Bh | _           | 59Bh | _         | 61Bh  |                 | 69Bh | —             | 71Bh | —             | 79Bh          | —             |

| 41Ch | TMR6      | 49Ch | —         | 51Ch | —           | 59Ch | _         | 61Ch  | —               | 69Ch | —             | 71Ch | —             | 79Ch          | —             |

| 41Dh | PR6       | 49Dh | —         | 51Dh | _           | 59Dh | _         | 61Dh  |                 | 69Dh | —             | 71Dh | —             | 79Dh          | —             |

| 41Eh | T6CON     | 49Eh | —         | 51Eh | —           | 59Eh | _         | 61Eh  | —               | 69Eh | —             | 71Eh | —             | 79Eh          | —             |

| 41Fh | —         | 49Fh | —         | 51Fh | —           | 59Fh | —         | 61Fh  |                 | 69Fh | —             | 71Fh | —             | 79Fh          | —             |

| 420h |           | 4A0h |           | 520h |             | 5A0h |           | 620h  | General Purpose | 6A0h |               | 720h |               | 7A0h          |               |

|      | General   |      | General   |      | General     |      | General   |       | Register        |      |               |      |               |               |               |

|      | Purpose   |      | Purpose   |      | Purpose     |      | Purpose   | 64Fh  | 48 Bytes        |      | Unimplemented |      | Unimplemented |               | Unimplemented |

|      | Register  |      | Register  |      | Register    |      | Register  | 650h  |                 |      | Read as '0'   |      | Read as '0'   |               | Read as '0'   |

|      | 80 Bytes  |      | 80 Bytes  |      | 80 Bytes    |      | 80 Bytes  | 00011 | Unimplemented   |      |               |      |               |               |               |

| 46Fh | -         | 4EFh | -         | 56Fh | -           | 5EFh | -         | 66Fh  | Read as '0'     | 6EFh |               | 76Fh |               | 7EFh          |               |

|      |           |      |           |      |             |      |           |       |                 | 6F0h |               | -    |               | 7EFII<br>7F0h |               |

| 470h |           | 4F0h |           | 570h |             | 5F0h |           | 670h  |                 | orun |               | 770h |               | /FUN          |               |

|      | Accesses  |      | Accesses  |      | Accesses    |      | Accesses  |       | Accesses        |      | Accesses      |      | Accesses      |               | Accesses      |

|      | 70h – 7Fh |      | 70h – 7Fh |      | 70h – 7Fh   |      | 70h – 7Fh |       | 70h – 7Fh       |      | 70h – 7Fh     |      | 70h – 7Fh     |               | 70h – 7Fh     |

| 47Fh |           | 4FFh |           | 57Fh |             | 5FFh |           | 67Fh  |                 | 6FFh |               | 77Fh |               | 7FFh          |               |

Legend: = Unimplemented data memory locations, read as '0'

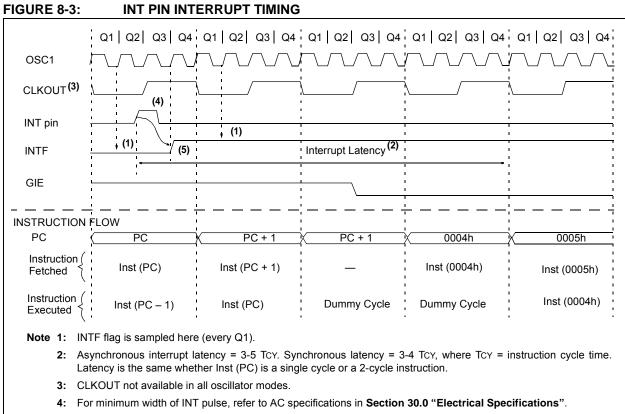

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

## 12.3 PORTB Registers (PIC16(L)F1829 only)

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-2 shows how to initialize a port.

Reading the PORTB register (Register 12-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The TRISB register (Register 12-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

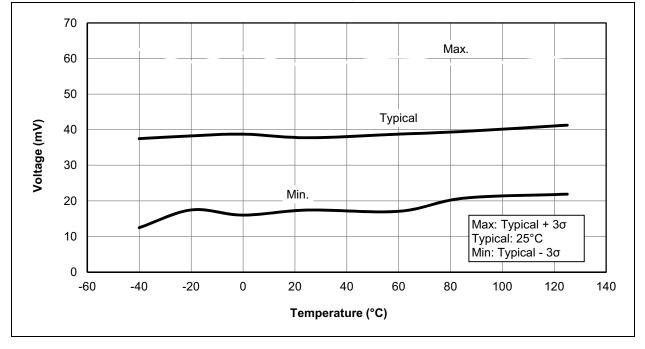

The INLVLB register (Register 12-14) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1825/9-I/E" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 12.3.1 ANSELB REGISTER

The ANSELB register (Register 12-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

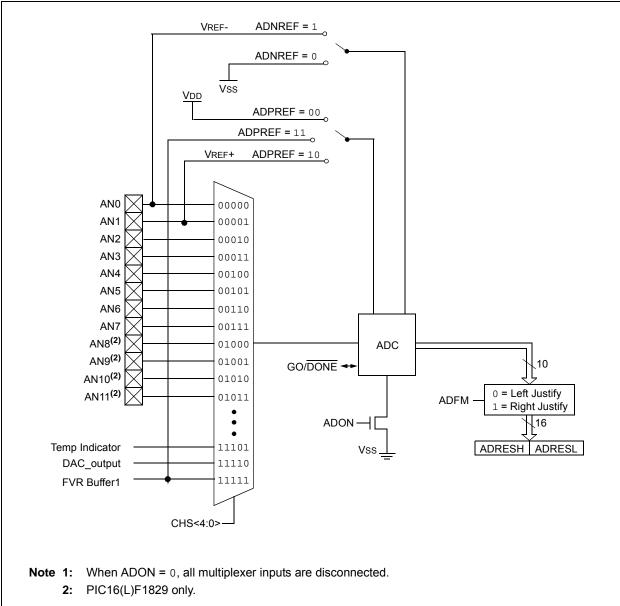

## 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

## FIGURE 16-1: ADC BLOCK DIAGRAM

**DDULE** a conversion. This interrupt can be used to wake-up the device from Sleep.

DC)

allows

10-bit binary

a conversion. This interrupt can be used to wake-up the device from Sleep.

The ADC can generate an interrupt upon completion of

## 23.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

## 23.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

## 23.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

## 23.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDMSODIS bit in the MDSRC register.

## 23.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

## 23.10 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

## 23.11 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

## 23.12 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

### REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                  | R/W-0/0                                                                                                                   | R/W-0/0                                                                                                                                                                                     | R/W-0/0                                                                                                                  | R/W-0/0                                                                                      | R/W-0/0                                          | R/W-0/0                                      |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|

| WCOL                    | SSPOV                                                                                                                                                                                                                                                                                                                       | SSPEN                                                                                                                     | CKP                                                                                                                                                                                         |                                                                                                                          | SSPN                                                                                         | 1<3:0>                                           |                                              |

| pit 7                   |                                                                                                                                                                                                                                                                                                                             |                                                                                                                           |                                                                                                                                                                                             |                                                                                                                          |                                                                                              |                                                  | bit (                                        |

|                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                           |                                                                                                                                                                                             |                                                                                                                          |                                                                                              |                                                  |                                              |

| Legend:                 |                                                                                                                                                                                                                                                                                                                             |                                                                                                                           |                                                                                                                                                                                             | 11 - 11-i                                                                                                                |                                                                                              |                                                  |                                              |

| R = Readable bit        |                                                                                                                                                                                                                                                                                                                             | W = Writable bit                                                                                                          | _                                                                                                                                                                                           | •                                                                                                                        | ted bit, read as '0'                                                                         |                                                  |                                              |

| u = Bit is unchang      | jea                                                                                                                                                                                                                                                                                                                         | x = Bit is unknow                                                                                                         |                                                                                                                                                                                             |                                                                                                                          | OR and BOR/Value                                                                             |                                                  |                                              |

| 1' = Bit is set         |                                                                                                                                                                                                                                                                                                                             | '0' = Bit is cleared                                                                                                      |                                                                                                                                                                                             | HS = Bit is set by                                                                                                       | / hardware                                                                                   | C = User cleared                                 |                                              |

| bit 7                   | 0 = No collision<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                                      | ne SSPxBUF registe<br>UF register is written                                                                              | ·                                                                                                                                                                                           |                                                                                                                          | itions were not valid<br>word (must be cleare                                                |                                                  | to be started                                |

| Dit 6                   | In SPI mode:<br>1 = A new byte i<br>Overflow ca<br>setting overf<br>SSPxBUF m<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                                           | n only occur in Slav<br>flow. In Master mode<br>egister (must be clea<br>v<br>eceived while the Si<br>eared in software). | SSPxBUF registe<br>e mode. In Slave i<br>e, the overflow bit is<br>ared in software).                                                                                                       | node, the user mus                                                                                                       | revious data. In case<br>t read the SSPxBUF,<br>new reception (and tr<br>previous byte. SSPC | even if only transmit<br>ansmission) is initiate | tting data, to avoic<br>ed by writing to the |

| bit 5                   | In both modes, w<br>In SPI mode:<br>1 = Enables ser<br>0 = Disables ser<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                                                     | erial port and config                                                                                                     | e pins must be pro<br>es SCKx, SDOx, s<br>ures these pins a<br>gures the SDAx a                                                                                                             | SDIx and SSx as the s I/O port pins                                                                                      | s input or output<br>e source of the serial<br>source of the serial p                        |                                                  |                                              |

| bit 4                   | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCLx release cor<br>1 = Enable clock                                                                                                                                                                                                                                 | clock is a high level<br>clock is a low level<br><u>e:</u><br>ntrol<br>ow (clock stretch). (<br><u>de:</u>                |                                                                                                                                                                                             | ata setup time.)                                                                                                         |                                                                                              |                                                  |                                              |

| bit 3-0                 | 0000 = SPI Mast<br>0001 = SPI Mast<br>0010 = SPI Mast<br>0010 = SPI Slave<br>0100 = SPI Slave<br>0100 = SPI Slave<br>0110 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Mast<br>1011 = I <sup>2</sup> C firmw<br>1000 = Reservec<br>1100 = Reservec<br>1110 = I <sup>2</sup> C Slave | e mode, 7-bit addres<br>mode, 10-bit addre<br>er mode, clock = Fo<br>er mode, clock = Fo<br>are controlled Mast           | DSC/4<br>DSC/16<br>DSC/64<br>MR2 output/2<br>Kx pin, <u>SSx</u> pin c<br>Kx pin, <u>SSx</u> pin c<br>SS<br>DSC / (4 * (SSPxAE<br>DSC/(4 * (SSPxAE<br>ter mode (Slave I<br>SS with Start and | ontrol enabled<br>ontrol disabled, SS<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup><br>dle)<br>Stop bit interrupts e | x can be used as I/0                                                                         | ) pin                                            |                                              |

| 2: Wh<br>3: Wh<br>4: SS | Aaster mode, the over<br>en enabled, these pi<br>en enabled, the SDA<br>PxADD values of 0,<br>PxADD value of '0' is                                                                                                                                                                                                         | ns must be proper<br>Ax and SCLx pins n<br>1 or 2 are not supp                                                            | y configured as ir<br>nust be configure<br>orted for I <sup>2</sup> C Mod                                                                                                                   | put or output.<br>d as inputs.<br>e.                                                                                     | mission) is initiated                                                                        | by writing to the SS                             | PxBUF register.                              |

## 26.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 26-9 for the timing of the Break character sequence.

#### 26.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### **FIGURE 26-9:** SEND BREAK CHARACTER SEQUENCE Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

### 26.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 26.3.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

## 26.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

### 26.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

### 26.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 26.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 26.4.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

## TABLE 30-21: DC CHARACTERISTICS FOR IPD SPECIFICATIONS FOR PIC16F1825/9-H (High Temp.)

| PIC16F | 1825/9                 | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |          |      |       |     |                                                                |  |  |  |

|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|-----|----------------------------------------------------------------|--|--|--|

| Param  | Davias Characteristics |                                                                                                                                                 | <b>T</b> |      |       |     | Condition                                                      |  |  |  |

| No.    | Device Characteristics | Min.                                                                                                                                            | Тур.     | Max. | Units | Vdd | Note                                                           |  |  |  |

|        | Power-Down Base Currer | nt (IPD) <sup>(2)</sup>                                                                                                                         |          |      |       |     |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 0.05     | 12   | μA    | 2.0 |                                                                |  |  |  |

| D020E  |                        | —                                                                                                                                               | 0.15     | 13   | μA    | 3.0 | IPD Base                                                       |  |  |  |

|        |                        | —                                                                                                                                               | 0.35     | 14   | μA    | 5.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 0.5      | 20   | μA    | 2.0 |                                                                |  |  |  |

| D021E  |                        | —                                                                                                                                               | 2.5      | 25   | μA    | 3.0 | WDT Current                                                    |  |  |  |

|        |                        | —                                                                                                                                               | 9.5      | 36   | μA    | 5.0 |                                                                |  |  |  |

| D022E  |                        | —                                                                                                                                               | 5.0      | 28   | μA    | 3.0 | BOR Current                                                    |  |  |  |

| DUZZL  |                        | —                                                                                                                                               | 6.0      | 36   | μA    | 5.0 | BOR Current                                                    |  |  |  |

| D023E  |                        | —                                                                                                                                               | 105      | 195  | μA    | 2.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 110      | 210  | μA    | 3.0 | <ul> <li>IPD Current (both comparators<br/>enabled)</li> </ul> |  |  |  |

|        |                        | —                                                                                                                                               | 116      | 220  | μA    | 5.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 50       | 105  | μA    | 2.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 55       | 110  | μA    | 3.0 | <ul> <li>IPD Current (one comparator<br/>enabled)</li> </ul>   |  |  |  |

|        |                        | —                                                                                                                                               | 60       | 125  | μA    | 5.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 30       | 58   | μA    | 2.0 |                                                                |  |  |  |

| D024E  |                        | —                                                                                                                                               | 45       | 85   | μA    | 3.0 | IPD (CVREF, high range)                                        |  |  |  |

|        |                        | —                                                                                                                                               | 75       | 142  | μA    | 5.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 39       | 76   | μA    | 2.0 |                                                                |  |  |  |

| D025E  |                        |                                                                                                                                                 | 59       | 114  | μA    | 3.0 | IPD (CVREF, low range)                                         |  |  |  |

|        |                        | —                                                                                                                                               | 98       | 190  | μA    | 5.0 |                                                                |  |  |  |

|        |                        | —                                                                                                                                               | 5.5      | 30   | μA    | 2.0 |                                                                |  |  |  |

| D026E  |                        | —                                                                                                                                               | 7.0      | 35   | μA    | 3.0 | IPD (T1 OSC, 32 kHz)                                           |  |  |  |

|        |                        |                                                                                                                                                 | 8.5      | 45   | μA    | 5.0 | <u> </u>                                                       |  |  |  |

| D027E  |                        |                                                                                                                                                 | 0.2      | 12   | μA    | 3.0 | IPD (ADC on not converting)                                    |  |  |  |

|        |                        | _                                                                                                                                               | 0.3      | 15   | μA    | 5.0 | -IPD (ADC on, not converting)                                  |  |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rage, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: A/D oscillator source is FRC.

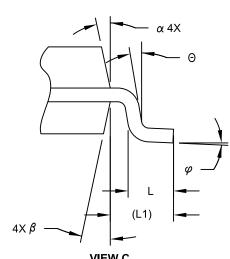

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| v | • | - | v |  | ٠ |  |

|---|---|---|---|--|---|--|

|   |   |   |   |  |   |  |

|   |   |   |   |  |   |  |

|                          | l N       | MILLIMETERS |          |      |  |  |  |

|--------------------------|-----------|-------------|----------|------|--|--|--|

| Dimension Lin            | nits      | MIN         | NOM      | MAX  |  |  |  |

| Number of Pins           | N         |             | 14       |      |  |  |  |

| Pitch                    | е         |             | 1.27 BSC |      |  |  |  |

| Overall Height           | A         | -           | -        | 1.75 |  |  |  |

| Molded Package Thickness | A2        | 1.25        | -        | -    |  |  |  |

| Standoff §               | A1        | 0.10        | -        | 0.25 |  |  |  |

| Overall Width            | E         |             | 6.00 BSC |      |  |  |  |

| Molded Package Width     | E1        | 3.90 BSC    |          |      |  |  |  |

| Overall Length           | D         | 8.65 BSC    |          |      |  |  |  |

| Chamfer (Optional)       | h         | 0.25        | -        | 0.50 |  |  |  |

| Foot Length              | L         | 0.40        | -        | 1.27 |  |  |  |

| Footprint                | L1        | 1.04 REF    |          |      |  |  |  |

| Lead Angle               | Θ         | 0°          | -        | -    |  |  |  |

| Foot Angle               | $\varphi$ | 0°          | -        | 8°   |  |  |  |

| Lead Thickness           | С         | 0.10        | -        | 0.25 |  |  |  |

| Lead Width               | b         | 0.31        | -        | 0.51 |  |  |  |

| Mold Draft Angle Top     | α         | 5°          | -        | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -        | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

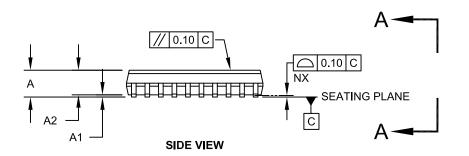

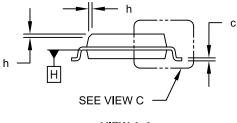

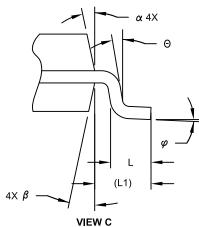

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| U                        | MILLIMETERS |          |           |      |  |  |

|--------------------------|-------------|----------|-----------|------|--|--|

| Dimension Lim            | nits        | MIN      | NOM       | MAX  |  |  |

| Number of Pins           | N           |          |           |      |  |  |

| Pitch                    | е           |          | 1.27 BSC  |      |  |  |

| Overall Height           | Α           | -        | -         | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05     | -         | -    |  |  |

| Standoff §               | A1          | 0.10     | -         | 0.30 |  |  |

| Overall Width            | E           |          | 10.30 BSC |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC |           |      |  |  |

| Overall Length           | D 12.80 BSC |          |           |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | -         | 0.75 |  |  |

| Foot Length              | L           | 0.40     | -         | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF |           |      |  |  |

| Lead Angle               | Θ           | 0°       | -         | -    |  |  |

| Foot Angle               | φ           | 0°       | -         | 8°   |  |  |

| Lead Thickness           | С           | 0.20     | -         | 0.33 |  |  |

| Lead Width               | b           | 0.31     | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°       | -         | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -         | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

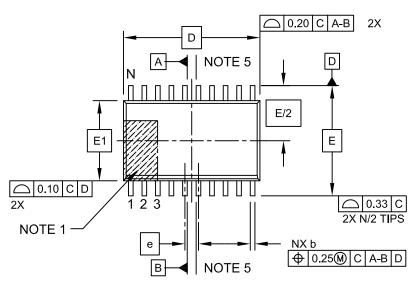

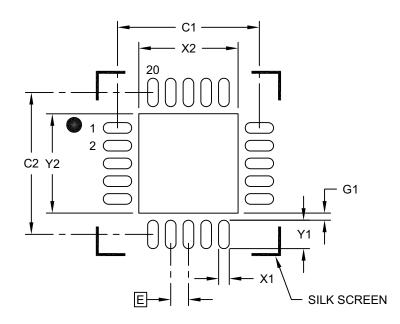

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS     |      |      |          |  |  |  |  |

|---------------------------------|-----------------|------|------|----------|--|--|--|--|

| Dimension                       | MIN             | NOM  | MAX  |          |  |  |  |  |

| Contact Pitch                   | Contact Pitch E |      |      | 0.50 BSC |  |  |  |  |

| Optional Center Pad Width       | X2              |      |      | 2.80     |  |  |  |  |

| Optional Center Pad Length      | Y2              |      |      | 2.80     |  |  |  |  |

| Contact Pad Spacing             | C1              |      | 4.00 |          |  |  |  |  |

| Contact Pad Spacing             | C2              |      | 4.00 |          |  |  |  |  |

| Contact Pad Width (X20)         | X1              |      |      | 0.30     |  |  |  |  |

| Contact Pad Length (X20)        | Y1              |      |      | 0.80     |  |  |  |  |

| Contact Pad to Center Pad (X20) | G1              | 0.20 |      |          |  |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2255A