Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

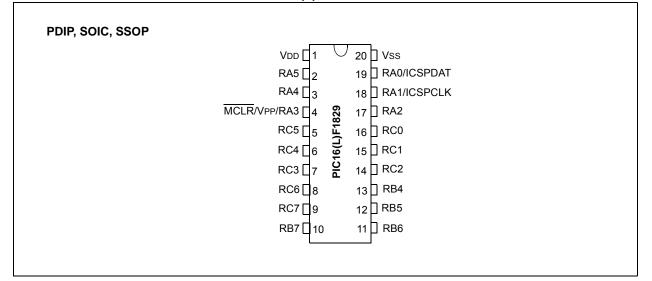

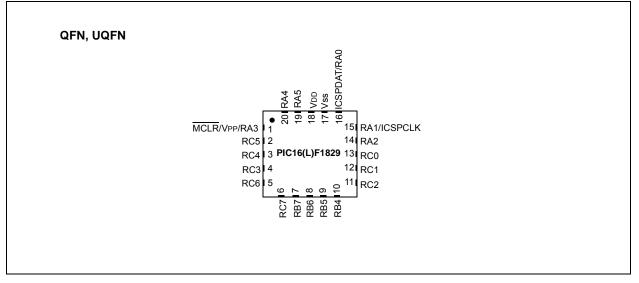

### FIGURE 3: 20-PIN DIAGRAM FOR PIC16(L)F1829

© 2010-2015 Microchip Technology Inc.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## TABLE 3-6:PIC16(L)F1825/9 MEMORY MAP, BANKS 24-31

| IADE |               | 0.0(1 | -)1 1023/3 Wit |      |               |      |               |      |               |      |               |      |               |      |                                       |

|------|---------------|-------|----------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------------------------------|

|      | BANK 24       |       | BANK 25        |      | BANK 26       |      | BANK 27       |      | BANK 28       |      | BANK 29       |      | BANK 30       |      | BANK 31                               |

| C00h | INDF0         | C80h  | INDF0          | D00h | INDF0         | D80h | INDF0         | E00h | INDF0         | E80h | INDF0         | F00h | INDF0         | F80h | INDF0                                 |

| C01h | INDF1         | C81h  | INDF1          | D01h | INDF1         | D81h | INDF1         | E01h | INDF1         | E81h | INDF1         | F01h | INDF1         | F81h | INDF1                                 |

| C02h | PCL           | C82h  | PCL            | D02h | PCL           | D82h | PCL           | E02h | PCL           | E82h | PCL           | F02h | PCL           | F82h | PCL                                   |

| C03h | STATUS        | C83h  | STATUS         | D03h | STATUS        | D83h | STATUS        | E03h | STATUS        | E83h | STATUS        | F03h | STATUS        | F83h | STATUS                                |

| C04h | FSR0L         | C84h  | FSR0L          | D04h | FSR0L         | D84h | FSR0L         | E04h | FSR0L         | E84h | FSR0L         | F04h | FSR0L         | F84h | FSR0L                                 |

| C05h | FSR0H         | C85h  | FSR0H          | D05h | FSR0H         | D85h | FSR0H         | E05h | FSR0H         | E85h | FSR0H         | F05h | FSR0H         | F85h | FSR0H                                 |

| C06h | FSR1L         | C86h  | FSR1L          | D06h | FSR1L         | D86h | FSR1L         | E06h | FSR1L         | E86h | FSR1L         | F06h | FSR1L         | F86h | FSR1L                                 |

| C07h | FSR1H         | C87h  | FSR1H          | D07h | FSR1H         | D87h | FSR1H         | E07h | FSR1H         | E87h | FSR1H         | F07h | FSR1H         | F87h | FSR1H                                 |

| C08h | BSR           | C88h  | BSR            | D08h | BSR           | D88h | BSR           | E08h | BSR           | E88h | BSR           | F08h | BSR           | F88h | BSR                                   |

| C09h | WREG          | C89h  | WREG           | D09h | WREG          | D89h | WREG          | E09h | WREG          | E89h | WREG          | F09h | WREG          | F89h | WREG                                  |

| C0Ah | PCLATH        | C8Ah  | PCLATH         | D0Ah | PCLATH        | D8Ah | PCLATH        | E0Ah | PCLATH        | E8Ah | PCLATH        | F0Ah | PCLATH        | F8Ah | PCLATH                                |

| C0Bh | INTCON        | C8Bh  | INTCON         | D0Bh | INTCON        | D8Bh | INTCON        | E0Bh | INTCON        | E8Bh | INTCON        | F0Bh | INTCON        | F8Bh | INTCON                                |

| C0Ch | —             | C8Ch  |                | D0Ch |               | D8Ch |               | E0Ch |               | E8Ch | _             | F0Ch |               | F8Ch |                                       |

| C0Dh | —             | C8Dh  |                | D0Dh |               | D8Dh |               | E0Dh |               | E8Dh | _             | F0Dh |               | F8Dh |                                       |

| C0Eh | -             | C8Eh  | _              | D0Eh | _             | D8Eh | _             | E0Eh | _             | E8Eh | -             | F0Eh | _             | F8Eh |                                       |

| C0Fh | —             | C8Fh  | —              | D0Fh | —             | D8Fh | —             | E0Fh | —             | E8Fh | —             | F0Fh | —             | F8Fh |                                       |

| C10h | —             | C90h  | —              | D10h | —             | D90h | —             | E10h | —             | E90h | —             | F10h | —             | F90h |                                       |

| C11h | —             | C91h  | —              | D11h | —             | D91h | —             | E11h | —             | E91h | —             | F11h | —             | F91h |                                       |

| C12h | _             | C92h  | —              | D12h | —             | D92h | —             | E12h | —             | E92h | _             | F12h | —             | F92h |                                       |

| C13h | _             | C93h  | —              | D13h | —             | D93h | —             | E13h | —             | E93h | _             | F13h | _             | F93h |                                       |

| C14h | —             | C94h  | _              | D14h | _             | D94h | _             | E14h | _             | E94h | —             | F14h | _             | F94h |                                       |

| C15h | _             | C95h  | —              | D15h | —             | D95h | —             | E15h | —             | E95h | _             | F15h | _             | F95h |                                       |

| C16h | —             | C96h  | —              | D16h | —             | D96h | —             | E16h | —             | E96h | —             | F16h | —             | F96h |                                       |

| C17h | —             | C97h  | —              | D17h | —             | D97h | —             | E17h | —             | E97h | —             | F17h | —             | F97h | One Table 0 7 fee                     |

| C18h | —             | C98h  | —              | D18h | —             | D98h | —             | E18h | —             | E98h | —             | F18h | —             | F98h | See Table 3-7 for<br>register mapping |

| C19h | _             | C99h  | —              | D19h | —             | D99h | —             | E19h | —             | E99h | _             | F19h | —             | F99h | details                               |

| C1Ah | —             | C9Ah  | —              | D1Ah | —             | D9Ah | —             | E1Ah | —             | E9Ah | _             | F1Ah | —             | F9Ah |                                       |

| C1Bh | _             | C9Bh  | —              | D1Bh | —             | D9Bh | —             | E1Bh | —             | E9Bh | _             | F1Bh | _             | F9Bh |                                       |

| C1Ch | _             | C9Ch  | —              | D1Ch | —             | D9Ch | —             | E1Ch | —             | E9Ch | _             | F1Ch | _             | F9Ch |                                       |

| C1Dh | —             | C9Dh  | —              | D1Dh | —             | D9Dh | —             | E1Dh | —             | E9Dh | —             | F1Dh | —             | F9Dh |                                       |

| C1Eh | —             | C9Eh  | —              | D1Eh | —             | D9Eh | —             | E1Eh | —             | E9Eh | —             | F1Eh | —             | F9Eh |                                       |

| C1Fh | —             | C9Fh  | —              | D1Fh | —             | D9Fh | —             | E1Fh | —             | E9Fh | —             | F1Fh | —             | F9Fh |                                       |

| C20h |               | CA0h  |                | D20h |               | DA0h |               | E20h |               | EA0h |               | F20h |               | FA0h |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

|      | Unimplemented |       | Unimplemented  |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      |                                       |

|      | Read as '0'   |       | Read as '0'    |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

| C6Fh |               | CEFh  |                | D6Fh |               | DEFh |               | E6Fh |               | EEFh |               | F6Fh |               | FEFh |                                       |

| C70h |               | CF0h  |                | D70h |               | DF0h |               | E70h |               | EF0h |               | F70h |               | FF0h |                                       |

|      | Accesses      |       | Accesses       |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses                              |

|      | 70h – 7Fh     |       | 70h – 7Fh      |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh                             |

| CFFh |               | CFFh  |                | D7Fh |               | DFFh |               | E7Fh |               | EFFh |               | F7Fh |               | FFFh |                                       |

|      |               |       |                |      |               |      |               |      |               |      |               |      |               |      |                                       |

**Legend:** = Unimplemented data memory locations, read as '0'.

| Address             | Name                 | Bit 7                            | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 5            | Bit 4      | Bit 3        | Bit 2       | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

|---------------------|----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------------|-------------|---------|--------|----------------------|---------------------------------|--|

| Bank 1              |                      |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |            |              |             |         |        |                      |                                 |  |

| 080h <sup>(1)</sup> | INDF0                | Addressing th<br>(not a physical |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | es contents of   | FSR0H/FSR0 | L to address | data memory | 1       |        | XXXX XXXX            | xxxx xxxx                       |  |

| 081h <sup>(1)</sup> | INDF1                | Addressing th<br>(not a physical |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | es contents of   | FSR1H/FSR1 | L to address | data memory | 1       |        | XXXX XXXX            | xxxx xxxx                       |  |

| 082h <sup>(1)</sup> | PCL                  | Program Cou                      | inter (PC) Lea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | st Significant E | Byte       |              |             |         |        | 0000 0000            | 0000 0000                       |  |

| 083h <sup>(1)</sup> | STATUS               | _                                | <u>TO</u> PD Z DC C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |            |              |             |         |        |                      | q quuu                          |  |

| 084h <sup>(1)</sup> | FSR0L                | Indirect Data                    | ndirect Data Memory Address 0 Low Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |            |              |             |         |        |                      |                                 |  |

| 085h <sup>(1)</sup> | FSR0H                | Indirect Data                    | Indirect Data Memory Address 0 High Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |            |              |             |         |        |                      |                                 |  |

| 086h <sup>(1)</sup> | FSR1L                | Indirect Data                    | Memory Addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | 0000 0000  | uuuu uuuu    |             |         |        |                      |                                 |  |

| 087h <sup>(1)</sup> | FSR1H                | Indirect Data                    | lirect Data Memory Address 1 High Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |            |              |             |         |        |                      | 0000 0000                       |  |

| 088h <sup>(1)</sup> | BSR                  | _                                | — — BSR<4:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |            |              |             |         | 0 0000 | 0 0000               |                                 |  |

| 089h <sup>(1)</sup> | WREG                 | Working Reg                      | /orking Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |            |              |             |         |        |                      | uuuu uuuu                       |  |

| 08Ah <sup>(1)</sup> | PCLATH               | —                                | Write Buffer for the upper 7 bits of the Program Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |            |              |             |         |        | -000 0000            | -000 0000                       |  |

| 08Bh <sup>(1)</sup> | INTCON               | GIE                              | PEIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TMR0IE           | INTE       | IOCIE        | TMR0IF      | INTF    | IOCIF  | 0000 0000            | 0000 0000                       |  |

| 08Ch                | TRISA                | —                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TRISA5           | TRISA4     | TRISA3       | TRISA2      | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |  |

| 08Dh                | TRISB <sup>(2)</sup> | TRISB7                           | TRISB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRISB5           | TRISB4     | _            | _           | —       | _      | 1111                 | 1111                            |  |

| 08Eh                | TRISC                | TRISC7 <sup>(2)</sup>            | TRISC6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRISC5           | TRISC4     | TRISC3       | TRISC2      | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |  |

| 08Fh                | —                    | Unimplement                      | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |            |              |             |         |        | _                    | _                               |  |

| 090h                | —                    | Unimplement                      | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |            |              |             |         |        | _                    | _                               |  |

| 091h                | PIE1                 | TMR1GIE                          | ADIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RCIE             | TXIE       | SSP1IE       | CCP1IE      | TMR2IE  | TMR1IE | 0000 0000            | 0000 0000                       |  |

| 092h                | PIE2                 | OSFIE                            | C2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C1IE             | EEIE       | BCL1IE       | _           | —       | CCP2IE | 0000 00              | 0000 00                         |  |

| 093h                | PIE3                 | —                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CCP4IE           | CCP3IE     | TMR6IE       | _           | TMR4IE  | _      | 00 0-0-              | 00 0-0-                         |  |

| 094h                | PIE4 <sup>(2)</sup>  | —                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                | _          | _            | _           | BCL2IE  | SSP2IE | 00                   | 00                              |  |

| 095h                | OPTION_REG           | WPUEN                            | INTEDG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMR0CS           | TMR0SE     | PSA          |             | PS<2:0> |        | 1111 1111            | 1111 1111                       |  |

| 096h                | PCON                 | STKOVF                           | STKUNF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                | _          | RMCLR        | RI          | POR     | BOR    | 00 11qq              | qq qquu                         |  |

| 097h                | WDTCON               | _                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | V          | VDTPS<4:0>   |             |         | SWDTEN | 01 0110              | 01 0110                         |  |

| 098h                | OSCTUNE              | —                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |            | TUN<         | 5:0>        |         |        | 00 0000              | 00 0000                         |  |

| 099h                | OSCCON               | SPLLEN                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IRCF<            | <3:0>      |              | —           | SCS     | <1:0>  | 0011 1-00            | 0011 1-00                       |  |

| 09Ah                | OSCSTAT              | T1OSCR                           | PLLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OSTS             | HFIOFR     | HFIOFL       | MFIOFR      | LFIOFR  | HFIOFS | 10q0 0q00            | वववव वव०व                       |  |

| 09Bh                | ADRESL               | A/D Result R                     | egister Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | •          |              | •           | •       | •      | xxxx xxxx            | uuuu uuuu                       |  |

| 09Ch                | ADRESH               | A/D Result R                     | egister High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |            |              |             |         |        | xxxx xxxx            | uuuu uuuu                       |  |

| 09Dh                | ADCON0               | —                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | CHS<4:0>   |              |             | GO/DONE | ADON   | -000 0000            | -000 0000                       |  |

| 09Eh                | ADCON1               | ADFM                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADCS<2:0>        |            | —            | ADNREF      | ADPRE   | F<1:0> | 0000 -000            | 0000 -000                       |  |

|                     |                      |                                  | ADFM         ADCS<2:0>         —         ADNREF         ADPREF<1:0>         0000 -000         000           nimplemented         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —          —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         _         _         < |                  |            |              |             |         |        |                      |                                 |  |

#### TABLE 3-8 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

PIC16(L)F1829 only.

PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

#

#### FIGURE 5-8: TWO-SPEED START-UP

## 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>u = Bit is unchanged x = Bit is unknown<br>-n/n = Value at POR and BOR/Value at all other Resets<br>'1' = Bit is set '0' = Bit is cleared<br>bit 7 RXDTSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RC2<br>1 = SD01 function is on RC2<br>1 = SD01 function is on RC2<br>1 = SD01 function is on RC4<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD01 function is always on RC7.<br>bit 5 S\$15EL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD01 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD3 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD3 function is on RA4<br>1 = T1G function is on RA4<br>1 = T1G function is on RA4<br>1 = TXCK function is on RA0<br>For 20 Pin Devices (PIC16(L)F1829);<br>0 = TXCK function is on RA0<br>For 20 Pin Devices (PIC16(L)F1829);<br>0 = TXCK function is on RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0/0          | R/W-0/0                                                                                                                      | R/W-0/0                                                                                                                          | U-0                                                      | R/W-0/0      | R/W-0/0          | U-0              | U-0          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|------------------|------------------|--------------|

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets<br>'1' = Bit is set '0' = Bit is cleared<br>bit 7 RXDTSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RB5<br>1 = RX/DT function is on RB5<br>1 = RX/DT function is on RC5<br>bit 6 SD01SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>0 = SD01 function is on RC2<br>1 = SD01 function is on RC2<br>1 = SD01 function is on RC2<br>1 = SD01 function is on RC4<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD01 function is always on RC7.<br>bit 5 SISEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD01 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SD1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is on RA4<br>1 = T1G function is on RA4<br>1 = T1G function is on RA4<br>1 = TXCK function is on RA4<br>1 = TXCK function is on RA0<br>For 20 Pin Devices (PIC16(L)F1829);<br>0 = TX/CK function is on RA0<br>For 20 Pin Devices (PIC16(L)F1829);<br>0 = TX/CK function is on RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RXDTSEL          | SDO1SEL                                                                                                                      | SS1SEL                                                                                                                           | _                                                        | T1GSEL       | TXCKSEL          |                  | _            |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>u = Bit is unchanged x = Bit is unknown<br>'1' = Bit is set '0' = Bit is cleared<br>bit 7 RXDTSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RC5<br>1 = RX/DT function is on RC5<br>bit 6 SDO1SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>0 = RX/DT function is on RC5<br>bit 6 SDO1SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>0 = SDO1 function is on RC2<br>1 = SDO1 function is on RC2<br>1 = SDO1 function is on RC3<br>SDO1 function is on RC3<br>SDO1 function is on RC3<br>1 = SS1 function is on RC3<br>1 = SS1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 3 TICSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 5 TICSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 2 TXCKSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = TX/CK function is on RA3<br>bit 2 TXCKSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = TX/CK function is on RA4<br>1 = T16 function is on RA4<br>1 = T16 function is on RA4<br>1 = T16 function is on RA4<br>1 = TX/CK function is on RA4                                                                                                                                                                                                                                                                                                                               | bit 7            |                                                                                                                              | 1 1                                                                                                                              |                                                          |              | 1                |                  | bit (        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>u = Bit is unchanged x = Bit is unknown<br>'1' = Bit is set '0' = Bit is cleared<br>bit 7 RXDTSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RC5<br>1 = RX/DT function is on RC5<br>bit 6 SDO1SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>0 = RX/DT function is on RC5<br>bit 6 SDO1SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>0 = SDO1 function is on RC2<br>1 = SDO1 function is on RC2<br>1 = SDO1 function is on RC3<br>SDO1 function is on RC3<br>SDO1 function is on RC3<br>1 = SS1 function is on RC3<br>1 = SS1 function is on RA3<br>For 20 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 3 TICSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 5 TICSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is always on RC6.<br>bit 4 Unimplemented: Read as '0'<br>bit 2 TXCKSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = TX/CK function is on RA3<br>bit 2 TXCKSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = TX/CK function is on RA4<br>1 = T16 function is on RA4<br>1 = T16 function is on RA4<br>1 = T16 function is on RA4<br>1 = TX/CK function is on RA4                                                                                                                                                                                                                                                                                                                               |                  |                                                                                                                              |                                                                                                                                  |                                                          |              |                  |                  |              |

| u = Bit is unchanged x = Bit is unknown<br>'1' = Bit is set '0' = Bit is cleared<br>bit 7 <b>RXDTSEL:</b> Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RA5<br>1 = RX/DT function is on RB5<br>1 = RX/DT function is on RC5<br>bit 6 <b>SDO1SEL:</b> Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = SDO1 function is on RC2<br>1 = SDO1 function is on RC3<br>bit 5 <b>SS1SEL:</b> Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = SS01 function is on RC3<br>1 = SS1 function is on RC3<br>1 = TIG Perios (PIC16(L)F1829);<br>Bit is read-only, '0'<br>SS1 function is on RC3<br>1 = TIG function is on RC4<br>1 = TIG function is on RA4<br>1 = TIG function is on RA3<br>bit 2 <b>TXCKSEL:</b> Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825);<br>0 = TX/CK function is on RC4<br>1 = TX/CK function is on RA4<br>1 = TIG function is on RA4<br>1 = TIG function is on RA4<br>1 = TIG function is on RA4<br>1 = TX/CK function is on RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Legend:          |                                                                                                                              |                                                                                                                                  |                                                          |              |                  |                  |              |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R = Readable     | bit                                                                                                                          | W = Writable I                                                                                                                   | oit                                                      | U = Unimple  | mented bit, read | as '0'           |              |

| bit 7 RXDTSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825):<br>0 = RX/DT function is on RC5<br>1 = RX/DT function is on RA1<br>For 20 Pin Devices (PIC16(L)F1829):<br>0 = RX/DT function is on RB5<br>1 = RX/DT function is on RC5<br>bit 6 SD01SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825):<br>0 = SD01 function is on RC2<br>1 = SD01 function is on RC4<br>For 20 Pin Devices (PIC16(L)F1829):<br>Bit is read-only, '0'<br>SD01 function is an RA4<br>For 20 Pin Devices (PIC16(L)F1825):<br>$0 = \overline{SS1}$ function is on RC7.<br>bit 5 SS1SEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825):<br>$0 = \overline{SS1}$ function is on RC3<br>$1 = \overline{SS1}$ function is on RC3<br>$1 = \overline{SS1}$ function is on RC6.<br>bit 4 Unimplemented: Read as '0'<br>Bit is read-only, '0'<br>SS1 function is on RA4<br>1 = T1G function is on RA4<br>1 = T1G function is on RA3<br>bit 2 TXCKSEL: Pin Selection bit<br>For 14 Pin Devices (PIC16(L)F1825):<br>0 = TX/CK function is on RA4<br>1 = T1G function is on RA4<br>1 = TX/CK function is on RA3<br>For 20 Pin Devices (PIC16(L)F1825):<br>0 = TX/CK function is on RA4<br>1 = TX/CK function is on RA4 | u = Bit is unch  | nanged                                                                                                                       | x = Bit is unkn                                                                                                                  | own                                                      | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |