# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT, IBT LIN/J2602                          |

| Number of I/O              | 12                                                                            |

| Program Memory Size        | 14KB (8K x 14)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 256 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

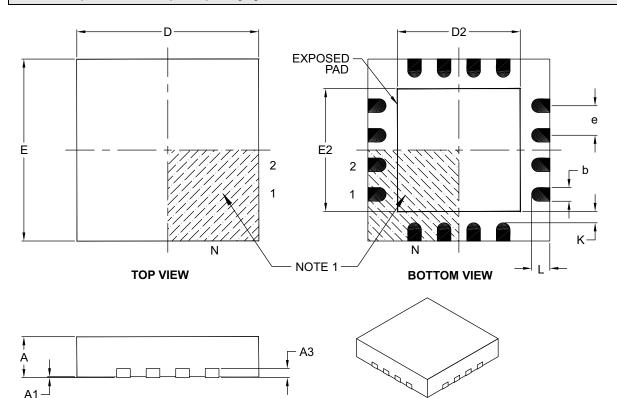

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829lint-e-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1825/9

#### 8.6.8 PIR3 REGISTER

The PIR3 register contains the interrupt flag bits, as shown in Register 8-8.

1 = Interrupt is pending0 = Interrupt is not pending

1 = Interrupt is pending0 = Interrupt is not pending

1 = Interrupt is pending0 = Interrupt is not pending

Unimplemented: Read as '0'

Unimplemented: Read as '0'

TMR6IF: TMR6 to PR6 Match Interrupt Flag bit

TMR4IF: TMR4 to PR4 Match Interrupt Flag bit

Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-8: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|---------|---------|---------|-----|---------|-------|

| —     |     | CCP4IF  | CCP3IF  | TMR6IF  | —   | TMR4IF  | —     |

| bit 7 |     |         |         |         |     |         | bit 0 |

| Legend:              |             |                        |                                                       |

|----------------------|-------------|------------------------|-------------------------------------------------------|

| R = Readable bit     |             | W = Writable bit       | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged |             | x = Bit is unknown     | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is s       | set         | '0' = Bit is cleared   |                                                       |

|                      |             |                        |                                                       |

| bit 7-6              | Unimplem    | nented: Read as '0'    |                                                       |

| bit 5                | CCP4IF: C   | CP4 Interrupt Flag bit |                                                       |

|                      |             | pt is pending          |                                                       |

|                      | 0 = Interru | pt is not pending      |                                                       |

| bit 4                | CCP3IF: C   | CP3 Interrupt Flag bit |                                                       |

bit 3

bit 2

bit 1

bit 0

### 8.6.9 PIR4 REGISTER<sup>(1)</sup>

The PIR4 register contains the interrupt flag bits, as shown in Register 8-9.

| Note 1:               | The PIR4 register is available only on the |  |  |  |  |  |  |

|-----------------------|--------------------------------------------|--|--|--|--|--|--|

| PIC16(L)F1829 device. |                                            |  |  |  |  |  |  |

2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# **REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | —   | _   | —   | —   | BCL2IF     | SSP2IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Bit is set by hardware                           |

| Unimplemented: Read as '0'                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCL2IF: MSSP2 Bus Collision Interrupt Flag bit                                                                                                                                |

| 1 = A Bus Collision was detected (must be cleared in software)                                                                                                                |

| 0 = No Bus collision was detected                                                                                                                                             |

| SSP2IF: Master Synchronous Serial Port 2 (MSSP2) Interrupt Flag bit                                                                                                           |

| <ul> <li>1 = The Transmission/Reception/Bus Condition is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive/Bus Condition in progress</li> </ul> |

|                                                                                                                                                                               |

**Note 1:** This register is only available on PIC16(L)F1829.

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name                | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|---------------------|---------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON              | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 87                  |

| OPTION_REG          | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 176                 |

| PIE1                | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE  | TMR1IE | 88                  |

| PIE2                | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE |        |         | CCP2IE | 89                  |

| PIE3                | —       |        | CCP4IE | CCP3IE | TMR6IE | -      | TMR4IE  | _      | 90                  |

| PIE4 <sup>(1)</sup> | —       | -      | -      | -      | _      | _      | BCL2IE  | SSP2IE | 91                  |

| PIR1                | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF  | TMR1IF | 92                  |

| PIR2                | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | _      | _       | CCP2IF | 93                  |

| PIR3                | _       | —      | CCP4IF | CCP3IF | TMR6IF | _      | TMR4IF  | _      | 94                  |

| PIR4 <sup>(1)</sup> | _       | _      | _      | _      | _      | _      | BCL2IF  | SSP2IF | 95                  |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by interrupts.

**Note 1:** PIC16(L)F1829 only.

| Name       | Bit 7   | Bit 6                  | Bit 5                  | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|------------------------|------------------------|-----------------------|---------|---------|---------|---------|---------------------|

| ANSELA     | _       | —                      | -                      | ANSA4                 | _       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| APFCON0    | RXDTSEL | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup>  | _                     | T1GSEL  | TXCKSEL | _       | _       | 118                 |

| APFCON1    | —       | —                      | SDO2SEL <sup>(1)</sup> | SS2SEL <sup>(1)</sup> | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL | 119                 |

| INLVLA     | _       | —                      | INLVLA5                | INLVLA4               | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| LATA       | _       | —                      | LATA5                  | LATA4                 | _       | LATA2   | LATA1   | LATA0   | 123                 |

| OPTION_REG | WPUEN   | INTEDG                 | TMR0CS                 | TMR0SE                | PSA     | PS<2:0> |         |         | 176                 |

| PORTA      | _       | —                      | RA5                    | RA4                   | RA3     | RA2     | RA1     | RA0     | 122                 |

| TRISA      | _       | —                      | TRISA5                 | TRISA4                | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| WPUA       | —       | —                      | WPUA5                  | WPUA4                 | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 124                 |

x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA. PIC16(L)F1829 only. PIC16(L)F1825 only. Legend:

Note 1:

2:

#### **TABLE 12-4:** SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|---------|---------|---------------------|

| 0015104 | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |         | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | FOSC<2:0>  |         | 48      |                     |

Legend: - Unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR Buffer2

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- · Capacitive Sensing module (CPS)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

# EQUATION 17-1: DAC OUTPUT VOLTAGE

# <u>**IF DACEN = 1**</u> $VOUT = \left( (VSOURCE - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE -$

IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE - = VSS

# 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "**Electrical Specifications**".

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

# 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17.5 shows an example buffering technique.

| SRCLK | Divider | Fosc = 32 MHz | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|-------|---------|---------------|---------------|---------------|--------------|--------------|

| 111   | 512     | 62.5 kHz      | 39.0 kHz      | 31.3 kHz      | 7.81 kHz     | 1.95 kHz     |

| 110   | 256     | 125 kHz       | 78.1 kHz      | 62.5 kHz      | 15.6 kHz     | 3.90 kHz     |

| 101   | 128     | 250 kHz       | 156 kHz       | 125 kHz       | 31.25 kHz    | 7.81 kHz     |

| 100   | 64      | 500 kHz       | 313 kHz       | 250 kHz       | 62.5 kHz     | 15.6 kHz     |

| 011   | 32      | 1 MHz         | 625 kHz       | 500 kHz       | 125 kHz      | 31.3 kHz     |

| 010   | 16      | 2 MHz         | 1.25 MHz      | 1 MHz         | 250 kHz      | 62.5 kHz     |

| 001   | 8       | 4 MHz         | 2.5 MHz       | 2 MHz         | 500 kHz      | 125 kHz      |

| 000   | 4       | 8 MHz         | 5 MHz         | 4 MHz         | 1 MHz        | 250 kHz      |

# TABLE 18-1: SRCLK FREQUENCY TABLE

# REGISTER 18-1: SRCON0: SR LATCH CONTROL 0 REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/S-0/0 | R/S-0/0 |

|---------|---------|------------|---------|---------|---------|---------|---------|

| SRLEN   |         | SRCLK<2:0> |         | SRQEN   | SRNQEN  | SRPS    | SRPR    |

| bit 7   |         |            |         |         |         |         | bit 0   |

| t W = Writable bit<br>nged x = Bit is unknown<br>'0' = Bit is cleared<br>SRLEN: SR Latch Enable bit<br>1 = SR latch is enabled<br>0 = SR latch is disabled<br>SRCLK<2:0>: SR Latch Clock Divider b<br>000 = Generates a 1 Fosc wide pulse e<br>010 = Generates a 1 Fosc wide pulse e<br>011 = Generates a 1 Fosc wide pulse e<br>100 = Generates a 1 Fosc wide pulse e<br>101 = Generates a 1 Fosc wide pulse e<br>102 = Generates a 1 Fosc wide pulse e<br>103 = Generates a 1 Fosc wide pulse e<br>104 = Generates a 1 Fosc wide pulse e<br>105 = Generates a 1 Fosc wide pulse e<br>106 = Generates a 1 Fosc wide pulse e<br>107 = Generates a 1 Fosc wide pulse e<br>108 = Generates a 1 Fosc wide pulse e<br>109 = Generates a 1 Fosc wide pulse e<br>100 = Generates a 1 Fosc wid | every 4th Fosc cycle clock<br>every 8th Fosc cycle clock<br>every 16th Fosc cycle clock<br>every 32nd Fosc cycle clock<br>every 64th Fosc cycle clock<br>every 128th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| '0' = Bit is cleared<br>SRLEN: SR Latch Enable bit<br>1 = SR latch is enabled<br>0 = SR latch is disabled<br>SRCLK<2:0>: SR Latch Clock Divider b<br>000 = Generates a 1 Fosc wide pulse e<br>010 = Generates a 1 Fosc wide pulse e<br>011 = Generates a 1 Fosc wide pulse e<br>100 = Generates a 1 Fosc wide pulse e<br>101 = Generates a 1 Fosc wide pulse e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S = Bit is set only<br>its<br>very 4th Fosc cycle clock<br>very 8th Fosc cycle clock<br>very 16th Fosc cycle clock<br>very 32nd Fosc cycle clock<br>very 64th Fosc cycle clock<br>very 128th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>SRLEN: SR Latch Enable bit</li> <li>1 = SR latch is enabled</li> <li>0 = SR latch is disabled</li> <li>SRCLK&lt;2:0&gt;: SR Latch Clock Divider b</li> <li>000 = Generates a 1 Fosc wide pulse e</li> <li>001 = Generates a 1 Fosc wide pulse e</li> <li>010 = Generates a 1 Fosc wide pulse e</li> <li>011 = Generates a 1 Fosc wide pulse e</li> <li>100 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | oits<br>every 4th Fosc cycle clock<br>every 8th Fosc cycle clock<br>every 16th Fosc cycle clock<br>every 32nd Fosc cycle clock<br>every 64th Fosc cycle clock<br>every 128th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>1 = SR latch is enabled</li> <li>0 = SR latch is disabled</li> <li>SRCLK&lt;2:0&gt;: SR Latch Clock Divider b</li> <li>000 = Generates a 1 Fosc wide pulse e</li> <li>001 = Generates a 1 Fosc wide pulse e</li> <li>010 = Generates a 1 Fosc wide pulse e</li> <li>011 = Generates a 1 Fosc wide pulse e</li> <li>100 = Generates a 1 Fosc wide pulse e</li> <li>100 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> <li>101 = Generates a 1 Fosc wide pulse e</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | every 4th Fosc cycle clock<br>every 8th Fosc cycle clock<br>every 16th Fosc cycle clock<br>every 32nd Fosc cycle clock<br>every 64th Fosc cycle clock<br>every 128th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                                                 |

| 000 = Generates a 1 Fosc wide pulse e<br>001 = Generates a 1 Fosc wide pulse e<br>010 = Generates a 1 Fosc wide pulse e<br>011 = Generates a 1 Fosc wide pulse e<br>100 = Generates a 1 Fosc wide pulse e<br>101 = Generates a 1 Fosc wide pulse e<br>110 = Generates a 1 Fosc wide pulse e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | every 4th Fosc cycle clock<br>every 8th Fosc cycle clock<br>every 16th Fosc cycle clock<br>every 32nd Fosc cycle clock<br>every 64th Fosc cycle clock<br>every 128th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                                                 |

| TTT - Oenerates a 11 OSC wide puise e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | very 512th Fosc cycle clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SRQEN: SR Latch Q Output Enable bit<br><u>If SRLEN = 1</u> :<br>1 = Q is present on the SRQ pin<br>0 = External Q output is disabled<br><u>If SRLEN = 0</u> :<br>SR latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>SRNQEN:</b> SR Latch $\overline{Q}$ Output Enable b<br><u>If SRLEN = 1</u> :<br>1 = $\overline{Q}$ is present on the SRnQ pin<br>0 = External $\overline{Q}$ output is disabled<br><u>If SRLEN = 0</u> :<br>SR latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>SRPS: Pulse Set Input of the SR Latch</li> <li>1 = Pulse set input for 1 Q-clock period</li> <li>0 = No effect on set input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>SRPR: Pulse Reset Input of the SR Late</li> <li>1 = Pulse Reset input for 1 Q-clock per</li> <li>0 = No effect on Reset input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 = External Q output is disabled<br>f <u>SRLEN = 0</u> :<br>SR latch is disabled<br><b>SRNQEN:</b> SR Latch $\overline{Q}$ Output Enable b<br>f <u>SRLEN = 1</u> :<br>1 = $\overline{Q}$ is present on the SRnQ pin<br>0 = External $\overline{Q}$ output is disabled<br>f <u>SRLEN = 0</u> :<br>SR latch is disabled<br><b>SRPS:</b> Pulse Set Input of the SR Latch<br>1 = Pulse set input for 1 Q-clock period<br>0 = No effect on set input.<br><b>SRPR:</b> Pulse Reset Input of the SR Latch<br>1 = Pulse Reset Input of the SR Latch<br>1 = Pulse Reset Input of the SR Latch |

# 21.12 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), shown in Register 21-2, is used to control Timer1 Gate.

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                           | R/W-0/u                                                                                                                                                                                                                        | R/W-0/u                         | R/W/HC-0/u                      | R-x/x            | R/W-0/u        | R/W-0/u      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------------------|----------------|--------------|

| TMR1GE           | T1GPOL                                                                                                                                                                                                                            | T1GTM                                                                                                                                                                                                                          | T1GSPM                          | T1GGO/<br>DONE                  | T1GVAL           | T1GS           | S<1:0>       |

| bit 7            |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                |                                 | •                               |                  |                | bit          |

| Legend:          |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                |                                 |                                 |                  |                |              |

| R = Readable     | e bit                                                                                                                                                                                                                             | W = Writable                                                                                                                                                                                                                   | bit                             | U = Unimplen                    | nented bit, read | l as '0'       |              |

| u = Bit is uncl  | hanged                                                                                                                                                                                                                            | x = Bit is unki                                                                                                                                                                                                                | nown                            | -n/n = Value a                  | It POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                   | '0' = Bit is cle                                                                                                                                                                                                               | ared                            | HC = Bit is cle                 | eared by hardw   | are            |              |

| bit 7            | If TMR1ON =<br>This bit is ign<br>If TMR1ON =<br>1 = Timer1 c                                                                                                                                                                     | ored<br><u>1</u> :                                                                                                                                                                                                             | rolled by the T                 | ïmer1 gate func<br>ate function | tion             |                |              |

| bit 6            | <b>T1GPOL:</b> Timer1 Gate Polarity bit<br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                     |                                                                                                                                                                                                                                |                                 |                                 |                  |                |              |

| bit 5            | 1 = Timer1 (<br>0 = Timer1 (                                                                                                                                                                                                      | er1 Gate Toggle<br>Gate Toggle mo<br>Gate Toggle mo<br>flip-flop toggles                                                                                                                                                       | de is enabled<br>de is disabled | and toggle flip-<br>g edge.     | flop is cleared  |                |              |

| bit 4            | 1 = Timer1 g                                                                                                                                                                                                                      | <b>T1GSPM:</b> Timer1 Gate Single-Pulse Mode bit<br>1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate<br>0 = Timer1 gate Single-Pulse mode is disabled                                               |                                 |                                 |                  |                |              |

| bit 3            | <b>T1GGO/DON</b><br>1 = Timer1 g                                                                                                                                                                                                  | <b>TIGGO/DONE:</b> Timer1 Gate Single-Pulse Acquisition Status bit<br>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge<br>0 = Timer1 gate single-pulse acquisition has completed or has not been started |                                 |                                 |                  |                |              |

| bit 2            | <b>T1GVAL:</b> Timer1 Gate Current State bit<br>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.<br>Unaffected by Timer1 Gate Enable (TMR1GE).                                               |                                                                                                                                                                                                                                |                                 |                                 |                  |                |              |

| bit 1-0          | T1GSS<1:0>: Timer1 Gate Enable (TMRTGE).<br>00 = Timer1 Gate pin<br>01 = Timer0 overflow output<br>10 = Comparator 1 optionally synchronized output (sync_C1OUT)<br>11 = Comparator 2 optionally synchronized output (sync_C2OUT) |                                                                                                                                                                                                                                |                                 |                                 |                  |                |              |

#### REGISTER 21-2: T1GCON: TIMER1 GATE CONTROL REGISTER

# 24.5 CCP Control Registers

# REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-00           | R/W-0/0                                                                                                                           | R/W-0/0                                                                                                                                                                           | R/W-0/0          | R/W-0/0                               | R/W-0/0           | R/W-0/0           | R/W-0/0    |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|-------------------|-------------------|------------|--|--|

| PxM              | <1:0> <sup>(1)</sup>                                                                                                              | DCxB                                                                                                                                                                              | 8<1:0>           |                                       | CCPxN             | Л<3:0>            |            |  |  |

| bit 7            |                                                                                                                                   |                                                                                                                                                                                   |                  |                                       |                   |                   | bit C      |  |  |

| Legend:          |                                                                                                                                   |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

| R = Readable     | bit                                                                                                                               | W = Writable bi                                                                                                                                                                   | t                | U = Unimpleme                         | nted bit, read as | · 'O'             |            |  |  |

| u = Bit is uncha | anged                                                                                                                             | x = Bit is unknown                                                                                                                                                                |                  | -n/n = Value at                       | POR and BOR/V     | alue at all other | Reset      |  |  |

| '1' = Bit is set |                                                                                                                                   | '0' = Bit is clear                                                                                                                                                                | ed               |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   |                                                                                                                                                                                   |                  | (1)                                   |                   |                   |            |  |  |

| bit 7-6          | Capture mode                                                                                                                      | hanced PWM Ou                                                                                                                                                                     | tput Configurat  | tion dits"                            |                   |                   |            |  |  |

|                  | Unused                                                                                                                            | <u>-</u>                                                                                                                                                                          |                  |                                       |                   |                   |            |  |  |

|                  | Compare mod                                                                                                                       | <u>e:</u>                                                                                                                                                                         |                  |                                       |                   |                   |            |  |  |

|                  | Unused                                                                                                                            |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   | > = 00, 01, 10:                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   |                                                                                                                                                                                   | Compare input;   | PxB, PxC, PxD a                       | ssigned as port p | bins              |            |  |  |

|                  | <u>If CCPxM&lt;3:2</u><br>0.0 = Single ou                                                                                         |                                                                                                                                                                                   | ted PxB PxC      | PxD assigned as                       | port pins         |                   |            |  |  |

|                  | 01 = Full-Bridg                                                                                                                   | <ul> <li>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins</li> <li>01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive</li> </ul> |                  |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   |                                                                                                                                                                                   |                  | rith dead-band con                    |                   | ssigned as port p | ins        |  |  |

| bit 5-4          | 11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br>DCxB<1:0>: PWM Duty Cycle Least Significant bits |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

| 511 5-4          | Capture mode                                                                                                                      |                                                                                                                                                                                   | -cast Significal | 11 0113                               |                   |                   |            |  |  |

|                  | Unused                                                                                                                            |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  | Compare mode:                                                                                                                     |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  | Unused                                                                                                                            |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  | <u>PWM mode:</u>                                                                                                                  | the two I She of t                                                                                                                                                                | bo DWM duty      | wele. The eight M                     | Sha ara faund in  | CCDByl            |            |  |  |

| bit 3-0          |                                                                                                                                   |                                                                                                                                                                                   | -                | cycle. The eight M                    | SDS are lound in  | CCFRXL.           |            |  |  |

| bit 5-0          |                                                                                                                                   | CCPxM<3:0>: ECCPx Mode Select bits                                                                                                                                                |                  |                                       |                   |                   |            |  |  |

|                  | 0000 = Capture/Compare/PWM off (resets ECCPx module)<br>0001 = Reserved                                                           |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  | •                                                                                                                                 | 010 = Compare mode: toggle output on match                                                                                                                                        |                  |                                       |                   |                   |            |  |  |

|                  | 0011 = Reser                                                                                                                      | ved                                                                                                                                                                               |                  |                                       |                   |                   |            |  |  |

|                  | 0100 = Captu                                                                                                                      | re mode: every fa                                                                                                                                                                 | illing edge      |                                       |                   |                   |            |  |  |

|                  | 0101 = Captu                                                                                                                      | re mode: every ris                                                                                                                                                                | sing edge        |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   | 0110 = Capture mode: every 4th rising edge<br>0111 = Capture mode: every 16th rising edge                                                                                         |                  |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   | re mode: every 10                                                                                                                                                                 | oth rising eage  |                                       |                   |                   |            |  |  |

|                  | 1000 = Comp                                                                                                                       | are mode: initializ                                                                                                                                                               | e ECCPx pin k    | ow; set output on o                   | compare match (   | set CCPxIF)       |            |  |  |

|                  | •                                                                                                                                 |                                                                                                                                                                                   | •                | igh; clear output c                   | •                 | ,                 |            |  |  |

|                  |                                                                                                                                   | 0                                                                                                                                                                                 |                  | errupt only; ECCP<br>(ECCPx resets Ti | •                 |                   | convorsion |  |  |

|                  |                                                                                                                                   | module is enable                                                                                                                                                                  |                  |                                       |                   |                   | COnversion |  |  |

|                  | CCP Modules                                                                                                                       | only:                                                                                                                                                                             |                  |                                       |                   |                   |            |  |  |

|                  | 11xx = PWM                                                                                                                        |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  | ECCP Module                                                                                                                       |                                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

|                  |                                                                                                                                   | -                                                                                                                                                                                 | active-high; P>  | B, PxD active-hig                     | n                 |                   |            |  |  |

|                  |                                                                                                                                   |                                                                                                                                                                                   | 0                | B, PxD active-low                     |                   |                   |            |  |  |

|                  |                                                                                                                                   | mode: PxA, PxC<br>mode: PxA, PxC                                                                                                                                                  |                  | 3, PxD active-high                    |                   |                   |            |  |  |

|                  |                                                                                                                                   | moue. I XA, FXC                                                                                                                                                                   |                  |                                       |                   |                   |            |  |  |

Note 1: These bits are not implemented on CCP<5:4>.

### 25.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCLx pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDAx line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDAx line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCLx on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 25.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSPx Slave mode operates in one of four modes selected in the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart or Stop condition.

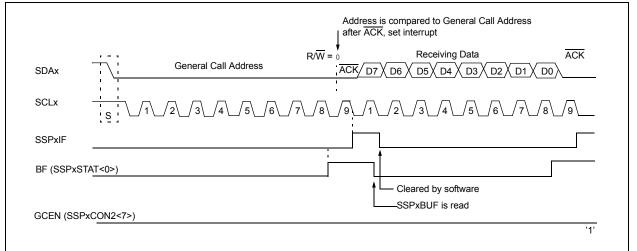

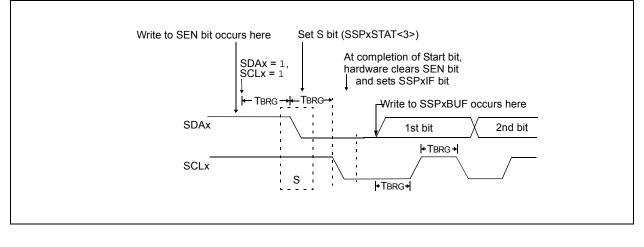

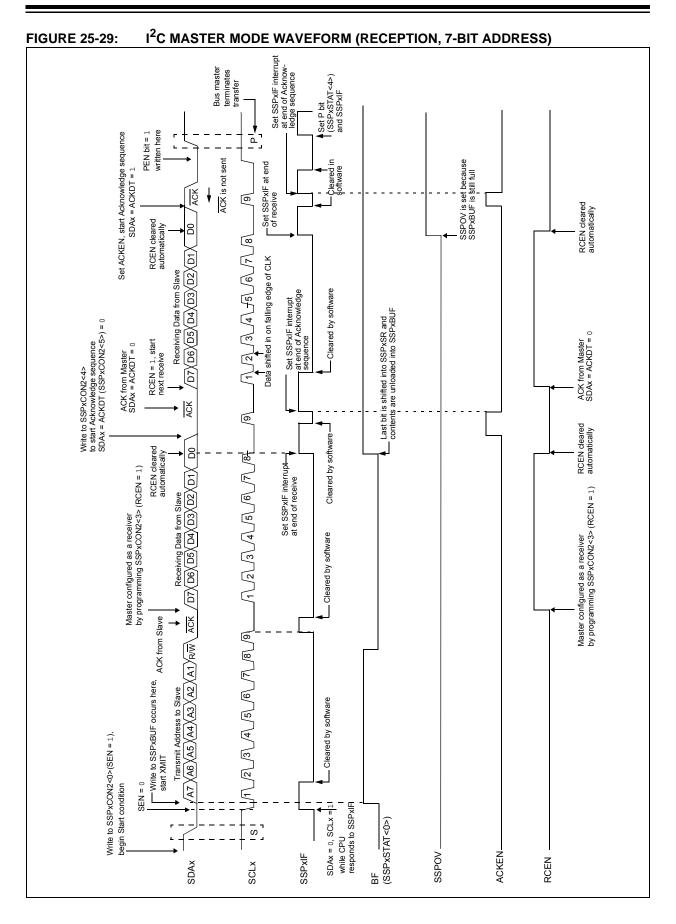

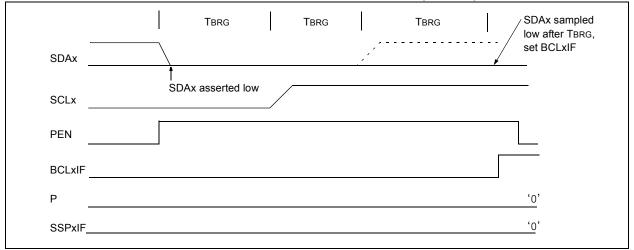

#### 25.5.1 SLAVE MODE ADDRESSES