Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829t-i-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0  | Device Overview                                                           |  |

|------|---------------------------------------------------------------------------|--|

| 2.0  | Enhanced Mid-range CPU                                                    |  |

| 3.0  | Memory Organization                                                       |  |

| 4.0  | Device Configuration                                                      |  |

| 5.0  | Oscillator Module (With Fail-Safe Clock Monitor)                          |  |

| 6.0  | Reference Clock Module                                                    |  |

| 7.0  | Resets                                                                    |  |

| 8.0  | Interrupts                                                                |  |

| 9.0  | Power-Down Mode (Sleep)                                                   |  |

| 10.0 |                                                                           |  |

| 11.0 |                                                                           |  |

| 12.0 |                                                                           |  |

| 13.0 |                                                                           |  |

| 14.0 |                                                                           |  |

| 15.0 |                                                                           |  |

| 16.0 |                                                                           |  |

| 17.0 | - 3                                                                       |  |

|      | SR Latch                                                                  |  |

|      | Comparator Module                                                         |  |

|      | Timer0 Module                                                             |  |

|      | Timer1 Module with Gate Control                                           |  |

|      | Timer2/4/6 Modules                                                        |  |

| 23.0 |                                                                           |  |

| 24.0 |                                                                           |  |

| 25.0 |                                                                           |  |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |  |

|      | Capacitive Sensing (CPS) Module                                           |  |

|      | In-Circuit Serial Programming™ (ICSP™)                                    |  |

|      | Instruction Set Summary                                                   |  |

| 30.0 |                                                                           |  |

| 31.0 |                                                                           |  |

| 32.0 |                                                                           |  |

|      | Packaging Information                                                     |  |

|      | endix A: Data Sheet Revision History                                      |  |

|      | endix B: Migrating From Other PIC® Devices                                |  |

|      | Microchip Web Site                                                        |  |

|      | omer Change Notification Service                                          |  |

|      | omer Support                                                              |  |

| Prod | uct Identification System                                                 |  |

| Address             | Name                  | Bit 7                          | Bit 6                                           | Bit 5            | Bit 4           | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|-----------------------|--------------------------------|-------------------------------------------------|------------------|-----------------|---------------|--------------|---------|-----------|----------------------|---------------------------------|

| Bank 3              |                       |                                |                                                 |                  |                 |               |              |         |           |                      |                                 |

| 180h <sup>(1)</sup> | INDF0                 | Addressing tl<br>(not a physic |                                                 | es contents of   | FSR0H/FSR0      | L to address  | data memory  | /       |           | XXXX XXXX            | XXXX XXXX                       |

| 181h <sup>(1)</sup> | INDF1                 | Addressing tl<br>(not a physic |                                                 | es contents of   | FSR1H/FSR1      | L to address  | data memory  | /       |           | XXXX XXXX            | XXXX XXXX                       |

| 182h <sup>(1)</sup> | PCL                   | Program Cou                    | inter (PC) Lea                                  | st Significant E | Byte            |               |              |         |           | 0000 0000            | 0000 0000                       |

| 183h <sup>(1)</sup> | STATUS                | _                              | <u>TO</u> <u>PD</u> <u>Z</u> <u>DC</u> <u>C</u> |                  |                 |               |              | С       | 1 1000    | q quuu               |                                 |

| 184h <sup>(1)</sup> | FSR0L                 | Indirect Data                  | Memory Addr                                     | ess 0 Low Poir   | nter            |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 185h <sup>(1)</sup> | FSR0H                 | Indirect Data                  | Memory Addr                                     | ess 0 High Poi   | nter            |               |              |         |           | 0000 0000            | 0000 0000                       |

| 186h <sup>(1)</sup> | FSR1L                 | Indirect Data                  | Memory Addr                                     | ess 1 Low Poir   | nter            |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 187h <sup>(1)</sup> | FSR1H                 | Indirect Data                  | Memory Addr                                     | ess 1 High Poi   | nter            |               |              |         |           | 0000 0000            | 0000 0000                       |

| 188h <sup>(1)</sup> | BSR                   | _                              | _                                               | —                |                 |               | BSR<4:0>     |         |           | 0 0000               | 0 0000                          |

| 189h <sup>(1)</sup> | WREG                  | Working Reg                    | /orking Register                                |                  |                 |               |              |         | 0000 0000 | uuuu uuuu            |                                 |

| 18Ah <sup>(1)</sup> | PCLATH                | —                              | Write Buffer f                                  | or the upper 7   | bits of the Pro | ogram Counte  | r            |         |           | -000 0000            | -000 0000                       |

| 18Bh <sup>(1)</sup> | INTCON                | GIE                            | PEIE                                            | TMR0IE           | INTE            | IOCIE         | TMR0IF       | INTF    | IOCIF     | 0000 0000            | 0000 0000                       |

| 18Ch                | ANSELA                | —                              | —                                               | _                | ANSA4           | —             | ANSA2        | ANSA1   | ANSA0     | 1 -111               | 1 -111                          |

| 18Dh                | ANSELB <sup>(2)</sup> | _                              | _                                               | ANSB5            | ANSB4           | _             | _            | _       |           | 11                   | 11                              |

| 18Eh                | ANSELC                | ANSC7 <sup>(2)</sup>           | ANSC6 <sup>(2)</sup>                            | -                | —               | ANSC3         | ANSC2        | ANSC1   | ANSC0     | 11 1111              | 11 1111                         |

| 18Fh                | —                     | Unimplement                    | ted                                             |                  |                 | •             |              | •       |           | _                    | _                               |

| 190h                | —                     | Unimplement                    | ted                                             |                  |                 |               |              |         |           | _                    | _                               |

| 191h                | EEADRL                | EEPROM / P                     | rogram Memo                                     | ry Address Re    | gister Low By   | te            |              |         |           | 0000 0000            | 0000 0000                       |

| 192h                | EEADRH                | (4)                            | EEPROM / P                                      | rogram Memo      | ry Address Re   | gister High B | yte          |         |           | 1000 0000            | 1000 0000                       |

| 193h                | EEDATL                | EEPROM / P                     | rogram Memo                                     | ry Read Data I   | Register Low    | Byte          |              |         |           | xxxx xxxx            | uuuu uuuu                       |

| 194h                | EEDATH                | _                              | _                                               | EEPROM / Pr      | rogram Memo     | ry Read Data  | Register Hig | gh Byte |           | xx xxxx              | uu uuuu                         |

| 195h                | EECON1                | EEPGD                          | CFGS                                            | LWLO             | FREE            | WRERR         | WREN         | WR      | RD        | 0000 x000            | 0000 q000                       |

| 196h                | EECON2                | EEPROM co                      | ntrol register 2                                |                  |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 197h                | —                     | Unimplement                    | ted                                             |                  |                 |               |              |         |           | —                    | _                               |

| 198h                | —                     | Unimplement                    | ted                                             |                  |                 |               |              |         |           | _                    | _                               |

| 199h                | RCREG                 | USART Rece                     | eive Data Regi                                  | ster             |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 19Ah                | TXREG                 | USART Tran                     | smit Data Reg                                   | ister            |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 19Bh                | SPBRGL                | Baud Rate G                    | enerator Data                                   | Register Low     |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 19Ch                | SPBRGH                | Baud Rate G                    | enerator Data                                   | Register High    |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 19Dh                | RCSTA                 | SPEN                           | RX9                                             | SREN             | CREN            | ADDEN         | FERR         | OERR    | RX9D      | 0000 000x            | 0000 000x                       |

| 19Eh                | TXSTA                 | CSRC                           | TX9                                             | TXEN             | SYNC            | SENDB         | BRGH         | TRMT    | TX9D      | 0000 0010            | 0000 0010                       |

|                     | 1                     | ABDOVF                         | RCIDL                                           |                  | SCKP            | BRG16         |              | WUE     | ABDEN     | 01-0 0-00            | 01-0 0-00                       |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-8

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

PIC16(L)F1829 only.

PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

| IABLE               | . 3-0.          | SPECIAL F                      | UNCTION                                                              | REGIST           | ER SUMI         |               |             | -D)       | 1         | 1                    | 1                               |

|---------------------|-----------------|--------------------------------|----------------------------------------------------------------------|------------------|-----------------|---------------|-------------|-----------|-----------|----------------------|---------------------------------|

| Address             | Name            | Bit 7                          | Bit 6                                                                | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3              | 1               |                                |                                                                      |                  |                 |               |             |           |           |                      |                                 |

| F80h <sup>(1)</sup> | INDF0           | Addressing th<br>(not a physic |                                                                      | es contents of   | FSR0H/FSR0      | )L to address | data memory | ý         |           | XXXX XXXX            | XXXX XXXX                       |

| F81h <sup>(1)</sup> | INDF1           | Addressing the (not a physic)  |                                                                      | es contents of   | FSR1H/FSR1      | 1L to address | data memory | ý         |           | XXXX XXXX            | XXXX XXXX                       |

| F82h <sup>(1)</sup> | PCL             | Program Cou                    | inter (PC) Lea                                                       | st Significant E | Byte            |               |             |           |           | 0000 0000            | 0000 0000                       |

| F83h <sup>(1)</sup> | STATUS          | _                              | _                                                                    | —                | TO              | PD            | Z           | DC        | С         | 1 1000               | q quuu                          |

| F84h <sup>(1)</sup> | FSR0L           | Indirect Data                  | Memory Addr                                                          | ess 0 Low Poi    | nter            |               |             | •         | •         | 0000 0000            | uuuu uuuu                       |

| F85h <sup>(1)</sup> | FSR0H           | Indirect Data                  | ct Data Memory Address 0 High Pointer                                |                  |                 |               |             |           |           |                      | 0000 0000                       |

| F86h <sup>(1)</sup> | FSR1L           | Indirect Data                  | Memory Addr                                                          | ess 1 Low Poi    | nter            |               |             |           |           | 0000 0000            | uuuu uuuu                       |

| F87h <sup>(1)</sup> | FSR1H           | Indirect Data                  | Memory Address 1 High Pointer           —         —         BSR<4:0> |                  |                 |               |             |           |           | 0000 0000            | 0000 0000                       |

| F88h <sup>(1)</sup> | BSR             |                                | —                                                                    | —                |                 |               |             | 0 0000    | 0 0000    |                      |                                 |

| F89h <sup>(1)</sup> | WREG            | Working Reg                    | ister                                                                |                  |                 |               |             | 0000 0000 | uuuu uuuu |                      |                                 |

| F8Ah <sup>(1)</sup> | PCLATH          | _                              | Write Buffer f                                                       | or the upper 7   | bits of the Pro | ogram Counte  | er          |           |           | -000 0000            | -000 0000                       |

| F8Bh <sup>(1)</sup> | INTCON          | GIE                            | PEIE                                                                 | TMR0IE           | INTE            | IOCIE         | TMR0IF      | INTF      | IOCIF     | 0000 0000            | 0000 0000                       |

| F8Ch                | —               | Unimplement                    | ted                                                                  |                  |                 |               |             |           |           | -                    | _                               |

| FE3h                |                 |                                |                                                                      | -                |                 |               |             |           |           |                      |                                 |

| FE4h                | STATUS_<br>SHAD | -                              | _                                                                    | —                | _               | _             | Z_SHAD      | DC_SHAD   | C_SHAD    | xxx                  | uuu                             |

| FE5h                | WREG_<br>SHAD   | Working Reg                    | ister Shadow                                                         |                  |                 |               |             |           |           | 0000 0000            | uuuu uuuu                       |

| FE6h                | BSR_<br>SHAD    | —                              | _                                                                    | _                | Bank Select     | Register Sha  | dow         |           |           | x xxxx               | u uuuu                          |

| FE7h                | PCLATH_<br>SHAD | -                              | Program Cou                                                          | Inter Latch Hig  | h Register Sh   | nadow         |             |           |           | -xxx xxxx            | uuuu uuuu                       |

| FE8h                | FSR0L_<br>SHAD  | Indirect Data                  | Memory Addr                                                          | ess 0 Low Poi    | nter Shadow     |               |             |           |           | XXXX XXXX            | uuuu uuuu                       |

| FE9h                | FSR0H_<br>SHAD  | Indirect Data                  | Memory Addr                                                          | ess 0 High Po    | inter Shadow    |               |             |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEAh                | FSR1L_<br>SHAD  | Indirect Data                  | Memory Addr                                                          | ess 1 Low Poi    | nter Shadow     |               |             |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEBh                | FSR1H_<br>SHAD  | Indirect Data                  | Memory Addr                                                          | ess 1 High Po    | inter Shadow    |               |             |           |           | XXXX XXXX            | uuuu uuuu                       |

| FECh                | —               | Unimplement                    | ted                                                                  |                  |                 |               |             |           |           | _                    | _                               |

| FEDh                | STKPTR          | —                              | _                                                                    | _                | Current Stac    | k pointer     |             |           |           | 1 1111               | 1 1111                          |

| FEEh                | TOSL            | Top-of-Stack                   | Low byte                                                             |                  | 1               |               |             |           |           | xxxx xxxx            | uuuu uuuu                       |

| FEFh                | TOSE            | _                              | Top-of-Stack                                                         | Hiah byte        |                 |               |             |           |           | -xxx xxxx            |                                 |

|                     | 1030            |                                |                                                                      | • •              |                 |               |             |           |           |                      | auu uuu                         |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-8:**

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only.

3: PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

| REGISTER 12-18: | ANSELC: PORTC ANALOG SELECT REGISTER |  |

|-----------------|--------------------------------------|--|

|                 |                                      |  |

| R/W-1/1                                 | R/W-1/1              | U-0                                                   | U-0              | R/W-1/1                                               | R/W-1/1          | R/W-1/1  | R/W-1/1                 |  |  |  |

|-----------------------------------------|----------------------|-------------------------------------------------------|------------------|-------------------------------------------------------|------------------|----------|-------------------------|--|--|--|

| ANSC7 <sup>(2)</sup>                    | ANSC6 <sup>(2)</sup> | _                                                     |                  | ANSC3                                                 | ANSC2            | ANSC1    | ANSC0                   |  |  |  |

| bit 7                                   | -                    |                                                       | •                | ·                                                     |                  | •        | bit 0                   |  |  |  |

|                                         |                      |                                                       |                  |                                                       |                  |          |                         |  |  |  |

| Legend:                                 |                      |                                                       |                  |                                                       |                  |          |                         |  |  |  |

| R = Readable bit W = Writable bit       |                      |                                                       |                  | U = Unimpler                                          | nented bit, read | d as '0' |                         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                      |                                                       |                  | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |                         |  |  |  |

| '1' = Bit is set                        |                      | '0' = Bit is cle                                      | ared             |                                                       |                  |          |                         |  |  |  |

| bit 7-6                                 | 0 = Digital I/       | Analog Select<br>O. Pin is assigr<br>nput. Pin is ass | ned to port or d | ligital special fu                                    | inction.         |          | ectively <sup>(2)</sup> |  |  |  |

| bit 5-4                                 | Unimplemen           | nted: Read as '                                       | 0'               |                                                       |                  |          |                         |  |  |  |

| bit 3-0                                 | 0 = Digital I/       | Analog Select<br>O. Pin is assigr<br>nput. Pin is ass | ned to port or d | ligital special fu                                    | inction.         |          | ectively                |  |  |  |

|                                         |                      |                                                       |                  |                                                       |                  |          |                         |  |  |  |

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

## REGISTER 12-19: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                | •                    |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

- 3: WPUC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

### 24.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 24-4.

#### EQUATION 24-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 24-5:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

#### TABLE 24-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 24-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

| R/W-0/0                                                            | R/W-0/0                                                                                                                           | R/W-0/0                              | R/W-0/0       | R/W-0/0         | R/W-0/0                | R/W-0/0            | R/W-0/0      |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|-----------------|------------------------|--------------------|--------------|--|--|--|

| CCPxASE                                                            |                                                                                                                                   | CCPxAS<2:0>                          |               | PSSxA           | \C<1:0>                | C<1:0> PSSxBD<1:0> |              |  |  |  |

| bit 7                                                              |                                                                                                                                   |                                      |               |                 |                        |                    | bit          |  |  |  |

|                                                                    |                                                                                                                                   |                                      |               |                 |                        |                    |              |  |  |  |

| Legend:                                                            |                                                                                                                                   |                                      |               |                 |                        |                    |              |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                                   |                                      |               |                 |                        |                    |              |  |  |  |

| u = Bit is unc                                                     | hanged                                                                                                                            | x = Bit is unkn                      | own           | -n/n = Value a  | at POR and BC          | R/Value at all     | other Resets |  |  |  |

| '1' = Bit is se                                                    | t                                                                                                                                 | '0' = Bit is clea                    | ared          |                 |                        |                    |              |  |  |  |

|                                                                    |                                                                                                                                   |                                      |               |                 |                        |                    |              |  |  |  |

| bit 7                                                              | CCPxASE: CCPx Auto-Shutdown Event Status bit                                                                                      |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | <ul> <li>1 = A shutdown event has occurred; CCPx outputs are in shutdown state</li> <li>0 = CCPx outputs are operating</li> </ul> |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | CCPxAS<2:0>: CCPx Auto-Shutdown Source Select bits                                                                                |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    |                                                                                                                                   | 000 = Auto-shutdown is disabled      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 001 = Comparator C1 output high <sup>(1)</sup>                                                                                    |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 010 = Comparator C2 output high <sup>(1)</sup>                                                                                    |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 011 = Either Comparator C1 or C2 high <sup>(1)</sup><br>100 = Vi∟ on FLT0 pin                                                     |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 101 = VIL on FLT0 pin or Comparator C1 high <sup>(1)</sup>                                                                        |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 110 = VIL on FLT0 pin or Comparator C2 high(1)                                                                                    |                                      |               |                 |                        |                    |              |  |  |  |

|                                                                    | 111 <b>=</b> VIL OI                                                                                                               | n FLT0 pin or Coi                    | mparator C1 o | or Comparator ( | C2 high <sup>(1)</sup> |                    |              |  |  |  |

| bit 3-2                                                            | PSSxAC<1                                                                                                                          | :0>: Pins PxA an                     | d PxC Shutdo  | own State Conti | rol bits               |                    |              |  |  |  |

|                                                                    | •                                                                                                                                 | 00 = Drive pins PxA and PxC to '0'   |               |                 |                        |                    |              |  |  |  |

|                                                                    |                                                                                                                                   | 01 = Drive pins PxA and PxC to '1'   |               |                 |                        |                    |              |  |  |  |

|                                                                    |                                                                                                                                   | xA and PxC tri-st                    |               |                 |                        |                    |              |  |  |  |

| bit 1-0                                                            |                                                                                                                                   | :0>: Pins PxB an                     |               | own State Contr | ol bits                |                    |              |  |  |  |

|                                                                    |                                                                                                                                   | oins PxB and PxE<br>oins PxB and PxE |               |                 |                        |                    |              |  |  |  |

|                                                                    | 01 = Drive r                                                                                                                      |                                      |               |                 |                        |                    |              |  |  |  |

## REGISTER 24-3: CCPxAS: CCPx AUTO-SHUTDOWN CONTROL REGISTER

**Note 1:** If CxSYNC is enabled, the shutdown will be delayed by Timer1.

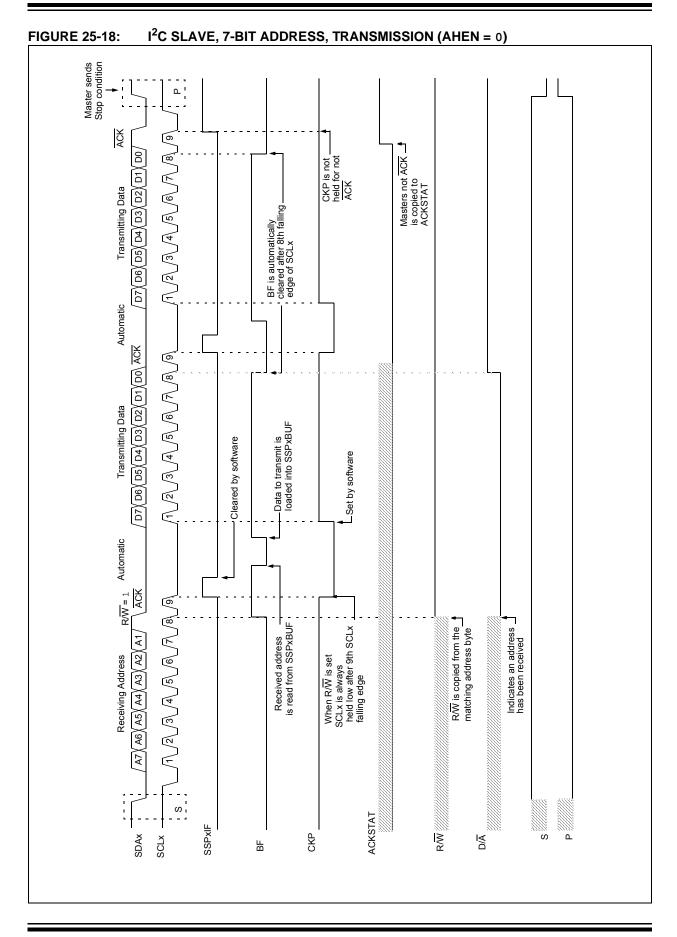

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

### 25.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of Clock Stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

## 25.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

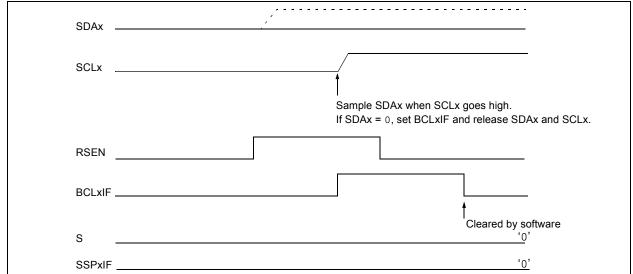

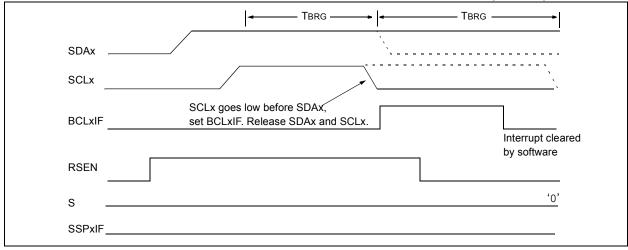

## 25.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from low level to high level. (CASE 1)

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'. (CASE 2)

When the user releases SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled. If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0' (Figure 25-36). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 25-37).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

#### FIGURE 25-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 25-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                |            |                             |                    |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Foso                                                 | : = 32.00  | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc           | : = 18.43  | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9600               | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10433              | 0.16       | 264                         |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |

## TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |            |                             |                |            |                             |                |            |                             |  |

|-----------------------|------------------------------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD Fosc = 8.000 MHz |                                                      |            | Fosc = 4.000 MHz            |                |            | Fosc                        | : = 3.686      | 4 MHz      | Fosc = 1.000 MHz            |                |            |                             |  |

| RATE                  | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300                   | 300.0                                                | 0.00       | 6666                        | 300.0          | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |  |

| 1200                  | 1200                                                 | -0.02      | 1666                        | 1200           | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |  |

| 2400                  | 2401                                                 | 0.04       | 832                         | 2398           | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |  |

| 9600                  | 9615                                                 | 0.16       | 207                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |  |

| 10417                 | 10417                                                | 0          | 191                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |  |

| 19.2k                 | 19.23k                                               | 0.16       | 103                         | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |  |

| 57.6k                 | 57.14k                                               | -0.79      | 34                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |  |

| 115.2k                | 117.6k                                               | 2.12       | 16                          | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | —              | —          | —                           |  |

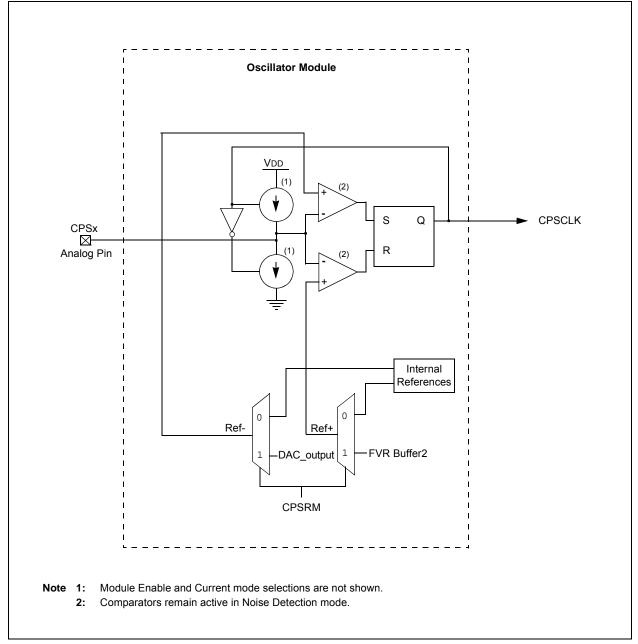

## FIGURE 27-2: CAPACITIVE SENSING OSCILLATOR BLOCK DIAGRAM

## 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1825/9 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

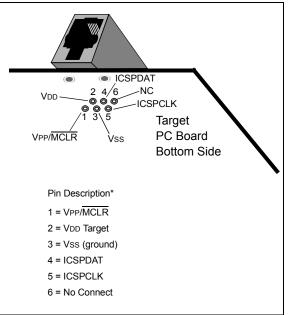

## 28.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

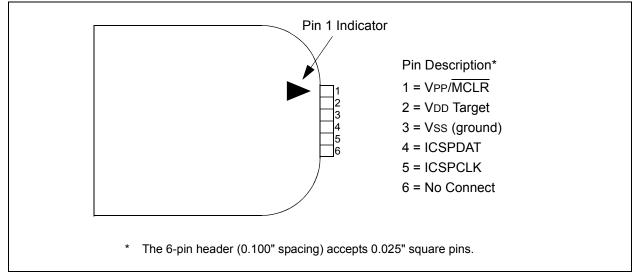

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

### FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

## 30.2 DC Characteristics: PIC16(L)F1825/9-I/E (Industrial, Extended)

| PIC16LF      | 1825/9                              | Operating temperature -40° |      |                               |         | tions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended   |                                          |  |  |  |

|--------------|-------------------------------------|----------------------------|------|-------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| PIC16F1825/9 |                                     |                            |      | <b>l Operati</b><br>g tempera | ature · | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                          |  |  |  |

| Param        | aram Device                         |                            | Тур† |                               | 11      | Conditions                                                                                                                     |                                          |  |  |  |

| No.          | Characteristics                     | Min.                       | турт | Max.                          | Units   | Vdd                                                                                                                            | Note                                     |  |  |  |

|              | Supply Current (IDD) <sup>(1,</sup> | 2)                         |      |                               |         |                                                                                                                                |                                          |  |  |  |

| D010         |                                     | _                          | 5.5  | 15                            | μΑ      | 1.8                                                                                                                            | Fosc = 32 kHz                            |  |  |  |

|              |                                     | _                          | 7.8  | 18                            | μΑ      | 3.0                                                                                                                            | LP Oscillator mode                       |  |  |  |

| D010         |                                     | _                          | 20   | 55                            | μΑ      | 1.8                                                                                                                            | Fosc = 32 kHz                            |  |  |  |

|              |                                     | —                          | 25   | 60                            | μΑ      | 3.0                                                                                                                            | LP Oscillator mode                       |  |  |  |

|              |                                     | —                          | 27   | 65                            | μA      | 5.0                                                                                                                            |                                          |  |  |  |

| D011         |                                     | —                          | 83   | 140                           | μA      | 1.8                                                                                                                            | Fosc = 1 MHz                             |  |  |  |

|              |                                     | _                          | 130  | 230                           | μA      | 3.0                                                                                                                            | XT Oscillator mode                       |  |  |  |

| D011         |                                     | —                          | 105  | 160                           | μA      | 1.8                                                                                                                            | Fosc = 1 MHz                             |  |  |  |

|              |                                     | —                          | 160  | 250                           | μΑ      | 3.0                                                                                                                            | XT Oscillator mode                       |  |  |  |

|              |                                     | —                          | 230  | 320                           | μΑ      | 5.0                                                                                                                            |                                          |  |  |  |

| D012         |                                     | —                          | 220  | 310                           | μA      | 1.8                                                                                                                            | Fosc = 4 MHz                             |  |  |  |

|              |                                     | —                          | 378  | 540                           | μA      | 3.0                                                                                                                            | XT Oscillator mode                       |  |  |  |

| D012         |                                     | —                          | 240  | 300                           | μΑ      | 1.8                                                                                                                            | Fosc = 4 MHz                             |  |  |  |

|              |                                     | —                          | 400  | 500                           | μA      | 3.0                                                                                                                            | XT Oscillator mode                       |  |  |  |

|              |                                     | —                          | 500  | 760                           | μA      | 5.0                                                                                                                            |                                          |  |  |  |

| D013         |                                     |                            | 46   | 160                           | μΑ      | 1.8                                                                                                                            | Fosc = 1 MHz                             |  |  |  |

|              |                                     | —                          | 90   | 230                           | μΑ      | 3.0                                                                                                                            | EC Oscillator mode, Medium-Power mode    |  |  |  |

| D013         |                                     | _                          | 70   | 180                           | μΑ      | 1.8                                                                                                                            | Fosc = 1 MHz                             |  |  |  |

|              |                                     | _                          | 120  | 240                           | μΑ      | 3.0                                                                                                                            | EC Oscillator mode<br>Medium-Power mode  |  |  |  |

|              |                                     | —                          | 190  | 320                           | μΑ      | 5.0                                                                                                                            |                                          |  |  |  |

| D014         |                                     | —                          | 192  | 250                           | μΑ      | 1.8                                                                                                                            | Fosc = 4 MHz                             |  |  |  |

|              |                                     | —                          | 336  | 430                           | μA      | 3.0                                                                                                                            | EC Oscillator mode,<br>Medium-Power mode |  |  |  |

| D014         |                                     |                            | 210  | 275                           | μA      | 1.8                                                                                                                            | Fosc = 4 MHz                             |  |  |  |

|              |                                     |                            | 356  | 450                           | μΑ      | 3.0                                                                                                                            | EC Oscillator mode<br>Medium-Power mode  |  |  |  |

|              |                                     | _                          | 430  | 650                           | μA      | 5.0                                                                                                                            |                                          |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- **3:** 8 MHz internal RC oscillator with 4xPLL enabled.

- **4:** 8 MHz crystal oscillator with 4xPLL enabled.

5: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

### TABLE 30-25: A/D CONVERTER (ADC) CHARACTERISTICS FOR PIC16F1825/9-H (High Temp.)

|              |      |                | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |      |       |                                 |  |  |

|--------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------------------------------|--|--|

| Param<br>No. | Sym. | Characteristic | Min.                                                                                                                                            | Тур. | Max. | Units | Conditions                      |  |  |

| AD04         | Eoff | Offset Error   | —                                                                                                                                               | —    | 3.5  |       | No missing codes<br>VREF = 3.0V |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF, VDD pin or FVR, whichever is selected as reference input.

#### TABLE 30-26: COMPARATOR SPECIFICATIONS FOR PIC16F1825/9-H (High Temp.)

| PIC16F       |       |                      |      |      | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |       |                                  |  |  |  |  |

|--------------|-------|----------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|--|--|--|--|

| Param<br>No. | Sym.  | Characteristic       | Min. | Тур. | Max.                                                                                                                                            | Units | Conditions                       |  |  |  |  |

| CM01         | VIOFF | Input Offset Voltage | —    | —    | ±70                                                                                                                                             | mV    | High-Power mode,<br>VICM = VDD/2 |  |  |  |  |

#### TABLE 30-27: CAP SENSE OSCILLATOR SPECIFICATIONS FOR PIC16F1825/9-H (High Temp.)

|              |      |                | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |      |       |                                                                  |  |

|--------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------------------|--|

| Param<br>No. | Sym. | Characteristic | Min.                                                                                                                                            | Тур. | Max. | Units | Conditions                                                       |  |

| All          | All  | All            |                                                                                                                                                 |      | —    |       | This module is not intended for use in high temperature devices. |  |

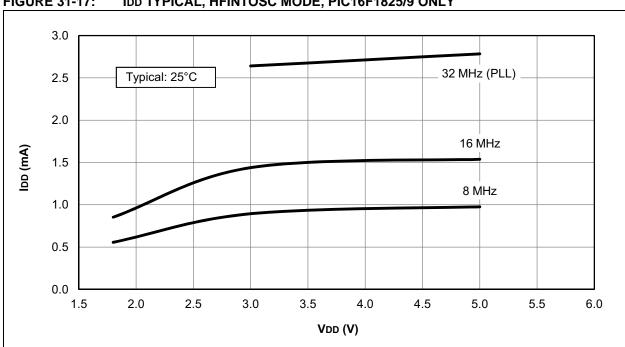

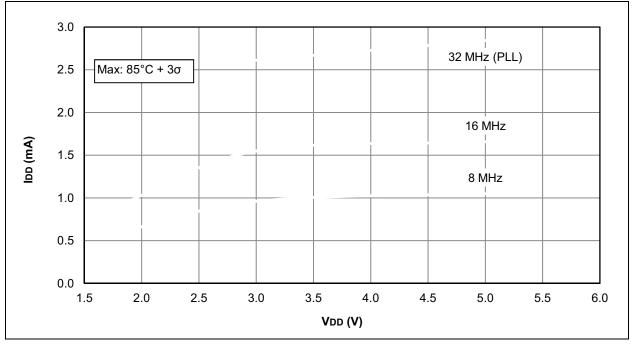

FIGURE 31-17: IDD TYPICAL, HFINTOSC MODE, PIC16F1825/9 ONLY

## 32.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 32.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 32.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 32.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 32.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

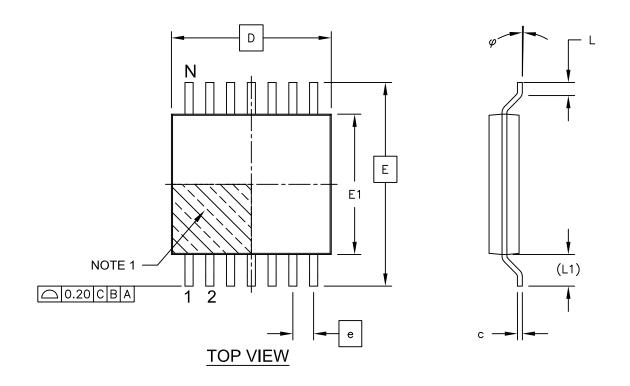

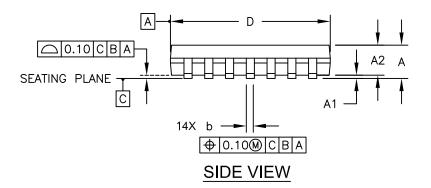

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2