Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

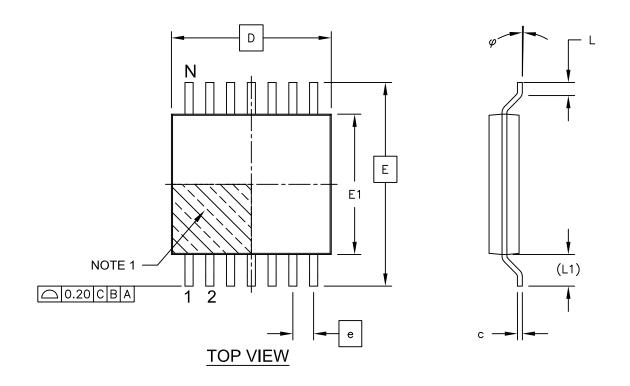

| Mounting Type              | Surface Mount                                                              |

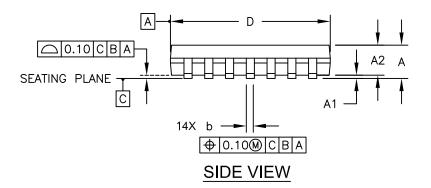

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1829t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

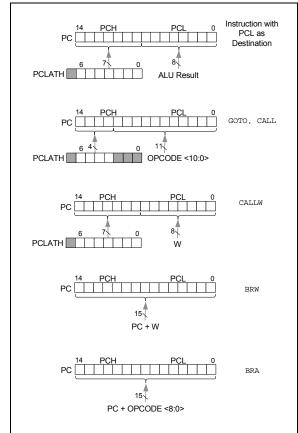

#### 3.3 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.3.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.3.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.3.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

| EXAM                 | PLE 11-4:                                             | ERASING ON                                   | E ROW OF PROGRAM MEMORY                                                                                                                                                              |

|----------------------|-------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; This               | row erase                                             | routine assumes                              | the following:                                                                                                                                                                       |

| ; 1. A               | valid addr                                            | ess within the                               | erase block is loaded in ADDRH:ADDRL                                                                                                                                                 |

| ; 2. A               | DDRH and AD                                           | DRL are located                              | l in shared data memory 0x70 - 0x7F                                                                                                                                                  |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF<br>BCF | EECON1,CFGS                                  |                                                                                                                                                                                      |

|                      | BSF                                                   |                                              | ; Specify an erase operation                                                                                                                                                         |

|                      | BSF                                                   | EECON1,WREN                                  | ; Enable writes                                                                                                                                                                      |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP        | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor</pre> |

|                      | NOP                                                   |                                              | ; halts to begin erase sequence<br>; Processor will stop here and wait for erase complete.                                                                                           |

|                      | BCF<br>BSF                                            | EECON1, WREN<br>INTCON, GIE                  | <ul> <li>; after erase processor continues with 3rd instruction</li> <li>; Disable writes</li> <li>; Enable interrupts</li> </ul>                                                    |

|                      |                                                       |                                              | -                                                                                                                                                                                    |

| U-0            | U-0             | R/W-0/0                                              | R/W-0/0               | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|-----------------|------------------------------------------------------|-----------------------|----------------|------------------|------------------|--------------|

| _              | _               | SDO2SEL <sup>(1)</sup>                               | SS2SEL <sup>(1)</sup> | P1DSEL         | P1CSEL           | P2BSEL           | CCP2SEL      |

| bit 7          |                 |                                                      |                       |                |                  |                  | bit 0        |

|                |                 |                                                      |                       |                |                  |                  |              |

| Legend:        |                 |                                                      |                       |                |                  |                  |              |

| R = Readat     | ole bit         | W = Writable                                         | bit                   | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is ur  | nchanged        | x = Bit is unkr                                      | iown                  | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s | et              | '0' = Bit is clea                                    | ared                  |                |                  |                  |              |

|                |                 |                                                      |                       |                |                  |                  |              |

| bit 7-6        | -               | ented: Read as '                                     |                       |                |                  |                  |              |

| bit 5          |                 | Pin Selection bit                                    |                       |                |                  |                  |              |

|                |                 | function is on R                                     |                       |                |                  |                  |              |

|                |                 | function is on R/                                    |                       |                |                  |                  |              |

| bit 4          |                 | in Selection bit <sup>(1)</sup><br>unction is on RC0 |                       |                |                  |                  |              |

|                |                 | unction is on RCC                                    |                       |                |                  |                  |              |

| bit 3          |                 | in Selection bit                                     |                       |                |                  |                  |              |

|                | -               | unction is on RC2                                    | 2                     |                |                  |                  |              |

|                | 1 = P1D fu      | unction is on RC0                                    | )                     |                |                  |                  |              |

| bit 2          | P1CSEL: P       | in Selection bit                                     |                       |                |                  |                  |              |

|                |                 | unction is on RC3                                    |                       |                |                  |                  |              |

|                |                 | unction is on RC <sup>2</sup>                        |                       |                |                  |                  |              |

| bit 1          | -               | in Selection bit                                     |                       |                |                  |                  |              |

|                |                 | unction is on RC2<br>unction is on RA4               | -                     |                |                  |                  |              |

| bit 0          |                 | Pin Selection bit                                    |                       |                |                  |                  |              |

|                |                 | P2A function is o                                    | on RC3                |                |                  |                  |              |

|                |                 | /P2A function is a                                   |                       |                |                  |                  |              |

| Noto 1.        |                 | only                                                 |                       |                |                  |                  |              |

| Note 1:        | PIC16(L)F1829 ( | oniy.                                                |                       |                |                  |                  |              |

#### REGISTER 12-2: APFCON1: ALTERNATE PIN FUNCTION CONTROL REGISTER 1

#### 12.3.2 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup>             |

|----------|----------------------------------------------|

| RB4      | SDA                                          |

| RB5      | SDA2<br>RX <sup>(2)</sup> /DT <sup>(2)</sup> |

| RB6      | SCL/SCK                                      |

| RB7      | TX <sup>(2)</sup> /CK <sup>(2)</sup>         |

TABLE 12-5: PORTB OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

2: Pin function is selectable via the APFCON0 or APFCON1 register.

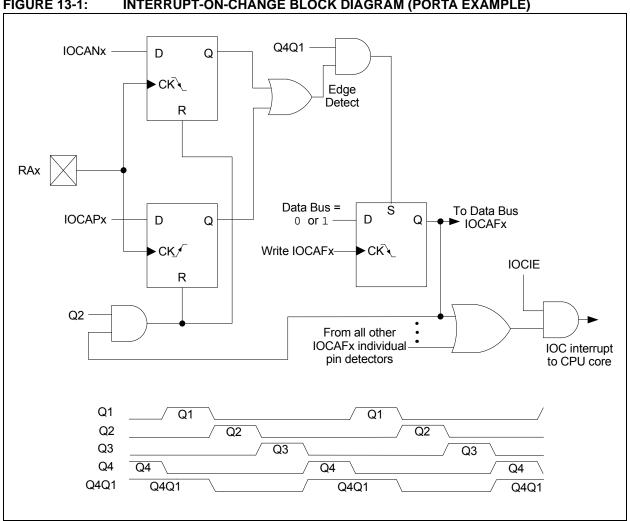

#### **FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM (PORTA EXAMPLE)**

#### Interrupt-on-Change Registers 13.6

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### 14.3 FVR Control Registers

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0          | R-q/q                                        | R/W-0/0                                                    | R/W-0/0                                         | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                              | R/W-0/0                                                 | R/W-0/0      |

|------------------|----------------------------------------------|------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|

| FVREN            | FVRRDY <sup>(1)</sup>                        | TSEN                                                       | TSRNG                                           | CDAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /R<1:0>                                                                                              | ADFVI                                                   | R<1:0>       |

| bit 7            |                                              | ·                                                          |                                                 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |                                                         | bit (        |

|                  |                                              |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                         |              |

| Legend:          |                                              |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                         |              |

| R = Readable     | bit                                          | W = Writable                                               | bit                                             | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nented bit, read                                                                                     | as '0'                                                  |              |

| u = Bit is unch  | nanged                                       | x = Bit is unkr                                            | nown                                            | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | at POR and BOI                                                                                       | R/Value at all c                                        | other Resets |

| '1' = Bit is set |                                              | '0' = Bit is cle                                           | ared                                            | q = Value dep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | pends on condit                                                                                      | ion                                                     |              |

| bit 7            | 0 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc<br>Itage Referenc         | e is disabled                                   | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |                                                         |              |

| bit 6            | 0 = Fixed Vo                                 | ed Voltage Ref<br>Itage Referenc<br>Itage Referenc         | e output is no                                  | t ready or not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nabled                                                                                               |                                                         |              |

| bit 5            | 0 = Tempera                                  | erature Indicato<br>ture indicator is<br>ture indicator is | s disabled                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                         |              |

| bit 4            | 0 = VOUT = V                                 | perature Indica<br>′DD - 2V⊤ (Low<br>′DD - 4V⊤ (High       | Range)                                          | election bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      |                                                         |              |

| bit 3-2          | 00 = Compara<br>01 = Compara<br>10 = Compara | ator and DAC I<br>ator and DAC I<br>ator and DAC I         | Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage | Reference Per<br>Reference Per<br>Reference Per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ference Selectic<br>ipheral output is<br>ipheral output is<br>ipheral output is<br>ipheral output is | s off<br>s 1x (1.024V)<br>s 2x (2.048V) <mark>(2</mark> |              |

| bit 1-0          | 00 = ADC Fix<br>01 = ADC Fix<br>10 = ADC Fix | ed Voltage Re<br>ed Voltage Re<br>ed Voltage Re            | ference Perip<br>ference Perip<br>ference Perip | nce Selection theral output is the heral outpu | off<br>1x (1.024V)<br>2x (2.048V) <b>(2)</b>                                                         |                                                         |              |

|                  | RRDY is always<br>ed Voltage Refe            |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /9).                                                                                                 |                                                         |              |

3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 142                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

#### 19.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 19-1) contain Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- · Speed/Power selection

- · Hysteresis enable

- · Output synchronization

The CMxCON1 registers (see Register 19-2) contain Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 19.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 19.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 19.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 19-1 shows the output state versus input conditions, including polarity control.

#### TABLE 19-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 19.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

#### 19.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

#### **19.4** Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 19-2) and the Timer1 Block Diagram (Figure 21-1) for more information.

#### **19.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

| Note: | Although a comparator is disabled, an      |

|-------|--------------------------------------------|

|       | interrupt can be generated by changing     |

|       | the output polarity with the CxPOL bit of  |

|       | the CMxCON0 register, or by switching      |

|       | the comparator on or off with the CxON bit |

|       | of the CMxCON0 register.                   |

## 19.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN+ analog pin

- DAC\_output

- FVR Buffer2

- Vss (Ground)

See **Section 14.0** "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

### 19.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

Note: To use CxIN+ and CxINx- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

#### 19.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 30.0 "Electrical Specifications"** for more details.

| Name    | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3     | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|------------------------|------------------------|---------|---------|-----------|---------|---------|---------|---------------------|

| CM1CON0 | C10N                   | C1OUT                  | C10E    | C1POL   | _         | C1SP    | C1HYS   | C1SYNC  | 171                 |

| CM1CON1 | C1NTP                  | C1INTN                 | C1PCH1  | C1PCH0  | —         | _       | C1NCI   | H<1:0>  | 172                 |

| CM2CON0 | C2ON                   | C2OUT                  | C2OE    | C2POL   | —         | C2SP    | C2HYS   | C2SYNC  | 171                 |

| CM2CON1 | C2NTP                  | C2INTN                 | C2PCI   | H<1:0>  | _         |         | C2NCI   | H<1:0>  | 172                 |

| CMOUT   | _                      | _                      | _       | _       | —         | _       | MC2OUT  | MC1OUT  | 172                 |

| DACCON0 | DACEN                  | DACLPS                 | DACOE   | _       | DACPS     | SS<1:0> | _       | DACNSS  | 160                 |

| DACCON1 | _                      | _                      | _       |         | DACR<4:0> |         |         |         | 160                 |

| FVRCON  | FVREN                  | FVRRDY                 | TSEN    | TSRNG   | CDAFV     | ′R<1:0> | ADFV    | R<1:0>  | 142                 |

| INLVLA  | _                      | _                      | INLVLA5 | INLVLA4 | INLVLA3   | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| INLVLC  | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3   | INLVLC2 | INLVLC1 | INLVLC0 | 135                 |

| INTCON  | GIE                    | PEIE                   | TMR0IE  | INTE    | IOCIE     | TMR0IF  | INTF    | IOCIF   | 87                  |

| PIE2    | OSFIE                  | C2IE                   | C1IE    | EEIE    | BCL1IE    | —       | _       | CCP2IE  | 89                  |

| PIR2    | OSFIF                  | C2IF                   | C1IF    | EEIF    | BCL1IF    | —       | _       | CCP2IF  | 93                  |

| PORTC   | RC7                    | RC6                    | RC5     | RC4     | RC3       | RC2     | RC1     | RC0     | 133                 |

| LATC    | LATC7                  | LATC6                  | LATC5   | LATC4   | LATC3     | LATC2   | LATC1   | LATC0   | 133                 |

| TRISA   | —                      | —                      | TRISA5  | TRISA4  | TRISA3    | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISC   | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3    | TRISC2  | TRISC1  | TRISC0  | 133                 |

Legend: — Unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

**Note 1:** PIC16(L)F1829 only.

#### 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 23.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current.

The values used to select the carrier high, carrier low, and modulator sources held by the Modulation Source, Modulation High Carrier, and Modulation Low Carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the MDOUT pin. During the time that the output is disabled, the MDOUT pin will remain low. The modulated output can be disabled by clearing the MDOE bit in the MDCON register.

#### 23.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Signal

- CCP2 Signal

- CCP3 Signal

- CCP4 Signal

- MSSP1 SDO1 Signal (SPI Mode Only)

- MSSP2 SDO2 Signal (SPI Mode Only)

- Comparator C1 Signal

- Comparator C2 Signal

- EUSART TX Signal

- External Signal on MDMIN pin

- MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

#### 23.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 Signal

- CCP2 Signal

- CCP3 Signal

- CCP4 Signal

- Reference Clock Module Signal

- External Signal on MDCIN1 pin

- External Signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

#### 23.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When synchronization is enabled, the carrier pulse that is being mixed at the time of the transition is allowed to transition low before the DSM switches over to the next carrier source.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal can be enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal can be enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 23-1 through Figure 23-5 show timing diagrams of using various synchronization methods.

| U-0            | U-0                                                                    | U-0                                                                                | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0        | R/W-1/1      |

|----------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------|-----------------|-------------------|----------------|--------------|

| _              | _                                                                      | —                                                                                  | STRxSYNC         | STRxD           | STRxC             | STRxB          | STRxA        |

| bit 7          |                                                                        |                                                                                    |                  | •               | •                 |                | bit C        |

|                |                                                                        |                                                                                    |                  |                 |                   |                |              |

| Legend:        |                                                                        |                                                                                    |                  |                 |                   |                |              |

| R = Readat     | ole bit                                                                | W = Writable bit                                                                   |                  | U = Unimpler    | mented bit, read  | d as '0'       |              |

| u = Bit is ur  | nchanged                                                               | x = Bit is unk                                                                     | nown             | -n/n = Value a  | at POR and BC     | R/Value at all | other Resets |

| '1' = Bit is s | et                                                                     | '0' = Bit is cle                                                                   | ared             |                 |                   |                |              |

|                |                                                                        |                                                                                    |                  |                 |                   |                |              |

| bit 7-5        | Unimplemer                                                             | nted: Read as                                                                      | '0'              |                 |                   |                |              |

| bit 4          | STRxSYNC:                                                              | STRxSYNC: Steering Sync bit                                                        |                  |                 |                   |                |              |

|                | 1 = Output steering update occurs on next PWM period                   |                                                                                    |                  |                 |                   |                |              |

|                | -                                                                      | = Output steering update occurs at the beginning of the instruction cycle boundary |                  |                 |                   |                |              |

| bit 3          |                                                                        | STRxD: Steering Enable bit D                                                       |                  |                 |                   |                |              |

|                | •                                                                      |                                                                                    | vaveform with p  | olarity control | from CCPxM<       | 1:0>           |              |

|                | •                                                                      | 0 = PxD pin is assigned to port pin                                                |                  |                 |                   |                |              |

| bit 2          |                                                                        | STRxC: Steering Enable bit C                                                       |                  |                 |                   |                |              |

|                | •                                                                      |                                                                                    | vaveform with p  | olarity control | from CCPxM<       | 1:0>           |              |

|                | •                                                                      | is assigned to                                                                     | •                |                 |                   |                |              |

| bit 1          |                                                                        | ering Enable bi                                                                    |                  |                 |                   |                |              |

|                | 1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0> |                                                                                    |                  |                 |                   |                |              |

|                | 0 = PxB pin i                                                          | s assigned to p                                                                    | port pin         |                 |                   |                |              |

| bit 0          |                                                                        | ering Enable bi                                                                    |                  |                 |                   |                |              |

|                | 1 = PxA pin ł                                                          | has the PWM v                                                                      | vaveform with p  | olarity control | from CCPxM<       | 1:0>           |              |

|                | 0 = PxA pin i                                                          | s assigned to p                                                                    | port pin         |                 |                   |                |              |