Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

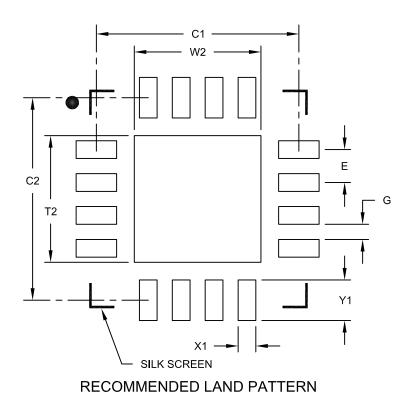

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1825-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE                        | . 3-0. 3   |                               |                                             | REGIST           |                 |               |             | (ט    |       |                      |                                 |  |  |  |

|------------------------------|------------|-------------------------------|---------------------------------------------|------------------|-----------------|---------------|-------------|-------|-------|----------------------|---------------------------------|--|--|--|

| Address                      | Name       | Bit 7                         | Bit 6                                       | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |  |  |

| Banks 9                      | Banks 9-30 |                               |                                             |                  |                 |               |             |       |       |                      |                                 |  |  |  |

| x00h/<br>x80h <sup>(1)</sup> | INDF0      | Addressing the (not a physic) |                                             | es contents of   | FSR0H/FSR0      | )L to address | data memory | ,     |       | XXXX XXXX            | XXXX XXXX                       |  |  |  |

| x00h/<br>x81h <sup>(1)</sup> | INDF1      | Addressing the (not a physic) |                                             | es contents of   | FSR1H/FSR1      | L to address  | data memory | ,     |       | XXXX XXXX            | XXXX XXXX                       |  |  |  |

| x02h/<br>x82h <sup>(1)</sup> | PCL        | Program Cou                   | inter (PC) Lea                              | st Significant E | 3yte            |               |             |       |       | 0000 0000            | 0000 0000                       |  |  |  |

| x03h/<br>x83h <sup>(1)</sup> | STATUS     | —                             | _                                           | _                | TO              | PD            | Z           | DC    | С     | 1 1000               | q quuu                          |  |  |  |

| x04h/<br>x84h <sup>(1)</sup> | FSR0L      | Indirect Data                 | Memory Addr                                 | ess 0 Low Poir   | nter            |               |             |       |       | 0000 0000            | uuuu uuuu                       |  |  |  |

| x05h/<br>x85h <sup>(1)</sup> | FSR0H      | Indirect Data                 | Memory Addr                                 | ess 0 High Poi   | nter            |               |             |       |       | 0000 0000            | 0000 0000                       |  |  |  |

| x06h/<br>x86h <sup>(1)</sup> | FSR1L      | Indirect Data                 | Indirect Data Memory Address 1 Low Pointer  |                  |                 |               |             |       |       |                      |                                 |  |  |  |

| x07h/<br>x87h <sup>(1)</sup> | FSR1H      | Indirect Data                 | Indirect Data Memory Address 1 High Pointer |                  |                 |               |             |       |       |                      |                                 |  |  |  |

| x08h/<br>x88h <sup>(1)</sup> | BSR        | —                             | <b>— — —</b> BSR<4:0>                       |                  |                 |               |             |       |       |                      |                                 |  |  |  |

| x09h/<br>x89h <sup>(1)</sup> | WREG       | Working Reg                   | Working Register                            |                  |                 |               |             |       |       |                      |                                 |  |  |  |

| x0Ah/<br>x8Ah <sup>(1)</sup> | PCLATH     | —                             | Write Buffer f                              | or the upper 7   | bits of the Pro | ogram Counte  | er          |       |       | -000 0000            | -000 0000                       |  |  |  |

| x0Bh/<br>x8Bh <sup>(1)</sup> | INTCON     | GIE                           | PEIE                                        | TMR0IE           | INTE            | IOCIE         | TMR0IF      | INTF  | IOCIF | 0000 0000            | 0000 0000                       |  |  |  |

| x0Ch/<br>x8Ch                | _          | Unimplement                   | Unimplemented                               |                  |                 |               |             |       |       |                      | _                               |  |  |  |

| x1Fh/<br>x9Fh                |            |                               |                                             |                  |                 |               |             |       |       |                      |                                 |  |  |  |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:legend: Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.$

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only.

**3:** PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

| System Chook     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GURE 5-7:                | INTERNAL OSCILLATOR SWITCH TIMING                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------|

| HEINTOSC/<br>MEDITOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                                                      |

| HFINTOSC/<br>MENTOSC       Orderstor Delay <sup>10</sup> Orderia dyna       Austria         LFINTOSC       #0       =0         IRCF <3:0>       #0       =0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          | LPINTOSC (PSCM and WOT distabled)                    |

| AMPRIPOSC       Contents Only ***       Restause         LFINTOSC       #************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                                                      |

| LFINTOSC       ≠0       =0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Cardinator Onlay <sup>63</sup> Science Synce Running |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LFINTOSC                 |                                                      |

| ARTINITOSC/ LETINITOSC (EIRHer PSCM or WDY enabled)<br>MEINITOSC<br>HFINTOSC<br>LETINTOSC<br>LETINTOSC<br>URCF <3:0> = 0 = 0<br>System Clock<br>URTRITOSC HEIRITOSC/MEINITOSC<br>URTRITOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IRCF <3:0>               | $\neq 0$ $= 0$                                       |

| NEFINITOSC/       2-cycles System         LFINTOSC       2-cycles System         IRCF <3.0>       ≠ 0         y= 0       = 0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System Clock             |                                                      |

| HFINTOSC/<br>LFINTOSC<br>LFINTOSC<br>IRCF <3:0> = 0 = 0<br>System Clock = 0 = 0<br>System Clock = 0 = 0<br>LFINTOSC == NFINTOSCARFINTOSC<br>LFINTOSC == NFINTOSCARFINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NENETOSO/                | LFINTOSC (ERDer POCM of WOT spabled)                 |

| LFINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HFINTOSC/                |                                                      |

| IRCF <3:0>       ≠ 0       = 0         System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | terran rana.             | l <u>iji 2-ovota konta</u> liji <u>Posasino</u>      |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LFINTOSC                 |                                                      |

| LEPHYTOSC HEINTOSC/MEINTOSC<br>LEPHYTOSC LIPHYTOSC turns off unterse WOY or Picose is enabled<br>Originator (newy <sup>Th</sup> ) provide Sync (<br>MEINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IRCF <3:0>               | $\neq 0$ $\chi = 0$                                  |

| LEINTOSC HEINTOSCIMETINTOSC<br>LEINTOSC LIPITOSC Linne off untere WOY or PLONE is enabled<br>URINTOSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                                                      |

| LFIRTOSC turns off unless WS7 or FS098 is anabied<br>UFIRTOSC Coddition Geory <sup>(1)</sup> (cryste Sanc )<br>MFIRTOSC Reprod<br>MFIRTOSC F<br>System Grook Codd Codd Codd Codd Codd Codd Codd C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System Clock             |                                                      |

| LFIRCHOSC turns off univers VCF or FSOM is anabied<br>LFIRCHOSC Lines off univers VCF or FSOM is anabied<br>Coldition Group <sup>(1)</sup> (-cycle Sanc )<br>Aurenting<br>MFENTOSC<br>MFENTOSC<br>IPCF <3:02 7 0<br>System Crock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |                                                      |

| LFIRTOSC turns off unless WS7 or FS098 is anabied<br>UFIRTOSC Coddition Geory <sup>(1)</sup> (cryste Sanc )<br>MFIRTOSC Reprod<br>MFIRTOSC F<br>System Grook Codd Codd Codd Codd Codd Codd Codd C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n ann na h-ann an an she |                                                      |

| Childhin Gook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 1922 I 1997            |                                                      |

| HEINTOBC/<br>MENTOSC<br>BECE <3:52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LEBITOSC                 |                                                      |

| MENTOSC         Image: Second sec |                          | California California Computer Sona 🕴 🦷 🥵 🥵 🥵        |

| System G>>>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                                                      |

| yuuuuuuun yuunuu yuuni yuuni yuuni yuuni yuuni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$2CE <3:0>              |                                                      |

| aamaamaamaamaamaamaamaamaamaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | System Crock             |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                                      |

| Nexa 1: Sen Table 5-1, "Capilizion Switching Dalays" for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                                                      |

#### 11.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 30.0 "Electrical Specifications**". If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### 11.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

EXAMPLE 11-1: DATA EEPROM READ

| BANKSEL | EEADRL  |       | i                      |

|---------|---------|-------|------------------------|

| MOVLW   | DATA_EE | _ADDR | i                      |

| MOVWF   | EEADRL  |       | ;Data Memory           |

|         |         |       | ;Address to read       |

| BCF     | EECON1, | CFGS  | ;Deselect Config space |

| BCF     | EECON1, | EEPGI | ;Point to DATA memory  |

| BSF     | EECON1, | RD    | ;EE Read               |

| MOVF    | EEDATL, | W     | ;W = EEDATL            |

|         |         |       |                        |

# Note: Data EEPROM can be read regardless of the setting of the CPD bit.

# 11.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set the WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### 11.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- · Power glitch

- · Software malfunction

#### 11.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit in the Configuration Word 1 (Register 5-1) to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

#### **REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER**

| U-0                                     | U-0 | R/W-0/0            | R/W-0/0                                               | R/W-0/0       | R/W-0/0            | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|-----|--------------------|-------------------------------------------------------|---------------|--------------------|---------|---------|

| _                                       | —   | IOCAN5             | IOCAN4                                                | IOCAN3        | IOCAN2             | IOCAN1  | IOCAN0  |

| bit 7                                   |     | •                  |                                                       |               |                    |         | bit 0   |

|                                         |     |                    |                                                       |               |                    |         |         |

| Legend:                                 |     |                    |                                                       |               |                    |         |         |

| R = Readable bit                        | :   | W = Writable bi    | t                                                     | U = Unimpleme | ented bit, read as | '0'     |         |

| u = Bit is unchanged x = Bit is unknown |     |                    | -n/n = Value at POR and BOR/Value at all other Resets |               |                    |         |         |

| '1' = Bit is set                        |     | '0' = Bit is clear | ed                                                    |               |                    |         |         |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

1 = Interrupt-on-change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin. Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

#### REGISTER 13-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER (PIC16(L)F1829 ONLY)

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | IOCBP<7:4>: Interrupt-on-Change PORTB Positive Edge Enable bits                                           |

|---------|-----------------------------------------------------------------------------------------------------------|

|         | 1 = Interrupt-on-change enabled on the pin for a positive going edge. Associated Status bit and interrupt |

|         | flag will be set upon detecting an edge.                                                                  |

|         | 0 = Interrupt-on-change disabled for the associated pin.                                                  |

| bit 3-0 | Unimplemented: Read as '0'                                                                                |

# 18.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- · Programmable input selection

- SR latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

#### 18.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT) (PIC16(L)F1829 only)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to Set or Reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 19.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically Set or Reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to Set or Reset the SR latch, respectively.

### 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 18.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

### 23.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

### 23.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

#### 23.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

#### 23.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDMSODIS bit in the MDSRC register.

#### 23.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

### 23.10 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

#### 23.11 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

#### 23.12 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

| Name     | Bit 7                  | Bit 6                  | Bit 5                           | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on<br>Page |  |  |

|----------|------------------------|------------------------|---------------------------------|-----------------------|---------|---------|---------|---------|---------------------|--|--|

| APFCON1  | —                      | —                      | SDO2SEL <sup>(2)</sup>          | SS2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL | 119                 |  |  |

| CCP1CON  | P1M<                   | 1:0> <b>(1)</b>        | DC1B                            | <1:0>                 |         | CCP1I   | M<3:0>  |         | 224                 |  |  |

| CCP2CON  | P2M<                   | 1:0> <b>(1)</b>        | DC2B                            | <1:0>                 |         | CCP2I   | M<3:0>  |         | 224                 |  |  |

| CCP3CON  | _                      | _                      | DC3B                            | <1:0>                 |         | CCP3I   | M<3:0>  |         | 224                 |  |  |

| CCP4CON  | _                      | —                      | DC4B                            | <1:0>                 |         | CCP4I   | M<3:0>  |         | 224                 |  |  |

| CCP1AS   | CCP1ASE                |                        | CCP1AS<2:0>                     |                       | PSS1A   | C<1:0>  | PSS1B   | D<1:0>  | 226                 |  |  |

| CCP2AS   | CCP2ASE                |                        | CCP2AS<2:0>                     |                       | PSS2A   | .C<1:0> | PSS2B   | D<1:0>  | 226                 |  |  |

| CCPTMRS  | C4TSE                  | EL<1:0>                | C3TSE                           | L<1:0>                | C2TSE   | L<1:0>  | C1TSE   | L<1:0>  | 225                 |  |  |

| INLVLA   | _                      | —                      | INLVLA5                         | INLVLA4               | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |  |  |

| INLVLC   | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5                         | INLVLC4               | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 135                 |  |  |

| INTCON   | GIE                    | PEIE                   | TMR0IE                          | INTE                  | IOCIE   | TMR0IF  | INTF    | IOCIF   | 87                  |  |  |

| PIE1     | TMR1GIE                | ADIE                   | RCIE                            | TXIE                  | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 88                  |  |  |

| PIE2     | OSFIE                  | C2IE                   | C1IE                            | EEIE                  | BCL1IE  | _       | _       | CCP2IE  | 89                  |  |  |

| PIE3     | —                      | _                      | CCP4IE                          | CCP3IE                | TMR6IE  | —       | TMR4IE  | —       | 90                  |  |  |

| PIR1     | TMR1GIF                | ADIF                   | RCIF                            | TXIF                  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 92                  |  |  |