Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1825-i-jq |

# **Peripheral Highlights (Continued)**

- · Data Signal Modulator Module:

- Selectable modulator and carrier sources

- · SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

PIC12(L)F1822/1840/PIC16(L)F182x/1847 Family Types

| 1 10 12(2): 102 |                  |                                 | <del>-/: :0-</del>     |                      |                      | ····· <i>y</i>  | .,            |             |                      |        |                               |                                                 |          |                      |     |

|-----------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|-------------------------------|-------------------------------------------------|----------|----------------------|-----|

| Device          | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O,8 <sub>(2)</sub> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> CTM/SPI) | ECCP (Full-Bridge)<br>ECCP (Half-Bridge)<br>CCP | SR Latch | Debug <sup>(1)</sup> | ХГР |

| PIC12(L)F1822   | (1)              | 2K                              | 256                    | 128                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC12(L)F1840   | (2)              | 4K                              | 256                    | 256                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1823   | (1)              | 2K                              | 256                    | 128                  | 12                   | 8               | 8             | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1824   | (3)              | 4K                              | 256                    | 256                  | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1825   | (4)              | 8K                              | 256                    | 1024                 | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1826   | (5)              | 2K                              | 256                    | 256                  | 16                   | 12              | 12            | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1827   | (5)              | 4K                              | 256                    | 384                  | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1828   | (3)              | 4K                              | 256                    | 256                  | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1829   | (4)              | 8K                              | 256                    | 1024                 | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1847   | (6)              | 8K                              | 256                    | 1024                 | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

3: DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

**TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)**

| Address             | Name   | Bit 7                          | Bit 6                                     | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|--------|--------------------------------|-------------------------------------------|------------------|-----------------|---------------|-------------|-------|---------|----------------------|---------------------------------|

| Bank 8              |        |                                |                                           |                  |                 |               |             |       |         |                      |                                 |

| 400h <sup>(1)</sup> | INDF0  | Addressing the (not a physical |                                           | es contents of   | FSR0H/FSR0      | )L to address | data memory | ,     |         | xxxx xxxx x          | xxx xxxx                        |

| 401h <sup>(1)</sup> | INDF1  | Addressing the (not a physical |                                           | es contents of   | FSR1H/FSR1      | IL to address | data memory | 1     |         | xxxx xxxx x          | xxx xxxx                        |

| 402h <sup>(1)</sup> | PCL    | Program Cou                    | inter (PC) Lea                            | st Significant E | Byte            |               |             |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(1)</sup> | STATUS |                                |                                           |                  |                 |               |             |       |         | 1 1000               | q quuu                          |

| 404h <sup>(1)</sup> | FSR0L  | Indirect Data                  | ndirect Data Memory Address 0 Low Pointer |                  |                 |               |             |       |         |                      | uuuu uuuu                       |

| 405h <sup>(1)</sup> | FSR0H  | Indirect Data                  | Memory Addr                               | ess 0 High Poi   | nter            |               |             |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(1)</sup> | FSR1L  | Indirect Data                  | ndirect Data Memory Address 1 Low Pointer |                  |                 |               |             |       |         |                      | uuuu uuuu                       |

| 407h <sup>(1)</sup> | FSR1H  | Indirect Data                  | direct Data Memory Address 1 High Pointer |                  |                 |               |             |       |         |                      | 0000 0000                       |

| 408h <sup>(1)</sup> | BSR    | _                              | _                                         | _                |                 |               | BSR<4:0>    |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(1)</sup> | WREG   | Working Reg                    | Norking Register                          |                  |                 |               |             |       |         |                      | uuuu uuuu                       |

| 40Ah <sup>(1)</sup> | PCLATH | _                              | Write Buffer f                            | or the upper 7   | bits of the Pro | ogram Counte  | er          |       |         | -000 0000 -          | 000 0000                        |

| 40Bh <sup>(1)</sup> | INTCON | GIE                            | PEIE                                      | TMR0IE           | INTE            | IOCIE         | TMR0IF      | INTF  | IOCIF   | 0000 0000            | 0000 0000                       |

| 40Ch                | _      | Unimplement                    | ted                                       |                  | _               | _             |             |       |         |                      |                                 |

| 40Dh                | _      | Unimplemented                  |                                           |                  |                 |               |             |       |         | _                    | _                               |

| 40Eh                | _      | Unimplement                    | Unimplemented                             |                  |                 |               |             |       |         |                      | _                               |

| 40Fh                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 410h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 411h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 412h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 413h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 414h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 415h                | TMR4   | Timer4 Modu                    | le Register                               |                  |                 |               |             |       |         | 0000 0000            | 0000 0000                       |

| 416h                | PR4    | Timer4 Perio                   | d Register                                |                  |                 |               |             |       |         | 1111 1111            | 1111 1111                       |

| 417h                | T4CON  | _                              |                                           | T4OUTF           | 'S<3:0>         |               | TMR40N      | T4CKF | PS<1:0> | -000 0000 -          | 000 0000                        |

| 418h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 419h                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         | _                    | _                               |

| 41Ah                | _      | Unimplement                    | Unimplemented                             |                  |                 |               |             |       |         | _                    | _                               |

| 41Bh                | _      | Unimplement                    | Unimplemented                             |                  |                 |               |             |       |         | _                    | _                               |

| 41Ch                | TMR6   | Timer6 Modu                    | le Register                               |                  |                 |               |             |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                | PR6    | Timer6 Perio                   | d Register                                |                  |                 |               |             |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                | T6CON  | _                              |                                           | T6OUTF           | 'S<3:0>         |               | TMR6ON      | T6CKF | PS<1:0> | -000 0000 -          | 000 0000                        |

| 41Fh                | _      | Unimplement                    | ted                                       |                  |                 |               |             |       |         |                      | _                               |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only.

3: PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

### 6.5 Reference Clock Control Register

#### REGISTER 6-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1     | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 |

|---------|---------|---------|-------------|---------|---------|--------------|---------|

| CLKREN  | CLKROE  | CLKRSLR | CLKRDC<1:0> |         | (       | CLKRDIV<2:0> | •       |

| bit 7   |         |         |             |         |         |              | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **CLKREN:** Reference Clock Module Enable bit 1 = Reference Clock module is enabled 0 = Reference Clock module is disabled bit 6 **CLKROE**: Reference Clock Output Enable bit<sup>(3)</sup> 1 = Reference Clock output is enabled on CLKR pin 0 = Reference Clock output disabled on CLKR pin CLKRSLR: Reference Clock Slew Rate Control Limiting Enable bit bit 5 1 = Slew Rate limiting is enabled 0 = Slew Rate limiting is disabled bit 4-3 CLKRDC<1:0>: Reference Clock Duty Cycle bits 11 = Clock outputs duty cycle of 75% 10 = Clock outputs duty cycle of 50% 01 = Clock outputs duty cycle of 25% 00 = Clock outputs duty cycle of 0% bit 2-0 CLKRDIV<2:0> Reference Clock Divider bits 111 = Base clock value divided by 128 110 = Base clock value divided by 64

111 = Base clock value divided by 128 110 = Base clock value divided by 64 101 = Base clock value divided by 32 100 = Base clock value divided by 16 011 = Base clock value divided by 8 010 = Base clock value divided by 4 001 = Base clock value divided by 2<sup>(1)</sup> 000 = Base clock value<sup>(2)</sup>

Note 1: In this mode, the 25% and 75% duty cycle accuracy will be dependent on the source clock duty cycle.

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- 3: To route CLKR to pin, CLKOUTEN of Configuration Word 1 = 1 is required. CLKOUTEN of Configuration Word 1 = 0 will result in Fosc/4. See Section 6.3 "Conflicts with the CLKR Pin" for details.

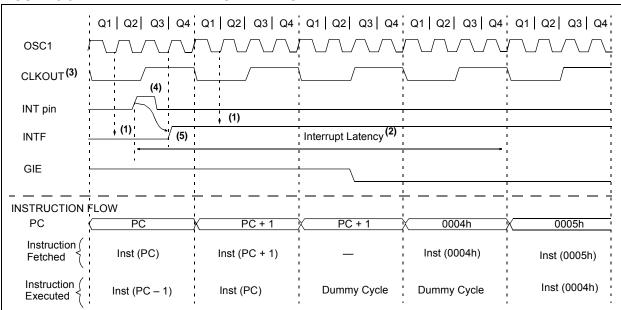

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 TcY. Synchronous latency = 3-4 TcY, where TcY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT not available in all oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 30.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### REGISTER 12-7: WPUA: WEAK PULL-UP PORTA REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(1,2)</sup>

1 = Pull-up enabled 0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for port reads and interrupt-on-change 0 = TTL input used for port reads and interrupt-on-change

TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |  |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>      |  |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>      |  |  |  |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The FRC source has a typical TAD time of 1.6  $\mu s$  for VDD.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock Fosc. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

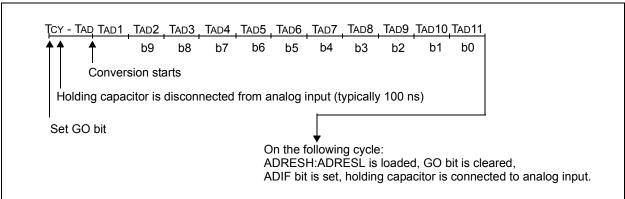

### FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

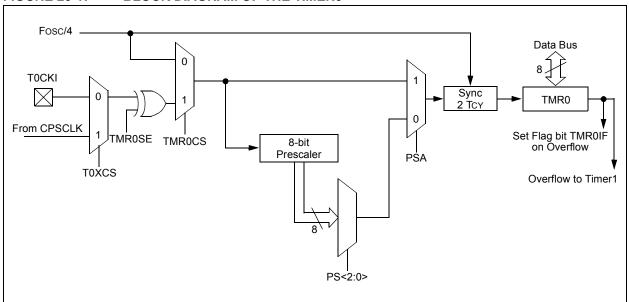

### 20.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

### 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note:

The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION REG register.

### FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

### 20.2 Option and Timer0 Control Register

### **REGISTER 20-1: OPTION REG: OPTION REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 WPUEN: Weak Pull-up Enable bit

1 = All weak pull-ups are disabled (except MCLR, if it is enabled)

0 = Weak pull-ups are enabled by individual WPUx latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TMR0CS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 TMR0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is not assigned to the Timer0 module

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| Bit Value | Timer0 Rate |

|-----------|-------------|

| 000       | 1:2         |

| 001       | 1:4         |

| 010       | 1:8         |

| 011       | 1:16        |

| 100       | 1:32        |

| 101       | 1:64        |

| 110       | 1 : 128     |

| 111       | 1:256       |

### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name                        | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3       | Bit 2   | Bit 1      | Bit 0   | Register<br>on Page |

|-----------------------------|-------|--------|---------|---------|-------------|---------|------------|---------|---------------------|

| CPSCON0                     | CPSON | CPSRM  | _       | _       | CPSRN       | IG<1:0> | CPSOUT     | T0xCS   | 315                 |

| FVRCON                      | FVREN | FVRRDY | TSEN    | TSRNG   | CDAFVR<1:0> |         | ADFVR<1:0> |         | 142                 |

| INLVLA                      | _     | _      | INLVLA5 | INLVLA4 | INLVLA3     | INLVLA2 | INLVLA1    | INLVLA0 | 124                 |

| INTCON                      | GIE   | PEIE   | TMR0IE  | INTE    | IOCIE       | TMR0IF  | INTF       | IOCIF   | 87                  |

| OPTION_REG                  | WPUEN | INTEDG | TMR0CS  | TMR0SE  | PSA         |         | PS<2:0>    |         | 176                 |

| TMR0 Timer0 Module Register |       |        |         |         |             |         |            |         | 174*                |

| TRISA                       | _     | _      | TRISA5  | TRISA4  | TRISA3      | TRISA2  | TRISA1     | TRISA0  | 122                 |

**Legend:** — Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

<sup>\*</sup> Page provides register information.

# 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                     |

|-------|------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                        |

| 01    | Overflow of Timer0 (TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT (optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT (optionally Timer1 synchronized output) |

### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 Gate Control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |  |

# 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 21-6 for timing details.

### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 gate event interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 24.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 24-4.

# **EQUATION 24-4: PWM RESOLUTION**

Resolution =

$$\frac{log[4(PRx + I)]}{log(2)}$$

bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 24-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

# TABLE 24-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 24-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### REGISTER 25-3: SSPxCON2: SSPx CONTROL REGISTER 2

| R/W-0/0 | R-0/0   | R/W-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/W/HS-0/0 |

|---------|---------|---------|------------|------------|------------|------------|------------|

| GCEN    | ACKSTAT | ACKDT   | ACKEN      | RCEN       | PEN        | RSEN       | SEN        |

| bit 7   |         |         |            |            |            |            | bit 0      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HC = Cleared by hardware S = User set

bit 7 **GCEN:** General Call Enable bit (in I<sup>2</sup>C Slave mode only)

1 = Enable interrupt when a general call address (0x00 or 00h) is received in the SSPxSR

0 = General call address disabled

bit 6 **ACKSTAT:** Acknowledge Status bit (in I<sup>2</sup>C mode only)

1 = Acknowledge was not received0 = Acknowledge was received

bit 5 **ACKDT:** Acknowledge Data bit (in I<sup>2</sup>C mode only)

In Receive mode:

Value transmitted when the user initiates an Acknowledge sequence at the end of a receive

1 = Not Acknowledge0 = Acknowledge

bit 4 **ACKEN:** Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only)

In Master Receive mode:

1 = Initiate Acknowledge sequence on SDAx and SCLx pins, and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence Idle

bit 3 **RCEN:** Receive Enable bit (in I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for I<sup>2</sup>C

0 = Receive Idle

bit 2 **PEN:** Stop Condition Enable bit (in I<sup>2</sup>C Master mode only)

SCKx Release Control:

1 = Initiate Stop condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Stop condition Idle

bit 1 **RSEN:** Repeated Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)

1 = Initiate Repeated Start condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Repeated Start condition Idle

bit 0 SEN: Start Condition Enable/Stretch Enable bit

In Master mode:

1 = Initiate Start condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Start condition Idle

In Slave mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)

0 = Clock stretching is disabled

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

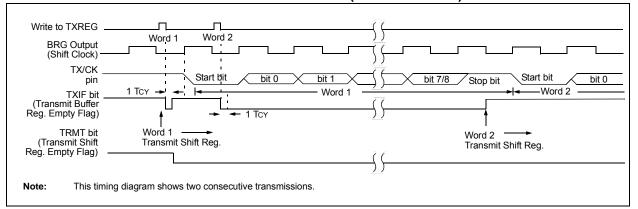

# FIGURE 26-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

TABLE 26-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name                  | Bit 7                  | Bit 6                  | Bit 5                 | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|-----------------------|------------------------|------------------------|-----------------------|---------|---------|---------|---------|---------|------------------|

| APFCON0               | RXDTSEL                | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup> |         | T1GSEL  | TXCKSEL | _       | _       | 118              |

| BAUDCON               | ABDOVF                 | RCIDL                  | -                     | SCKP    | BRG16   | _       | WUE     | ABDEN   | 292              |

| INLVLA <sup>(3)</sup> | _                      | _                      | INLVLA5               | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124              |

| INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6                | INLVLB5               | INLVLB4 | 1       | _       | 1       | _       | 129              |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5               | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 135              |

| INTCON                | GIE                    | PEIE                   | TMR0IE                | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF   | 87               |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE                  | TXIE    | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 88               |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF                  | TXIF    | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 92               |

| RCSTA                 | SPEN                   | RX9                    | SREN                  | CREN    | ADDEN   | FERR    | OERR    | RX9D    | 291              |

| SPBRGL                |                        |                        |                       | SPBRG   | i<7:0>  |         |         |         | 293*             |

| SPBRGH                |                        |                        |                       | SPBRG   | <15:8>  |         |         |         | 293*             |

| TRISA                 | _                      | -                      | TRISA5                | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122              |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5                | TRISB4  | _       | _       | _       | _       | 128              |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5                | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 133              |

| TXREG                 | EUSART Tra             | nsmit Data Re          | gister                |         |         |         |         |         | 283              |

| TXSTA                 | CSRC                   | TX9                    | TXEN                  | SYNC    | SENDB   | BRGH    | TRMT    | TX9D    | 290              |

**Legend:** — Unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

Note 1: PIC16(L)F1829 only. 2: PIC16(L)F1825 only.

3: Unshaded cells apply to PIC16(L)F1825 only.