### Microchip Technology - PIC16LF1825-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1825-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                               | Function | Input<br>Type | Output<br>Type | Description                         |

|----------------------------------------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------|

| RC3/AN7/CPS7/C12IN3-/                                                                              | RC3      | TTL           | CMOS           | General purpose I/O.                |

| P2A <sup>(1,2)</sup> /CCP2 <sup>(1,2)</sup> /P1C <sup>(1,2)</sup> /<br>SS1 <sup>(1,2)</sup> /MDMIN | AN7      | AN            | —              | A/D Channel 7 input.                |

| 551 <sup>···-</sup> /MDMIN                                                                         | CPS7     | AN            | _              | Capacitive sensing input 7.         |

|                                                                                                    | C12IN3-  | AN            | —              | Comparator C1 or C2 negative input. |

|                                                                                                    | P2A      | _             | CMOS           | PWM output.                         |

|                                                                                                    | CCP2     | AN            | _              | Capture/Compare/PWM2.               |

|                                                                                                    | P1C      | _             | CMOS           | PWM output.                         |

|                                                                                                    | SS1      | ST            | _              | Slave Select input.                 |

|                                                                                                    | MDMIN    | ST            | —              | Modulator source input.             |

| RC4/C2OUT/SRNQ/P1B/TX <sup>(1,2)</sup> /                                                           | RC4      | TTL           | CMOS           | General purpose I/O.                |

| CK <sup>(1,2)</sup> /MDOUT                                                                         | C2OUT    | _             | CMOS           | Comparator C2 output.               |

|                                                                                                    | SRNQ     | _             | CMOS           | SR Latch inverting output.          |

|                                                                                                    | P1B      | _             | CMOS           | PWM output.                         |

|                                                                                                    | TX       | _             | CMOS           | USART asynchronous transmit.        |

|                                                                                                    | СК       | ST            | CMOS           | USART synchronous clock.            |

|                                                                                                    | MDOUT    | _             | CMOS           | Modulator output.                   |

| RC5/P1A/CCP1/DT <sup>(1,2)</sup> /RX <sup>(1,2)</sup> /                                            | RC5      | TTL           | CMOS           | General purpose I/O.                |

| MDCIN2                                                                                             | P1A      | _             | CMOS           | PWM output.                         |

|                                                                                                    | CCP1     | ST            | CMOS           | Capture/Compare/PWM1.               |

|                                                                                                    | RX       | ST            | _              | USART asynchronous input.           |

|                                                                                                    | DT       | ST            | CMOS           | USART synchronous data.             |

|                                                                                                    | MDCIN2   | ST            | —              | Modulator Carrier Input 2.          |

| Vdd                                                                                                | Vdd      | Power         | —              | Positive supply.                    |

| Vss                                                                                                | Vss      | Power         | —              | Ground reference.                   |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

**2:** Default function location.

| Name                                                               | Function | Input<br>Type    | Output<br>Type | Description                            |

|--------------------------------------------------------------------|----------|------------------|----------------|----------------------------------------|

| RA5/CLKIN/OSC1/T1OSI/                                              | RA5      | TTL              | CMOS           | General purpose I/O.                   |

| SD02 <sup>(1)</sup> /T1CKI/P2A <sup>(1)</sup> /CCP2 <sup>(1)</sup> | CLKIN    | CMOS             | —              | External clock input (EC mode).        |

|                                                                    | OSC1     | XTAL             | —              | Crystal/Resonator (LP, XT, HS modes).  |

|                                                                    | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.          |

|                                                                    | SD02     |                  | CMOS           | SPI data output 2.                     |

|                                                                    | T1CKI    | ST               | —              | Timer1 clock input.                    |

|                                                                    | P2A      | _                | CMOS           | PWM output.                            |

|                                                                    | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                  |

| RB4/AN10/CPS10/SDA1/SDI1                                           | RB4      | TTL              | CMOS           | General purpose I/O.                   |

|                                                                    | AN10     | AN               | _              | A/D Channel 10 input.                  |

|                                                                    | CPS10    | AN               | —              | Capacitive sensing input 10.           |

|                                                                    | SDA1     | l <sup>2</sup> C | OD             | I <sup>2</sup> C™ data input/output.   |

|                                                                    | SDI1     | CMOS             | —              | SPI data input.                        |

| RB5/AN11/CPS11/RX <sup>(1,2)</sup> /                               | RB5      | TTL              | CMOS           | General purpose I/O.                   |

| DT <sup>(1,2)</sup> /SDA2/SDI2                                     | AN11     | AN               | —              | A/D Channel 11 input.                  |

|                                                                    | CPS11    | AN               | —              | Capacitive sensing input 11.           |

|                                                                    | RX       | ST               | —              | USART asynchronous input.              |

|                                                                    | DT       | ST               | CMOS           | USART synchronous data.                |

|                                                                    | SDA2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output 2.  |

|                                                                    | SDI2     | CMOS             | —              | SPI data input 2.                      |

| RB6/SCL1/SCK1                                                      | RB6      | TTL              | CMOS           | General purpose I/O.                   |

|                                                                    | SCL1     | l <sup>2</sup> C | OD             | I <sup>2</sup> C <sup>™</sup> clock 1. |

|                                                                    | SCK1     | ST               | CMOS           | SPI clock 1.                           |

| RB7/TX <sup>(1,2)</sup> /CK <sup>(1,2)</sup> /SCL2/SCK2            | RB7      | TTL              | CMOS           | General purpose I/O.                   |

|                                                                    | ΤX       |                  | CMOS           | USART asynchronous transmit.           |

|                                                                    | СК       | ST               | CMOS           | USART synchronous clock.               |

|                                                                    | SCL2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C <sup>™</sup> clock 2. |

|                                                                    | SCK2     | ST               | CMOS           | SPI clock 2.                           |

| RC0/AN4/CPS4/C2IN+/P1D <sup>(1)</sup> /                            | RC0      | TTL              | CMOS           | General purpose I/O.                   |

| SS2 <sup>(1,2)</sup>                                               | AN4      | AN               | —              | A/D Channel 4 input.                   |

|                                                                    | CPS4     | AN               |                | Capacitive sensing input 4.            |

|                                                                    | C2IN+    | AN               |                | Comparator C2 positive input.          |

|                                                                    | P1D      |                  | CMOS           | PWM output.                            |

|                                                                    | SS2      | ST               | —              | Slave Select input 2.                  |

| RC1/AN5/CPS5/C12IN1-/P1C(1)/                                       | RC1      | TTL              | CMOS           | General purpose I/O.                   |

| SD02 <sup>(1,2)</sup>                                              | AN5      | AN               | —              | A/D Channel 5 input.                   |

|                                                                    | CPS5     | AN               | —              | Capacitive sensing input 5.            |

|                                                                    | C12IN1-  | AN               | —              | Comparator C1 or C2 negative input.    |

|                                                                    | P1C      | —                | CMOS           | PWM output.                            |

|                                                                    | SDO2     | _                | CMOS           | SPI data output 2.                     |

### TABLE 1-3: PIC16(L)F1829 PINOUT DESCRIPTION (CONTINUED)

Legend:AN= Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal

ו־C י™ = Schmitt Tr levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Default function location.

### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4       | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on Page |

|---------|--------|--------|---------|-------------|-------|-------|------------|-------|---------------------|

| CLKRCON | CLKREN | CLKROE | CLKRSLR | CLKRDC<1:0> |       | C     | LKRDIV<2:0 | >     | 72                  |

|         |        |        |         |             |       |       |            |       |                     |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2        | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|-----------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREI           | N<1:0>  | CPD     | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | <1:0> FOSC<2:0> |         |         | 48                  |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

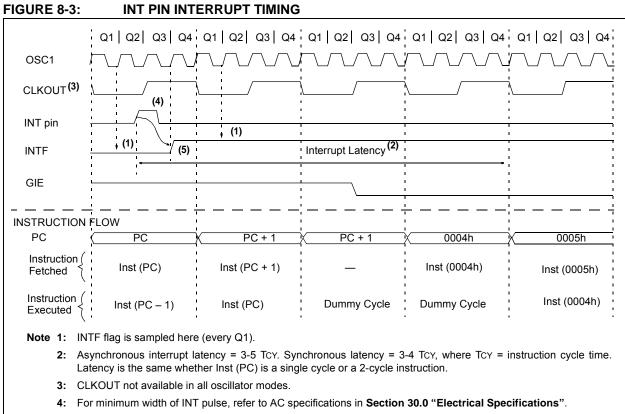

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

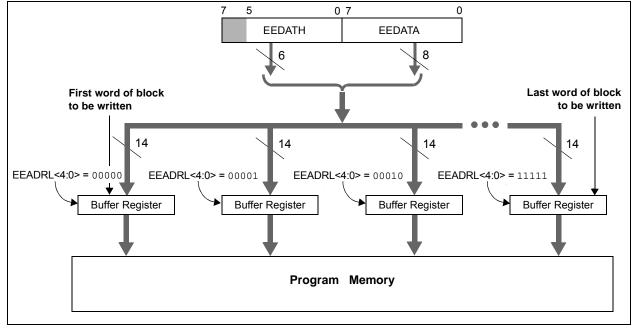

### 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EED-ATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the write operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the write takes place (i.e., the last word of the block write). This is not Sleep mode as the clocks and peripherals will

continue to run. The processor does not stall when LWLO = 1, loading the write latches. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

### 12.4 PORTC Registers

PORTC is a 6-bit wide (8-bit wide for PIC16(L)F1829), bidirectional port. The corresponding data direction register is TRISC (Register 12-16). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-2 shows how to initialize a port.

Reading the PORTC register (Register 12-15) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-16) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLC register (Register 12-20) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Character-istics: PIC16(L)F1825/9-I/E" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 12.4.1 ANSELC REGISTER

The ANSELC register (Register 12-18) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELC bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

| R/W-0/0                 | R-0/0                                                                                             | R/W-0/0                                      | R/W-0/0         | U-0             | R/W-1/1           | R/W-0/0         | R/W-0/0          |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------|-------------------|-----------------|------------------|--|--|--|--|

| CxON                    | CxOUT                                                                                             | CxOE                                         | CxPOL           | _               | CxSP              | CxHYS           | CxSYNC           |  |  |  |  |

| bit 7                   |                                                                                                   |                                              |                 |                 |                   |                 | bit 0            |  |  |  |  |

| Levend                  |                                                                                                   |                                              |                 |                 |                   |                 |                  |  |  |  |  |

| Legend:<br>R = Readable | , hit                                                                                             | W = Writable                                 | hit             | II – Unimple    | emented bit, read | d ac 'O'        |                  |  |  |  |  |

| u = Bit is unc          |                                                                                                   | x = Bit is unkr                              |                 | •               | at POR and BC     |                 | other Pesets     |  |  |  |  |

| '1' = Bit is set        | •                                                                                                 | 0' = Bit is cle                              |                 |                 |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   |                                              | urcu            |                 |                   |                 |                  |  |  |  |  |

| bit 7                   | CxON: Com                                                                                         | parator Enable                               | bit             |                 |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   | ator is enabled                              |                 |                 |                   |                 |                  |  |  |  |  |

|                         | 0 = Compara                                                                                       | ator is disabled                             | and consumes    | s no active pov | ver               |                 |                  |  |  |  |  |

| bit 6                   |                                                                                                   | nparator Output                              |                 |                 |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   | (inverted polarity):                         |                 |                 |                   |                 |                  |  |  |  |  |

|                         | -                                                                                                 | 1 = CxVP < CxVN $0 = CxVP > CxVN$            |                 |                 |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   | If CxPOL = 0 (non-inverted polarity):        |                 |                 |                   |                 |                  |  |  |  |  |

|                         | 1 = CxVP >                                                                                        | CxVN                                         |                 |                 |                   |                 |                  |  |  |  |  |

|                         | 0 = CxVP <                                                                                        | -                                            |                 |                 |                   |                 |                  |  |  |  |  |

| bit 5                   |                                                                                                   | parator Output I                             |                 |                 |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   |                                              |                 | Requires that   | the associated T  | RIS bit be clea | ared to actually |  |  |  |  |

|                         | drive the pin. Not affected by CxON.<br>0 = CxOUT is internal only                                |                                              |                 |                 |                   |                 |                  |  |  |  |  |

| bit 4                   |                                                                                                   | nparator Output                              | Polarity Sele   | ct bit          |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   | ator output is inv                           | •               |                 |                   |                 |                  |  |  |  |  |

|                         | 0 = Compara                                                                                       | ator output is no                            | t inverted      |                 |                   |                 |                  |  |  |  |  |

| bit 3                   | Unimpleme                                                                                         | nted: Read as '                              | 0'              |                 |                   |                 |                  |  |  |  |  |

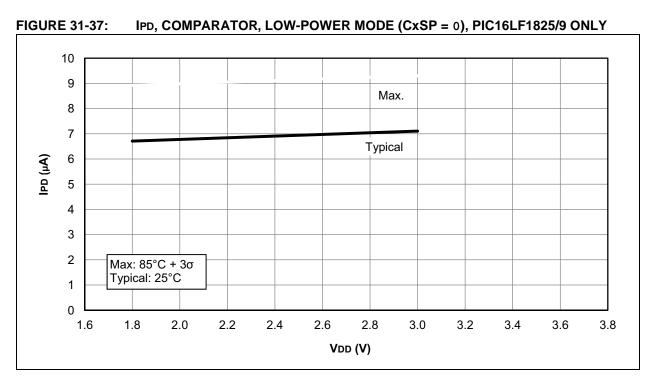

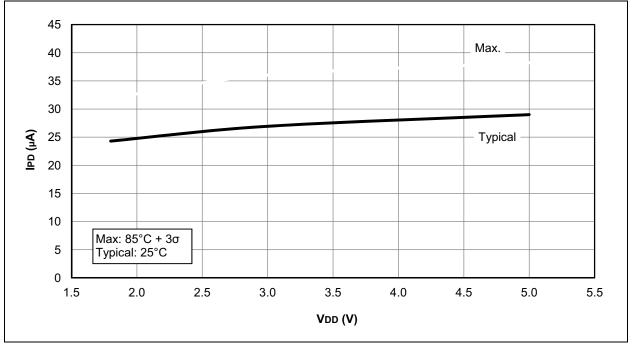

| bit 2                   | -                                                                                                 | parator Speed/F                              |                 |                 |                   |                 |                  |  |  |  |  |

|                         | 1 = Comparator operates in normal power, higher speed mode                                        |                                              |                 |                 |                   |                 |                  |  |  |  |  |

| 1.11.4                  |                                                                                                   | arator operates in low-power, low-speed mode |                 |                 |                   |                 |                  |  |  |  |  |

| bit 1                   |                                                                                                   | CxHYS: Comparator Hysteresis Enable bit      |                 |                 |                   |                 |                  |  |  |  |  |

|                         | <ul> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul> |                                              |                 |                 |                   |                 |                  |  |  |  |  |

| bit 0                   | -                                                                                                 | omparator Outp                               |                 | us Mode bit     |                   |                 |                  |  |  |  |  |

|                         |                                                                                                   |                                              | -               |                 | ronous to chang   | ges on Timer1   | clock source     |  |  |  |  |

|                         | Output u                                                                                          | updated on the                               | falling edge of | Timer1 clock    | source.           | -               |                  |  |  |  |  |

|                         | 0 = Compar                                                                                        | ator output to T                             | imer1 and I/O   | pin is asynchr  | onous.            |                 |                  |  |  |  |  |

### REGISTER 19-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| Name    | Bit 7          | Bit 6                                                                      | Bit 5            | Bit 4             | Bit 3                   | Bit 2   | Bit 1      | Bit 0   | Register on<br>Page |

|---------|----------------|----------------------------------------------------------------------------|------------------|-------------------|-------------------------|---------|------------|---------|---------------------|

| ANSELA  | _              | —                                                                          | _                | ANSA4             | —                       | ANSA2   | ANSA1      | ANSA0   | 123                 |

| CCP1CON | P1M•           | <1:0>                                                                      | DC1B             | <1:0>             |                         | CCP1N   | 1<3:0>     |         | 224                 |

| CCP2CON | P2M            | <1:0>                                                                      | DC2B             | <1:0>             |                         | CCP2N   | 1<3:0>     |         | 224                 |

| INLVLA  | _              | _                                                                          | INLVLA5          | INLVLA4           | INLVLA3                 | INLVLA2 | INLVLA1    | INLVLA0 | 124                 |

| INTCON  | GIE            | PEIE                                                                       | TMR0IE           | INTE              | IOCIE                   | TMR0IF  | INTF       | IOCIF   | 87                  |

| PIE1    | TMR1GIE        | ADIE                                                                       | RCIE             | TXIE              | SSP1IE                  | CCP1IE  | TMR2IE     | TMR1IE  | 88                  |

| PIR1    | TMR1GIF        | ADIF                                                                       | RCIF             | TXIF              | SSP1IF                  | CCP1IF  | TMR2IF     | TMR1IF  | 92                  |

| TMR1H   | Holding Regist | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                  |                   |                         |         |            |         | 181*                |

| TMR1L   | Holding Regist | er for the Least                                                           | Significant Byte | e of the 16-bit ⊺ | FMR1 Register           |         |            |         | 181*                |

| TRISA   | —              | —                                                                          | TRISA5           | TRISA4            | TRISA3                  | TRISA2  | TRISA1     | TRISA0  | 122                 |

| T1CON   | TMR1C          | S<1:0>                                                                     | T1CKP            | S<1:0>            | T1OSCEN                 | T1SYNC  | _          | TMR10N  | 185                 |

| T1GCON  | TMR1GE         | T1GPOL                                                                     | T1GTM            | T1GSPM            | T <u>1GGO</u> /<br>DONE | T1GVAL  | T1GSS<1:0> |         | 186                 |

Unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information. Legend:

| R/W-x/u                 | R/W-x/u                                   | R/W-x/u                                                                                  | U-0          | R/W-x/u            | R/W-x/u           | R/W-x/u          | R/W-x/u         |  |  |  |

|-------------------------|-------------------------------------------|------------------------------------------------------------------------------------------|--------------|--------------------|-------------------|------------------|-----------------|--|--|--|

| MDCHODIS                | MDCHPOL                                   | MDCHSYNC                                                                                 | _            |                    | MDCH              | 1<3:0>           |                 |  |  |  |

| bit 7                   |                                           |                                                                                          |              |                    |                   |                  | bit 0           |  |  |  |

| Logondi                 |                                           |                                                                                          |              |                    |                   |                  |                 |  |  |  |

| Legend:<br>R = Readable | hit                                       | W = Writable b                                                                           | i+           | II = I Inimpler    | nented bit, read  | l as 'N'         |                 |  |  |  |

| u = Bit is unch         |                                           | x = Bit is unknown                                                                       | •            |                    | at POR and BO     |                  | othor Posots    |  |  |  |

|                         | angeu                                     | '0' = Bit is clear                                                                       |              |                    | at FOR and BO     |                  |                 |  |  |  |

| '1' = Bit is set        |                                           | 0 = Bit is clear                                                                         | ea           |                    |                   |                  |                 |  |  |  |

| bit 7                   | MDCHODIS                                  | Modulator High                                                                           | Carrier Ou   | tout Disable bit   |                   |                  |                 |  |  |  |

|                         |                                           | signal driving the                                                                       |              | •                  | ted by MDCH<      | 3·0>) is disable | ed              |  |  |  |

|                         |                                           | signal driving the                                                                       |              |                    |                   |                  |                 |  |  |  |

| bit 6                   | MDCHPOL:                                  | Modulator High C                                                                         | Carrier Pola | arity Select bit   |                   |                  |                 |  |  |  |

|                         | 1 = Selected                              | d high carrier sigr                                                                      | al is invert | ed                 |                   |                  |                 |  |  |  |

|                         | 0 = Selected                              | d high carrier sign                                                                      | al is not in | verted             |                   |                  |                 |  |  |  |

| bit 5                   | MDCHSYNC                                  | : Modulator High                                                                         | Carrier Sy   | nchronization E    | nable bit         |                  |                 |  |  |  |

|                         |                                           | or waits for a falli                                                                     | ing edge o   | n the high time o  | carrier signal be | efore allowing a | a switch to the |  |  |  |

|                         | low time                                  |                                                                                          |              |                    |                   | (1)              |                 |  |  |  |

|                         |                                           | or Output is not s                                                                       |              | ed to the high tim | ie carrier signal | (')              |                 |  |  |  |

| bit 4                   | -                                         | nted: Read as '0'                                                                        |              |                    | (4)               |                  |                 |  |  |  |

| bit 3-0                 |                                           | Modulator Data                                                                           | •            |                    | (1)               |                  |                 |  |  |  |

|                         | 1111 = Res                                | erved. No chann                                                                          | nel connect  | ted.               |                   |                  |                 |  |  |  |

|                         | •                                         |                                                                                          |              |                    |                   |                  |                 |  |  |  |

|                         | •                                         |                                                                                          |              |                    |                   |                  |                 |  |  |  |

|                         | 1000 = Res                                | erved. No chanr                                                                          | nel connect  | ted.               |                   |                  |                 |  |  |  |

|                         |                                           | 0111 = CCP4 output (PWM Output mode only)                                                |              |                    |                   |                  |                 |  |  |  |

|                         | 0110 = CCP3 output (PWM Output mode only) |                                                                                          |              |                    |                   |                  |                 |  |  |  |

|                         |                                           | 0101 = CCP2 output (PWM Output mode only)                                                |              |                    |                   |                  |                 |  |  |  |

|                         |                                           | 0100 = CCP1 output (PWM Output mode only)<br>0011 = Reference Clock module signal (CLKR) |              |                    |                   |                  |                 |  |  |  |

|                         |                                           | CIN2 port pin                                                                            | uule signai  |                    |                   |                  |                 |  |  |  |

|                         |                                           | CIN1 port pin                                                                            |              |                    |                   |                  |                 |  |  |  |

|                         | 0000 = Vss                                |                                                                                          |              |                    |                   |                  |                 |  |  |  |

| Note 1. Nar             | rowed corrier                             | nulse widths or si                                                                       |              | cour in the signs  | l stroom if the   | arriar is not a  | nobronizod      |  |  |  |

### REGISTER 23-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

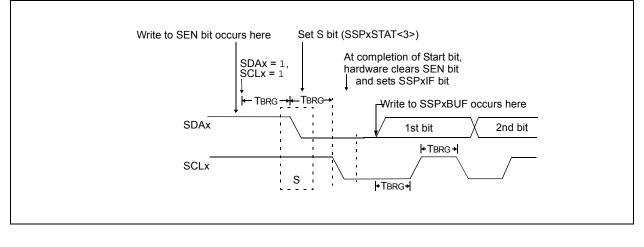

### 25.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 25-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SDAx bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

### FIGURE 25-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- 2: The Philips I<sup>2</sup>C<sup>™</sup> Specification states that a bus collision cannot occur on a Start.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                             |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                               |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                      |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                       |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1', the<br>result is placed back in register 'f'. |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |

## PIC16(L)F1825/9

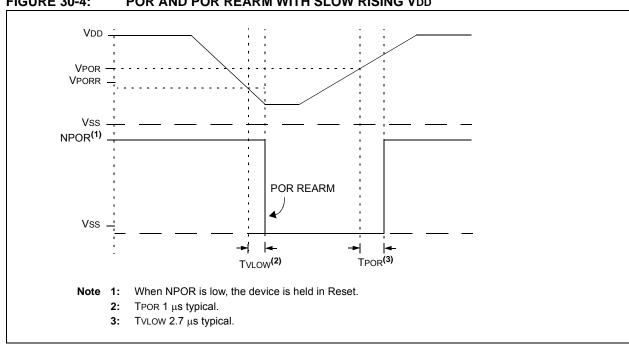

#### FIGURE 30-4: POR AND POR REARM WITH SLOW RISING VDD

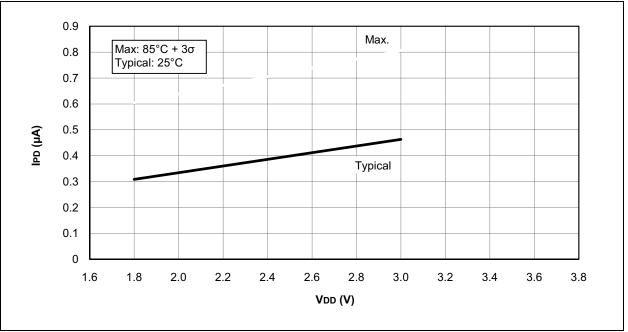

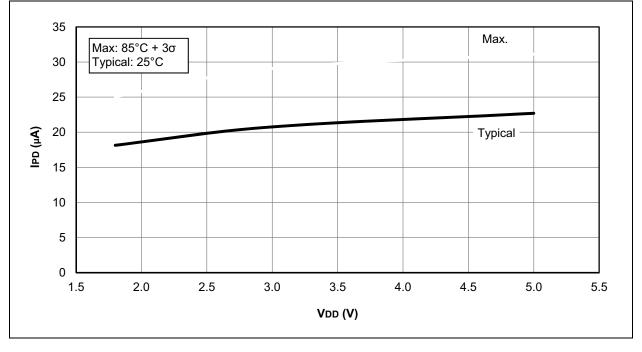

### 30.3 DC Characteristics: PIC16(L)F1825/9-I/E (Power-Down)

| PIC16LF1825/9<br>PIC16F1825/9 |                         | Operating temperature |      |       | ditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended<br>ditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |                                    |                                                    |

|-------------------------------|-------------------------|-----------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------|----------------------------------------------------|

|                               |                         |                       |      |       |                                                                                                                                                                                                                                                                                                          |       |                                    | Param                                              |

| No.                           | Device Characteristics  | WIIII.                | Тур† | +85°C | +125°C                                                                                                                                                                                                                                                                                                   | Units | VDD                                | Note                                               |

|                               | Power-down Base Current | (IPD) <sup>(2)</sup>  |      | -     |                                                                                                                                                                                                                                                                                                          |       |                                    | -                                                  |

| D022                          |                         |                       | 0.02 | 1.0   | 2.7                                                                                                                                                                                                                                                                                                      | μA    | 1.8                                | WDT, BOR, FVR, and T1OSC                           |

|                               |                         | —                     | 0.05 | 1.75  | 3.3                                                                                                                                                                                                                                                                                                      | μA    | 3.0                                | disabled, all Peripherals Inactive                 |

| D022                          |                         |                       | 17.8 | 37    | 44                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | WDT, BOR, FVR, and T1OSC                           |

|                               |                         | 20.5                  | 42   | 48    | μA                                                                                                                                                                                                                                                                                                       | 3.0   | disabled, all Peripherals Inactive |                                                    |

|                               |                         | —                     | 21.7 | 45    | 65                                                                                                                                                                                                                                                                                                       | μA    | 5.0                                |                                                    |

| D023                          |                         |                       | 0.3  | 1.5   | 3.0                                                                                                                                                                                                                                                                                                      | μA    | 1.8                                | LPWDT Current (Note 1)                             |

|                               |                         | —                     | 0.5  | 2.0   | 3.7                                                                                                                                                                                                                                                                                                      | μA    | 3.0                                |                                                    |

| D023                          |                         |                       | 18   | 38    | 44                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | LPWDT Current (Note 1)                             |

|                               |                         | 20.9                  | 43   | 48    | μA                                                                                                                                                                                                                                                                                                       | 3.0   |                                    |                                                    |

|                               |                         | —                     | 22.1 | 48    | 65                                                                                                                                                                                                                                                                                                       | μA    | 5.0                                |                                                    |

| D023A                         |                         |                       | 12.6 | 22    | 25                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | FVR current (Note 1)                               |

|                               |                         | —                     | 12.8 | 24    | 27                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                |                                                    |

| D023A                         |                         |                       | 32.7 | 62    | 65                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | FVR current (Note 1)                               |

|                               |                         |                       | 39   | 72    | 75                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                |                                                    |

|                               |                         | —                     | 69   | 115   | 120                                                                                                                                                                                                                                                                                                      | μA    | 5.0                                |                                                    |

| D024                          |                         | —                     | 7    | 14    | 16                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                | BOR Current (Note 1)                               |

| D024                          |                         | —                     | 24   | 47    | 50                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                | BOR Current (Note 1)                               |

|                               |                         | —                     | 27   | 55    | 70                                                                                                                                                                                                                                                                                                       | μA    | 5.0                                |                                                    |

| D025                          |                         |                       | 0.65 | 4.5   | 5                                                                                                                                                                                                                                                                                                        | μA    | 1.8                                | T1OSC Current (Note 1)                             |

|                               |                         | —                     | 1.3  | 5     | 5.5                                                                                                                                                                                                                                                                                                      | μA    | 3.0                                |                                                    |

| D025                          |                         | _                     | 19   | 39    | 45                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | T1OSC Current (Note 1)                             |

|                               |                         | _                     | 21.6 | 42    | 65                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                |                                                    |

|                               |                         | —                     | 23   | 47    | 52                                                                                                                                                                                                                                                                                                       | μA    | 5.0                                |                                                    |

| D026                          |                         | _                     | 0.05 | 1.5   | 3.0                                                                                                                                                                                                                                                                                                      | μA    | 1.8                                | A/D Current (Note 1, 3), no conversion in progress |

|                               |                         | —                     | 0.07 | 2.0   | 3.5                                                                                                                                                                                                                                                                                                      | μA    | 3.0                                |                                                    |

| D026                          |                         | _                     | 17.8 | 38    | 45                                                                                                                                                                                                                                                                                                       | μA    | 1.8                                | A/D Current (Note 1, 3), no                        |

|                               |                         | _                     | 21   | 45    | 50                                                                                                                                                                                                                                                                                                       | μA    | 3.0                                | conversion in progress                             |

|                               |                         | -                     | 22   | 50    | 65                                                                                                                                                                                                                                                                                                       | μA    | 5.0                                |                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

**3:** A/D oscillator source is FRC.

## PIC16(L)F1825/9

FIGURE 31-38: IPD, COMPARATOR, LOW-POWER MODE (CxSP = 0), PIC16F1825/9 ONLY

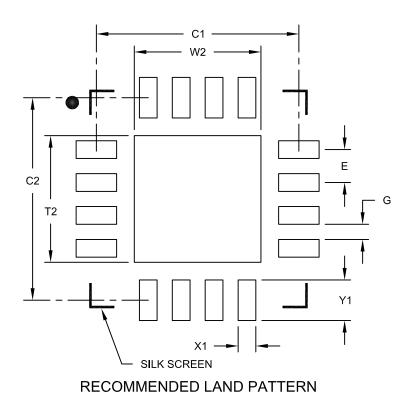

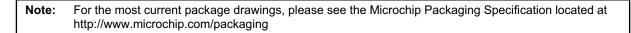

### 16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |          |      |

|----------------------------|----|-------------|----------|------|

| Dimension Limits           |    | MIN         | NOM      | MAX  |

| Contact Pitch              | E  |             | 0.65 BSC |      |

| Optional Center Pad Width  | W2 |             |          | 2.50 |

| Optional Center Pad Length | T2 |             |          | 2.50 |

| Contact Pad Spacing        | C1 |             | 4.00     |      |

| Contact Pad Spacing        | C2 |             | 4.00     |      |

| Contact Pad Width (X16)    | X1 |             |          | 0.35 |

| Contact Pad Length (X16)   | Y1 |             |          | 0.80 |

| Distance Between Pads      | G  | 0.30        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2127A

### 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

### APPENDIX A: DATA SHEET REVISION HISTORY

### Revision A (08/2010)

Original release.

### Revision B (05/2011)

Revised Electrical Specifications.

### Revision C (06/2012)

Updated the Family Types table; Updated Figures 1, 2 and 3; Updated Table 3-3; Changed all instances of SDO into SDO1, SDOSEL into SDO1SEL and SSSEL into SS1SEL; Added PIR3, PIR4, PIE3 and PIE4 to Table 3-3; Updated Register 4-2; Updated Sections 5.2.2.5 and 5.5.3; Added Note 1 to Table 11-3; Updated Figure 13-1 and Equation 16-1; Updated Section 19.9; Added charts to the DC and AC Characteristics Graphs section; Revised the Electrical Specifications section; Updated the Packaging Information section; Updated the Product Identification System section; Other minor corrections.

### Revision D (05/2014)

Added new UQFN packages: 16-Lead, UQFN, 4x4x0.5, (JQ) and 20-Lead, UQFN, 4x4x0.5, (GZ) packages. Minor corrections.

### Revision E (4/2015)

Added Section 30.9: High Temperature Operation in the Electrical Specifications section.

### APPENDIX B: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This shows a comparison of features in the migration from the PIC16F648 device to the PIC16(L)F1825/9 family of devices.

This section provides comparisons when migrating from other similar  $PIC^{\circledast}$  devices to the PIC16(L)F1825/9 family of devices.

### B.1 PIC16F648A to PIC16F1825/9

### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F648A         | PIC16F1825/9                                                                                      |

|---------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|

| Max. Operating<br>Speed               | 20 MHz             | 32 MHz                                                                                            |

| Max. Program<br>Memory (Words)        | 4K                 | 8K                                                                                                |

| Max. SRAM (Bytes)                     | 256                | 1024                                                                                              |