Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1825-i-sl |

**TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)**

| Address             | Name     | Bit 7                                | Bit 6          | Bit 5            | Bit 4           | Bit 3        | Bit 2       | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|----------|--------------------------------------|----------------|------------------|-----------------|--------------|-------------|-----------|-----------|----------------------|---------------------------------|

| Bank 5              |          |                                      |                |                  |                 |              |             |           |           |                      |                                 |

| 280h <sup>(1)</sup> | INDF0    | Addressing the (not a physical       |                | es contents of   | FSR0H/FSR0      | L to address | data memory | 1         |           | xxxx xxxx            | xxxx xxxx                       |

| 281h <sup>(1)</sup> | INDF1    | Addressing the (not a physical       |                | es contents of   | FSR1H/FSR1      | L to address | data memory | 1         |           | xxxx xxxx            | xxxx xxxx                       |

| 282h <sup>(1)</sup> | PCL      | Program Cou                          | nter (PC) Lea  | st Significant E | Byte            |              |             |           |           | 0000 0000            | 0000 0000                       |

| 283h <sup>(1)</sup> | STATUS   | _                                    | _              | _                | TO              | PD           | Z           | DC        | С         | 1 1000               | q quuu                          |

| 284h <sup>(1)</sup> | FSR0L    | Indirect Data                        | Memory Addr    | ess 0 Low Poi    | nter            |              | •           | •         | •         | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(1)</sup> | FSR0H    | Indirect Data                        | Memory Addr    | ess 0 High Poi   | inter           |              |             |           |           | 0000 0000            | 0000 0000                       |

| 286h <sup>(1)</sup> | FSR1L    | Indirect Data                        | Memory Addr    | ess 1 Low Poi    | nter            |              |             |           |           | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(1)</sup> | FSR1H    | Indirect Data                        | Memory Addr    | ess 1 High Poi   | inter           |              |             |           |           | 0000 0000            | 0000 0000                       |

| 288h <sup>(1)</sup> | BSR      | _                                    | _              | _                |                 |              | BSR<4:0>    |           |           | 0 0000               | 0 0000                          |

| 289h <sup>(1)</sup> | WREG     | Working Reg                          | ister          |                  |                 |              |             |           |           | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1)</sup> | PCLATH   | _                                    | Write Buffer f | or the upper 7   | bits of the Pro | gram Counte  | er          |           |           | -000 0000            | -000 0000                       |

| 28Bh <sup>(1)</sup> | INTCON   | GIE                                  | PEIE           | TMR0IE           | INTE            | IOCIE        | TMR0IF      | INTF      | IOCIF     | 0000 0000            | 0000 0000                       |

| 28Ch                | _        | Unimplement                          | Unimplemented  |                  |                 |              |             |           |           | _                    | _                               |

| 28Dh                | _        | Unimplement                          | Unimplemented  |                  |                 |              |             |           |           | _                    | _                               |

| 28Eh                | _        | Unimplement                          | Unimplemented  |                  |                 |              |             |           |           | _                    | _                               |

| 28Fh                | _        | Unimplement                          | ed             |                  |                 |              |             |           |           | _                    | _                               |

| 290h                | _        | Unimplement                          | ed             |                  |                 |              |             |           |           | _                    | _                               |

| 291h                | CCPR1L   | Capture/Com                          | pare/PWM Re    | egister 1 (LSB)  |                 |              |             |           |           | xxxx xxxx            | uuuu uuuu                       |

| 292h                | CCPR1H   | Capture/Com                          | pare/PWM Re    | egister 1 (MSB   | )               |              |             |           |           | xxxx xxxx            | uuuu uuuu                       |

| 293h                | CCP1CON  | P1M·                                 | <1:0>          | DC1B             | <1:0>           |              | CCP1N       | M<3:0>    |           | 0000 0000            | 0000 0000                       |

| 294h                | PWM1CON  | P1RSEN                               |                |                  | F               | P1DC<6:0>    |             |           |           | 0000 0000            | 0000 0000                       |

| 295h                | CCP1AS   | CCP1ASE                              |                | CCP1AS<2:0>      | •               | PSS1A        | C<1:0>      | PSS1B     | D<1:0>    | 0000 0000            | 0000 0000                       |

| 296h                | PSTR1CON | _                                    | _              | _                | STR1SYNC        | STR1D        | STR1C       | STR1B     | STR1A     | 0 0001               | 0 0001                          |

| 297h                | _        | Unimplement                          | ed             |                  |                 |              |             |           |           | _                    | _                               |

| 298h                | CCPR2L   | Capture/Com                          | pare/PWM Re    | egister 2 (LSB)  |                 |              |             |           |           | xxxx xxxx            | uuuu uuuu                       |

| 299h                | CCPR2H   | Capture/Compare/PWM Register 2 (MSB) |                |                  |                 |              |             | xxxx xxxx | uuuu uuuu |                      |                                 |

| 29Ah                | CCP2CON  | P2M1                                 | P2M0           | DC2B1            | DC2B0           | CCP2M3       | CCP2M2      | CCP2M1    | CCP2M0    | 0000 0000            | 0000 0000                       |

| 29Bh                | PWM2CON  | P2RSEN                               | P2DC6          | P2DC5            | P2DC4           | P2DC3        | P2DC2       | P2DC1     | P2DC0     | 0000 0000            | 0000 0000                       |

| 29Ch                | CCP2AS   | CCP2ASE                              | CCP2AS2        | CCP2AS1          | CCP2AS0         | PSS2AC1      | PSS2AC0     | PSS2BD1   | PSS2BD0   | 0000 0000            | 0000 0000                       |

| 29Dh                | PSTR2CON |                                      | _              |                  | STR2SYNC        | STR2D        | STR2C       | STR2B     | STR2A     | 0 0001               | 0 0001                          |

| 29Eh                | CCPTMRS  | C4TSEL1                              | C4TSEL0        | C3TSEL1          | C3TSEL0         | C2TSEL1      | C2TSEL0     | C1TSEL1   | C1TSEL0   | 0000 0000            | 0000 0000                       |

| 29Fh                |          | Unimplement                          | ed             |                  |                 |              |             |           |           | _                    | _                               |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only. 3: PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                     |        |                                  |                | I KEGISTI        |                 |               |             |       |           | Value on  | Value on all    |

|---------------------|--------|----------------------------------|----------------|------------------|-----------------|---------------|-------------|-------|-----------|-----------|-----------------|

| Address             | Name   | Bit 7                            | Bit 6          | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1 | Bit 0     | POR, BOR  | other<br>Resets |

| Bank 8              | Bank 8 |                                  |                |                  |                 |               |             |       |           |           |                 |

| 400h <sup>(1)</sup> | INDF0  | Addressing the (not a physical   |                | es contents of   | FSR0H/FSR0      | )L to address | data memory |       |           | xxxx xxxx | xxxx xxxx       |

| 401h <sup>(1)</sup> | INDF1  | Addressing the (not a physical   |                | es contents of   | FSR1H/FSR1      | IL to address | data memory |       |           | xxxx xxxx | xxxx xxxx       |

| 402h <sup>(1)</sup> | PCL    | Program Cou                      | nter (PC) Lea  | st Significant E | Byte            |               |             |       |           | 0000 0000 | 0000 0000       |

| 403h <sup>(1)</sup> | STATUS | _                                | ı              | ı                | TO              | PD            | Z           | DC    | С         | 1 1000    | q quuu          |

| 404h <sup>(1)</sup> | FSR0L  | Indirect Data                    | Memory Addr    | ess 0 Low Poir   | nter            |               |             |       |           | 0000 0000 | uuuu uuuu       |

| 405h <sup>(1)</sup> | FSR0H  | Indirect Data                    | Memory Addr    | ess 0 High Poi   | nter            |               |             |       |           | 0000 0000 | 0000 0000       |

| 406h <sup>(1)</sup> | FSR1L  | Indirect Data                    | Memory Addr    | ess 1 Low Poir   | nter            |               |             |       |           | 0000 0000 | uuuu uuuu       |

| 407h <sup>(1)</sup> | FSR1H  | Indirect Data                    | Memory Addr    | ess 1 High Poi   | nter            |               |             |       |           | 0000 0000 | 0000 0000       |

| 408h <sup>(1)</sup> | BSR    | _                                | _              | _                |                 |               | BSR<4:0>    |       |           | 0 0000    | 0 0000          |

| 409h <sup>(1)</sup> | WREG   | Working Reg                      | ister          |                  |                 |               |             |       |           | 0000 0000 | uuuu uuuu       |

| 40Ah <sup>(1)</sup> | PCLATH | _                                | Write Buffer f | or the upper 7   | bits of the Pro | ogram Counte  | er          |       |           | -000 0000 | -000 0000       |

| 40Bh <sup>(1)</sup> | INTCON | GIE                              | PEIE           | TMR0IE           | INTE            | IOCIE         | TMR0IF      | INTF  | IOCIF     | 0000 0000 | 0000 0000       |

| 40Ch                | _      | Unimplement                      | Unimplemented  |                  |                 |               |             |       |           | _         | _               |

| 40Dh                | _      | Unimplement                      | Unimplemented  |                  |                 |               |             |       |           | _         | _               |

| 40Eh                | _      | Unimplement                      | Unimplemented  |                  |                 |               |             |       | _         | _         |                 |

| 40Fh                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 410h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 411h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 412h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 413h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 414h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 415h                | TMR4   | Timer4 Modu                      | le Register    |                  |                 |               |             |       |           | 0000 0000 | 0000 0000       |

| 416h                | PR4    | Timer4 Perio                     | d Register     |                  |                 |               |             |       |           | 1111 1111 | 1111 1111       |

| 417h                | T4CON  | _                                |                | T4OUTP           | 'S<3:0>         |               | TMR4ON      | T4CKF | PS<1:0>   | -000 0000 | -000 0000       |

| 418h                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

| 419h                | _      | Unimplemented                    |                |                  |                 |               |             |       | _         | _         |                 |

| 41Ah                | _      | Unimplemented —                  |                |                  |                 |               |             |       | _         | _         |                 |

| 41Bh                | _      | Unimplemented —                  |                |                  |                 |               |             |       |           |           |                 |

| 41Ch                | TMR6   | Timer6 Module Register 0000 0000 |                |                  |                 |               |             |       | 0000 0000 |           |                 |

| 41Dh                | PR6    | Timer6 Perio                     | d Register     |                  |                 |               |             |       |           | 1111 1111 | 1111 1111       |

| 41Eh                | T6CON  | _                                |                | T6OUTP           | 'S<3:0>         |               | TMR6ON      | T6CKF | PS<1:0>   | -000 0000 | -000 0000       |

| 41Fh                | _      | Unimplement                      | ed             |                  |                 |               |             |       |           | _         | _               |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only.

3: PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register on Page |

|--------|--------|--------|------------|-------|-------|-------|--------|--------|------------------|

| BORCON | SBOREN | _      | _          | _     | _     | _     | _      | BORRDY | 76               |

| PCON   | STKOVF | STKUNF | _          | _     | RMCLR | RI    | POR    | BOR    | 80               |

| STATUS | _      | _      | -          | TO    | PD    | Z     | DC     | С      | 22               |

| WDTCON | _      | _      | WDTPS<4:0> |       |       |       | SWDTEN | 100    |                  |

**Legend:** — Unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

### **EXAMPLE 11-4: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase block is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F

BCF

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

EEADRL

MOVF

ADDRL,W

; Load lower 8 bits of erase address boundary

MOVWF

EEADRL

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVF

MOVWF

EEADRH

EECON1, EEPGD

; Point to program memory

BSF

EECON1, CFGS

BCF

; Not configuration space

BSF

EECON1, FREE

; Specify an erase operation

BSF

EECON1, WREN

; Enable writes

; Start of required sequence to initiate erase

MOVT.W

55h

MOVWF

EECON2

; Write 55h

Required

Sequence

MOVLW

0AAh

MOVWF

EECON2

; Write AAh

BSF

EECON1,WR

; Set WR bit to begin erase

NOP

; Any instructions here are ignored as processor

; halts to begin erase sequence

NOP

; Processor will stop here and wait for erase complete.

; after erase processor continues with 3rd instruction

BCF

EECON1, WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

### REGISTER 12-20: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| U-0(3)                 | U-0(3)                 | R/W-0/0 <sup>(3)</sup> |

|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| R/W-1/1 <sup>(2)</sup> |

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5                | INLVLC4                | INLVLC3                | INLVLC2                | INLVLC1                | INLVLC0                |

| bit 7                  |                        |                        |                        |                        |                        |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup>

For RC<7:0> pins, respectively

1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

Note 1: INLVLC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

2: PIC16(L)F1829 only, Reset default value.

3: PIC16(L)F1825 only, Reset default value.

TABLE 12-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 129                 |

| INLVLC | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 135                 |

| LATC   | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 128                 |

| PORTC  | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 128                 |

| TRISC  | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 128                 |

| WPUC   | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 129                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16(L)F1829 only.

### 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1I.

### 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note:

The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

### 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note:

When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

# 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

### 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

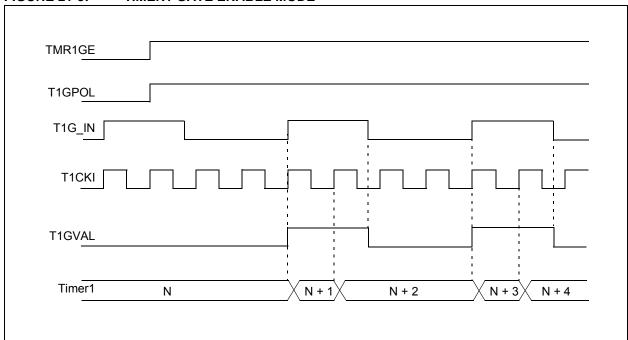

#### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK    | T1GPOL | T1G | Timer1 Operation |

|----------|--------|-----|------------------|

| <b>↑</b> | 0      | 0   | Counts           |

| 1        | 0      | 1   | Holds Count      |

| <b>↑</b> | 1      | 0   | Holds Count      |

| <b>↑</b> | 1      | 1   | Counts           |

### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

**TABLE 21-4: TIMER1 GATE SOURCES**

| T1GSS | Timer1 Gate Source                                                     |

|-------|------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                        |

| 01    | Overflow of Timer0 (TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT (optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT (optionally Timer1 synchronized output) |

### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 Gate Control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

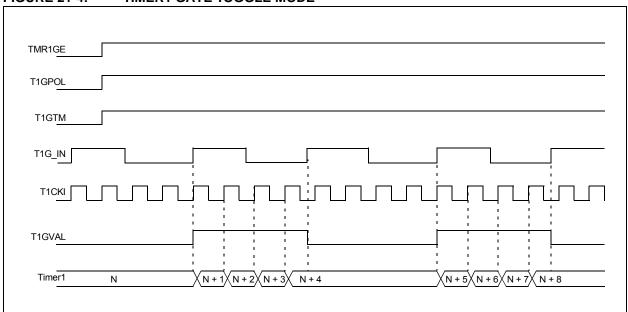

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |

|-------|---------------------------------------------|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |

|       | indeterminate operation.                    |  |  |  |

### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 21-6 for timing details.

### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 gate event interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

FIGURE 21-3: TIMER1 GATE ENABLE MODE

FIGURE 21-4: TIMER1 GATE TOGGLE MODE

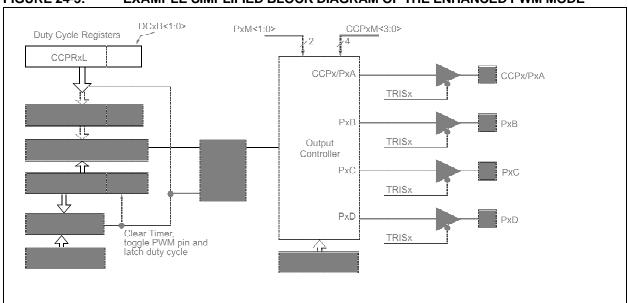

### 24.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1 and ECCP2, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- · TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- · PSTRxCON registers

- · PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- · Single PWM

- · Half-Bridge PWM

- · Full-Bridge PWM, Forward mode

- · Full-Bridge PWM, Reverse mode

- · Single PWM with PWM Steering mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 24-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Figure 24-8 shows the pin assignments for various Enhanced PWM modes.

- **Note 1:** The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- **2:** Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- **4:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

### FIGURE 24-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The 8-bit timer TMRx register is concatenated with the 2-bit internal Q clock, or two bits of the prescaler to create the 10-bit time base.

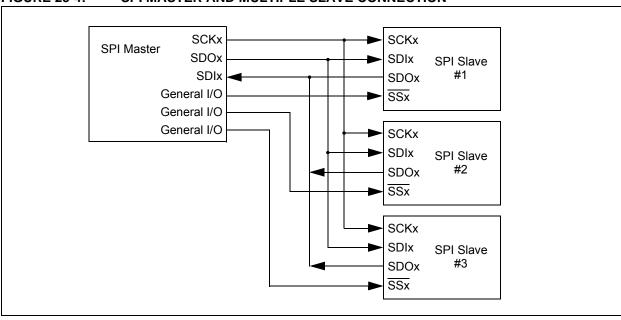

#### FIGURE 25-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 25.2.1 SPI MODE REGISTERS

The MSSPx module has five registers for SPI mode operation. These are:

- MSSPx STATUS register (SSPxSTAT)

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Control Register 3 (SSPxCON3)

- MSSPx Data Buffer register (SSPxBUF)

- MSSPx Address register (SSPxADD)

- MSSPx Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 25.7** "Baud Rate Generator".

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

### 25.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

To enable the serial port, SSPx Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDIx must have corresponding TRIS bit set

- SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding TRIS bit cleared

- SCKx (Slave mode) must have corresponding TRIS bit set

- SSx must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

### 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                                  |  |  |  |

| Operands:        | $-32 \le k \le 31$<br>$n \in [0, 1]$                                                                      |  |  |  |

| Operation:       | $FSR(n) + k \to FSR(n)$                                                                                   |  |  |  |

| Status Affected: | None                                                                                                      |  |  |  |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair.                   |  |  |  |

|                  | FSRn is limited to the range 0000h - FFFFh. Moving beyond these bounds will cause the FSR to wrap-around. |  |  |  |

| r are<br>al 'k'. The<br>egister. |

|----------------------------------|

|                                  |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                     |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                           |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                    |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                     |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                                                      |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                               |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ASRF f {,d}                                                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $(f<7>)\rightarrow dest<7>$<br>$(f<7:1>)\rightarrow dest<6:0>,$<br>$(f<0>)\rightarrow C,$                                                                                                                            |  |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

register f

| ADDWFC           | VFC ADD W and CARRY bit to f                                                                                                                                   |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |  |  |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                             |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'. |  |  |  |  |  |  |

### 30.1 DC Characteristics: PIC16(L)F1825/9-I/E (Industrial, Extended)

| PIC16LF1825/9 |                                                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                                                                                                                                                                                                                                    |        |            |        |                                                                                         |  |

|---------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--------|-----------------------------------------------------------------------------------------|--|

| PIC16F1825/9  |                                                     |                                                                                                                                                                                                                                     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |        |            |        |                                                                                         |  |

| Param.<br>No. | Sym.                                                | Characteristic                                                                                                                                                                                                                      | Min.                                                                                                                                                                                                                               | Тур†   | Max.       | Units  | Conditions                                                                              |  |

| D001          | VDD                                                 | Supply Voltage (VDDMIN, VDDMAX)                                                                                                                                                                                                     |                                                                                                                                                                                                                                    |        |            |        |                                                                                         |  |

|               |                                                     | PIC16LF1825/9                                                                                                                                                                                                                       | 1.8<br>2.5                                                                                                                                                                                                                         | _<br>_ | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                       |  |

| D001          |                                                     | PIC16F1825/9                                                                                                                                                                                                                        | 1.8<br>2.5                                                                                                                                                                                                                         |        | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                       |  |

| D002*         | D002* VDR RAM Data Retention Voltage <sup>(1)</sup> |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                    |        |            |        |                                                                                         |  |

|               |                                                     | PIC16LF1825/9                                                                                                                                                                                                                       | 1.5                                                                                                                                                                                                                                | _      | _          | V      | Device in Sleep mode                                                                    |  |

| D002*         |                                                     | PIC16F1825/9                                                                                                                                                                                                                        | 1.7                                                                                                                                                                                                                                | _      | _          | V      | Device in Sleep mode                                                                    |  |

|               | VPOR*                                               | Power-on Reset Release Voltage                                                                                                                                                                                                      | _                                                                                                                                                                                                                                  | 1.6    | _          | V      |                                                                                         |  |

| D002B*        | VPORR*                                              | Power-on Reset Rearm Voltage                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |        |            |        |                                                                                         |  |

|               |                                                     | PIC16LF1825/9                                                                                                                                                                                                                       |                                                                                                                                                                                                                                    | 0.8    |            | V      | Device in Sleep mode                                                                    |  |

|               |                                                     | PIC16F1825/9                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                  | 1.5    | _          | V      | Device in Sleep mode                                                                    |  |

| D003          | VADFVR                                              | Fixed Voltage Reference Voltage for ADC                                                                                                                                                                                             | -8                                                                                                                                                                                                                                 | _      | 6          | %      | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V                         |  |

| D003A         | VCDAFVR                                             | Fixed Voltage Reference Voltage for Comparator and DAC                                                                                                                                                                              | -11                                                                                                                                                                                                                                | _      | 7          | %      | $1.024V$ , VDD $\geq 2.5V$<br>$2.048V$ , VDD $\geq 2.5V$<br>$4.096V$ , VDD $\geq 4.75V$ |  |

| D003C*        | TCVFVR                                              | Temperature Coefficient, Fixed Voltage Reference                                                                                                                                                                                    | _                                                                                                                                                                                                                                  | -130   |            | ppm/°C |                                                                                         |  |

| D003D*        | ΔVFVR/<br>ΔVIN                                      | Line Regulation, Fixed Voltage<br>Reference                                                                                                                                                                                         |                                                                                                                                                                                                                                    | 0.270  | _          | %/V    |                                                                                         |  |

| D004*         | SVDD                                                | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                                                                                                           | 0.05                                                                                                                                                                                                                               |        | _          | V/ms   | See Section 7.1 "Power-on Reset (POR)" for details.                                     |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> PLL required for 32 MHz operation.

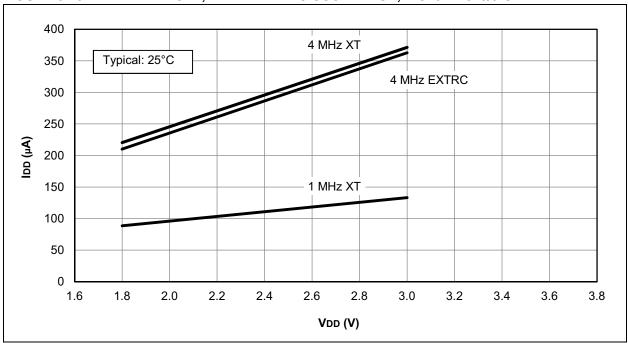

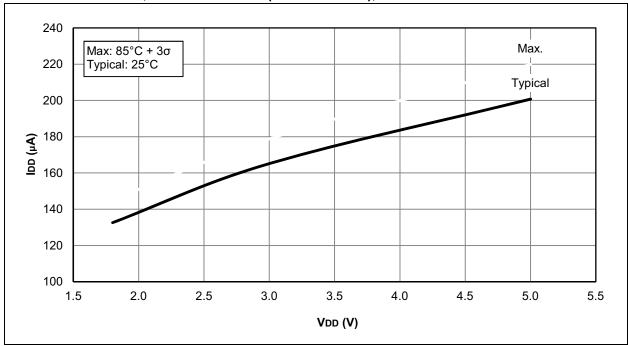

FIGURE 31-3: IDD TYPICAL, XT AND EXTRC OSCILLATOR, PIC16LF1825/9 ONLY

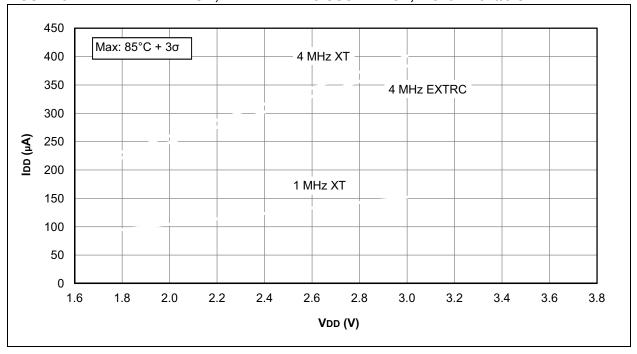

FIGURE 31-4: IDD MAXIMUM, XT AND EXTRC OSCILLATOR, PIC16LF1825/9 ONLY

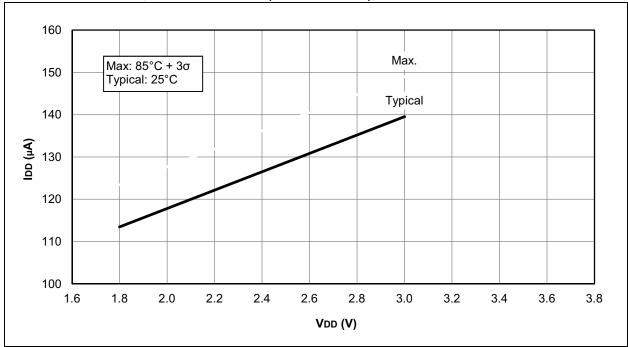

FIGURE 31-14: IDD, MFINTOSC MODE (Fosc = 500 kHz), PIC16F1825/9 ONLY

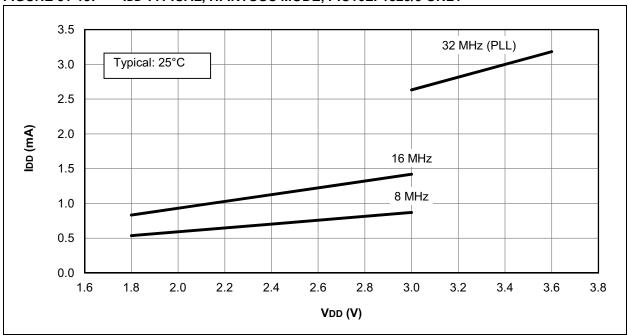

FIGURE 31-15: IDD TYPICAL, HFINTOSC MODE, PIC16LF1825/9 ONLY

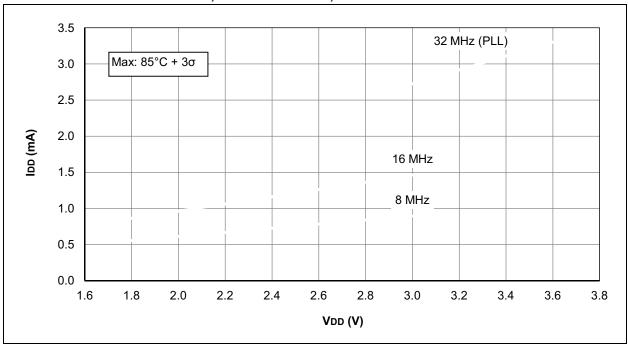

FIGURE 31-16: IDD MAXIMUM, HFINTOSC MODE, PIC16LF1825/9 ONLY

-5

0

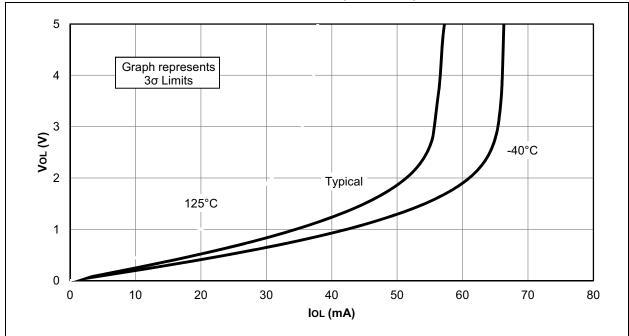

6 Graph represents 5 . 3σ Limits 4 -40°C 125°C 2 Typical 1 0

-15

IOH (mA)

-10

FIGURE 31-41: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V), PIC16F1825/9 ONLY

-20

-30

-25

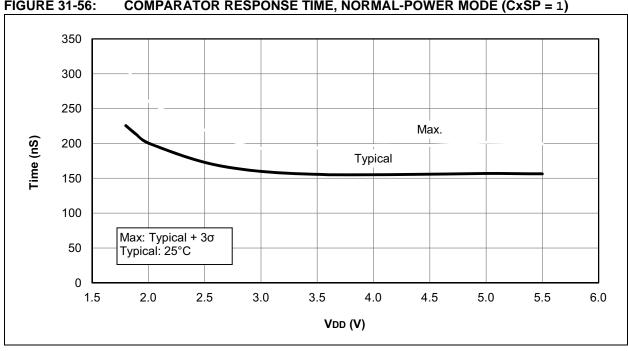

FIGURE 31-56: COMPARATOR RESPONSE TIME, NORMAL-POWER MODE (CxSP = 1)

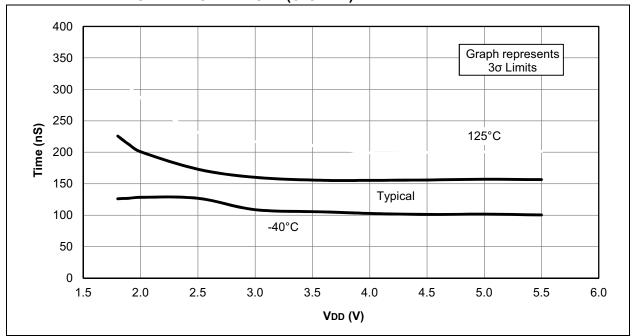

FIGURE 31-57: COMPARATOR RESPONSE TIME OVER TEMPERATURE, NORMAL-POWER MODE (CxSP = 1)

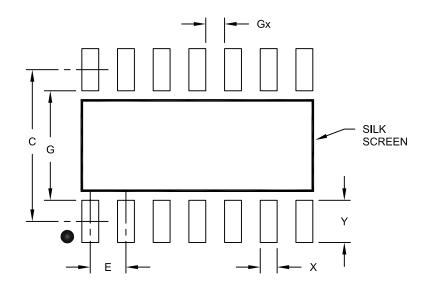

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### **RECOMMENDED LAND PATTERN**

|                       | MILLIMETERS      |          |      |      |

|-----------------------|------------------|----------|------|------|

| Dimension             | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch         | Е                | 1.27 BSC |      |      |

| Contact Pad Spacing   | С                |          | 5.40 |      |

| Contact Pad Width     | Х                |          |      | 0.60 |

| Contact Pad Length    | Υ                |          |      | 1.50 |

| Distance Between Pads | Gx               | 0.67     |      |      |

| Distance Between Pads | G                | 3.90     |      |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

### THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support