Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

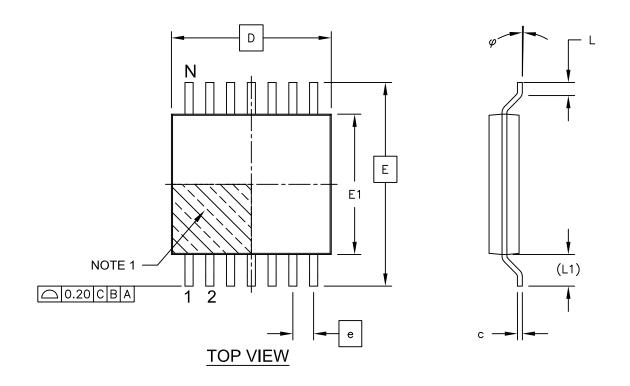

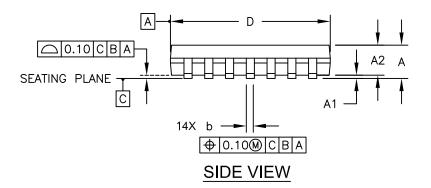

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1825t-i-st |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                 | Function Input<br>Type Type |                                                   |      | Description                                   |

|------------------------------------------------------|-----------------------------|---------------------------------------------------|------|-----------------------------------------------|

| RA0/AN0/CPS0/C1IN+/VREF-/                            | RA0                         | TTL                                               | CMOS | General purpose I/O.                          |

| DACOUT/TX <sup>(1)</sup> /CK <sup>(1)</sup> /        | AN0                         | AN                                                | —    | A/D Channel 0 input.                          |

| ICSPDAT/ICDDAT                                       | CPS0                        | AN                                                | _    | Capacitive sensing input 0.                   |

|                                                      | C1IN+                       | C1IN+ AN — Comparator C1 positive input.          |      | Comparator C1 positive input.                 |

|                                                      | VREF-                       | VREF- AN — A/D and DAC Negative Voltage Reference |      | A/D and DAC Negative Voltage Reference input. |

|                                                      | DACOUT                      | _                                                 | AN   | Digital-to-Analog Converter output.           |

|                                                      | TX                          | _                                                 | CMOS | USART asynchronous transmit.                  |

|                                                      | СК                          | ST                                                | CMOS | USART synchronous clock.                      |

|                                                      | ICSPDAT                     | ST                                                | CMOS | ICSP™ Data I/O.                               |

|                                                      | ICDDAT                      | ST                                                | CMOS | In-Circuit Data I/O.                          |

| RA1/AN1/CPS1/C12IN0-/VREF+/                          | RA1                         | TTL                                               | CMOS | General purpose I/O.                          |

| SRI/RX <sup>(1)</sup> /DT <sup>(1)</sup> /ICSPCLK/   | AN1                         | AN                                                | —    | A/D Channel 1 input.                          |

| CDCLK                                                | CPS1                        | AN                                                | _    | Capacitive sensing input 1.                   |

|                                                      | C12IN0-                     | AN                                                | —    | Comparator C1 or C2 negative input.           |

|                                                      | VREF+                       | AN                                                | —    | A/D and DAC Positive Voltage Reference input. |

|                                                      | SRI                         | ST                                                | —    | SR Latch input.                               |

|                                                      | RX                          | ST                                                | —    | USART asynchronous input.                     |

|                                                      | DT                          | ST                                                | CMOS | USART synchronous data.                       |

|                                                      | ICSPCLK                     | ST                                                | —    | Serial Programming Clock.                     |

|                                                      | ICDCLK                      | ST                                                | —    | In-Circuit Debug Clock.                       |

| RA2/AN2/CPS2/T0CKI/INT/                              | RA2                         | ST                                                | CMOS | General purpose I/O.                          |

| C1OUT/SRQ/CCP3/FLT0                                  | AN2                         | AN                                                | —    | A/D Channel 2 input.                          |

|                                                      | CPS2                        | AN                                                | —    | Capacitive sensing input 2.                   |

|                                                      | TOCKI                       | ST                                                | _    | Timer0 clock input.                           |

|                                                      | INT                         | ST                                                | _    | External interrupt.                           |

|                                                      | C10UT                       |                                                   | CMOS | Comparator C1 output.                         |

|                                                      | SRQ                         |                                                   | CMOS | SR Latch non-inverting output.                |

|                                                      | CCP3                        | ST                                                | CMOS | Capture/Compare/PWM3.                         |

|                                                      | FLT0                        | ST                                                | _    | ECCP Auto-Shutdown Fault input.               |

| RA3/SS1 <sup>(1)</sup> /T1G <sup>(1)</sup> /VPP/MCLR | RA3                         | TTL                                               |      | General purpose input.                        |

|                                                      | SS1                         | ST                                                | —    | Slave Select input.                           |

|                                                      | T1G                         | ST                                                | —    | Timer1 Gate input.                            |

|                                                      | VPP                         | ΗV                                                | _    | Programming voltage.                          |

|                                                      | MCLR                        | ST                                                | _    | Master Clear with internal pull-up.           |

TABLE 1-2: PIC16(L)F1825 PINOUT DESCRIPTION

Legend:AN = Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$ = Schmitt Trigger input with  $I^2C$ HV = High VoltageXTAL = CrystalLevels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Default function location.

## TABLE 3-3: PIC16(L)F1825/9 MEMORY MAP, BANKS 0-7

|              | BANK 0               | 010(         | BANK 1                |               | BANK 2                |              | BANK 3                |               | BANK 4                  |              | BANK 5                |              | BANK 6                |              | BANK 7                |

|--------------|----------------------|--------------|-----------------------|---------------|-----------------------|--------------|-----------------------|---------------|-------------------------|--------------|-----------------------|--------------|-----------------------|--------------|-----------------------|

| 000h         | INDF0                | 080h         | INDF0                 | 100h          | INDF0                 | 180h         | INDF0                 | 200h          | INDF0                   | 280h         | INDF0                 | 300h         | INDF0                 | 380h         | INDF0                 |

| 001h         | INDF1                | 081h         | INDF1                 | 101h          | INDF1                 | ] 181h [     | INDF1                 | 201h          | INDF1                   | 281h         | INDF1                 | 301h         | INDF1                 | 381h         | INDF1                 |

| 002h         | PCL                  | 082h         | PCL                   | 102h          | PCL                   | 182h         | PCL                   | 202h          | PCL                     | 282h         | PCL                   | 302h         | PCL                   | 382h         | PCL                   |

| 003h         | STATUS               | 083h         | STATUS                | 103h          | STATUS                | 183h         | STATUS                | 203h          | STATUS                  | 283h         | STATUS                | 303h         | STATUS                | 383h         | STATUS                |

| 004h         | FSR0L                | 084h         | FSR0L                 | 104h          | FSR0L                 | 184h         | FSR0L                 | 204h          | FSR0L                   | 284h         | FSR0L                 | 304h         | FSR0L                 | 384h         | FSR0L                 |

| 005h         | FSR0H                | 085h<br>086h | FSR0H<br>FSR1L        | 105h          | FSR0H<br>FSR1L        | 185h         | FSR0H<br>FSR1L        | 205h          | FSR0H<br>FSR1L          | 285h<br>286h | FSR0H<br>FSR1L        | 305h         | FSR0H<br>FSR1L        | 385h         | FSR0H<br>FSR1L        |

| 006h<br>007h | FSR1L<br>FSR1H       | 086h<br>087h | FSR1L<br>FSR1H        | 106h<br>107h  | FSR1L<br>FSR1H        | 186h<br>187h | FSR1L<br>FSR1H        | 206h<br>207h  | FSR1L<br>FSR1H          | 286n<br>287h | FSR1L<br>FSR1H        | 306h<br>307h | FSR1L<br>FSR1H        | 386h<br>387h | FSR1L<br>FSR1H        |

| 007h<br>008h | BSR                  | 088h         | BSR                   | 10711<br>108h | BSR                   | 188h         | BSR                   | 20711<br>208h | BSR                     | 288h         | BSR                   | 308h         | BSR                   | 388h         | BSR                   |

| 009h         | WREG                 | 089h         | WREG                  | 109h          | WREG                  | 189h         | WREG                  | 209h          | WREG                    | 289h         | WREG                  | 309h         | WREG                  | 389h         | WREG                  |

| 00Ah         | PCLATH               | 08Ah         | PCLATH                | 10Ah          | PCLATH                | 18Ah         | PCLATH                | 20Ah          | PCLATH                  | 28Ah         | PCLATH                | 30Ah         | PCLATH                | 38Ah         | PCLATH                |

| 00Bh         | INTCON               | 08Bh         | INTCON                | 10Bh          | INTCON                | 18Bh         | INTCON                | 20Bh          | INTCON                  | 28Bh         | INTCON                | 30Bh         | INTCON                | 38Bh         | INTCON                |

| 00Ch         | PORTA                | 08Ch         | TRISA                 | 10Ch          | LATA                  | 18Ch         | ANSELA                | 20Ch          | WPUA                    | 28Ch         | _                     | 30Ch         | _                     | 38Ch         | INLVLA                |

| 00Dh         | PORTB <sup>(1)</sup> | 08Dh         | TRISB <sup>(1)</sup>  | 10Dh          | LATB <sup>(1)</sup>   | 18Dh         | ANSELB <sup>(1)</sup> | 20Dh          | WPUB <sup>(1)</sup>     | 28Dh         |                       | 30Dh         | —                     | 38Dh         | INLVLB <sup>(1)</sup> |

| 00Eh         | PORTC                | 08Eh         | TRISC                 | 10Eh          | LATC                  | 18Eh         | ANSELC                | 20Eh          | WPUC                    | 28Eh         | -                     | 30Eh         | —                     | 38Eh         | INLVLC                |

| 00Fh         | —                    | 08Fh         | —                     | 10Fh          | _                     | 18Fh         | _                     | 20Fh          | _                       | 28Fh         | _                     | 30Fh         | _                     | 38Fh         | _                     |

| 010h         | _                    | 090h         | —                     | 110h          | —                     | 190h         | _                     | 210h          | _                       | 290h         | —                     | 310h         |                       | 390h         | _                     |

| 011h         | PIR1                 | 091h         | PIE1                  | 111h          | CM1CON0               | 191h         | EEADRL                | 211h          | SSP1BUF                 | 291h         | CCPR1L                | 311h         | CCPR3L                | 391h         | IOCAP                 |

| 012h         | PIR2                 | 092h         | PIE2                  | 112h          | CM1CON1               | 192h         | EEADRH                | 212h          | SSP1ADD                 | 292h         | CCPR1H                | 312h         | CCPR3H                | 392h         | IOCAN                 |

| 013h         | PIR3                 | 093h         | PIE3                  | 113h          | CM2CON0               | 193h         | EEDATL                | 213h          | SSP1MSK                 | 293h         | CCP1CON               | 313h         | CCP3CON               | 393h         | IOCAF                 |

| 014h         | PIR4 <sup>(1)</sup>  | 094h         | PIE4 <sup>(1)</sup>   | 114h          | CM2CON1               | 194h         | EEDATH                | 214h          | SSP1STAT                | 294h         | PWM1CON               | 314h         | _                     | 394h         | IOCBP <sup>(1)</sup>  |

| 015h         | TMR0                 | 095h         | OPTION_REG            | 115h          | CMOUT                 | 195h         | EECON1                | 215h          | SSP1CON1                | 295h         | CCP1AS                | 315h         | _                     | 395h         | IOCBN <sup>(1)</sup>  |

| 016h         | TMR1L                | 096h         | PCON                  | 116h          | BORCON                | 196h         | EECON2                | 216h          | SSP1CON2                | 296h         | PSTR1CON              | 316h         | _                     | 396h         | IOCBF <sup>(1)</sup>  |

| 017h         | TMR1H                | 097h         | WDTCON                | 117h          | FVRCON                | 197h         | _                     | 217h          | SSP1CON3                | 297h         | —                     | 317h         | —                     | 397h         | _                     |

| 018h         | T1CON                | 098h         | OSCTUNE               | 118h          | DACCON0               | 198h         | —                     | 218h          | _                       | 298h         | CCPR2L                | 318h         | CCPR4L                | 398h         | _                     |

| 019h         | T1GCON               | 099h         | OSCCON                | 119h          | DACCON1               | 199h         | RCREG                 | 219h          | SSP2BUF <sup>(1)</sup>  | 299h         | CCPR2H                | 319h         | CCPR4H                | 399h         | _                     |

| 01Ah         | TMR2                 | 09Ah         | OSCSTAT               | 11Ah          | SRCON0                | 19Ah         | TXREG                 | 21Ah          | SSP2ADD <sup>(1)</sup>  | 29Ah         | CCP2CON               | 31Ah         | CCP4CON               | 39Ah         | CLKRCON               |

| 01Bh         | PR2                  | 09Bh         | ADRESL                | 11Bh          | SRCON1                | 19Bh         | SPBRGL                | 21Bh          | SSP2MSK <sup>(1)</sup>  | 29Bh         | PWM2CON               | 31Bh         | _                     | 39Bh         | _                     |

| 01Ch         | T2CON                | 09Ch         | ADRESH                | 11Ch          | —                     | 19Ch         | SPBRGH                | 21Ch          | SSP2STAT <sup>(1)</sup> | 29Ch         | CCP2AS                | 31Ch         | —                     | 39Ch         | MDCON                 |

| 01Dh         | _                    | 09Dh         | ADCON0                | 11Dh          | APFCON0               | 19Dh         | RCSTA                 | 21Dh          | SSP2CON1 <sup>(1)</sup> | 29Dh         | PSTR2CON              | 31Dh         | —                     | 39Dh         | MDSRC                 |

| 01Eh         | CPSCON0              | 09Eh         | ADCON1                | 11Eh          | APFCON1               | 19Eh         | TXSTA                 | 21Eh          | SSP2CON2 <sup>(1)</sup> | 29Eh         | CCPTMRS               | 31Eh         | —                     | 39Eh         | MDCARL                |

| 01Fh         | CPSCON1              | 09Fh         | —                     | 11Fh          | _                     | 19Fh         | BAUDCON               | 21Fh          | SSP2CON3 <sup>(1)</sup> | 29Fh         | _                     | 31Fh         | _                     | 39Fh         | MDCARH                |

| 020h         |                      | 0A0h         |                       | 120h          |                       | 1A0h         |                       | 220h          |                         | 2A0h         |                       | 320h         |                       | 3A0h         |                       |

|              | General              |              | General               |               | General               |              | General               |               | General                 |              | General               |              | General               |              | General               |

|              | Purpose              |              | Purpose               |               | Purpose               |              | Purpose               |               | Purpose                 |              | Purpose               |              | Purpose               |              | Purpose               |

|              | Register             |              | Register              |               | Register              |              | Register              |               | Register                |              | Register              |              | Register              |              | Register              |

|              | 96 Bytes             |              | 80 Bytes              |               | 80 Bytes              |              | 80 Bytes              |               | 80 Bytes                |              | 80 Bytes              |              | 80 Bytes              |              | 80 Bytes              |

| 06Fh         |                      | 0EFh         |                       | 16Fh          |                       | 1EFh         |                       | 26Fh          |                         | 2EFh         |                       | 36Fh         |                       | 3EFh         |                       |

| 070h         |                      | 0F0h         |                       | 170h          |                       | 1F0h         |                       | 270h          |                         | 2F0h         |                       | 370h         |                       | 3F0h         |                       |

|              | Common RAM           |              | Accesses<br>70h – 7Fh |               | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |               | Accesses<br>70h – 7Fh   |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |

| 07Fh         |                      | 0FFh         | /011 – /FII           | 17Fh          | / UII – / FII         | 1FFh         | /011 - / FII          | 27Fh          | /011 – / FII            | 2FFh         | -                     | 37Fh         | /011 – / F11          | 3FFh         | /011-/F11             |

| 07FN         |                      | UFFN         |                       | l ı⁄⊢u l      |                       | liteu        |                       | _ ∠/⊦n [      |                         | ZEEN         |                       | 37FN         |                       | 3FFN         |                       |

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Available only on PIC16(L)F1829.

# PIC16(L)F1825/9

| Address             | Name                | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 6                                                    | Bit 5                  | Bit 4                 | Bit 3  | Bit 2     | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |  |

|---------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------|-----------------------|--------|-----------|-----------------------|---------|----------------------|---------------------------------|--|--|

| Bank 2              |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |                        |                       |        |           |                       |         |                      |                                 |  |  |

| 100h <sup>(1)</sup> | INDF0               | Addressing the Addres | XXXX XXXX                                                | XXXX XXXX              |                       |        |           |                       |         |                      |                                 |  |  |

| 101h <sup>(1)</sup> | INDF1               | Addressing the Addres | XXXX XXXX                                                | XXXX XXXX              |                       |        |           |                       |         |                      |                                 |  |  |

| 102h <sup>(1)</sup> | PCL                 | Program Cou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Program Counter (PC) Least Significant Byte              |                        |                       |        |           |                       |         |                      |                                 |  |  |

| 103h <sup>(1)</sup> | STATUS              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                        | _                      | TO                    | PD     | Z         | DC                    | С       | 1 1000               | q quuu                          |  |  |

| 104h <sup>(1)</sup> | FSR0L               | Indirect Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Memory Addr                                              | ess 0 Low Poir         | nter                  | •      | •         | •                     | •       | 0000 0000            | uuuu uuuu                       |  |  |

| 105h <sup>(1)</sup> | FSR0H               | Indirect Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Memory Addr                                              | ess 0 High Poi         | nter                  |        |           |                       |         | 0000 0000            | 0000 0000                       |  |  |

| 106h <sup>(1)</sup> | FSR1L               | Indirect Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Memory Addr                                              | ess 1 Low Poir         | nter                  |        |           |                       |         | 0000 0000            | uuuu uuuu                       |  |  |

| 107h <sup>(1)</sup> | FSR1H               | Indirect Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Memory Addr                                              | ess 1 High Poi         | nter                  |        |           |                       |         | 0000 0000            | 0000 0000                       |  |  |

| 108h <sup>(1)</sup> | BSR                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                        | _                      |                       |        | BSR<4:0>  |                       |         | 0 0000               | 0 0000                          |  |  |

| 109h <sup>(1)</sup> | WREG                | Working Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ister                                                    |                        | •                     |        |           |                       |         | 0000 0000            | uuuu uuuu                       |  |  |

| 10Ah <sup>(1)</sup> | PCLATH              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Write Buffer for the upper 7 bits of the Program Counter |                        |                       |        |           |                       |         |                      |                                 |  |  |

| 10Bh <sup>(1)</sup> | INTCON              | GIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PEIE                                                     | TMR0IE                 | INTE                  | IOCIE  | TMR0IF    | INTF                  | IOCIF   | 0000 0000            | 0000 0000                       |  |  |

| 10Ch                | LATA                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                        | LATA5                  | LATA4                 | _      | LATA2     | LATA1                 | LATA0   | xx -xxx              | uu -uuu                         |  |  |

| 10Dh                | LATB <sup>(2)</sup> | LATB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LATB6                                                    | LATB5                  | LATB4                 | —      | _         | _                     | _       | xxxx                 | xxxx                            |  |  |

| 10Eh                | LATC                | LATC7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LATC6 <sup>(2)</sup>                                     | LATC5                  | LATC4                 | LATC3  | LATC2     | LATC1                 | LATC0   | xxxx xxxx            | uuuu uuuu                       |  |  |

| 10Fh                | —                   | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ted                                                      |                        |                       |        |           |                       |         | _                    | _                               |  |  |

| 110h                | —                   | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ted                                                      |                        |                       |        |           |                       |         | _                    | _                               |  |  |

| 111h                | CM1CON0             | C10N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C10UT                                                    | C10E                   | C1POL                 | _      | C1SP      | C1HYS                 | C1SYNC  | 0000 -100            | 0000 -100                       |  |  |

| 112h                | CM1CON1             | C1INTP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C1INTN                                                   | C1PCH                  | H<1:0>                | _      | _         | C1NCH1                | C1NCH0  | 00000                | 00000                           |  |  |

| 113h                | CM2CON0             | C2ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C2OUT                                                    | C2OE                   | C2POL                 | _      | C2SP      | C2HYS                 | C2SYNC  | 0000 -100            | 0000 -100                       |  |  |

| 114h                | CM2CON1             | C2INTP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C2INTN                                                   | C2PCH                  | H<1:0>                | _      | _         | C2NCH                 | H<1:0>  | 000000               | 000000                          |  |  |

| 115h                | CMOUT               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                        | _                      | _                     | _      | _         | MC2OUT                | MC1OUT  | 00                   | 00                              |  |  |