# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Word 2 is    |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

###

#### FIGURE 5-8: TWO-SPEED START-UP

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

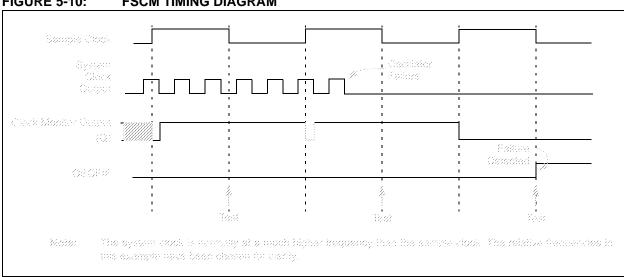

#### FIGURE 5-10: **FSCM TIMING DIAGRAM**

#### 8.6 Interrupt Control Registers

#### 8.6.1 INTCON REGISTER

The INTCON register is a readable and writable register, that contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | GIE: Global Interrupt Enable bit                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Enables all active interrupts<br>0 = Disables all interrupts                                                                                                                                          |

| bit 6   | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                    |

| bit 5   | <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                              |

| bit 4   | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                              |

| bit 3   | IOCIE: Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                                      |

| bit 2   | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                               |

| bit 1   | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur                                                                          |

| bit 0   | <b>IOCIF:</b> Interrupt-on-Change Interrupt Flag bit <sup>(1)</sup><br>1 = When at least one of the interrupt-on-change pins changed state<br>0 = None of the interrupt-on-change pins have changed state |

| Note 1: | The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCxF register                                                                                                  |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCxF register have been cleared by software.

#### 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EED-ATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

#### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

## PIC16(L)F1825/9

#### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

MOVLW PROG_ADDR_LO ; Select Bank for EEPROM registers

MOVWF EEADRL ; Store LSB of address

MOVLW PROG_ADDR_HI ;

MOVWL EEADRH ;

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

; Initiate read

; Executed (Figure 11-1)

BSF

EECON1,RD

NOP

; Ignored (Figure 11-1)

NOP

INTCON,GIE

; Restore interrupts

BSF

MOVF

EEDATL,W

; Get LSB of word

MOVWF PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

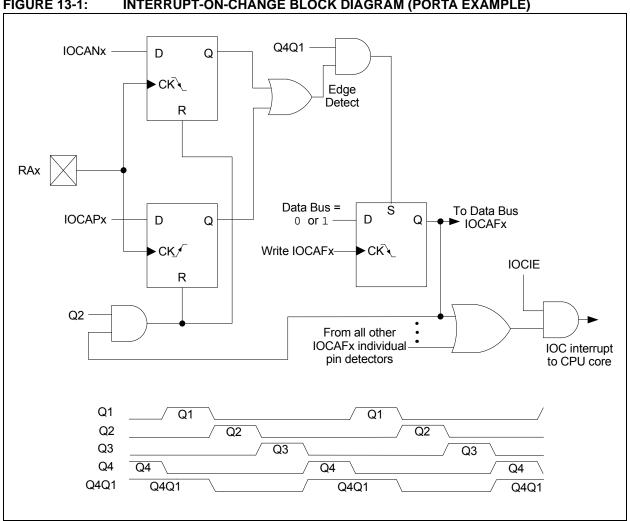

### 13.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-on-Change (IOC) pins. On the PIC16(L)F1829 devices, the PORTB pins can also be configured to operate as IOC pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

#### 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

#### 13.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

#### 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

#### 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

#### **FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM (PORTA EXAMPLE)**

#### Interrupt-on-Change Registers 13.6

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER (PIC16(L)F1829 ONLY)

| R/W-0/0                                                                                       | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0       | U-0 | U-0 | U-0   |

|-----------------------------------------------------------------------------------------------|---------|---------|---------|-----------|-----|-----|-------|

| IOCBN7                                                                                        | IOCBN6  | IOCBN5  | IOCBN4  |           |     |     | —     |

| bit 7                                                                                         |         |         |         |           |     |     | bit 0 |

|                                                                                               |         |         |         |           |     |     |       |

| Legend:                                                                                       |         |         |         |           |     |     |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                          |         |         |         |           |     |     |       |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |         |         |         | er Resets |     |     |       |

| '1' = Bit is set '0' = Bit is cleared                                                         |         |         |         |           |     |     |       |

IOCAN<7:4>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-change disabled for the associated pin.

bit 5-0 Unimplemented: Read as '0'

bit 7-4

#### REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER (PIC16(L)F1829 ONLY)

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | IOCBF<7:4>: Interrupt-on-Change PORTB Flag bits                                                  |

|---------|--------------------------------------------------------------------------------------------------|

|         | 1 = An enabled change was detected on the associated pin.                                        |

|         | Set when IOCBPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge |

|         | was detected on RBx.                                                                             |

|         | 0 = No change was detected, or the user cleared the detected change.                             |

| bit 5-0 | Unimplemented: Read as '0'                                                                       |

|         |                                                                                                  |

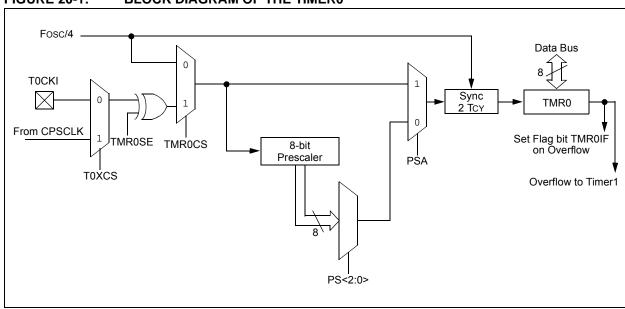

### 20.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

#### 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

#### FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

## PIC16(L)F1825/9

The  $\mathsf{I}^2\mathsf{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- Address Hold and Data Hold modes

- Selectable SDAx hold times

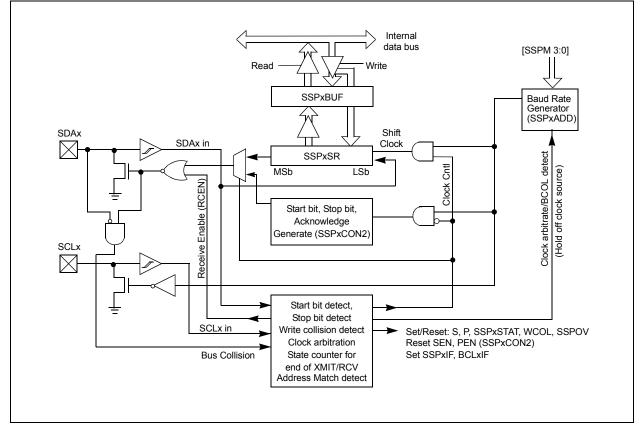

Figure 25-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 25-3 is a diagram of the  $I^2C$  interface module in Slave mode.

The PIC16F1829 has two MSSP modules, MSSP1 and MSSP2, each module operating independently from the other.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSP1CON1 and SSP1CON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

#### FIGURE 25-2: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

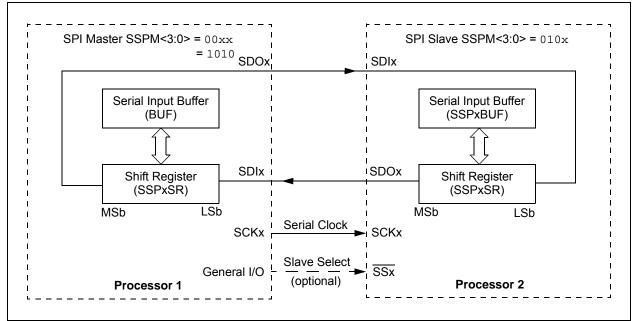

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device. MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

#### FIGURE 25-5: SPI MASTER/SLAVE CONNECTION

#### 25.4 I<sup>2</sup>C MODE OPERATION

All MSSPx I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 25.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

#### 25.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips I<sup>2</sup>C specification.

#### 25.4.3 SDAx AND SCLx PINS

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 25.4.4 SDAx HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

#### TABLE 25-2:I<sup>2</sup>C BUS TERMS

| TABLE 23-2:         | I-C BUS IERMS                                                                                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                      |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer,<br>generates clock signals and<br>terminates a transfer.                                                                                                   |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                     |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                                   |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCLx low to stall communication.                                                                                                                                   |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is<br>outputting and expected high<br>state.                                                                                     |

#### 25.5.1.3 Slave Reception

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV bit of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 25-4.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 25.2.3 "SPI Master Mode"** for more detail.

#### 25.5.1.4 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 25-14 and Figure 25-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the Master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

## 25.5.1.5 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^{2}C$  communcation. Figure 25-16 displays a module using both address and data holding. Figure 25-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to determine if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### 25.5.2.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 25-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- 7. Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the <u>ACK</u>.

13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

| BCF              | Bit Clear f                                                         |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               | BTFSS       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Syntax:          | [label] BRA label                                                                                                                                                                                                             | Syntax:     |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                      | Operands:   |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255                                                                                                                                                                                                   |             |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                          | Operation:  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 | Status Affe |

| Status Affected: | None                                                                                                                                                                                                                          | Descriptior |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |             |

| BRW              | Relative Branch with W                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                                 |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                 |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be $PC + 1 + (W)$ .<br>This instruction is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| TFSS           | Bit Test f, Skip if Set                                                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| yntax:         | [label]BTFSS f,b                                                                                                                                                                                                |

| perands:       | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| peration:      | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| atus Affected: | None                                                                                                                                                                                                            |

| escription:    | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

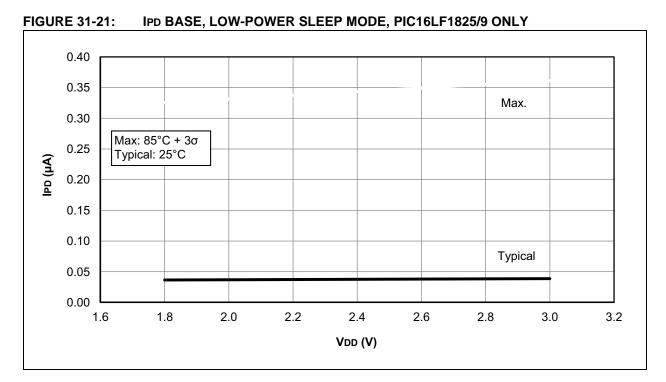

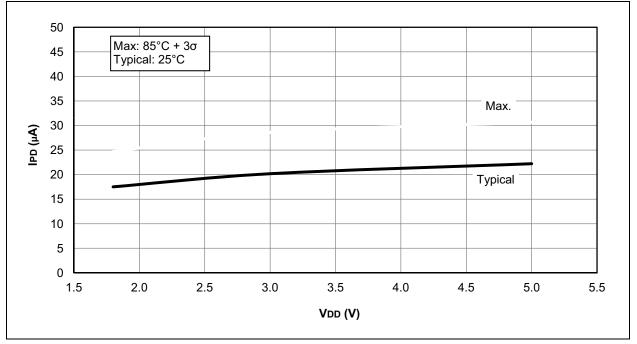

FIGURE 31-22: IPD BASE, LOW-POWER SLEEP MODE, PIC16F1825/9 ONLY

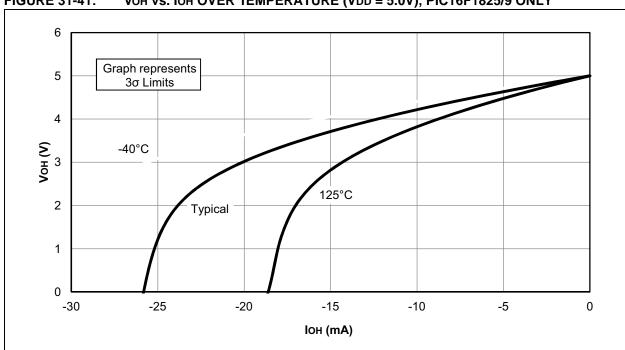

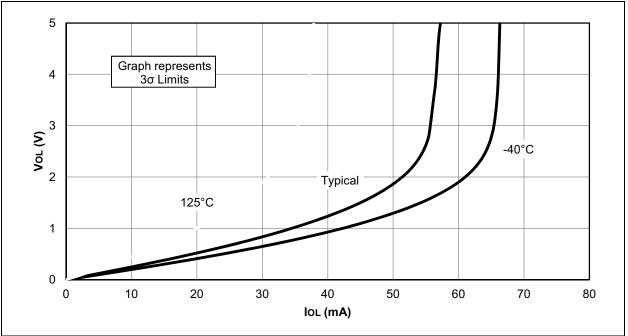

FIGURE 31-41: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V), PIC16F1825/9 ONLY

## PIC16(L)F1825/9

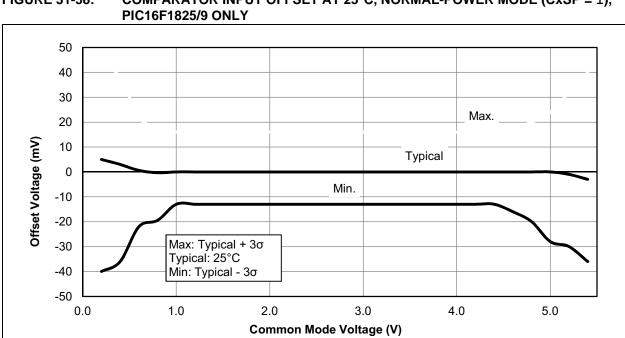

#### FIGURE 31-58: COMPARATOR INPUT OFFSET AT 25°C, NORMAL-POWER MODE (CxSP = 1),

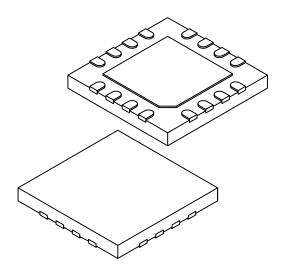

#### 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |      |      |

|-------------------------|-------------|-----------|------|------|

| Dimension Limits        |             | MIN       | NOM  | MAX  |

| Number of Pins          | N           | 16        |      |      |

| Pitch                   | е           | 0.65 BSC  |      |      |

| Overall Height          | Α           | 0.45      | 0.50 | 0.55 |

| Standoff                | A1          | 0.00      | 0.02 | 0.05 |

| Terminal Thickness      | A3          | 0.127 REF |      |      |

| Overall Width           | E           | 4.00 BSC  |      |      |

| Exposed Pad Width       | E2          | 2.50      | 2.60 | 2.70 |

| Overall Length          | D           | 4.00 BSC  |      |      |

| Exposed Pad Length      | D2          | 2.50      | 2.60 | 2.70 |

| Terminal Width          | b           | 0.25      | 0.30 | 0.35 |

| Terminal Length         | L           | 0.30      | 0.40 | 0.50 |

| Terminal-to-Exposed-Pad | К           | 0.20      | -    | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2