Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

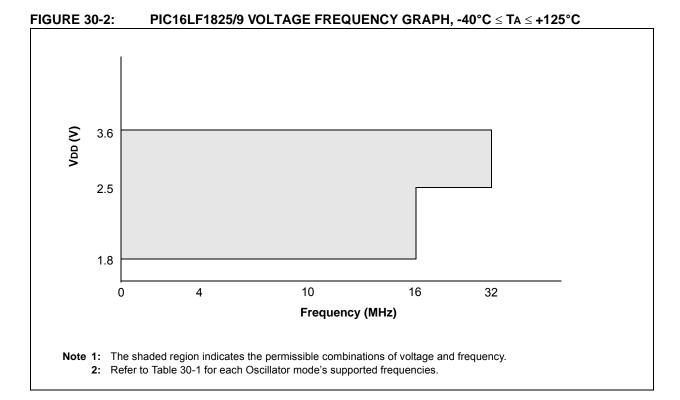

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE               | . 3-0.          | SPECIAL F                                                                                                     | UNCTION                                            | REGIST           | ER SUMI         |               |             | -D)     | 1      | 1                    | 1                               |

|---------------------|-----------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------|---------------|-------------|---------|--------|----------------------|---------------------------------|

| Address             | Name            | Bit 7                                                                                                         | Bit 6                                              | Bit 5            | Bit 4           | Bit 3         | Bit 2       | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3              | 1               |                                                                                                               |                                                    |                  |                 |               |             |         |        |                      |                                 |

| F80h <sup>(1)</sup> | INDF0           | DF0 Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                                    |                  |                 |               |             |         |        |                      | XXXX XXXX                       |

| F81h <sup>(1)</sup> | INDF1           | Addressing the (not a physic)                                                                                 |                                                    | es contents of   | FSR1H/FSR1      | 1L to address | data memory | ý       |        | XXXX XXXX            | XXXX XXXX                       |

| F82h <sup>(1)</sup> | PCL             | Program Cou                                                                                                   | inter (PC) Lea                                     | st Significant E | Byte            |               |             |         |        | 0000 0000            | 0000 0000                       |

| F83h <sup>(1)</sup> | STATUS          | _                                                                                                             | _                                                  | —                | TO              | PD            | Z           | DC      | С      | 1 1000               | q quuu                          |

| F84h <sup>(1)</sup> | FSR0L           | Indirect Data                                                                                                 | Memory Addr                                        | ess 0 Low Poi    | nter            |               |             | •       | •      | 0000 0000            | uuuu uuuu                       |

| F85h <sup>(1)</sup> | FSR0H           | Indirect Data                                                                                                 | Memory Addr                                        | ess 0 High Po    | inter           |               |             |         |        | 0000 0000            | 0000 0000                       |

| F86h <sup>(1)</sup> | FSR1L           | Indirect Data                                                                                                 | Memory Addr                                        | ess 1 Low Poi    | nter            |               |             |         |        | 0000 0000            | uuuu uuuu                       |

| F87h <sup>(1)</sup> | FSR1H           | Indirect Data                                                                                                 | Memory Addr                                        | ess 1 High Po    | inter           |               |             |         |        | 0000 0000            | 0000 0000                       |

| F88h <sup>(1)</sup> | BSR             |                                                                                                               | —                                                  | —                |                 |               | BSR<4:0>    |         |        | 0 0000               | 0 0000                          |

| F89h <sup>(1)</sup> | WREG            | Working Reg                                                                                                   | ister                                              |                  |                 |               |             |         |        | 0000 0000            | uuuu uuuu                       |

| F8Ah <sup>(1)</sup> | PCLATH          | _                                                                                                             | Write Buffer f                                     | or the upper 7   | bits of the Pro | ogram Counte  | er          |         |        | -000 0000            | -000 0000                       |

| F8Bh <sup>(1)</sup> | INTCON          | GIE                                                                                                           | PEIE                                               | TMR0IE           | INTE            | IOCIE         | TMR0IF      | INTF    | IOCIF  | 0000 0000            | 0000 0000                       |

| F8Ch                | —               | Unimplement                                                                                                   | ted                                                |                  |                 |               |             |         |        | -                    | _                               |

| FE3h                |                 |                                                                                                               |                                                    |                  |                 | -             |             |         |        |                      |                                 |

| FE4h                | STATUS_<br>SHAD | -                                                                                                             | _                                                  | —                | _               | _             | Z_SHAD      | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h                | WREG_<br>SHAD   | Working Reg                                                                                                   | ister Shadow                                       |                  |                 |               |             |         |        | 0000 0000            | uuuu uuuu                       |

| FE6h                | BSR_<br>SHAD    | —                                                                                                             | _                                                  | _                | Bank Select     | Register Sha  | dow         |         |        | x xxxx               | u uuuu                          |

| FE7h                | PCLATH_<br>SHAD | -                                                                                                             | Program Cou                                        | Inter Latch Hig  | h Register Sh   | nadow         |             |         |        | -xxx xxxx            | uuuu uuuu                       |

| FE8h                | FSR0L_<br>SHAD  | Indirect Data                                                                                                 | Memory Addr                                        | ess 0 Low Poi    | nter Shadow     |               |             |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE9h                | FSR0H_<br>SHAD  | Indirect Data                                                                                                 | Memory Addr                                        | ess 0 High Po    | inter Shadow    |               |             |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh                | FSR1L_<br>SHAD  | Indirect Data                                                                                                 | Indirect Data Memory Address 1 Low Pointer Shadow  |                  |                 |               |             |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEBh                | FSR1H_<br>SHAD  | Indirect Data                                                                                                 | Indirect Data Memory Address 1 High Pointer Shadow |                  |                 |               |             |         |        | XXXX XXXX            | uuuu uuuu                       |

| FECh                | —               | Unimplement                                                                                                   | Unimplemented                                      |                  |                 |               |             |         |        | _                    | -                               |

| FEDh                | STKPTR          | —                                                                                                             | _                                                  | _                | Current Stac    | k pointer     |             |         |        | 1 1111               | 1 1111                          |

| FEEh                | TOSL            | Top-of-Stack                                                                                                  | Low byte                                           |                  | 1               |               |             |         |        | xxxx xxxx            | uuuu uuuu                       |

| FEFh                | TOSE            | _                                                                                                             | Top-of-Stack                                       | Hiah byte        |                 |               |             |         |        | -xxx xxxx            |                                 |

|                     | 1030            |                                                                                                               |                                                    | • •              |                 |               |             |         |        |                      | auu uuu                         |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-8:**

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1829 only.

3: PIC16(L)F1825 only.

4: Unimplemented, read as '1'.

| EXAM                 | PLE 11-4:                                                              | ERASING ON                                   | E ROW OF PROGRAM MEMORY                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| ; This               | row erase                                                              | routine assumes                              | the following:                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| ; 1. A               | valid addr                                                             | ess within the                               | erase block is loaded in ADDRH:ADDRL                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| ; 2. A               | ; 2. ADDRH and ADDRL are located in shared data memory $0x70$ - $0x7F$ |                                              |                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF<br>BCF                  | EECON1,CFGS                                  |                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|                      | BSF                                                                    |                                              | ; Specify an erase operation                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                      | BSF                                                                    | EECON1,WREN                                  | ; Enable writes                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP                         | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor</pre> |  |  |  |  |  |  |  |  |  |

|                      | NOP                                                                    |                                              | ; halts to begin erase sequence<br>; Processor will stop here and wait for erase complete.                                                                                           |  |  |  |  |  |  |  |  |  |

|                      | BCF<br>BSF                                                             | EECON1, WREN<br>INTCON, GIE                  | <ul> <li>; after erase processor continues with 3rd instruction</li> <li>; Disable writes</li> <li>; Enable interrupts</li> </ul>                                                    |  |  |  |  |  |  |  |  |  |

|                      |                                                                        |                                              | -                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

## 11.7 EEPROM and Flash Control Registers

## REGISTER 11-1: EEDATL: EEPROM LOW BYTE DATA REGISTER

| R/W-x/u            | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u             | R/W-x/u |

|--------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                    |         |                      | EEDA    | T<7:0>            |                      |                     |         |

| bit 7              |         |                      |         |                   |                      |                     | bit 0   |

|                    |         |                      |         |                   |                      |                     |         |

| Legend:            |         |                      |         |                   |                      |                     |         |

| R = Readable bit   |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | 3                   |         |

| u = Bit is unchang | ed      | x = Bit is unknow    | n       | -n/n = Value at F | POR and BOR/Valu     | ue at all other Res | ets     |

| '1' = Bit is set   |         | '0' = Bit is cleared | I       |                   |                      |                     |         |

bit 7-0

-0 EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

#### REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | EEDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 11-3: EEADRL: EEPROM ADDRESS REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | EEADI   | R<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Logondy |         |         |         |         |         |         |         |

| Legend.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

## REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

**Note 1:** Unimplemented, read as '1'.

## 12.2 PORTA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-4). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-2 shows how to initialize a port.

Reading the PORTA register (Register 12-3) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLA register (Register 12-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1825/9-I/E" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 12.2.1 ANSELA REGISTER

The ANSELA register (Register 12-6) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### EXAMPLE 12-2: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

| — — LATA5 LATA4 — LATA2 LATA1 LATA0                 | I a manual. |     |         |         |     |         |         |         |

|-----------------------------------------------------|-------------|-----|---------|---------|-----|---------|---------|---------|

| — — LATA5 LATA4 — LATA2 LATA1 LATA0                 |             |     |         |         |     |         |         |         |

|                                                     | bit 7       |     |         |         |     |         |         | bit 0   |

| U-0 U-0 R/W-x/u R/W-x/u U-0 R/W-x/u R/W-x/u R/W-x/u | —           | —   | LATA5   | LATA4   | —   | LATA2   | LATA1   | LATA0   |

|                                                     | U-0         | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

### REGISTER 12-5: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0'                                |

bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

## REGISTER 12-6: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | —   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                                         |

| U-0                                     | U-0                               | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|-----------------------------------------|-----------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                                       |                                   | WPUA5             | WPUA4   | WPUA3                                                 | WPUA2   | WPUA1   | WPUA0   |  |  |

| bit 7                                   |                                   |                   |         |                                                       |         |         | bit 0   |  |  |

|                                         |                                   |                   |         |                                                       |         |         |         |  |  |

| Legend:                                 |                                   |                   |         |                                                       |         |         |         |  |  |

| R = Readable b                          | R = Readable bit W = Writable bit |                   |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                                   |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |                                   | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

## REGISTER 12-7: WPUA: WEAK PULL-UP PORTA REGISTER

| bit 7-6 | Unimplemented: Read as '0'                             |

|---------|--------------------------------------------------------|

| bit 5-0 | WPUA<5:0>: Weak Pull-up Register bits <sup>(1,2)</sup> |

|         | 1 = Pull-up enabled                                    |

|         | 0 = Pull-up disabled                                   |

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

## REGISTER 12-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits For RA<5:0> pins, respectively 1 = ST input used for port reads and interrupt-on-change 0 = TTL input used for port reads and interrupt-on-change

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA                | —       | _       | _       | ANSA4   | —       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| ANSELB <sup>(1)</sup> | —       | _       | ANSB5   | ANSB4   | —       | —       | _       | —       | 129                 |

| INLVLA                | _       | _       | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| INLVLB <sup>(1)</sup> | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 |         |         | -       |         | 129                 |

| INTCON                | GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF   | 87                  |

| IOCAF                 | _       | _       | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 138                 |

| IOCAN                 | —       | _       | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 138                 |

| IOCAP                 | _       |         | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 137                 |

| IOCBF <sup>(1)</sup>  | IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | —       | _       | _       | _       | 139                 |

| IOCBN <sup>(1)</sup>  | IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | _       |         | _       | _       | 139                 |

| IOCBP <sup>(1)</sup>  | IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | —       | —       | _       | —       | 138                 |

| TRISA                 | _       | _       | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISB <sup>(1)</sup>  | TRISB7  | TRISB6  | TRISB5  | TRISB4  | —       | —       | —       | —       | 128                 |

## TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — Unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

**Note 1:** PIC16(L)F1829 only.

## REGISTER 16-3: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u      |  |

|------------------|---------|-------------------|---------|------------------------------------|---------|---------|--------------|--|

|                  |         |                   | ADRE    | S<9:2>                             |         |         |              |  |

| bit 7            |         |                   |         |                                    |         |         | bit 0        |  |

|                  |         |                   |         |                                    |         |         |              |  |

| Legend:          |         |                   |         |                                    |         |         |              |  |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimplemented bit, read as '0' |         |         |              |  |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | n -n/n = Value at POR and E        |         |         | other Resets |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                    |         |         |              |  |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

## **REGISTER 16-4:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | 6<1:0>  | —       | —       | —       | —       | _       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

## 19.9 Interaction with ECCP Logic

In some devices, a comparator output signal can be used to trigger the auto-shutdown feature found within the ECCP module. When the ECCP auto-shutdown feature is enabled and a comparator output signal is selected as the source, the comparator can be used simultaneously as a general purpose comparator and as the ECCP auto-shutdown source. In addition, the comparator output signal can also be routed to the designated I/O pin. If the ECCP Auto-Restart mode is also enabled, the comparators can be used as a closed loop analog feedback circuit to the ECCP, thereby creating an analog controlled PWM.

Please see section

#### for more information.

**Note:** When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

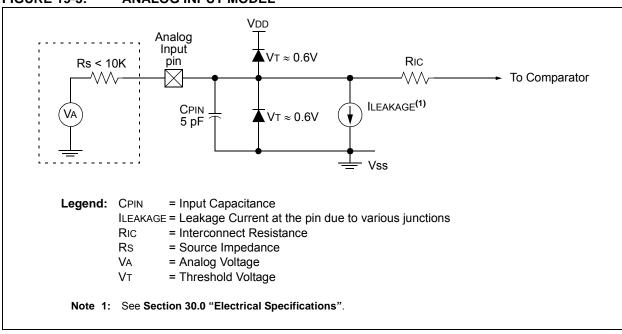

## FIGURE 19-3: ANALOG INPUT MODEL

## 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD.

If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| R/W-0/0                 | R-0/0                    | R/W-0/0                                  | R/W-0/0           | U-0             | R/W-1/1           | R/W-0/0         | R/W-0/0          |

|-------------------------|--------------------------|------------------------------------------|-------------------|-----------------|-------------------|-----------------|------------------|

| CxON                    | CxOUT                    | CxOE                                     | CxPOL             | _               | CxSP              | CxHYS           | CxSYNC           |

| bit 7                   |                          |                                          |                   |                 |                   |                 | bit 0            |

| Levende                 |                          |                                          |                   |                 |                   |                 |                  |

| Legend:<br>R = Readable | , hit                    | W = Writable                             | hit               | II – Unimple    | emented bit, read | d ac 'O'        |                  |

| u = Bit is unc          |                          | x = Bit is unkr                          |                   | •               | at POR and BC     |                 | other Pesets     |

| '1' = Bit is set        | •                        | '0' = Bit is cle                         |                   |                 |                   |                 |                  |

|                         |                          |                                          | urcu              |                 |                   |                 |                  |

| bit 7                   | CxON: Com                | parator Enable                           | bit               |                 |                   |                 |                  |

|                         |                          | ator is enabled                          |                   |                 |                   |                 |                  |

|                         | 0 = Compara              | ator is disabled                         | and consumes      | s no active pov | wer               |                 |                  |

| bit 6                   |                          | nparator Output                          |                   |                 |                   |                 |                  |

|                         |                          | (inverted polar                          | <u>ity):</u>      |                 |                   |                 |                  |

|                         | 1 = CxVP <<br>0 = CxVP > | -                                        |                   |                 |                   |                 |                  |

|                         |                          | ) (non-inverted p                        | <u>oolarity):</u> |                 |                   |                 |                  |

|                         | 1 = CxVP >               | -                                        | • •               |                 |                   |                 |                  |

|                         | 0 = CxVP <               | -                                        |                   |                 |                   |                 |                  |

| bit 5                   |                          | parator Output I                         |                   |                 |                   |                 |                  |

|                         |                          | is present on the<br>e pin. Not affected |                   | Requires that   | the associated T  | RIS bit be clea | ared to actually |

|                         |                          | is internal only                         |                   |                 |                   |                 |                  |

| bit 4                   |                          | nparator Output                          | Polarity Sele     | ct bit          |                   |                 |                  |

|                         |                          | ator output is inv                       | •                 |                 |                   |                 |                  |

|                         | 0 = Compara              | ator output is no                        | t inverted        |                 |                   |                 |                  |

| bit 3                   | Unimpleme                | nted: Read as '                          | 0'                |                 |                   |                 |                  |

| bit 2                   |                          | parator Speed/F                          |                   |                 |                   |                 |                  |

|                         |                          | ator operates in                         |                   |                 |                   |                 |                  |

|                         |                          | ator operates in                         |                   |                 | 9                 |                 |                  |

| bit 1                   |                          | nparator Hyster                          |                   | it              |                   |                 |                  |

|                         |                          | ator hysteresis ator hysteresis          |                   |                 |                   |                 |                  |

| bit 0                   |                          | omparator Outp                           |                   | us Mode bit     |                   |                 |                  |

|                         |                          |                                          | -                 |                 | ronous to chang   | ges on Timer1   | clock source     |

|                         | Output                   | updated on the                           | falling edge of   | Timer1 clock    | source.           | ,               |                  |

|                         | 0 = Compar               | ator output to T                         | imer1 and I/O     | pin is asynchr  | onous.            |                 |                  |

## REGISTER 19-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

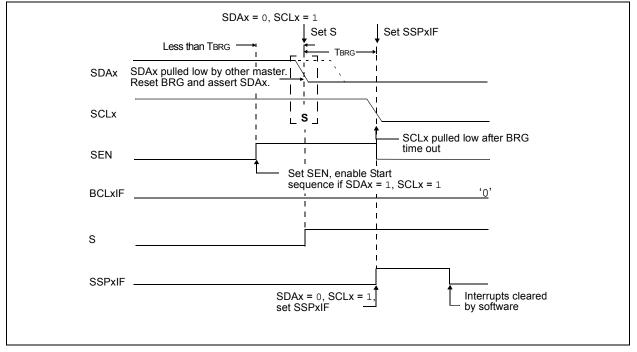

#### FIGURE 25-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

## 26.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 26-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 26.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 26-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 26.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

## 26.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 26.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 26.4.1.2 "Clock Polarity"**.

## 26.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

| U-0              | U-0                                 | U-0                                | U-0                  | R/W-0/0 <sup>(1)</sup> | R/W-0/0           | R/W-0/0          | R/W-0/0   |

|------------------|-------------------------------------|------------------------------------|----------------------|------------------------|-------------------|------------------|-----------|

| —                |                                     |                                    |                      |                        | CPSCI             | H<3:0>           |           |

| bit 7            |                                     |                                    |                      |                        |                   |                  | bit (     |

|                  |                                     |                                    |                      |                        |                   |                  |           |

| Legend:          |                                     |                                    |                      |                        |                   |                  |           |

| R = Readable I   | pit                                 | W = Writable b                     | it                   | U = Unimpleme          | ented bit, read a | is '0'           |           |

| u = Bit is uncha | anged                               | x = Bit is unkno                   | own                  | -n/n = Value at        | POR and BOR       | Value at all oth | er Resets |

| '1' = Bit is set |                                     | '0' = Bit is clea                  | red                  |                        |                   |                  |           |

|                  |                                     |                                    |                      |                        |                   |                  |           |

| bit 7-4          | Unimplement                         | ed: Read as '0'                    |                      |                        |                   |                  |           |

| bit 3-0          | CPSCH<3:0>                          | : Capacitive Sen                   | sing Channe          | el Select bits         |                   |                  |           |

|                  | <u>If CPSON = 0</u>                 |                                    |                      |                        |                   |                  |           |

|                  |                                     | s are ignored. N                   | o channel is         | selected.              |                   |                  |           |

|                  | $\frac{\text{If CPSON} = 1}{20000}$ |                                    | 20)                  |                        |                   |                  |           |

|                  |                                     | channel 0, (CPS<br>channel 1, (CPS | ,                    |                        |                   |                  |           |

|                  |                                     | channel 2, (CPS                    | ,                    |                        |                   |                  |           |

|                  |                                     | channel 3, (CPS                    |                      |                        |                   |                  |           |

|                  |                                     | channel 4, (CPS                    | ,                    |                        |                   |                  |           |

|                  |                                     | channel 5, (CPS                    | ,                    |                        |                   |                  |           |

|                  |                                     | channel 6, (CPS                    | ,                    |                        |                   |                  |           |

|                  |                                     | channel 7, (CPS                    |                      |                        |                   |                  |           |

|                  |                                     | channel 8, (CPS                    |                      |                        |                   |                  |           |

|                  | 1001 =                              | channel 9, (CPS                    | 59) <sup>(1)</sup>   |                        |                   |                  |           |

|                  | 1010 =                              | channel 10, (CF                    | PS10) <sup>(1)</sup> |                        |                   |                  |           |

|                  | 1011 =                              | channel 11, (CF                    | °S11) <sup>(1)</sup> |                        |                   |                  |           |

|                  | 1100 =                              | Reserved. Do n                     | ot use.              |                        |                   |                  |           |

|                  | •                                   |                                    |                      |                        |                   |                  |           |

|                  | •                                   |                                    |                      |                        |                   |                  |           |

|                  | •                                   |                                    |                      |                        |                   |                  |           |

|                  | 1111 =                              | Reserved. Do n                     | ot use.              |                        |                   |                  |           |

**Note 1:** These channels are only implemented on the PIC16(L)F1829.

| TABLE 27-3: | SUMM | REGISTER | S ASSOC | IATED WI | ТН САРА | CITIVE SE | NSING |  |

|-------------|------|----------|---------|----------|---------|-----------|-------|--|

|             |      |          |         |          |         |           |       |  |

| Name                  | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on<br>Page |

|-----------------------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA                | —                      | _                      | —       | ANSA4   | —       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| ANSELC                | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | —       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 134                 |

| CPSCON0               | CPSON                  | CPSRM                  | —       | _       | CPSRN   | IG<1:0> | CPSOUT  | T0XCS   | 315                 |

| CPSCON1               | —                      | _                      | —       | -       |         | CPSC    | H<3:0>  |         | 316                 |

| INLVLA                | _                      | _                      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6                | INLVLB5 | INLVLB4 | _       | _       | _       | _       | 129                 |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 135                 |

| INTCON                | GIE                    | PEIE                   | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF   | 87                  |

| OPTION_REG            | WPUEN                  | INTEDG                 | TMR0CS  | TMR0SE  | PSA     | PS2     | PS1     | PS0     | 176                 |

| T1CON                 | TMR1CS1                | TMR1CS0                | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC  | -       | TMR10N  | 185                 |

| TRISA                 | —                      | _                      | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5  | TRISB4  | _       | _       | _       | —       | 128                 |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 133                 |

Legend: — Unimplemented locations, read as '0'. Shaded cells are not used by the CPS module. Note 1: PIC16(L)F1829 only.

## 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1825/9 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 28.3 Common Programming Interfaces

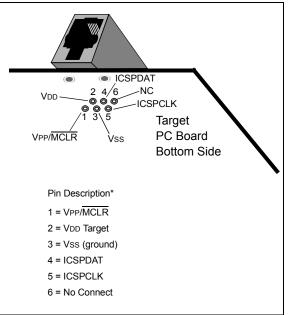

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

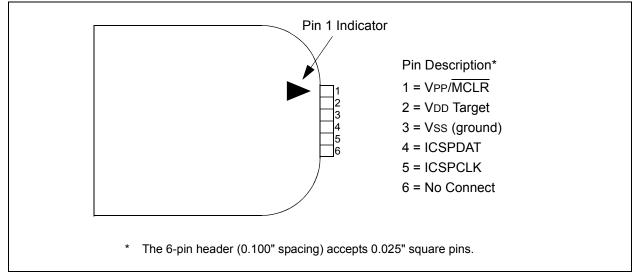

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

## FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

| TABLE 30-15: | SPI MODE REQUIREMENTS |

|--------------|-----------------------|

|--------------|-----------------------|

| Param<br>No. | Symbol                | Characteristic                      |                                    | Min.        | Тур† | Max. | Units | Conditions |

|--------------|-----------------------|-------------------------------------|------------------------------------|-------------|------|------|-------|------------|

| SP70*        | TssL2scH,<br>TssL2scL | SSx↓ to SCKx↓ or SCKx↑ input        |                                    | 2.25 TCY    |      | —    | ns    |            |

| SP71*        | TscH                  | SCKx input high time (Slave mo      | de)                                | Tcy + 20    | _    | —    | ns    |            |

| SP72*        | TscL                  | SCKx input low time (Slave mod      | e)                                 | Tcy + 20    | _    | —    | ns    |            |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDIx data input to    | SCKx edge                          | 100         |      | —    | ns    |            |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDIx data input to S   | ne of SDIx data input to SCKx edge |             |      | —    | ns    |            |

| SP75*        | TDOR                  | SDOx data output rise time          | 3.0-5.5V                           | —           | 10   | 25   | ns    |            |

|              |                       |                                     | 1.8-5.5V                           | —           | 25   | 50   | ns    |            |

| SP76*        | TDOF                  | SDOx data output fall time          |                                    | _           | 10   | 25   | ns    |            |

| SP77*        | TssH2doZ              | SSx↑ to SDOx output high-impe       | dance                              | 10          |      | 50   | ns    |            |

| SP78*        | TscR                  | SCKx output rise time               | 3.0-5.5V                           | _           | 10   | 25   | ns    |            |

|              |                       | (Master mode)                       | 1.8-5.5V                           | _           | 25   | 50   | ns    |            |

| SP79*        | TscF                  | SCKx output fall time (Master me    | ode)                               | _           | 10   | 25   | ns    |            |

| SP80*        | TscH2doV,             | SDOx data output valid after        | 3.0-5.5V                           | _           |      | 50   | ns    |            |

|              | TscL2DoV              | SCKx edge                           | 1.8-5.5V                           | _           |      | 145  | ns    |            |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDOx data output setup to SCKx edge |                                    | Тсу         |      | _    | ns    |            |

| SP82*        | TssL2doV              | SDOx data output valid after SS     | ↓ edge                             | _           | _    | 50   | ns    |            |

| SP83*        | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx edge               |                                    | 1.5Tcy + 40 |      | —    | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

\*

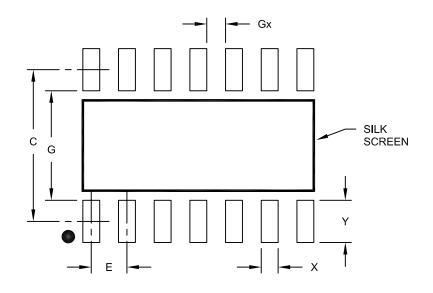

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |  |

|-----------------------|--------|-------------|------|------|--|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |  |

| Contact Pitch         |        | 1.27 BSC    |      |      |  |  |

| Contact Pad Spacing   | С      |             | 5.40 |      |  |  |

| Contact Pad Width     | X      |             |      | 0.60 |  |  |

| Contact Pad Length    | Y      |             |      | 1.50 |  |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |  |

| Distance Between Pads | G      | 3.90        |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

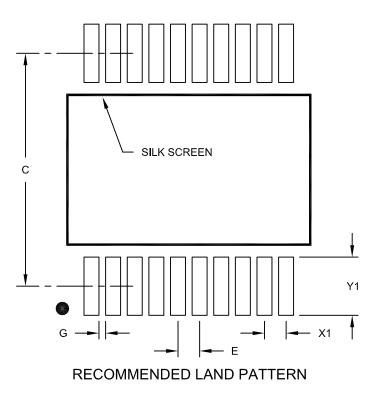

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν                | <b>ILLIMETER</b> | S        |      |

|--------------------------|------------------|------------------|----------|------|

| Dimension                | Dimension Limits |                  |          |      |

| Contact Pitch            | E                |                  | 0.65 BSC |      |

| Contact Pad Spacing      | С                |                  | 7.20     |      |

| Contact Pad Width (X20)  | X1               |                  |          | 0.45 |

| Contact Pad Length (X20) | Y1               |                  |          | 1.75 |

| Distance Between Pads    | G                | 0.20             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A