Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829-i-so |

TABLE 1-3: PIC16(L)F1829 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                | Function | Input<br>Type | Output<br>Type | Description                         |

|---------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------|

| RC2/AN6/CPS6/C12IN2-/                                               | RC2      | TTL           | CMOS           | General purpose I/O.                |

| P1D <sup>(1,2)</sup> /P2B <sup>(1,2)</sup> /MDCIN1                  | AN6      | AN            | _              | A/D Channel 6 input.                |

|                                                                     | CPS6     | AN            | _              | Capacitive sensing input 6.         |

|                                                                     | C12IN2-  | AN            | _              | Comparator C1 or C2 negative input. |

|                                                                     | P1D      | _             | CMOS           | PWM output.                         |

|                                                                     | P2B      | _             | CMOS           | PWM output.                         |

|                                                                     | MDCIN1   | ST            | _              | Modulator Carrier Input 1.          |

| RC3/AN7/CPS7/C12IN3-/                                               | RC3      | TTL           | CMOS           | General purpose I/O.                |

| P2A <sup>(1,2)</sup> /CCP2 <sup>(1,2)</sup> /P1C <sup>(1,2)</sup> / | AN7      | AN            | _              | A/D Channel 7 input.                |

| MDMIN                                                               | CPS7     | AN            | _              | Capacitive sensing input 7.         |

|                                                                     | C12IN3-  | AN            | _              | Comparator C1 or C2 negative input. |

|                                                                     | P2A      | _             | CMOS           | PWM output.                         |

|                                                                     | CCP2     | AN            | _              | Capture/Compare/PWM2.               |

|                                                                     | P1C      | _             | CMOS           | PWM output.                         |

|                                                                     | MDMIN    | ST            | _              | Modulator source input.             |

| RC4/C2OUT/SRNQ/P1B/TX <sup>(1)</sup> /                              | RC4      | TTL           | CMOS           | General purpose I/O.                |

| CK <sup>(1)</sup> /MDOUT                                            | C2OUT    | _             | CMOS           | Comparator C2 output.               |

|                                                                     | SRNQ     | _             | CMOS           | SR Latch inverting output.          |

|                                                                     | P1B      | _             | CMOS           | PWM output.                         |

|                                                                     | TX       | _             | CMOS           | USART asynchronous transmit.        |

|                                                                     | CK       | ST            | CMOS           | USART synchronous clock.            |

|                                                                     | MDOUT    | _             | CMOS           | Modulator output.                   |

| RC5/P1A/CCP1/DT <sup>(1)</sup> /RX <sup>(1)</sup> /                 | RC5      | TTL           | CMOS           | General purpose I/O.                |

| MDCIN2                                                              | P1A      | _             | CMOS           | PWM output.                         |

|                                                                     | CCP1     | ST            | CMOS           | Capture/Compare/PWM1.               |

|                                                                     | RX       | ST            | _              | USART asynchronous input.           |

|                                                                     | DT       | ST            | CMOS           | USART synchronous data.             |

|                                                                     | MDCIN2   | ST            | _              | Modulator Carrier Input 2.          |

| RC6/AN8/CPS8/CCP4/SS1                                               | RC6      | TTL           | CMOS           | General purpose I/O.                |

|                                                                     | AN8      | AN            | _              | A/D Channel 8 input.                |

|                                                                     | CPS8     | AN            | _              | Capacitive sensing input 8.         |

|                                                                     | CCP4     | AN            | _              | Capture/Compare/PWM4.               |

|                                                                     | SS1      | ST            | _              | Slave Select input.                 |

| RC7/AN9/CPS9/SDO1                                                   | RC7      | TTL           | CMOS           | General purpose I/O.                |

|                                                                     | AN9      | AN            | _              | A/D Channel 9 input.                |

|                                                                     | CPS9     | AN            | _              | Capacitive sensing input 9.         |

|                                                                     | SDO1     | _             | CMOS           | SPI data output.                    |

| VDD                                                                 | VDD      | Power         | _              | Positive supply.                    |

| Vss                                                                 | Vss      | Power         | _              | Ground reference.                   |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$  HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Default function location.

# REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| R-1/q  | R-0/q | R-q/q | R-0/q  | R-0/q  | R-q/q  | R-0/0  | R-0/q  |

|--------|-------|-------|--------|--------|--------|--------|--------|

| T10SCR | PLLR  | OSTS  | HFIOFR | HFIOFL | MFIOFR | LFIOFR | HFIOFS |

| bit 7  |       |       |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Conditional

bit 7 T10SCR: Timer1 Oscillator Ready bit

If T10SCEN = 1:

1 = Timer1 oscillator is ready

0 = Timer1 oscillator is not ready

If T1OSCEN = 0:

1 = Timer1 clock source is always ready

bit 6 PLLR 4xPLL Ready bit

1 = 4xPLL is ready

0 = 4xPLL is not ready

bit 5 OSTS: Oscillator Start-up Timer Status bit

1 = Running from the clock defined by the FOSC<2:0> bits of the Configuration Word 1

0 = Running from an internal oscillator (FOSC<2:0> = 100)

bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit

1 = HFINTOSC is ready

0 = HFINTOSC is not ready

bit 3 **HFIOFL:** High-Frequency Internal Oscillator Locked bit

1 = HFINTOSC is at least 2% accurate

0 = HFINTOSC is not 2% accurate

bit 2 MFIOFR: Medium-Frequency Internal Oscillator Ready bit

1 = MFINTOSC is ready

0 = MFINTOSC is not ready

bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit

1 = LFINTOSC is ready

0 = LFINTOSC is not ready

bit 0 **HFIOFS:** High-Frequency Internal Oscillator Stable bit

1 = HFINTOSC is at least 0.5% accurate

0 = HFINTOSC is not 0.5% accurate

# 8.6 Interrupt Control Registers

# 8.6.1 INTCON REGISTER

The INTCON register is a readable and writable register, that contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

Note:

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                              |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Enables all active interrupts                                                                                                                                                             |

|       | 0 = Disables all interrupts                                                                                                                                                                   |

| bit 6 | PEIE: Peripheral Interrupt Enable bit  1 = Enables all active peripheral interrupts  0 = Disables all peripheral interrupts                                                                   |

| bit 5 | <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit 1 = Enables the Timer0 interrupt 0 = Disables the Timer0 interrupt                                                                        |

| bit 4 | INTE: INT External Interrupt Enable bit  1 = Enables the INT external interrupt  0 = Disables the INT external interrupt                                                                      |

| bit 3 | IOCIE: Interrupt-on-Change Enable bit  1 = Enables the interrupt-on-change  0 = Disables the interrupt-on-change                                                                              |

| bit 2 | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                   |

| bit 1 | INTF: INT External Interrupt Flag bit  1 = The INT external interrupt occurred  0 = The INT external interrupt did not occur                                                                  |

| bit 0 | IOCIF: Interrupt-on-Change Interrupt Flag bit <sup>(1)</sup> 1 = When at least one of the interrupt-on-change pins changed state  0 = None of the interrupt-on-change pins have changed state |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCxF register have been cleared by software.

# 8.6.6 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 8-6.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 8-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-------|-------|---------|---------|---------|---------|

| TMR1GIF | ADIF    | RCIF  | TXIF  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  |

| bit 7   |         |       |       | •       |         |         | bit 0   |

Note:

| '                                                                                          | Legend:              |                      |                                                       |

|--------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------------------------------------|

| Dir. 1 1 DOD 100041 1 1 1 1 D                                                              | R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res | u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set '0' = Bit is cleared                                                      | '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                          |

|-------|------------------------------------------------------------------|

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                           |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                           |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                          |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 3 | <b>SSP1IF:</b> Synchronous Serial Port (MSSP) Interrupt Flag bit |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                                  |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                         |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                       |

|       | 1 = Interrupt is pending                                         |

|       | 0 = Interrupt is not pending                                     |

# 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 25.0 "Electrical Specifications"** for the LFINTOSC tolerances.

# 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word 1. See Table 10-1.

### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word 1 are set to '11', the WDT is always on.

WDT protection is active during Sleep.

### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word 1 are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

## 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word 1 are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

TABLE 10-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | ~              | Active      |

| 01        | 01 X   |                | Disabled    |

| 00        | Х      | Х              | Disabled    |

### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail event

- · WDT is disabled

- · Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

# 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. See **Section 3.0 "Memory Organization"** for more information.

**TABLE 10-2: WDT CLEARING CONDITIONS**

| Conditions                                               | WDT                          |  |  |

|----------------------------------------------------------|------------------------------|--|--|

| WDTE<1:0> = 00                                           |                              |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            | Cleared                      |  |  |

| WDTE<1:0> = 10 and enter Sleep                           |                              |  |  |

| CLRWDT Command                                           |                              |  |  |

| Oscillator Fail Detected                                 | ]                            |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |

#### REGISTER 12-1: **APFCONO: ALTERNATE PIN FUNCTION CONTROL REGISTER 0**

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0   |

|---------|---------|---------|-----|---------|---------|-----|-------|

| RXDTSEL | SDO1SEL | SS1SEL  | _   | T1GSEL  | TXCKSEL | -   | _     |

| bit 7   |         |         |     |         |         |     | bit 0 |

Legend:

R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit

u = Bit is unchanged -n/n = Value at POR and BOR/Value at all other Resets x = Bit is unknown

'1' = Bit is set '0' = Bit is cleared

bit 7 **RXDTSEL:** Pin Selection bit

For 14 Pin Devices (PIC16(L)F1825):

0 = RX/DT function is on RC5 RX/DT function is on RA1

For 20 Pin Devices (PIC16(L)F1829):

RX/DT function is on RB5 RX/DT function is on RC5

bit 6 SDO1SEL: Pin Selection bit

For 14 Pin Devices (PIC16(L)F1825):

0 = SDO1 function is on RC2 1 = SDO1 function is on RA4 For 20 Pin Devices (PIC16(L)F1829):

Bit is read-only, '0'

SDO1 function is always on RC7.

SS1SEL: Pin Selection bit bit 5

For 14 Pin Devices (PIC16(L)F1825):

SS1 function is on RC3  $1 = \overline{SS1}$  function is on RA3

For 20 Pin Devices (PIC16(L)F1829):

Bit is read-only, '0'

SS1 function is always on RC6.

bit 4 Unimplemented: Read as '0'

bit 3 T1GSEL: Pin Selection bit

> 0 = T1G function is on RA4 1 = T1G function is on RA3

bit 2 TXCKSEL: Pin Selection bit

For 14 Pin Devices (PIC16(L)F1825):

0 = TX/CK function is on RC4 1 = TX/CK function is on RA0

For 20 Pin Devices (PIC16(L)F1829):

0 = TX/CK function is on RB7 1 = TX/CK function is on RC4

bit 1-0 Unimplemented: Read as '0'

# 12.2.2 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

Analog input functions, such as ADC, comparator and Cap Sense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

**TABLE 12-2: PORTA OUTPUT PRIORITY**

| Pin Name | Function Priority <sup>(1)</sup>                                     |

|----------|----------------------------------------------------------------------|

| RA0      | ICSPDAT<br>ICDDAT<br>DACOUT                                          |

| RA1      | ICSPCLK<br>ICDCLK<br>RX/DT <sup>(2)</sup>                            |

| RA2      | SRQ<br>C1OUT<br>CCP3                                                 |

| RA3      | None (input only)                                                    |

| RA4      | CLKOUT<br>T10SO<br>CLKR<br>SDO1<br>P2B <sup>(2)</sup>                |

| RA5      | SDO2 (PIC16(L)F1829 only)<br>CCP2 <sup>(2)</sup> /P2A <sup>(2)</sup> |

Note 1: Priority listed from highest to lowest.

**2:** Pin function is selectable via the APFCON0 or APFCON1 register.

TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7   | Bit 6                  | Bit 5                  | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|------------------------|------------------------|-----------------------|---------|---------|---------|---------|---------------------|

| ANSELA     | _       | _                      |                        | ANSA4                 | _       | ANSA2   | ANSA1   | ANSA0   | 123                 |

| APFCON0    | RXDTSEL | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup>  | _                     | T1GSEL  | TXCKSEL | _       | _       | 118                 |

| APFCON1    | _       | _                      | SDO2SEL <sup>(1)</sup> | SS2SEL <sup>(1)</sup> | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL | 119                 |

| INLVLA     | _       | _                      | INLVLA5                | INLVLA4               | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| LATA       | _       | _                      | LATA5                  | LATA4                 | _       | LATA2   | LATA1   | LATA0   | 123                 |

| OPTION_REG | WPUEN   | INTEDG                 | TMR0CS                 | TMR0SE                | PSA     |         | PS<2:0> |         | 176                 |

| PORTA      | _       | _                      | RA5                    | RA4                   | RA3     | RA2     | RA1     | RA0     | 122                 |

| TRISA      | _       | _                      | TRISA5                 | TRISA4                | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 122                 |

| WPUA       | _       | _                      | WPUA5                  | WPUA4                 | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 124                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PIC16(L)F1829 only.

2: PIC16(L)F1825 only.

# TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|-----------|---------|------------------|

| CONFICA | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |           | CPD     | 40               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |            | FOSC<2:0> |         | 48               |

**Legend:** — Unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# 12.3 PORTB Registers (PIC16(L)F1829 only)

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-2 shows how to initialize a port.

Reading the PORTB register (Register 12-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The TRISB register (Register 12-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLB register (Register 12-14) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1825/9-I/E" for more information on threshold levels.

Note:

Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 12.3.1 ANSELB REGISTER

The ANSELB register (Register 12-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note:

The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

# 16.2 ADC Operation

## 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 16.2.6 "A/D Conversion Procedure".

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

**Note:** A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to

**TABLE 16-2: SPECIAL EVENT TRIGGER**

| Device          | CCPx/ECCPx |

|-----------------|------------|

| PIC16(L)F1825/9 | CCP4       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

#### 24.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 24.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

**TABLE 24-4:** SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

| Name    | Bit 7                  | Bit 6                             | Bit 5                      | Bit 4                 | Bit 3             | Bit 2      | Bit 1   | Bit 0   | Register on Page |  |  |

|---------|------------------------|-----------------------------------|----------------------------|-----------------------|-------------------|------------|---------|---------|------------------|--|--|

| APFCON1 | _                      | _                                 | SDO2SEL <sup>(2)</sup>     | SS2SEL <sup>(2)</sup> | P1DSEL            | P1CSEL     | P2BSEL  | CCP2SEL | 119              |  |  |

| CCP1CON | P1M<                   | P1M<1:0> <sup>(1)</sup> DC1B<1:0> |                            |                       |                   | CCP1M<3:0> |         |         |                  |  |  |

| CCP2CON | P2M<                   | 1:0> <sup>(1)</sup>               | DC2B                       | <1:0>                 |                   | CCP2M<3:0> |         |         |                  |  |  |

| CCP3CON | _                      | _                                 | DC3B                       | <1:0>                 |                   | CCP3M<     | :3:0>   |         | 224              |  |  |

| CCP4CON | _                      | _                                 | DC4B                       | <1:0>                 |                   | CCP4M<     | :3:0>   |         | 224              |  |  |

| CCPRxL  | Capture/Com            | pare/PWM Reg                      | gister x Low By            | te (LSB)              |                   |            |         |         | 202*             |  |  |

| CCPRxH  | Capture/Com            | pare/PWM Rec                      | Register x High Byte (MSB) |                       |                   |            |         |         | 202*             |  |  |

| INLVLA  | _                      | _                                 | INLVLA5                    | INLVLA4               | INLVLA3           | INLVLA2    | INLVLA1 | INLVLA0 | 124              |  |  |

| INLVLC  | INLVLC7 <sup>(2)</sup> | INLVLC6 <sup>(2)</sup>            | INLVLC5                    | INLVLC4               | INLVLC3           | INLVLC2    | INLVLC1 | INLVLC0 | 135              |  |  |

| INTCON  | GIE                    | PEIE                              | TMR0IE                     | INTE                  | IOCIE             | TMR0IF     | INTF    | IOCIF   | 87               |  |  |

| PIE1    | TMR1GIE                | ADIE                              | RCIE                       | TXIE                  | SSP1IE            | CCP1IE     | TMR2IE  | TMR1IE  | 88               |  |  |

| PIE2    | OSFIE                  | C2IE                              | C1IE                       | EEIE                  | BCL1IE            | ı          | _       | CCP2IE  | 89               |  |  |

| PIE3    |                        | _                                 | CCP4IE                     | CCP3IE                | TMR6IE            | 1          | TMR4IE  | _       | 90               |  |  |

| PIR1    | TMR1GIF                | ADIF                              | RCIF                       | TXIF                  | SSP1IF            | CCP1IF     | TMR2IF  | TMR1IF  | 92               |  |  |

| PIR2    | OSFIF                  | C2IF                              | C1IF                       | EEIF                  | BCL1IF            | ı          | _       | CCP2IF  | 93               |  |  |

| PIR3    |                        | _                                 | CCP4IF                     | CCP3IF                | TMR6IF            | 1          | TMR4IF  | _       | 94               |  |  |

| T1CON   | TMR10                  | S<1:0>                            | T1CKP                      | S<1:0>                | T10SCEN           | T1SYNC     | _       | TMR10N  | 185              |  |  |

| T1GCON  | TMR1GE                 | T1GPOL                            | T1GTM                      | T1GSPM                | T1GGO/DONE        | T1GVAL     | T1GS    | S<1:0>  | 186              |  |  |

| TMR1L   | Holding Regis          | ster for the Lea                  | st Significant B           | syte of the 16-b      | oit TMR1 Register | •          |         | •       | 181*             |  |  |

| TMR1H   | Holding Regis          | ster for the Mos                  | st Significant B           | yte of the 16-b       | it TMR1 Register  |            |         |         | 181*             |  |  |

| TRISA   | _                      | _                                 | TRISA5                     | TRISA4                | TRISA3            | TRISA2     | TRISA1  | TRISA0  | 122              |  |  |

| TRISC   | TRISC7 <sup>(2)</sup>  | TRISC6 <sup>(2)</sup>             | TRISC5                     | TRISC4                | TRISC3            | TRISC2     | TRISC1  | TRISC0  | 133              |  |  |

**Legend:** — Unimplemented location, read as '0'. Shaded cells are not used by Compare mode.

Applies to ECCP modules only. PIC16(L)F1829 only. PIC16(L)F1825 only. Note 1:

2:

3:

<sup>\*</sup> Page provides register information.

### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRIS bit.

- Load the PRx register with the PWM period value

- 3. Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2/4/6:

- Select the Timer2/4/6 resource to be used for PWM generation by setting the CxTSEL<1:0> bits in the CCPTMRS register.

- •Clear the TMRxIF interrupt flag bit of the PIRx register. See Note below.

- •Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- •Enable the Timer by setting the TMRxON bit of the TxCON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMRxIF bit of the PIRx register is set. See Note below.

- •Enable the CCPx pin output driver by clearing the associated TRIS bit.

Note: In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### 24.3.3 TIMER2/4/6 TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS register selects which Timer2/4/6 timer is used.

# 24.3.4 PWM PERIOD

The PWM period is specified by the PRx register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

### **EQUATION 24-1: PWM PERIOD**

$$PWM \ Period = [(PRx) + 1] \bullet 4 \bullet TOSC \bullet$$

$(TMRx \ Prescale \ Value)$

Note 1: Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

· TMRx is cleared

Note:

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

The Timer postscaler (see **Section 22.1** "**Timer2/4/6 Operation**") is not used in the determination of the PWM frequency.

### 24.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 24-2 is used to calculate the PWM pulse width.

Equation 24-3 is used to calculate the PWM duty cycle ratio.

# **EQUATION 24-2: PULSE WIDTH**

Pulse Width = (CCPRxL:CCPxCON<5:4>) •

TOSC • (TMRx Prescale Value)

## **EQUATION 24-3: DUTY CYCLE RATIO**

$Duty\ Cycle\ Ratio\ =\ \frac{(CCPRxL:CCPxCON<5:4>)}{4(PRx+1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 24-4).

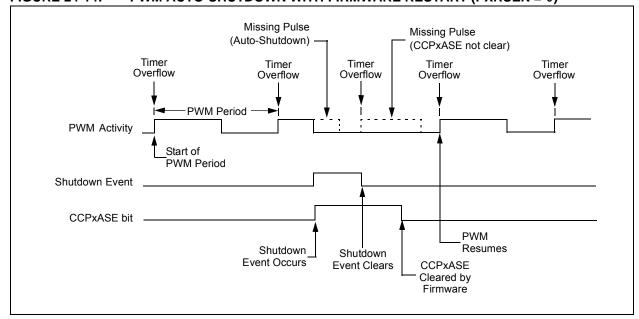

# 24.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the FLT0 pin

- A logic '1' on a Comparator (async\_CxOUT) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 24.4.4 "Auto-restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- · Drive logic '1'

- · Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit of the CCPxAS register is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or FLT0 pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The autorestart feature tracks the active status of a shutdown caused by a comparator output or FLT0 pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

FIGURE 24-14: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PXRSEN = 0)

# 26.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 26-3 contains the formulas for determining the baud rate. Example 26-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 26-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

# EXAMPLE 26-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

$$Desired \ Baud \ Rate = \frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$$

Solving for SPBRGH:SPBRGL:

$$X = \frac{Fosc}{\frac{Desired Baud Rate}{64}} - 1$$

$$= \frac{\frac{16000000}{9600}}{\frac{9600}{64}} - 1$$

$$= [25.042] = 25$$

$$Calculated Baud Rate = \frac{16000000}{64(25+1)}$$

$$= 9615$$

$$Error = \frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$$

$$= \frac{(9615 - 9600)}{9600} = 0.16\%$$

# TABLE 30-8: PIC16(L)F1825/9 A/D CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3)</sup>

Operating Conditions (unless otherwise stated)  $VDD = 3.0V, TA = 25^{\circ}C$ **Param** Svm. Characteristic Min. Typ† Max. Units Conditions No. AD01 NR Resolution 10 bit LSb AD02 EIL Integral Error ±1.7 **VREF = 3.0V** AD03 Differential Error **E**DL ±1 LSb No missing codes VREF = 3.0V LSb AD04 **E**OFF Offset Error ±2.5 **VREF = 3.0V** AD05 FGN Gain Error ±2.0 LSb VREF = 3.0VAD06 VREF Reference Voltage<sup>(4)</sup> 1.8 VDD ٧ VREF = (VREF+ minus VREF-) AD07 Full-Scale Range Vain Vss **V**REF ٧ AD08 ZAIN Recommended Impedance of 10  $k\Omega$ Can go higher if external 0.01µF capacitor is

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

present on input pin.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

Analog Voltage Source

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF, VDD pin or FVR, whichever is selected as reference input.

- 4: ADC Reference Voltage (REF+) is the selected input, VREF+ pin, VDD pin or the FVR Buffer1. When the FVR is selected as the reference input, the FVR Buffer1 output selection must be 2.048 or 4.096V (ADFVR<1:0> = 1x).

# TABLE 30-9: PIC16(L)F1825/9 A/D CONVERSION REQUIREMENTS

|              | Operating Conditions (unless otherwise stated)  VDD = 3.0V, TA = 25°C |                                                                 |      |      |      |       |                                        |  |  |

|--------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|--|--|

| Param<br>No. | Sym.                                                                  | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |  |  |

| AD130*       | TAD                                                                   | A/D Clock Period                                                | 1.0  | _    | 9.0  | μS    | Tosc-based                             |  |  |

|              |                                                                       | A/D Internal RC Oscillator<br>Period                            | 1.0  | 2.5  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |  |  |

| AD131        | TCNV                                                                  | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11   | _    | TAD   | Set GO/DONE bit to conversion complete |  |  |

| AD132*       | TACQ                                                                  | Acquisition Time                                                | _    | 5.0  | _    | μS    |                                        |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: The ADRES register may be read on the following TcY cycle.

## **TABLE 30-10: COMPARATOR SPECIFICATIONS**

Operating Conditions (unless otherwise stated)

$VDD = 3.0V, TA = 25^{\circ}C$

| Param<br>No. | Sym.                  | Characteristics                         | Min. | Тур. | Max. | Units | Comments                        |

|--------------|-----------------------|-----------------------------------------|------|------|------|-------|---------------------------------|

| CM01         | VIOFF                 | Input Offset Voltage <sup>(1)</sup>     | _    | ±7.5 | ±60  | mV    | High-Power mode<br>VICM = VDD/2 |

| CM02         | VICM                  | Input Common Mode Voltage               | 0    | _    | VDD  | V     |                                 |

| CM03         | CMRR                  | Common Mode Rejection Ratio             | _    | 50   | _    | dB    |                                 |

| CM04A        |                       | Response Time Rising Edge               | _    | 400  | 800  | ns    | High-Power mode                 |

| CM04B        | T <sub>RESP</sub> (1) | Response Time Falling Edge              | _    | 200  | 400  | ns    | High-Power mode                 |

| CM04C        | IKESP                 | Response Time Rising Edge               | _    | 1200 | _    | ns    | Low-Power mode                  |

| CM04D        |                       | Response Time Falling Edge              | _    | 550  | _    | ns    | Low-Power mode                  |

| CM05         | Тмс2оv                | Comparator Mode Change to Output Valid* | _    | _    | 10   | μS    |                                 |

| CM06         | CHYSTER               | Comparator Hysteresis <sup>(2)</sup>    | _    | 65   | _    | mV    | CxHYS = 1                       |

Note 1: High-Power mode only.

# TABLE 30-11: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| Operating Conditions (unless otherwise stated) VDD = 3.0V, TA = 25°C |      |                              |      |        |       |       |          |  |

|----------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|--|

| Param<br>No.                                                         | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |  |

| DAC01*                                                               | CLSB | Step Size <sup>(2)</sup>     | _    | VDD/32 |       | V     |          |  |

| DAC02*                                                               | CACC | Absolute Accuracy            | _    | _      | ± 1/2 | LSb   |          |  |

| DAC03*                                                               | CR   | Unit Resistor Value (R)      | _    | 5K     | _     | Ω     |          |  |

| DAC04*                                                               | CsT  | Settling Time <sup>(1)</sup> | _    | _      | 10    | μS    |          |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# TABLE 30-12: PIC16(L)F1825/9 LOW DROPOUT (LDO) REGULATOR CHARACTERISTICS:

|              | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                                |     |     |   |    |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|---|----|--|--|--|

| Param<br>No. | Sym.                                                                                                                                        | Characteristic Min. Typ† Max. Units Conditions |     |     |   |    |  |  |  |

| LD001        |                                                                                                                                             | LDO Regulation Voltage                         | _   | 3.2 | _ | V  |  |  |  |

| LD002        |                                                                                                                                             | LDO External Capacitor                         | 0.1 | _   | 1 | μF |  |  |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> Comparator Hysteresis is available when the CxHYS bit of the CMxCON0 register is enabled.

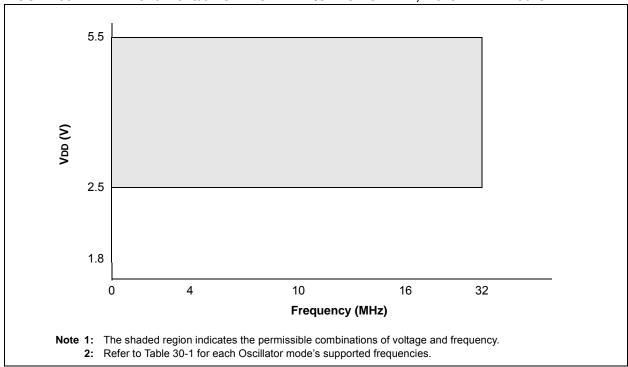

FIGURE 30-22: PIC16F1825/9 VOLTAGE FREQUENCY GRAPH, -40°C ≤TA ≤+150°C

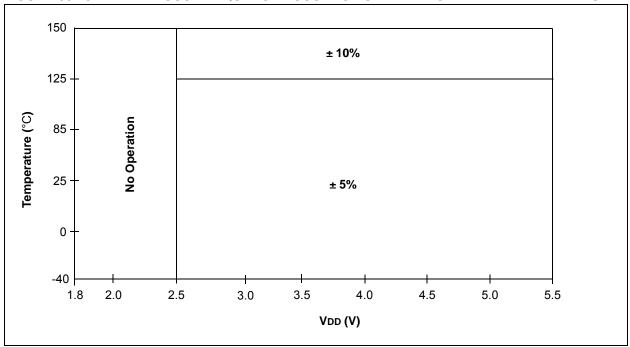

FIGURE 30-23: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

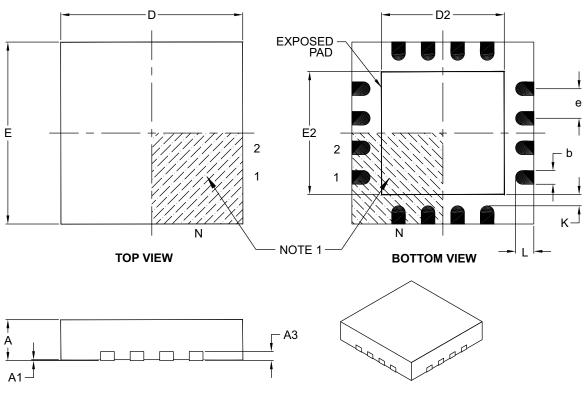

# 16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          |          |      |

|------------------------|------------------|----------|----------|------|

| Dime                   | Dimension Limits |          |          |      |

| Number of Pins         | N                |          | 16       |      |

| Pitch                  | е                |          | 0.65 BSC |      |

| Overall Height         | А                | 0.80     | 0.90     | 1.00 |

| Standoff               | A1               | 0.00     | 0.02     | 0.05 |

| Contact Thickness      | A3               | 0.20 REF |          |      |

| Overall Width          | E                | 4.00 BSC |          |      |

| Exposed Pad Width      | E2               | 2.50     | 2.65     | 2.80 |

| Overall Length         | D                |          | 4.00 BSC |      |

| Exposed Pad Length     | D2               | 2.50     | 2.65     | 2.80 |

| Contact Width          | b                | 0.25     | 0.30     | 0.35 |

| Contact Length         | L                | 0.30     | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20     | -        | _    |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-127B

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |          |      |  |

|-------------------------|--------|-------------|----------|------|--|

| Dimension               | Limits | MIN         | NOM      | MAX  |  |

| Number of Pins          | N      |             | 16       |      |  |

| Pitch                   | е      |             | 0.65 BSC |      |  |

| Overall Height          | Α      | 0.45        | 0.50     | 0.55 |  |

| Standoff                | A1     | 0.00        | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     | 0.127 REF   |          |      |  |

| Overall Width           | Е      |             | 4.00 BSC |      |  |

| Exposed Pad Width       | E2     | 2.50        | 2.60     | 2.70 |  |

| Overall Length          | D      |             | 4.00 BSC |      |  |

| Exposed Pad Length      | D2     | 2.50        | 2.60     | 2.70 |  |

| Terminal Width          | b      | 0.25        | 0.30     | 0.35 |  |

| Terminal Length         | L      | 0.30        | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K      | 0.20        | -        | -    |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device       | [X] -<br>Tape and Reel<br>Option                        | X<br> <br>Temperature<br>Range                                                                                                           | /XX<br> <br>Package  | XXX<br> <br>Pattern | Exai<br>a)<br>b) | mples:  PIC16F1825 - E/SL 301 = Extended temp., SOIC package, QTP pattern #301.  PIC16LF1829 - E/SS = Extended temp., SSOP package.                                                                                                                                                                                                               |

|--------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F1825, P<br>PIC16F1829T,                           |                                                                                                                                          |                      |                     | c)               | PIC16LF1829 - E/ML= Extended temp., QFN package.                                                                                                                                                                                                                                                                                                  |

| Tape and Reel<br>Option: | Blank = Standa<br>T = Tape and R                        | rd packaging (tube leel <sup>(1)</sup>                                                                                                   | or tray)             |                     |                  |                                                                                                                                                                                                                                                                                                                                                   |

| Temperature<br>Range:    |                                                         |                                                                                                                                          | dustrial)<br>tended) |                     |                  |                                                                                                                                                                                                                                                                                                                                                   |

| Package: <sup>(2)</sup>  | JQ = UQF ML = QFN P = Plas SL = SO(0 SO = SO(0 SS = SSC | FN, 20-lead (4x4x0.5<br>FN, 16-lead (4x4x0.5<br>II, 16-lead, 20-lead (itic DIP<br>C, 14-lead<br>C, 20-lead<br>IP, 20-lead<br>OP, 14-lead | īmm)                 |                     | Note             | catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.  2: For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or |

| Pattern:                 | QTP, SQTP, Co<br>(blank otherwis                        | ode or Special Requ<br>e)                                                                                                                | irements             |                     |                  | contact your local sales office.                                                                                                                                                                                                                                                                                                                  |