Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

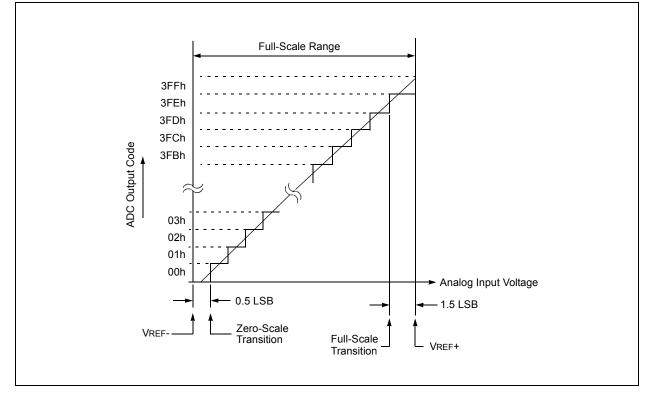

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

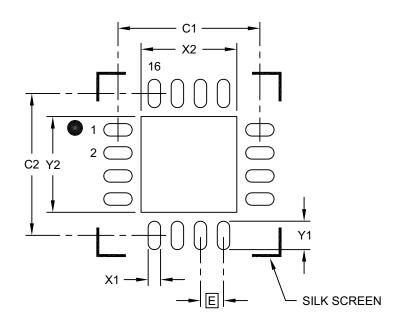

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

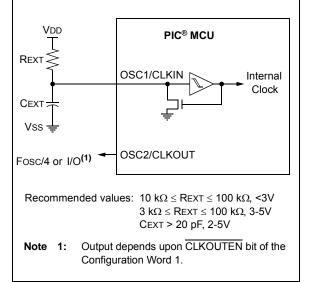

#### FIGURE 5-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

## 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Word 1 to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 5.3 "Clock Switching"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the state of the  $\overline{\text{CLKOUTEN}}$  bit in Configuration Word 1.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

Note: When FSCM is enabled, Two-Speed Start-up will automatically be enabled.

| Switch From             | Switch To                                                                     | Frequency                                       | Oscillator Delay                 |  |  |

|-------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|--|--|

| Sleep/POR               | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) |  |  |

| Sleep/POR               | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |  |  |

| LFINTOSC                | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |  |  |

| Sleep/POR               | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |  |  |

| Any clock source        | y clock source MFINTOSC <sup>(1)</sup> 31<br>HFINTOSC <sup>(1)</sup> 31       |                                                 | 2 μs (approx.)                   |  |  |

| Any clock source        | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |  |  |

| Any clock source        | Any clock source Timer1 Oscillator 32                                         |                                                 | 1024 Clock Cycles (OST)          |  |  |

| PLL inactive PLL active |                                                                               | 16-32 MHz                                       | 2 ms (approx.)                   |  |  |

Note 1: PLL inactive.

#### REGISTER 7-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u          | U-0                                                                                                                                                                                                                                                                                                 | U-0               | U-0  | U-0                                | U-0              | U-0               | R-q/u      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------------------------------------|------------------|-------------------|------------|--|

| SBOREN           | —                                                                                                                                                                                                                                                                                                   | —                 | —    | —                                  | —                | —                 | BORRDY     |  |

| bit 7            |                                                                                                                                                                                                                                                                                                     |                   |      |                                    | -                |                   | bit 0      |  |

|                  |                                                                                                                                                                                                                                                                                                     |                   |      |                                    |                  |                   |            |  |

| Legend:          |                                                                                                                                                                                                                                                                                                     |                   |      |                                    |                  |                   |            |  |

| R = Readable b   | oit                                                                                                                                                                                                                                                                                                 | W = Writable b    | oit  | U = Unimplemented bit, read as '0' |                  |                   |            |  |

| u = Bit is uncha | anged                                                                                                                                                                                                                                                                                               | x = Bit is unkn   | own  | -n/n = Value a                     | at POR and BOR   | /Value at all oth | ner Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                     | '0' = Bit is clea | ared | q = Value dep                      | ends on conditio | on                |            |  |

| bit 7<br>bit 6-1 | SBOREN: Software Brown-out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Word 1 ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR.<br><u>If BOREN &lt;1:0&gt; in Configuration Word 1 = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled<br>Unimplemented: Read as '0' |                   |      |                                    |                  |                   |            |  |

| bit 0            | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                 |                   |      |                                    |                  |                   |            |  |

### 8.6.9 PIR4 REGISTER<sup>(1)</sup>

The PIR4 register contains the interrupt flag bits, as shown in Register 8-9.

| Note 1: | The PIR4 register is available only on the |

|---------|--------------------------------------------|

|         | PIC16(L)F1829 device.                      |

2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## **REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | —   | _   | —   | —   | BCL2IF     | SSP2IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Bit is set by hardware                           |

| Unimplemented: Read as '0'                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCL2IF: MSSP2 Bus Collision Interrupt Flag bit                                                                                                                                |

| 1 = A Bus Collision was detected (must be cleared in software)                                                                                                                |

| 0 = No Bus collision was detected                                                                                                                                             |

| SSP2IF: Master Synchronous Serial Port 2 (MSSP2) Interrupt Flag bit                                                                                                           |

| <ul> <li>1 = The Transmission/Reception/Bus Condition is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive/Bus Condition in progress</li> </ul> |

|                                                                                                                                                                               |

**Note 1:** This register is only available on PIC16(L)F1829.

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name                | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|---------------------|---------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| INTCON              | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 87                  |

| OPTION_REG          | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 176                 |

| PIE1                | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 88                  |

| PIE2                | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE |         |        | CCP2IE | 89                  |

| PIE3                | —       |        | CCP4IE | CCP3IE | TMR6IE | -       | TMR4IE | _      | 90                  |

| PIE4 <sup>(1)</sup> | —       | -      | -      | -      | _      | _       | BCL2IE | SSP2IE | 91                  |

| PIR1                | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 92                  |

| PIR2                | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | _       | _      | CCP2IF | 93                  |

| PIR3                | _       | —      | CCP4IF | CCP3IF | TMR6IF | _       | TMR4IF | _      | 94                  |

| PIR4 <sup>(1)</sup> | _       | _      | _      | _      | _      | _       | BCL2IF | SSP2IF | 95                  |

Legend: — Unimplemented locations read as '0'. Shaded cells are not used by interrupts.

**Note 1:** PIC16(L)F1829 only.

| REGISTER 12-18: | ANSELC: PORTC ANALOG SELECT REGISTER |  |

|-----------------|--------------------------------------|--|

|                 |                                      |  |

| R/W-1/1                                 | R/W-1/1                                                                                                                                                                                                                                                                                                           | U-0                                                   | U-0              | R/W-1/1                                               | R/W-1/1          | R/W-1/1  | R/W-1/1                 |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------------------------------------------------------|------------------|----------|-------------------------|--|

| ANSC7 <sup>(2)</sup>                    | ANSC6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                              | _                                                     |                  | ANSC3                                                 | ANSC2            | ANSC1    | ANSC0                   |  |

| bit 7                                   | -                                                                                                                                                                                                                                                                                                                 |                                                       | •                | ·                                                     |                  | •        | bit 0                   |  |

|                                         |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                                                       |                  |          |                         |  |

| Legend:                                 |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                                                       |                  |          |                         |  |

| R = Readable                            | bit                                                                                                                                                                                                                                                                                                               | W = Writable                                          | bit              | U = Unimpler                                          | nented bit, read | d as '0' |                         |  |

| u = Bit is unchanged x = Bit is unknown |                                                                                                                                                                                                                                                                                                                   |                                                       | nown             | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |                         |  |

| '1' = Bit is set                        |                                                                                                                                                                                                                                                                                                                   | '0' = Bit is cle                                      | ared             |                                                       |                  |          |                         |  |

| bit 7-6                                 | 0 = Digital I/                                                                                                                                                                                                                                                                                                    | Analog Select<br>O. Pin is assigr<br>nput. Pin is ass | ned to port or d | ligital special fu                                    | inction.         |          | ectively <sup>(2)</sup> |  |

| bit 5-4                                 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |                                                       |                  |                                                       |                  |          |                         |  |

| bit 3-0                                 | <ul> <li>ANSC&lt;3:0&gt;: Analog Select between Analog or Digital Function on pins RC&lt;3:0&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |                                                       |                  |                                                       |                  |          |                         |  |

|                                         |                                                                                                                                                                                                                                                                                                                   |                                                       |                  |                                                       |                  |          |                         |  |

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

## REGISTER 12-19: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                | •                    |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

- 3: WPUC<7:6> available on PIC16(L)F1829 only. Otherwise, they are unimplemented and read as '0'.

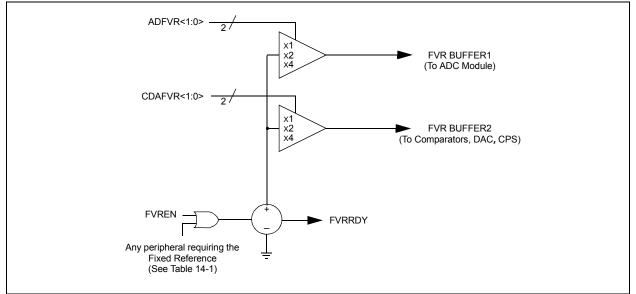

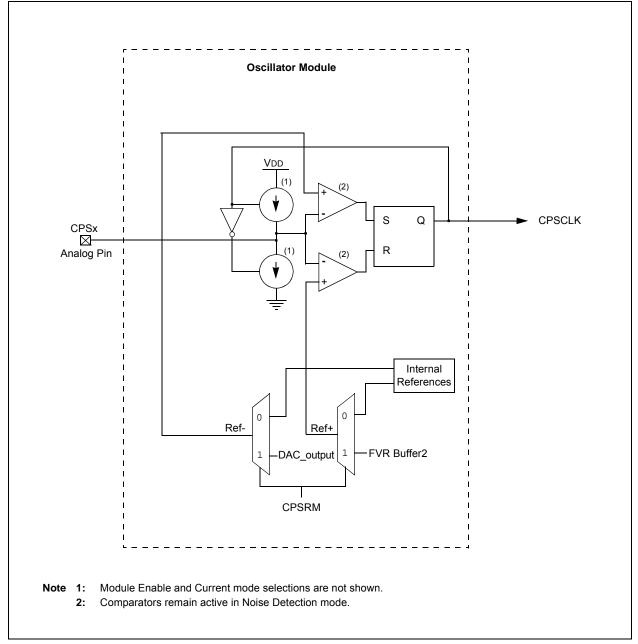

# 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

- Capacitive Sensing (CPS) module

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, DAC and CPS are routed through two independent programmable gain amplifiers. Each amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC, CPS and comparator module. Reference **Section 17.0** "**Digital-to-Analog Converter (DAC) Module**" and **Section 19.0** "**Comparator Module**" for additional information.

## 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 30.0** "**Electrical Specifications**" for the minimum delay requirement.

#### FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

# 14.3 FVR Control Registers

## REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0          | R-q/q                                        | R/W-0/0                                                    | R/W-0/0                                         | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                              | R/W-0/0                                               | R/W-0/0      |

|------------------|----------------------------------------------|------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|

| FVREN            | FVRRDY <sup>(1)</sup>                        | TSEN                                                       | TSRNG                                           | CDAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /R<1:0>                                                                                              | ADFVI                                                 | R<1:0>       |

| bit 7            |                                              |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                       | bit (        |

|                  |                                              |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                       |              |

| Legend:          |                                              |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                       |              |

| R = Readable     | bit                                          | W = Writable                                               | bit                                             | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nented bit, read                                                                                     | as '0'                                                |              |

| u = Bit is unch  | anged                                        | x = Bit is unkr                                            | nown                                            | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | at POR and BOI                                                                                       | R/Value at all c                                      | other Resets |

| '1' = Bit is set |                                              | '0' = Bit is cle                                           | ared                                            | q = Value dep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | pends on condit                                                                                      | on                                                    |              |

| bit 7            | 0 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc<br>Itage Referenc         | e is disabled                                   | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |                                                       |              |

| bit 6            | 0 = Fixed Vo                                 | ed Voltage Ref<br>Itage Referenc<br>Itage Referenc         | e output is no                                  | t ready or not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nabled                                                                                               |                                                       |              |

| bit 5            | 0 = Tempera                                  | erature Indicato<br>ture indicator is<br>ture indicator is | s disabled                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |                                                       |              |

| bit 4            | 0 = VOUT = V                                 | perature Indica<br>′DD - 2VT (Low<br>′DD - 4VT (High       | Range)                                          | election bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      |                                                       |              |

| bit 3-2          | 00 = Compara<br>01 = Compara<br>10 = Compara | ator and DAC I<br>ator and DAC I<br>ator and DAC I         | Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage | Reference Per<br>Reference Per<br>Reference Per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ference Selectic<br>ipheral output is<br>ipheral output is<br>ipheral output is<br>ipheral output is | s off<br>s 1x (1.024V)<br>s 2x (2.048V) <sup>(2</sup> |              |

| bit 1-0          | 00 = ADC Fix<br>01 = ADC Fix<br>10 = ADC Fix | ed Voltage Re<br>ed Voltage Re<br>ed Voltage Re            | ference Perip<br>ference Perip<br>ference Perip | nce Selection theral output is the formation of the forma | off<br>1x (1.024V)<br>2x (2.048V) <b>(2)</b>                                                         |                                                       |              |

|                  | RRDY is always<br>ed Voltage Refe            |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /9).                                                                                                 |                                                       |              |

3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |       | ADFVF | R<1:0> | 142                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

## 22.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 modules is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 22.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMRx register

- · a write to the TxCON register

- · Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMRx is not cleared when TxCON is written.

#### 22.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIRx register. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIEx register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

#### 22.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode. Additional information is provided in Section 25.0 "Master Synchronous Serial Port (MSSP1 and MSSP2) Module".

## 22.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

# 23.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

## 23.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

#### 23.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

## 23.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDMSODIS bit in the MDSRC register.

#### 23.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

# 23.10 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

### 23.11 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

## 23.12 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PRx register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2/4/6:

- •Select the Timer2/4/6 resource to be used for PWM generation by setting the CxTSEL<1:0> bits in the CCPTMRS register.

- •Clear the TMRxIF interrupt flag bit of the PIRx register. See Note below.

- •Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- •Enable the Timer by setting the TMRxON bit of the TxCON register.

- 6. Enable PWM output pin:

- •Wait until the Timer overflows and the TMRxIF bit of the PIRx register is set. See Note below.

- •Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

# 24.3.3 TIMER2/4/6 TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS register selects which Timer2/4/6 timer is used.

#### 24.3.4 PWM PERIOD

The PWM period is specified by the PRx register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

# EQUATION 24-1: PWM PERIOD

$PWM Period = [(PRx) + 1] \bullet 4 \bullet TOSC \bullet$ (TMRx Prescale Value)

**Note 1:** Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- TMRx is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 22.1 "Timer2/4/6 Operation") is not used in the determination of the PWM frequency.

#### 24.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 24-2 is used to calculate the PWM pulse width.

Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 24-2: PULSE WIDTH

$$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$$

TOSC • (TMRx Prescale Value)

# EQUATION 24-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PRx+1)}$$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 24-4).

# 25.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP1 AND MSSP2) MODULE

### 25.1 Master SSPx (MSSPx) Module Overview

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- · Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

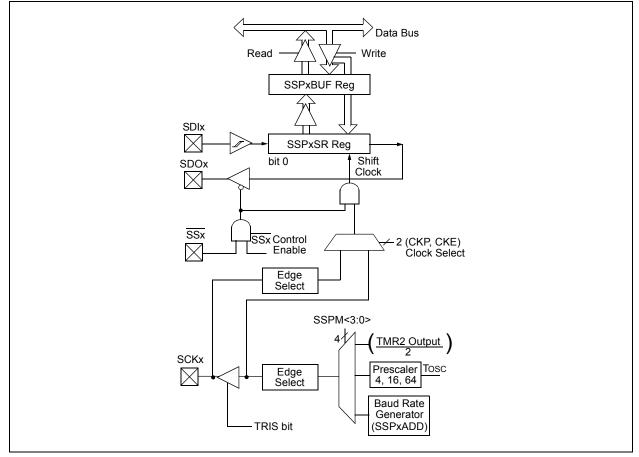

Figure 25-1 is a block diagram of the SPI interface module.

#### FIGURE 25-1: MSSPx BLOCK DIAGRAM (SPI MODE)

#### 25.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

| Name                  | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4                  | Bit 3   | Bit 2   | Bit 1                  | Bit 0                  | Register on<br>Page |

|-----------------------|------------------------|------------------------|------------------------|------------------------|---------|---------|------------------------|------------------------|---------------------|

| ANSELA                | —                      | _                      | _                      | ANSA4                  | _       | ANSA2   | ANSA1                  | ANSA0                  | 122                 |

| ANSELB <sup>(1)</sup> | —                      | _                      | ANSB5                  | ANSB4                  | _       | _       | _                      | _                      | 129                 |

| ANSELC                | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _                      | _                      | ANSC3   | ANSC2   | ANSC1                  | ANSC0                  | 134                 |

| APFCON0               | RXDTSEL                | SDO1SEL <sup>(2)</sup> | SS1SEL <sup>(2)</sup>  | _                      | T1GSEL  | TXCKSEL | _                      | —                      | 118                 |

| APFCON1               | —                      | -                      | SDO2SEL <sup>(1)</sup> | SS2SEL <sup>(1)</sup>  | P1DSEL  | P1CSEL  | P2BSEL                 | CCP2SEL                | 119                 |

| INLVLA                | —                      | -                      | INLVLA5 <sup>(1)</sup> | INLVLA4 <sup>(1)</sup> | INLVLA3 | INLVLA2 | INLVLA1                | INLVLA0                | 124                 |