Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.1.11-                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829t-i-gz |

#### **Peripheral Highlights (Continued)**

- · Data Signal Modulator Module:

- Selectable modulator and carrier sources

- · SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

PIC12(L)F1822/1840/PIC16(L)F182x/1847 Family Types

| 1 10 12(2): 102 |                  |                                 | <del>-/: :0</del> -    |                      |                      | ····· <i>y</i>  | .,            |             |                      |        |                               |                                                 |          |                      |     |

|-----------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|-------------------------------|-------------------------------------------------|----------|----------------------|-----|

| Device          | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O,8 <sub>(2)</sub> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> CTM/SPI) | ECCP (Full-Bridge)<br>ECCP (Half-Bridge)<br>CCP | SR Latch | Debug <sup>(1)</sup> | ХГР |

| PIC12(L)F1822   | (1)              | 2K                              | 256                    | 128                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC12(L)F1840   | (2)              | 4K                              | 256                    | 256                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1823   | (1)              | 2K                              | 256                    | 128                  | 12                   | 8               | 8             | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1824   | (3)              | 4K                              | 256                    | 256                  | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1825   | (4)              | 8K                              | 256                    | 1024                 | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1826   | (5)              | 2K                              | 256                    | 256                  | 16                   | 12              | 12            | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1827   | (5)              | 4K                              | 256                    | 384                  | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1828   | (3)              | 4K                              | 256                    | 256                  | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1829   | (4)              | 8K                              | 256                    | 1024                 | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1847   | (6)              | 8K                              | 256                    | 1024                 | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

3: DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

#### 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP}$  = 0, external reads and writes of program memory are inhibited and a read will return all 'o's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See Section 4.3 "Write Protection" for more information.

#### 4.2.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

#### 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 11.5 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16F/LF182X/PIC12F/LF1822 Memory Programming Specification" (DS41390).

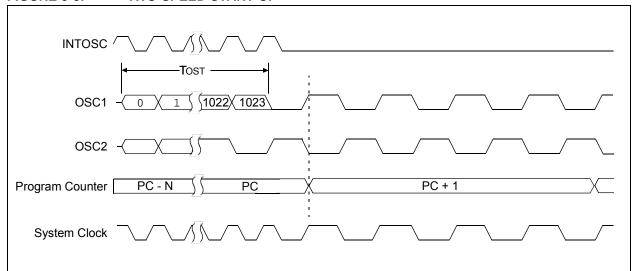

### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- System clock is switched to external clock source.

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

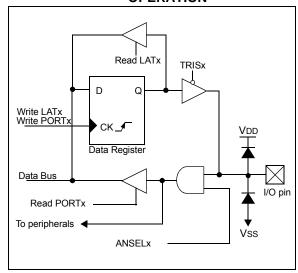

#### 12.0 I/O PORTS

Depending on the device selected and peripherals enabled, there are up to two ports available. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

- · INLVLx (input level control)

TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1825 | •     |       | •     |

| PIC16(L)F1829 | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

### FIGURE 12-1: GENERIC I/O PORT OPERATION

#### **EXAMPLE 12-1: INITIALIZING PORTA**

```

; This code example illustrates

; initializing the PORTA register. The

; other ports are initialized in the same

; manner.

BANKSEL PORTA

CLRF

PORTA

;Init PORTA

BANKSEL LATA

;Data Latch

CLRF

T.ATA

BANKSEL ANSELA

;digital I/O

CLRF

ANSELA

BANKSEL TRISA

B'00111000'

MOVLW

;Set RA<5:3> as inputs

MOVWF

;and set RA<2:0> as

TRISA

;outputs

```

#### 13.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-on-Change (IOC) pins. On the PIC16(L)F1829 devices, the PORTB pins can also be configured to operate as IOC pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-change enable (Master Switch)

- · Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

#### 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

#### 13.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

#### 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

# EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

#### 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

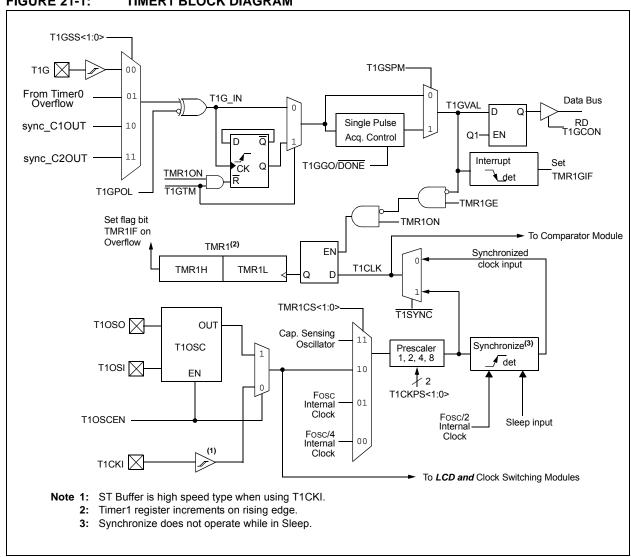

## 21.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP/ECCP)

- · Selectable Gate Source Polarity

- · Gate Toggle Mode

- · Gate Single-pulse Mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 21-1 is a block diagram of the Timer1 module.

#### FIGURE 21-1: TIMER1 BLOCK DIAGRAM

#### REGISTER 23-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

| R/W-x/u   | R/W-x/u | R/W-x/u  | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------|---------|----------|-----|---------|---------|---------|---------|

| MDCHODIS  | MDCHPOL | MDCHSYNC | _   |         | MDCH    | l<3:0>  |         |

| bit 7 bit |         |          |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| I - Dit is set | o – Bit is cicared                                                                                                      |

|----------------|-------------------------------------------------------------------------------------------------------------------------|

|                |                                                                                                                         |

| bit 7          | MDCHODIS: Modulator High Carrier Output Disable bit                                                                     |

|                | 1 = Output signal driving the peripheral output pin (selected by MDCH<3:0>) is disabled                                 |

|                | 0 = Output signal driving the peripheral output pin (selected by MDCH<3:0>) is enabled                                  |

| bit 6          | MDCHPOL: Modulator High Carrier Polarity Select bit                                                                     |

|                | 1 = Selected high carrier signal is inverted                                                                            |

|                | 0 = Selected high carrier signal is not inverted                                                                        |

| bit 5          | MDCHSYNC: Modulator High Carrier Synchronization Enable bit                                                             |

|                | 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the low time carrier |

|                | 0 = Modulator Output is not synchronized to the high time carrier signal <sup>(1)</sup>                                 |

| bit 4          | Unimplemented: Read as '0'                                                                                              |

| bit 3-0        | MDCH<3:0> Modulator Data High Carrier Selection bits (1)                                                                |

|                | 1111 = Reserved. No channel connected.                                                                                  |

|                | •                                                                                                                       |

|                | •                                                                                                                       |

|                | 1000 = Reserved. No channel connected.                                                                                  |

|                | 0111 = CCP4 output (PWM Output mode only)                                                                               |

|                | 0110 = CCP3 output (PWM Output mode only)                                                                               |

|                | 0101 = CCP2 output (PWM Output mode only)                                                                               |

|                | 0100 = CCP1 output (PWM Output mode only)                                                                               |

|                | 0011 = Reference Clock module signal (CLKR)                                                                             |

|                | 0010 = MDCIN2 port pin                                                                                                  |

|                | 0001 = MDCIN1 port pin                                                                                                  |

|                | 0000 = Vss                                                                                                              |

**Note 1:** Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

| R/W-x/u  | R/W-x/u | R/W-x/u  | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------|---------|----------|-----|---------|---------|---------|---------|

| MDCLODIS | MDCLPOL | MDCLSYNC | _   |         | MDCL    | <3:0>   |         |

| bit 7    |         |          |     |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 MDCLODIS: Modulator Low Carrier Output Disable bit

1 = Output signal driving the peripheral output pin (selected by MDCL<3:0> of the MDCARL register) is disabled

0 = Output signal driving the peripheral output pin (selected by MDCL<3:0> of the MDCARL register) is enabled

bit 6 MDCLPOL: Modulator Low Carrier Polarity Select bit

1 = Selected low carrier signal is inverted

0 = Selected low carrier signal is not inverted

bit 5 MDCLSYNC: Modulator Low Carrier Synchronization Enable bit

1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high time carrier

0 = Modulator Output is not synchronized to the low time carrier signal<sup>(1)</sup>

bit 4 **Unimplemented:** Read as '0'

bit 3-0 MDCL<3:0> Modulator Data High Carrier Selection bits (1)

1111 = Reserved. No channel connected.

•

1000 = Reserved. No channel connected.

0111 = CCP4 output (PWM Output mode only)

0110 = CCP3 output (PWM Output mode only)

0101 = CCP2 output (PWM Output mode only)

0100 = CCP1 output (PWM Output mode only)

0011 = Reference Clock module signal

0010 = MDCIN2 port pin

0001 = MDCIN1 port pin

0000 = Vss

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0 | Register on Page |

|--------|----------|---------|----------|--------|-------|-------|--------|-------|------------------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC |        |       | MDCH  | l<3:0> |       | 199              |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      |       | MDCL  | .<3:0> |       | 200              |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT | _     | _      | MDBIT | 197              |

| MDSRC  | MDMSODIS | _       | _        | _      |       | MDMS  | S<3:0> |       | 198              |

**Legend:** — Unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

#### REGISTER 24-5: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 |

|-------|-----|-----|----------|---------|---------|---------|---------|

| _     | 1   | ı   | STRxSYNC | STRxD   | STRxC   | STRxB   | STRxA   |

| bit 7 |     |     |          |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-5 Unimplemented: Read as '0' bit 4 STRxSYNC: Steering Sync bit 1 = Output steering update occurs on next PWM period 0 = Output steering update occurs at the beginning of the instruction cycle boundary bit 3 STRxD: Steering Enable bit D 1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0> 0 = PxD pin is assigned to port pin bit 2 STRxC: Steering Enable bit C 1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0> 0 = PxC pin is assigned to port pin bit 1 STRxB: Steering Enable bit B 1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0> 0 = PxB pin is assigned to port pin bit 0 STRxA: Steering Enable bit A 1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0> 0 = PxA pin is assigned to port pin

**Note 1:** The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

### 25.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

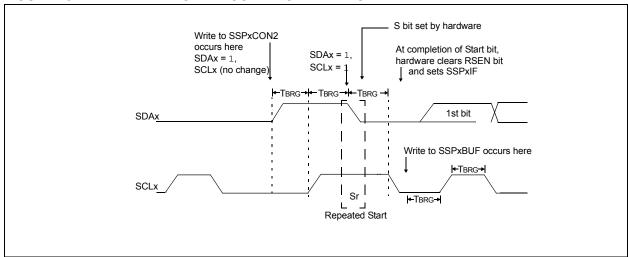

A Repeated Start condition (Figure 25-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be

automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

FIGURE 25-27: REPEAT START CONDITION WAVEFORM

#### 27.4 Current Ranges

The Capacitive Sensing Oscillator can operate within several different current ranges, depending on the Voltage Reference mode and current range selections. Within each of the two Voltage Reference modes there are four current ranges.

Selection between the Voltage Reference modes is controlled by the CPSRM bit of the CPSCON0 register. Clearing this bit selects the Fixed Voltage References provided by the Capacitive Sensing Oscillator module. Setting this bit selects the variable voltage references supplied by the Fixed Voltage Reference (FVR) module and the Digital-to-Analog Converter (DAC) module. See Section 27.3 "Voltage References" for more information on configuring the voltage references. Selecting the current range within the voltage reference mode is controlled by configuring the CPSRNG<1:0> bits in the CPSCON0 register. See Table 27-1 for proper current mode

selection.

The Noise Detection mode is unique in that it disables the constant current source associated with the selected input pin, but leaves the rest of the oscillator circuitry and pin structure active. This eliminates the oscillation frequency on the analog pin and greatly reduces the current consumed by the Oscillator module. When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator stage, indicating the presence of activity on the pin. Figure 27-2 shows a more detailed drawing of the constant current sources and comparators associated with the oscillator and input pin.

TABLE 27-1: CURRENT MODE SELECTION

| CPSRM | Voltage Reference Mode | CPSRNG<1:0> | Current Range <sup>(1)</sup> |

|-------|------------------------|-------------|------------------------------|

|       |                        | 00          | Off                          |

| 2     | Fixed                  | 01          | Low                          |

| 0     | Fixed                  | 10          | Medium                       |

|       |                        | 11          | High                         |

| 1     |                        | 00          | Noise Detection              |

|       | ) /o via bla           | 01          | Low                          |

|       | Variable —             | 10          | Medium                       |

|       |                        | 11          | High                         |

Note 1: See Power-Down Currents (IPD) in Section 30.3 "DC Characteristics: PIC16(L)F1825/9-I/E (Power-Down)" for more information.

| CALL             | Call Subroutine                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Call Subroutine. First, return address (PC + 1) is pushed onto the stack. The 11-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a 2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CLRWDT                                                                                                                                              |

| Operands:        | None                                                                                                                                                          |

| Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$<br>1 → $\overline{PD}$                                                                                 |

| Status Affected: | TO, PD                                                                                                                                                        |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                         |

| Operands:        | None                                                                                                                                                                                                                    |

| Operation:       | $(PC) +1 \to TOS,$<br>$(W) \to PC<7:0>,$<br>$(PCLATH<6:0>) \to PC<14:8>$                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                    |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a two-cycle instruction. |

| COMF             | Complement f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                         |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |

|                  |                                                                                                                                                    |

| CLRF             | Clear f                                                        |

|------------------|----------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                 |

| Operands:        | $0 \leq f \leq 127$                                            |

| Operation:       | $00h \rightarrow (f)$ $1 \rightarrow Z$                        |

| Status Affected: | Z                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |

| DECF             | Decrement f                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                       |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |

| Status Affected: | Z                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| CLRW             | Clear W                                     |

|------------------|---------------------------------------------|

| Syntax:          | [label] CLRW                                |

| Operands:        | None                                        |

| Operation:       | $00h \to (W)$ $1 \to Z$                     |

| Status Affected: | Z                                           |

| Description:     | W register is cleared. Zero bit (Z) is set. |

| LSLF             | Logical Left Shift                                                                                                                                                                                                      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] LSLF f {,d}                                                                                                                                                                                                   |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                      |  |

| Operation:       | $(f<7>) \rightarrow C$<br>$(f<6:0>) \rightarrow dest<7:1>$<br>$0 \rightarrow dest<0>$                                                                                                                                   |  |

| Status Affected: | C, Z                                                                                                                                                                                                                    |  |

| Description:     | The contents of register 'f' are shifted one bit to the left through the Carry flag. A '0' is shifted into the LSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |  |

|                  | C ← register f ← 0                                                                                                                                                                                                      |  |

| LSRF             | Logical Right Shift                                                                                                                                                                                                      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] LSRF f {,d}                                                                                                                                                                                                    |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                       |  |

| Operation:       | $0 \rightarrow \text{dest<7>}$ $(f<7:1>) \rightarrow \text{dest<6:0>},$ $(f<0>) \rightarrow C,$                                                                                                                          |  |

| Status Affected: | C, Z                                                                                                                                                                                                                     |  |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. A '0' is shifted into the MSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |  |

|                  | 0 → register f C                                                                                                                                                                                                         |  |

| MOVF             | Move f                                                                                                                                                                                                                                                  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                      |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                      |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                |  |

| Status Affected: | Z                                                                                                                                                                                                                                                       |  |

| Description:     | The contents of register f is moved to a destination dependent upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |  |

| Words:           | 1                                                                                                                                                                                                                                                       |  |

| Cycles:          | 1                                                                                                                                                                                                                                                       |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                             |  |

|                  | After Instruction  W = value in FSR register  Z = 1                                                                                                                                                                                                     |  |

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVIW ++FSRn<br>[ label ] MOVIWFSRn<br>[ label ] MOVIW FSRn++<br>[ label ] MOVIW FSRn<br>[ label ] MOVIW k[FSRn]                                                                                                                 |

| Operands:        | $n \in [0,1]$<br>$mm \in [00,01, 10, 11]$<br>$-32 \le k \le 31$                                                                                                                                                                            |

| Operation:       | INDFn → W Effective address is determined by • FSR + 1 (preincrement) • FSR - 1 (predecrement) • FSR + k (relative offset) After the Move, the FSR value will be either: • FSR + 1 (all increments) • FSR - 1 (all decrements) • Unchanged |

| Status Affected: | Z                                                                                                                                                                                                                                          |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

| Description: | This instruction is used to move data  |

|--------------|----------------------------------------|

|              | between W and one of the indirect      |

|              | registers (INDFn). Before/after this   |

|              | move, the pointer (FSRn) is updated by |

|              | nre/nost incrementing/decrementing it  |

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

#### MOVLB Move literal to BSR

| Syntax:          | [ label ] MOVLB k |

|------------------|-------------------|

| Operands:        | $0 \le k \le 15$  |

| Operation:       | $k \to BSR$       |

| Status Affected: | None              |

|                  |                   |

The 5-bit literal 'k' is loaded into the Bank Select Register (BSR).

| MOVLP            | Move literal to PCLATH                                    |  |  |  |  |

|------------------|-----------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] MOVLP k                                         |  |  |  |  |

| Operands:        | $0 \leq k \leq 127$                                       |  |  |  |  |

| Operation:       | $k \to PCLATH$                                            |  |  |  |  |

| Status Affected: | None                                                      |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register. |  |  |  |  |

| MOVLW            | Move literal to W                                         |  |  |  |  |

| Syntax:          | [label] MOVLW k                                           |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                       |  |  |  |  |

| Syrilax.         | [ laber ] IVIO V LVV K                                                                    |

|------------------|-------------------------------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction W = 0x5A                                                                |

| MOVWF            | Move W to f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWF f                                                  |

| Operands:        | $0 \leq f \leq 127$                                                |

| Operation:       | $(W) \rightarrow (f)$                                              |

| Status Affected: | None                                                               |

| Description:     | Move data from W register to register 'f'.                         |

| Words:           | 1                                                                  |

| Cycles:          | 1                                                                  |

| Example:         | MOVWF OPTION_REG                                                   |

|                  | Before Instruction  OPTION_REG = 0xFF  W = 0x4F  After Instruction |

OPTION\_REG = 0x4F

W = 0x4F

Description:

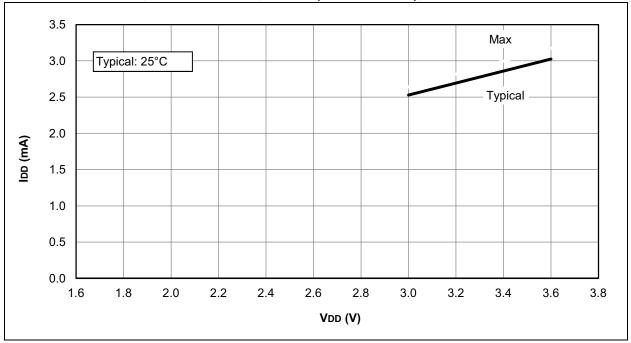

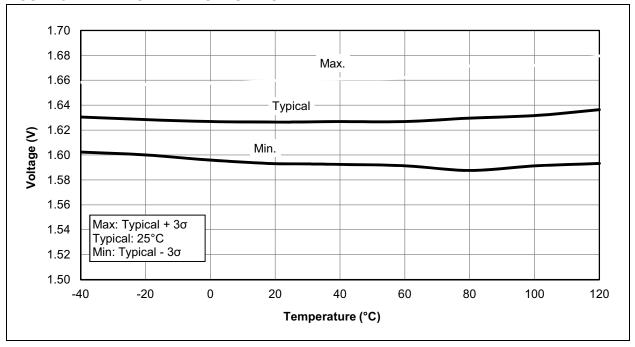

FIGURE 31-19: IDD, HS OSCILLATOR, 32 MHz (8 MHz + 4xPLL), PIC16LF1825/9 ONLY

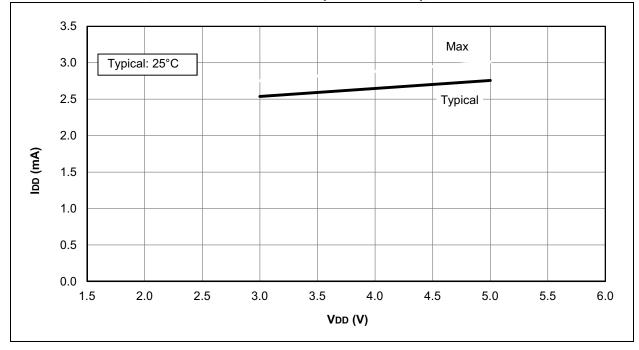

FIGURE 31-20: IDD, HS OSCILLATOR, 32 MHz (8 MHz + 4xPLL), PIC16F1825/9 ONLY

-5

0

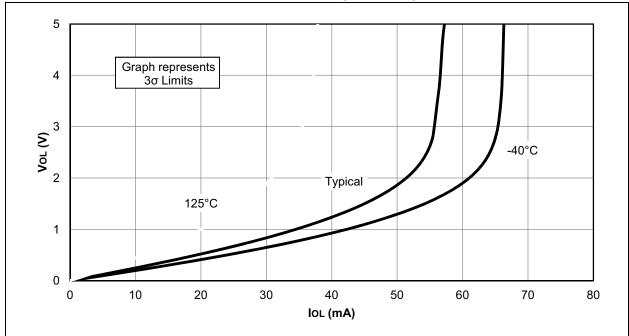

6 Graph represents 5 . 3σ Limits 4 -40°C 125°C 2 Typical 1 0

-15

IOH (mA)

-10

FIGURE 31-41: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V), PIC16F1825/9 ONLY

-20

-30

-25

FIGURE 31-47: POR RELEASE VOLTAGE

FIGURE 31-48: POR REARM VOLTAGE, PIC16F1825/9 ONLY

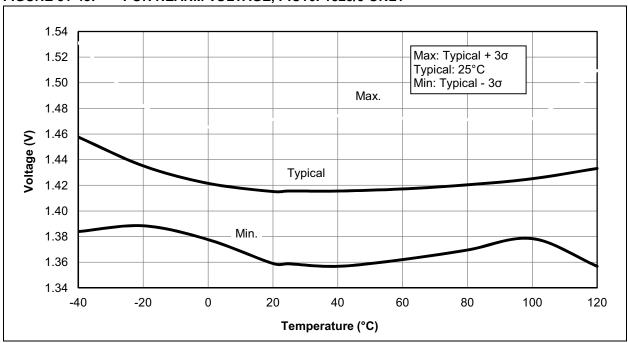

#### 33.2 Package Details

The following sections give the technical details of the packages.

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES   |      |      |

|----------------------------|------------------|----------|------|------|

|                            | Dimension Limits | MIN      | NOM  | MAX  |

| Number of Pins             | N                | 14       |      |      |

| Pitch                      | е                | .100 BSC |      |      |

| Top to Seating Plane       | А                | _        | _    | .210 |

| Molded Package Thickness   | A2               | .115     | .130 | .195 |

| Base to Seating Plane      | A1               | .015     | _    | _    |

| Shoulder to Shoulder Width | E                | .290     | .310 | .325 |

| Molded Package Width       | E1               | .240     | .250 | .280 |

| Overall Length             | D                | .735     | .750 | .775 |

| Tip to Seating Plane       | L                | .115     | .130 | .150 |

| Lead Thickness             | С                | .008     | .010 | .015 |

| Upper Lead Width           | b1               | .045     | .060 | .070 |

| Lower Lead Width           | b                | .014     | .018 | .022 |

| Overall Row Spacing §      | eB               | _        | _    | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

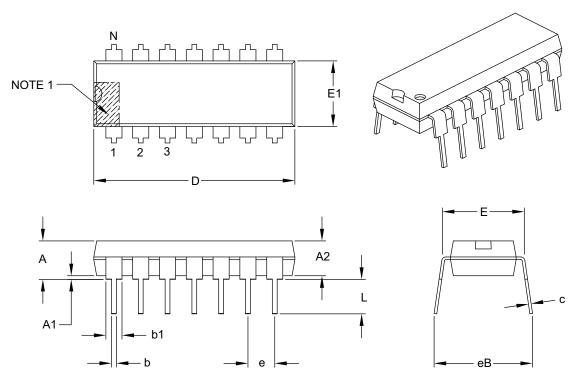

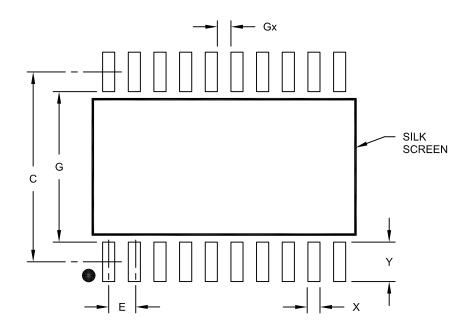

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | Е           | 1.27 BSC |      |      |

| Contact Pad Spacing      | С           |          | 9.40 |      |

| Contact Pad Width (X20)  | Х           |          |      | 0.60 |

| Contact Pad Length (X20) | Υ           |          |      | 1.95 |

| Distance Between Pads    | Gx          | 0.67     |      |      |

| Distance Between Pads    | G           | 7.45     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

#### THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support