# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

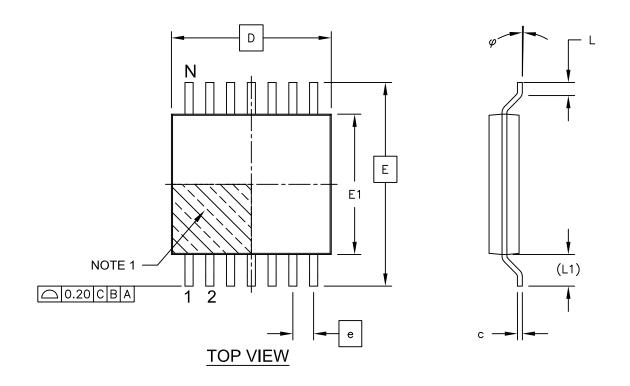

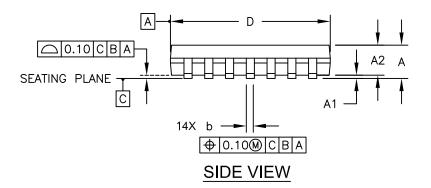

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1829t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                 | Function | Input<br>Type | Output<br>Type | Description                                   |

|------------------------------------------------------|----------|---------------|----------------|-----------------------------------------------|

| RA0/AN0/CPS0/C1IN+/VREF-/                            | RA0      | TTL           | CMOS           | General purpose I/O.                          |

| DACOUT/TX <sup>(1)</sup> /CK <sup>(1)</sup> /        | AN0      | AN            | —              | A/D Channel 0 input.                          |

| ICSPDAT/ICDDAT                                       | CPS0     | AN            | _              | Capacitive sensing input 0.                   |

|                                                      | C1IN+    | AN            | _              | Comparator C1 positive input.                 |

|                                                      | VREF-    | AN            | —              | A/D and DAC Negative Voltage Reference input. |

|                                                      | DACOUT   | _             | AN             | Digital-to-Analog Converter output.           |

|                                                      | TX       | _             | CMOS           | USART asynchronous transmit.                  |

|                                                      | СК       | ST            | CMOS           | USART synchronous clock.                      |

|                                                      | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                               |

|                                                      | ICDDAT   | ST            | CMOS           | In-Circuit Data I/O.                          |

| RA1/AN1/CPS1/C12IN0-/VREF+/                          | RA1      | TTL           | CMOS           | General purpose I/O.                          |

| SRI/RX <sup>(1)</sup> /DT <sup>(1)</sup> /ICSPCLK/   | AN1      | AN            | —              | A/D Channel 1 input.                          |

| ICDCLK                                               | CPS1     | AN            | _              | Capacitive sensing input 1.                   |

|                                                      | C12IN0-  | AN            | —              | Comparator C1 or C2 negative input.           |

|                                                      | VREF+    | AN            | —              | A/D and DAC Positive Voltage Reference input. |

|                                                      | SRI      | ST            | —              | SR Latch input.                               |

|                                                      | RX       | ST            | —              | USART asynchronous input.                     |

|                                                      | DT       | ST            | CMOS           | USART synchronous data.                       |

|                                                      | ICSPCLK  | ST            | —              | Serial Programming Clock.                     |

|                                                      | ICDCLK   | ST            | —              | In-Circuit Debug Clock.                       |

| RA2/AN2/CPS2/T0CKI/INT/                              | RA2      | ST            | CMOS           | General purpose I/O.                          |

| C1OUT/SRQ/CCP3/FLT0                                  | AN2      | AN            | —              | A/D Channel 2 input.                          |

|                                                      | CPS2     | AN            | —              | Capacitive sensing input 2.                   |

|                                                      | TOCKI    | ST            | _              | Timer0 clock input.                           |

|                                                      | INT      | ST            | _              | External interrupt.                           |

|                                                      | C10UT    |               | CMOS           | Comparator C1 output.                         |

|                                                      | SRQ      |               | CMOS           | SR Latch non-inverting output.                |

|                                                      | CCP3     | ST            | CMOS           | Capture/Compare/PWM3.                         |

|                                                      | FLT0     | ST            | _              | ECCP Auto-Shutdown Fault input.               |

| RA3/SS1 <sup>(1)</sup> /T1G <sup>(1)</sup> /VPP/MCLR | RA3      | TTL           |                | General purpose input.                        |

|                                                      | SS1      | ST            | —              | Slave Select input.                           |

|                                                      | T1G      | ST            | —              | Timer1 Gate input.                            |

|                                                      | VPP      | ΗV            | _              | Programming voltage.                          |

|                                                      | MCLR     | ST            | _              | Master Clear with internal pull-up.           |

TABLE 1-2: PIC16(L)F1825 PINOUT DESCRIPTION

Legend:AN = Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$ = Schmitt Trigger input with  $I^2C$ HV = High VoltageXTAL = CrystalLevels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Default function location.

### 3.3 PCL and PCLATH

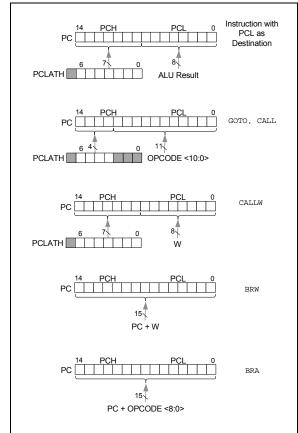

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.3.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.3.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.3.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

### 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Word 1

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Word 1.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |

|-------|-------------------------------------------|

|       | occur from Two-Speed Start-up or          |

|       | Fail-Safe Clock Monitor, does not update  |

|       | the SCS bits of the OSCCON register. The  |

|       | user can monitor the OSTS bit of the      |

|       | OSCSTAT register to determine the current |

|       | system clock source.                      |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 Oscillator.

#### 5.3.3 TIMER1 OSCILLATOR

The Timer1 Oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 21.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 Oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

|         | -     | -      | _     |       |             | _           |       | _           | _                   |        |     |

|---------|-------|--------|-------|-------|-------------|-------------|-------|-------------|---------------------|--------|-----|

| Name    | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2       | Bit 1 | Bit 0       | Register<br>on page |        |     |

| FVRCON  | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV       | CDAFVR<1:0> |       | CDAFVR<1:0> |                     | R<1:0> | 142 |

| DACCON0 | DACEN | DACLPS | DACOE | _     | DACPSS<1:0> |             | —     | DACNSS      | 160                 |        |     |

| DACCON1 | —     | —      |       |       | DACR<4:0>   |             |       |             |                     |        |     |

TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

Legend: — Unimplemented, read as '0'. Shaded cells are unused by the DAC module.

#### 22.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 modules is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 22.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMRx register

- · a write to the TxCON register

- · Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMRx is not cleared when TxCON is written.

#### 22.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIRx register. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIEx register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

#### 22.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode. Additional information is provided in Section 25.0 "Master Synchronous Serial Port (MSSP1 and MSSP2) Module".

#### 22.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

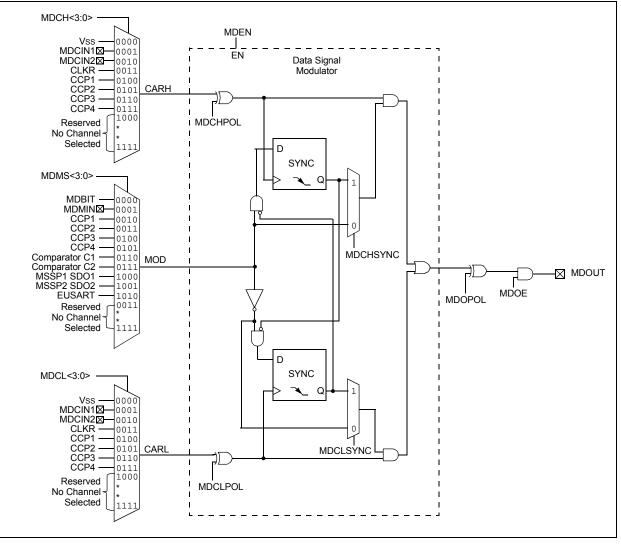

### 23.0 DATA SIGNAL MODULATOR

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal. Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- Carrier Source Pin Disable

- Programmable Modulator Data

- Modulator Source Pin Disable

- Modulated Output Polarity Select

- Slew Rate Control

Figure 23-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

### 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 25-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSPx module must be in an Idle     |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 25.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

### 25.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

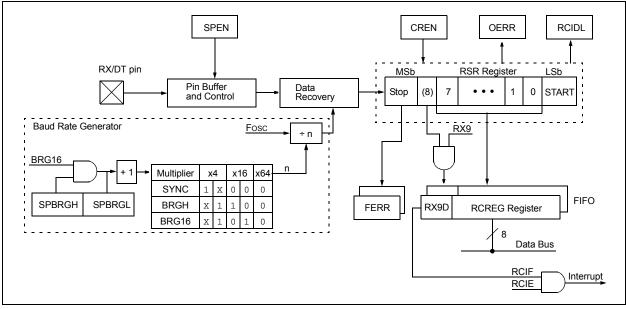

#### FIGURE 26-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 26-1, Register 26-2 and Register 26-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

#### 26.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 26.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 26.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 26.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1825/9 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

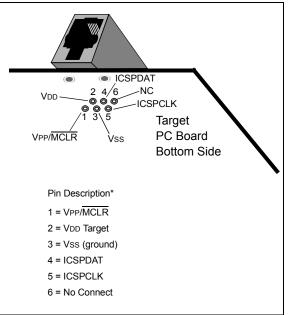

#### 28.3 Common Programming Interfaces

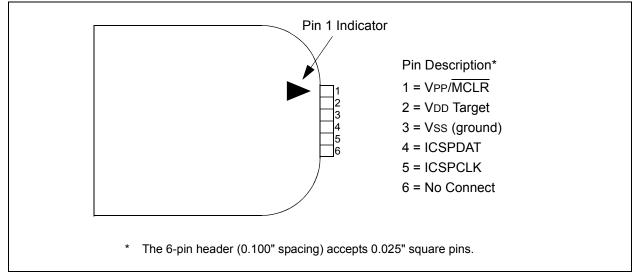

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

#### FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

| Mnen   | nonic, | Description                                   | Cycles |     | 14-Bit | Opcode | 9    | Status   | Notes |

|--------|--------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Oper   | ands   | Description                                   | Cycles | MSb |        |        | LSb  | Affected | Notes |

|        |        | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA    | k      | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW    | -      | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL   | k      | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW  | -      | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO   | k      | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE | k      | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW  | k      | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN | -      | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|        |        |                                               | ATIONS |     |        |        |      |          |       |

| CLRWDT | _      | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP    | -      | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION | -      | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET  | -      | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP  | -      | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS   | f      | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|        |        | C-COMPILER OPT                                | IMIZED |     |        |        |      | •        |       |

| ADDFSR | n, k   | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW  | n mm   | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|        |        | modifier, mm                                  |        |     |        |        |      |          |       |

|        | k[n]   | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | kkkk | Z        | 2     |

| MOVWI  | n mm   | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | lnmm |          | 2, 3  |

|        |        | modifier, mm                                  |        |     |        |        |      |          |       |

|        | k[n]   | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   | kkkk |          | 2     |

### TABLE 29-3: PIC16(L)F1825/9 ENHANCED INSTRUCTION SET (CONTINUED)

Note 1:If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

#### **TABLE 30-4**: **CLKOUT AND I/O TIMING PARAMETERS**

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sym.                                                                                                                     | Characteristic                                                                                                           | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Тур†                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| TosH2ckL                                                                                                                 | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TosH2ckH                                                                                                                 | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TckL2ioV                                                                                                                 | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TioV2ckH                                                                                                                 | Port input valid before CLKOUT↑ <sup>(1)</sup>                                                                           | Tosc + 200 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TosH2ioV                                                                                                                 | Fosc↑ (Q1 cycle) to Port out valid                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TosH2iol                                                                                                                 | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TioV2osH                                                                                                                 | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TioR                                                                                                                     | Port output rise time                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40<br>15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72<br>32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 1.8V<br>VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TioF                                                                                                                     | Port output fall time                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28<br>15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55<br>30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD = 1.8V<br>VDD = 3.3-5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Tinp                                                                                                                     | INT pin input high or low time                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Tioc                                                                                                                     | Interrupt-on-change new input level time                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                          | sym.<br>TosH2ckL<br>TosH2ckH<br>TckL2ioV<br>TioV2ckH<br>TosH2ioV<br>TosH2ioI<br>TioV2osH<br>TioR<br>TioF<br>Tinp<br>Tioc | sym.CharacteristicTosH2ckLFosc^ to CLKOUT $\downarrow$ (1)TosH2ckHFosc^ to CLKOUT $\uparrow$ (1)TokL2ioVCLKOUT $\downarrow$ to Port out valid (1)TioV2ckHPort input valid before CLKOUT $\uparrow$ (1)TosH2ioVFosc^ (Q1 cycle) to Port out validTosH2ioIFosc^ (Q2 cycle) to Port input invalid<br>(I/O in hold time)TioV2osHPort input valid to Fosc^ (Q2 cycle)<br>(I/O in setup time)TioRPort output rise timeTioFPort output fall timeTinpINT pin input high or low timeTiocInterrupt-on-change new input level | ng Temperature -40°C $\leq$ TA $\leq$ +125°CSym.CharacteristicMin.TosH2ckLFosc^t to CLKOUT $\downarrow$ (1)—TosH2ckHFosc^t to CLKOUT $\uparrow$ (1)—TckL2ioVCLKOUT $\downarrow$ to Port out valid (1)—TioV2ckHPort input valid before CLKOUT $\uparrow$ (1)Tosc + 200 nsTosH2ioVFosc^t (Q1 cycle) to Port out valid—TosH2ioIFosc^t (Q2 cycle) to Port input invalid<br>(I/O in hold time)50TioV2osHPort input valid to Fosc^t (Q2 cycle)<br>(I/O in setup time)20TioRPort output rise time—TioFPort output fall time—TinpINT pin input high or low time25TiocInterrupt-on-change new input level<br>time25 | Sym.CharacteristicMin.TyptTosH2ckLFosc^t to CLKOUT $\downarrow$ (1)TosH2ckHFosc^t to CLKOUT $\uparrow$ (1)TckL2ioVCLKOUT $\downarrow$ to Port out valid (1)TioV2ckHPort input valid before CLKOUT $\uparrow$ (1)Tosc + 200 nsTosH2ioVFosc^t (Q1 cycle) to Port out valid50TosH2ioVFosc^t (Q2 cycle) to Port input invalid50TioV2osHPort input valid to Fosc^t (Q2 cycle)20TioRPort output rise time40TioFPort output fall time15TinpINT pin input high or low time25TiocInterrupt-on-change new input level25 | Ing Temperature -40°C $\leq$ TA $\leq$ +125°CMin.TyptMax.Sym.CharacteristicMin.TyptMax.TosH2ckLFosc^t to CLKOUT $\downarrow$ (1)70TosH2ckHFosc^t to CLKOUT $\uparrow$ (1)72TckL2ioVCLKOUT $\downarrow$ to Port out valid (1)20TioV2ckHPort input valid before CLKOUT $\uparrow$ (1)Tosc + 200 nsTosH2ioVFosc^t (Q1 cycle) to Port out valid5070*TosH2ioIFosc^t (Q2 cycle) to Port input invalid<br>(I/O in hold time)50TioV2osHPort input valid to Fosc^t (Q2 cycle)<br>(I/O in setup time)20TioRPort output rise time4072TioFPort output fall time2855TioPINT pin input high or low time25TiocInterrupt-on-change new input level<br>time25 | sym.CharacteristicMin.TyptMax.UnitsTosH2ckLFosc^ to CLKOUT $\downarrow$ (1)70nsTosH2ckHFosc^ to CLKOUT $\uparrow$ (1)72nsTckL2ioVCLKOUT $\downarrow$ to Port out valid (1)20nsTioV2ckHPort input valid before CLKOUT $\uparrow$ (1)Tosc + 200 nsnsTosH2ioVFosc^ (Q1 cycle) to Port out valid5070*nsTosH2ioVFosc^ (Q2 cycle) to Port input invalid50nsTosH2ioIFosc^ (Q2 cycle) to Port input invalid50nsTioV2osHPort input valid to Fosc^ (Q2 cycle)20nsTioRPort output rise time4072nsTioFPort output fall time2855nsTinpINT pin input high or low time25nsTioCInterrupt-on-change new input level25ns |  |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. t

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

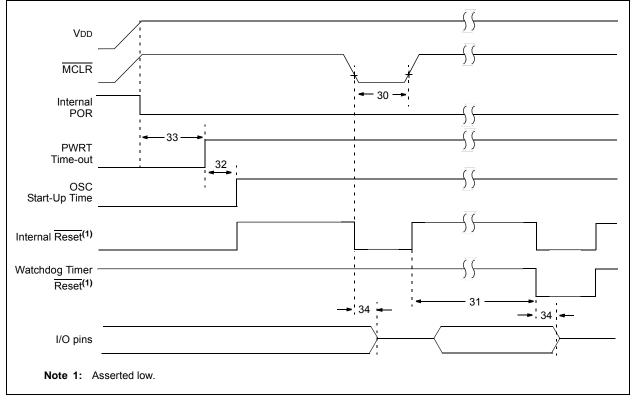

#### RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP **FIGURE 30-8:** TIMER TIMING

#### **TABLE 30-5**: **RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER** AND BROWN-OUT RESET PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated)<br>Dperating Temperature -40°C $\leq$ TA $\leq$ +125°C |                                                          |              |             |              |        |                                       |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|-------------|--------------|--------|---------------------------------------|--|--|--|--|

| Param<br>No. | Sym.                                                                                                           | Characteristic                                           | Min.         | Тур†        | Max.         | Units  | Conditions                            |  |  |  |  |